### **ADVANCE INFORMATION**

# 54ACT/74ACT2726 512 x 9 Bidirectional First In, First Out Memory (BIFIFO)

### **General Description**

The 512 x 9 FIFO is a first-in, first-out dual port memory capable of asynchronous, simultaneous read and write. Other important features are: expansion capability in both the word depth and bit width, half-full flag capability in the single device mode, empty and full warning flags, and ring pointers for zero fall-through time. There are two sets of bidirectional ports, each 9 bits wide, through which data flow can be controlled. A direction pin (DIR) controls the direction of the data: when the DIR is HIGH, A is the input port and B is the output port. When the DIR is LOW, the input port is B and output port is A. It is suited for high-speed applications.

#### **Features**

- First-in, first-out bidirectional memory

- 512 x 9 organization

- Low power consumption

- Asynchronous and simultaneous read and write

- Fully expandable by word depth and/or bit width

- Half-full flag capability in single device mode

- Master/slave multiprocessing applications

Bidirectional and rate buffer applications

- Empty and full warning flags

- Outputs source/sink 8 mA

- 'ACT2726 has TTL-compatible inputs

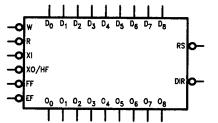

# **Logic Symbol**

TL/F/10656-1

| Pin Names                                                        | Description                   |  |

|------------------------------------------------------------------|-------------------------------|--|

| D <sub>0</sub> -D <sub>8</sub>                                   | Data Inputs                   |  |

| D <sub>0</sub> -D <sub>8</sub><br>O <sub>0</sub> -O <sub>8</sub> | Data Outputs                  |  |

| ₩                                                                | Write Enable                  |  |

| F                                                                | Read Enable                   |  |

| XI                                                               | Expansion In                  |  |

| XO/HF                                                            | Expansion Out, Half-Full Flag |  |

| EF                                                               | Empty Flag                    |  |

| FF                                                               | Full Flag                     |  |

| RS                                                               | Reset                         |  |

| DIR                                                              | Direction                     |  |

## **Connection Diagram**

# Pin Assignment for DiP. Flatpak and SOIC

|                  |    |    | •                       |

|------------------|----|----|-------------------------|

| ₩—               | 1  | 28 | -v <sub>cc</sub>        |

| 08-              | 2  | 27 | -D <sub>4</sub>         |

| D <sub>3</sub> — | 3  | 26 | —⊅ <sub>5</sub>         |

| D <sub>2</sub> — | 4  | 25 | <b>−</b> 06             |

| D,-              | 5  | 24 | <b>⊢</b> ₽ <sub>7</sub> |

| D <sub>0</sub> - | 6  | 23 | DIR                     |

| XI-              | 7  | 22 | — RS                    |

| řř–              | 8  | 21 | ⊷ ĔĒ                    |

| <b>₀</b> −       | 9  | 20 | ⊢ xo/π                  |

| 0,-              | 10 | 19 | <b>⊢</b> 0 <sub>7</sub> |

| 02-              | 11 | 18 | —о <sub>б</sub>         |

| 03-              | 12 | 17 | <b>−</b> 0 <sub>5</sub> |

| 08               | 13 | 16 | <b>⊢</b> 0₄             |

| ND —             | 14 | 15 | <b>⊢</b> Ā              |

|                  |    |    | J                       |

TL/F/10656-2