# HT93C56/C66 CMOS 2K/4K-Bit Serial EEPROM

### **Features**

- $5V \pm 10\%$  power supply

- Low power consumption

- Operating: 5mA max.

- Standby: 2µA max.

- User selectable internal organization

- 2K(HT93C56): 256×8 or 128×16

- 4K(HT93C66): 512×8 or 256×16

- Write cycle time <2ms

- Write operation with built-in timer

- Automatic erase-before-write operation

# **General Description**

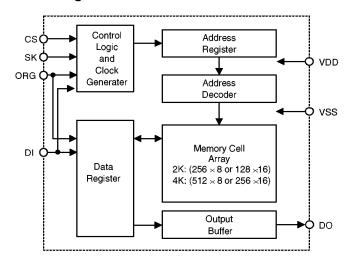

The HT93C56/C66 is a 2K/4K-bit serial read/write non-volatile memory device using the CMOS floating gate process. Its 2048/4096 bits of memory are organized into 128/256 words and each word is 16 bits, when the ORG pin is connected to VDD or 256/512 words and each word is 8 bits, when ORG pin is connected to GND. But

- Word/chip erase and write operation

- Auto-increment read operation

- Programming Status Indicator

- Software and hardware controlled write protection

- 10-year data retention after 100K rewrite cycles

- 10<sup>6</sup> rewrite cycles per word

- Operating temperature range: -40°C~+85°C

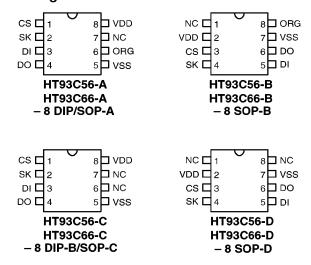

- 8-pin DIP/SOP package

HT93C56-C/66-C and HT93C56-D/66-D have not ORG pin and each word is always 16 bits.

By popular microcontroller, the versatile serial interface including chip select (CS), serial clock (SK), data input (DI) and data output (DO) can be easily controlled.

1

# Pin Assignment

# **Block Diagram**

# **Pin Description**

| Pin No. |           | Pin Name | I/O       | Dogovintion |                     |                                    |

|---------|-----------|----------|-----------|-------------|---------------------|------------------------------------|

| -A      | <b>-B</b> | -C       | <b>-D</b> | rm Name     | 100                 | Description                        |

| 1       | 3         | 1        | 3         | CS          | I                   | Chip select input                  |

| 2       | 4         | 2        | 4         | SK          | I                   | Serial clock input                 |

| 3       | 5         | 3        | 5         | DI          | I Serial data input |                                    |

| 4       | 6         | 4        | 6         | DO O        |                     | Serial data output                 |

| 5       | 7         | 5        | 7         | VSS         | I                   | Negative power supply              |

| 6       | 8         | 6        | 8         | ORG         | I                   | -A, -B Per word 8/16 bits option   |

| 6       | 0         | О        | 0         | OKG         | 1                   | -C, -D No ORG and Per word 16 bits |

| 7       | 1         | 7        | 8         | NC —        |                     | No connection                      |

| 8       | 2         | 8        | 2         | VDD I       |                     | Positive power supply              |

# **Absolute Maximum Ratings\***

| Supply Voltage0.3V to 6.0V       | Input VoltageVSS-0.3 to $V_{\rm DD}$ +0.3 |

|----------------------------------|-------------------------------------------|

| Storage Temperature50°C to 125°C | Operating Temperature40°C to 85°C         |

\*Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **D.C.** Characteristics

(Ta=-40°C to 85°C)

| G1                 | D                               |          | Test Conditions                                             | Min.  | Max. | Unit |

|--------------------|---------------------------------|----------|-------------------------------------------------------------|-------|------|------|

| Symbol             | Parameter                       | $V_{DD}$ | Conditions                                                  | WIII. |      |      |

| 37                 | O                               | _        | Read                                                        | 4.5   | 5.5  | v    |

| $ m V_{DD}$        | Operating Voltage               | _        | Write                                                       | 4.5   | 5.5  | v    |

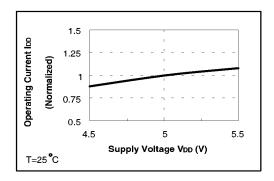

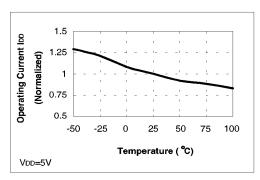

| $I_{\mathrm{DD1}}$ | Operating Current<br>Write mode | 5V       | DO unload, SK=1MHz                                          | _     | 5    | mA   |

| $I_{\mathrm{DD2}}$ | Operating Current<br>Read mode  | 5V       | DO unload, SK=1MHz                                          | _     | 2    | mA   |

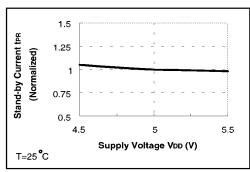

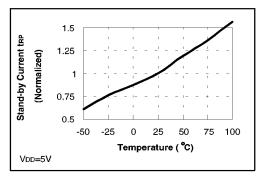

| $I_{STB}$          | Standby Current                 | 5V       | CS=SK=DI=0V                                                 | _     | 2    | μА   |

| ${ m I_{LI}}$      | Input Leakage<br>Current        | 5V       | $V_{\mathrm{IN}}=V_{\mathrm{DD}}\sim V_{\mathrm{SS}}$       | 0     | 1    | μА   |

| $I_{ m LO}$        | Output Leakage<br>Current       | 5V       | V <sub>OUT</sub> =V <sub>DD</sub> ~V <sub>SS</sub><br>CS=0V | 0     | 1    | μА   |

| G11                | D                                  |                 | Test Conditions                                 | ъ <i>п</i> : | Max.        | Unit           |

|--------------------|------------------------------------|-----------------|-------------------------------------------------|--------------|-------------|----------------|

| Symbol             | Parameter                          | V <sub>DD</sub> | Conditions                                      | Min.         |             |                |

| $ m V_{IL}$        | Low Level Input<br>Voltage         | 5V              | _                                               | 0            | 0.8         | v              |

| $V_{\mathrm{IH}}$  | High Level Input<br>Voltage        |                 |                                                 | 2            | $V_{ m DD}$ | v              |

| $V_{ m OL}$        | Low Level Output<br>Voltage        | 5V              | I <sub>OL</sub> =2.1mA                          | _            | 0.4         | v              |

| VoH                | High Level Output<br>Voltage       | 5V              | Ι <sub>ΟΗ</sub> =–400μΑ                         | 2.4          | _           | v              |

| $T_{ m RW}$        | Rewriting Times                    | 5V              | 25°C V <sub>DD</sub> =5V<br>Block mode (Note 2) | $10^6$       | _           | Times/<br>word |

| ${ m C_{IN}}$      | Input Capacitance<br>(see Note 1)  | _               | f=250kHz                                        | _            | 5           | pF             |

| $C_{\mathrm{OUT}}$ | Output Capacitance<br>(see Note 1) | _               | f=250kHz                                        | _            | 5           | pF             |

Note1: These parameters are periodically sampled but not 100% tested Note2: The block mode exercises all the cells of the array simultanously

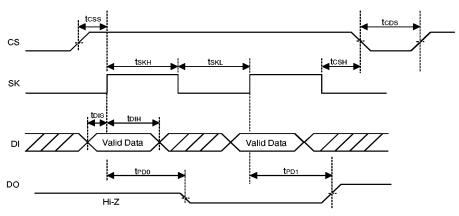

# A.C. Characteristics

(Ta=-40°C to 85°C)

| Symbol | Parameter         | VDD=     | Unit |     |

|--------|-------------------|----------|------|-----|

| ,      |                   | Min.     | Max. | •   |

| fsĸ    | Clock Frequency   | 0        | 2000 | kHz |

| tsкн   | SK High Time      | 250      | _    | ns  |

| tsĸĿ   | SK Low Time       | 250      | _    | ns  |

| tcss   | CS Setup Time     | 50       | _    | ns  |

| tсsн   | CS Hold Time      | 0        | _    | ns  |

| tcos   | CS Deselect Time  | 100      | _    | ns  |

| tois   | DI Setup Time     | 100      | _    | ns  |

| toin   | DI Hold Time      | ne 100 — |      | ns  |

| tPD1   | DO Delay to '1'   | _        | 400  | ns  |

| tPD0   | DO Delay to '0'   | _        | 400  | ns  |

| tsv    | Status Valid Time | _        | 100  | ns  |

| tHZ    | DO Disable Time   | _        | 100  | ns  |

| tpr    | Write Cycle Time  | _        | 2    | ms  |

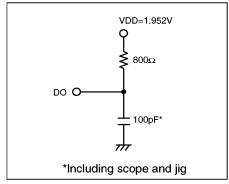

### A.C. Test Conditions

Input pluse levels: 0V to 3V

Input rise and fall time: 5ns (1V to 2V)

Input and output timing reference levels: 1.5V

Frequency: 1MHz

Output load: See Figure right

**Output Load Circuit**

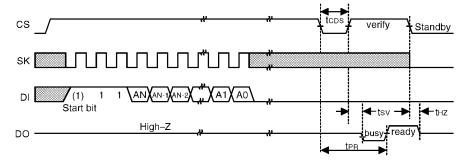

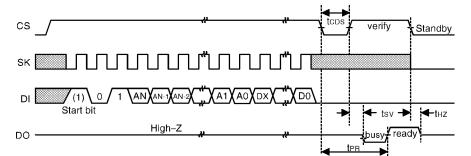

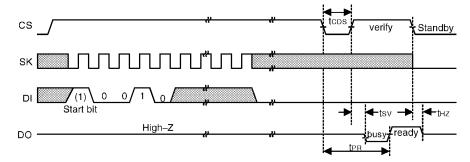

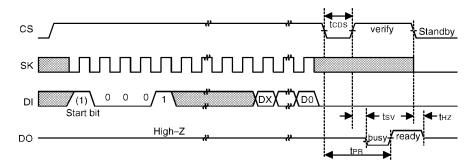

# **Timing Diagrams**

5

### **Functional Description**

The HT93C56/66 is accessed via a three-wire serial communication interface. The device is arranged into 128/256 words by 16 bits or 256/512 words by 8 bits depending on the ORG pin is connected to VDD or GND. The HT93C56/66 contains 7 instructions: READ, ERASE, WRITE, EWEN, EWDS, ERAL and WRAL. When the user selectable internal organization is arranged into 128/256x16 (256/512x8), these instructions are all made up of 11(12) bits data: 1 start bit, 2 op code bits and 8(9) address bits.

By using the control signal CS, SK and data input signal DI, these instructions can be given to the HT93C56/66 separately. These serial instruction data presented at the DI input will be

written into the device at the rising edge of SK. During the READ cycle, DO pin acts as the data output and during the WRITE or ERASE cycle, DO pin indicates the BUSY/READY status. When the DO pin to be active for read data or as a BUSY/READY indicator the CS pin must be high; otherwise DO pin will be in a high-impedance state. For successful instructions, CS must be low once after the instruction is sent. After power on, the device is defautly in the EWDS state. And, an EWEN instruction must be performed before any ERASE or WRITE instruction can be executed. Following are the functional descriptions and timing diagrams of all 7 instructions.

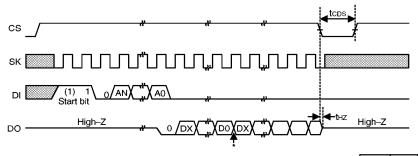

#### READ

The READ instruction will stream out data at a specified address on the DO pin. The data on DO pin changes during the low-to-high edge of SK signal. The 8 bits or 16 bits data stream is preceded by a logical '0' dummy bit. Irrespective of the condition of the EWEN or EWDS instruction, the READ command is always valid and independent of these two instructions. After the data word has been read the internal address will be automatically incremented by 1 allowing the next consecutive data word to be read out without entering further address data. The address will wrap around with CS High until CS returns to LOW.

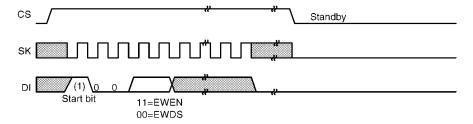

#### **EWEN/EWDS**

The EWEN/EWDS instruction will enable or disable the programming capabilities. At both the power on and power off state the device is automatically entered the disable mode. Before a WRITE, ERASE, WRAL or ERAL instruction is given, the programming enable instruction EWEN must be issued, otherwise the ERASE/WRITE instruction is invalid. After the EWEN instruction is issued, the programming enable condition remains until power is turned off or a EWDS instruction is given. None data can be written into the device in the programming disabled state. By so doing, the internal memory data can be protected.

#### **ERASE**

The ERASE instruction erases data at the specified addresses in the programming enable mode. After the ERASE op-code and the specified address have been issued, the data erasing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signals for the internal erasing, so the SK clock is not required. During the internal erasing, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over the DO pin will return to high and further instructions can be executed.

#### **WRITE**

The WRITE instruction writes data into the device at the specified addresses in the programming enable mode. After the WRITE opcode and the specified address and data have been issued, the data writing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signal for the internal writing, so the SK clock is not required. The auto-timing write cycle includes an automatic erase-before-write capability. So, it is not necessary to erase data before the WRITE instruction. During the internal writing, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over the DO pin will return to high and further instructions can be executed.

#### **ERAL**

The ERAL instruction erases the entire 128/256x16 or 256/512x8memory cells to logical '1' state in the programming enable mode. After the erase-all instruction set has been issued, the data erasing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signal for the erase-all operation, so the SK clock is not required. During the internal erase-all operation, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over the DO pin will return to high and further instruction can be executed.

### WRAL

6

The WRAL instruction writes data into the entire 128/256x16 or 256/512x8 memory cells in the programming enable mode. After the writeall instruction set has been issued, the data writing is activated by the falling edge of CS. Since the internal auto-timing generator provides all timing signals for the write-all operation, so the SK clock is not required. During the internal write-all operation, we can verify the busy/ready status if CS is high. The DO pin will remain low but when the operation is over the DO pin will return to high and further instruction can be executed.

# **Instruction Set for HT93C56**

| Instruction | Comments            | Start<br>bit | Op<br>Code | Address<br>ORG=0 ORG=1<br>X8 X16 | Data<br>ORG=0 ORG=1<br>X8 X16 |

|-------------|---------------------|--------------|------------|----------------------------------|-------------------------------|

| READ        | Read data           | 1            | 10         | XA7~A0 XA6~A0                    | D7~D0 D15~D0                  |

| ERASE       | Erase data          | 1            | 11         | XA7~A0 XA6~A0                    | _                             |

| WRITE       | Write data          | 1            | 01         | XA7~A0 XA6~A0                    | D7~D0 D15~D0                  |

| EWEN        | Erase/Write Enable  | 1            | 00         | 11XXXXXXX 11XXXXXX               | _                             |

| EWDS        | Erase/Write Disable | 1            | 00         | 00XXXXXXX 00XXXXXX               | _                             |

| ERAL        | Erase All           | 1            | 00         | 10XXXXXXX 10XXXXXX               | _                             |

| WRAL        | Write All           | 1            | 00         | 01XXXXXXX 01XXXXXX               | D7~D0 D15~D0                  |

# Instruction Set for HT93C66

| Instruction | Comments            | Start<br>bit | Op<br>Code | Address<br>ORG=0 ORG=1<br>X8 X16 | Data<br>ORG=0 ORG=1<br>X8 X16 |

|-------------|---------------------|--------------|------------|----------------------------------|-------------------------------|

| READ        | Read data           | 1            | 10         | A8~A0 A7~A0                      | D7~D0 D15~D0                  |

| ERASE       | Erase data          | 1            | 11         | A8~A0 A7~A0                      | _                             |

| WRITE       | Write data          | 1            | 01         | A8~A0 A7~A0                      | D7~D0 D15~D0                  |

| EWEN        | Erase/Write Enable  | 1            | 00         | 11XXXXXXX 11XXXXXX               | _                             |

| EWDS        | Erase/Write Disable | 1            | 00         | 00XXXXXXX 00XXXXXX               | _                             |

| ERAL        | Erase All           | 1            | 00         | 10XXXXXXX 10XXXXXX               | _                             |

| WRAL        | Write All           | 1            | 00         | 01XXXXXXX 01XXXXXX               | D7~D0 D15~D0                  |

7

Note: X stands for "don't care"

# **Instruction Timing**

### READ

- $^{\star}$  Address bit A7 becomes a "don't care" (X16 mode) on 93C56

- \* Address bit A8 becomes a "don't care" (X8 mode) on 93C56

- \* Address pointer automatically cycles to the next word

| Mode | (X16) | (X8) |  |  |

|------|-------|------|--|--|

| AN   | A7    | A8   |  |  |

| DX   | D15   | D7   |  |  |

### **EWEN/EWDS**

### **ERASE**

8

# WRITE

### **ERAL**

### WRAL

9

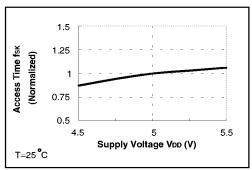

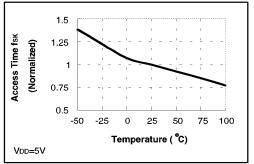

# **Characteristic Curves**