T-75-11-29

# 2MBIT PCM SIGNALLING CIRCUIT MV1441

## HDB3 ENCODER/DECODER/CLOCK REGENERATOR

The 2.048MBit PCM Signalling Circuits comprise a group of circuits which will perform the common signalling and error detection functions for a 2.048MBit PCM transmission link operating to the appropriate CCITT recommendations. The circuits are fabricated in CMOS and operate from a single 5 volt supply with relevant inputs and outputs TTL compatible.

The MV1441 is an encoder/decoder for the pseudo-ternary transmission code, HDB3 (CCITT Orange Book Vol.III.2 Annex to Rec. G703). The device encodes and decodes simultaneously and asynchronously. Error monitoring functions are provided to detect violations of HDB3 coding, all ones detection and loss of input (all zeros detection). In addition a loop back function is provided for terminal testing. A clock recovery circuit is provided using a 16.384MHz crystal (12.352MHz for 1.544MHz operation), which may be shared between several separate devices.

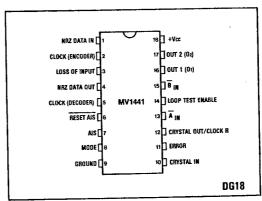

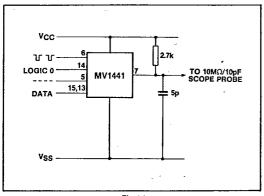

Fig.1 Pin connections - top view

#### **FEATURES**

- On-Chip Digital Clock Regenerator

- HDB3 Encoding and Decoding to CCITT rec. G703

- Asynchronous Operation

- Simultaneous Encoding and Decoding

- Clock Recovery Signal allows Off-Chip Clock Regeneration

- Loop Back Control

- HDB3 Error Monitor

- 'All Ones' Error Monitor

- Loss of Input Alarm (All Zeros Detector)

- Decode Data in NRZ Form

- Low Power Operation

- 2.048MHz or 1.544MHz Operation

#### DATA IN ENCODER 001 CLOCK o-(ENCODER) LOSS COUNTER INPUT SWITCH TEST C NRZ DATA AIN C DECODER BING CLOCK O-CLOCK CRYSTAL O ERROR CIRCUIT FRROR CRYSTAL OUT/ CLOCK R SWITCH AIS CIRCUIT

Fig.2 Block diagram

#### **ABSOLUTE MAXIMUM RATINGS**

The absolute maximum ratings are limiting values above which operating life may be shortened or specified parameters may be degraded.

#### Electrical Ratings

+Vcc Inputs Outputs -0.5V to +7V Vcc +0.5V Gnd -0.3V Vcc Gnd -0.3V

### **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated):

Supply voltage  $Vcc = 5V \pm 0.5V$  Ambient temperature  $T_{amb} = 0^{\circ}C$  to  $+70^{\circ}C$

#### Static characteristics

MV1441

| Characteristic            | Symbol | Pins        | Value    |     |     | Units | Conditions                                |

|---------------------------|--------|-------------|----------|-----|-----|-------|-------------------------------------------|

|                           |        |             | Min      | Тур | Max | Units | Conditions                                |

| Low level input voltage   | VIL    | All inputs  | -0.3     |     | 0.8 | ٧     |                                           |

| Low level input current   | l III. |             |          |     | 50  | μΑ    | $V_{IL} = 0V$                             |

| High level input voltage  | Vін    | i i         | 2.0      |     | Vcc | v     | •                                         |

| High level input current  | lıн    |             |          |     | 50  | μΑ    | $V_{IH} = 5V$                             |

| Low level output voltage  | Vol    | All outputs |          |     | 0.4 | V     | Isink = 2.0mA                             |

| High level output voltage | Von    |             | 2.8      |     | ŀ   | l v   | Isource = 2mA) both                       |

|                           |        |             | Vcc-0.75 |     |     | V     | Isource = 1mA) apply                      |

| Supply current            | lcc    |             |          | 2 . | 4   | mA    | All inputs to 0V All outputs open circuit |

#### **Dynamic Characteristics**

| Characteristic                                                       | Symbol              | Value |     |     | Units | Conditions                         |  |

|----------------------------------------------------------------------|---------------------|-------|-----|-----|-------|------------------------------------|--|

| Characteristic                                                       |                     | Min   | Тур | Max | Omis  | Continuous                         |  |

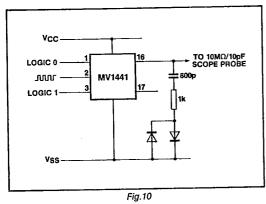

| Max. Clock (Encoder) frequency                                       | fmaxenc             | 4.0   | 10  |     | MHz   | Figs.10,15                         |  |

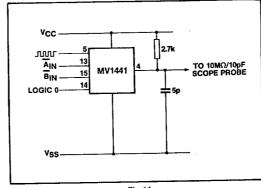

| Max. Clock (Decoder) frequency                                       | fmaxdec             | 2.2   | 5   |     | MHz   | Figs.11,15                         |  |

| Propagation Delay Clock (Encoder) to O <sub>1</sub> , O <sub>2</sub> | t <sub>pd1A/B</sub> |       |     | 100 | ns    | Figs.8,10,15 See Note 1            |  |

| Rise and Fall times O <sub>1</sub> , O <sub>2</sub>                  |                     | 1     |     | 20  | ns    | Figs.10,15                         |  |

| tpd1A - tpd1B difference                                             | 1                   | 1     |     | 20  | ns    | Figs.10,15                         |  |

| Propagation Delay Clock (Encoder) to Clock Regenerate                | t <sub>pd3</sub>    |       |     | 150 | ns    | Loop test enable = '1', Figs.10,15 |  |

| Setup time of NRZ data in to Clock (Encoder)                         | ts3                 | 75    |     |     | ns    | Figs.7,10,15                       |  |

| Hold time of NRZ data in                                             | ths                 | 55    |     |     | ns    | Figs.7,10,15                       |  |

| Propagation delay Ain, Bin to Clock<br>Regenerate                    | t <sub>pd2</sub>    |       |     | 150 | ns    | Loop test enable = '0' Figs.13,15  |  |

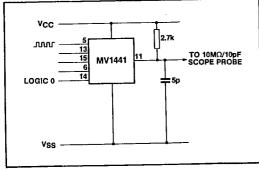

| Propagation delay Clock (Decoder) to error                           | t <sub>pd4</sub>    |       |     | 200 | ns    | Figs.12,15                         |  |

| Propagation delay Reset AIS falling edge to AIS output               | t <sub>pd5</sub>    |       |     | 200 | ns    | Loop test enable = '0', Figs.14,15 |  |

| Propagation delay Clock (Decoder) to<br>NRZ data out                 | t <sub>pd6</sub>    |       |     | 150 | ns    | Figs.7,11,15 See Note 2            |  |

| Setup time of Āin, Bin to Clock<br>(Decoder)                         | tsı                 | 75    |     |     | ns    | Figs.7,11,15                       |  |

| Hold time of Ain, Binto Clock (Decoder)                              | thi                 | 5     |     |     | ns    | Figs.7,11,15                       |  |

| Hold time of Reset AIS = '0'                                         | th2                 | 30    |     | l   | ns    | Figs.7,14,15                       |  |

| Setup time Clock (Decoder) to Reset AIS                              | ts2                 | 100   |     |     | ns    | Figs.7,14,15                       |  |

| Setup time Reset AIS = 1 to Clock (Decoder)                          | ts2                 | 0     | ,   |     | ns    | Figs.14,15                         |  |

| Propagation Delay Clock (Decoder)<br>to LIP                          |                     |       |     | 150 | ns    |                                    |  |

#### NOTES

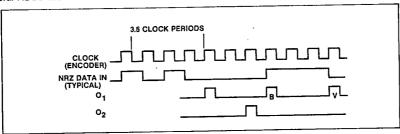

The Encoded ternary outputs (O1, O2) are delayed by 3.5 clock periods from NRZ Data In (Fig.3).

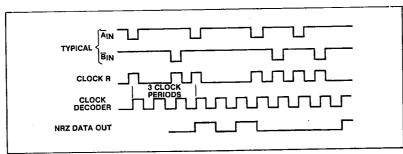

The decoded NRZ output is delayed by 3 clock periods from the HDB3 inputs (Ain, Bin) (Fig.4).

High Density Bipolar 3 (HDB3) is a pseudo-ternary signal in which the number of consecutive zeros that may occur is restricted to a maximum number of three. In any sequence of four consecutive binary zeros, the ultimate zero is substituted by a 'mark' (+ or -) of the same polarity as the previous mark, i.e. it violates AMI code (Alternate Mark Inversion) and is termed a 'violation'. To ensure parity between marks of opposite polarity, the first zero is substituted by an additional mark when there would otherwise be an even number of marks between 'violations'. Thus violations alternate in polarity.

#### PLESSEY SEMICONDUCTORS

#### **FUNCTIONAL DESCRIPTION**

#### Functions Listed by pin number

1. NRZ data in

Input data for encoding into ternary form. The data is clocked by the negative-going edge of the Clock (Encoder).

2. Clock (Encoder)

Clock for encoding data on pin 1.

3. LIP

Loss of input circuit detects eleven consecutive zeros at the decoder input and then gives an output high. Any logic '1' at the input (Ain or Bin = '0') resets this count.

4. NRZ data out

Decoded binary data from pseudo-ternary inputs AIN, BIN

5. Clock (Decoder)

Clock for decoding data on Ain and Bin, or O1 and O2 in loop test mode.

6,7. Reset AIS, AIS

Logic '0' on Reset AIS resets a decoded zero counter and either resets AIS output to '0' provided 3 or more zeros have been decoded in the preceding Reset AIS = 1 period, or sets AlS to '1' if less than 3 zeros have been decoded in the preceding Reset AlS = 1 period to indicate loss of time slot Zero. Logic '1' on Reset AlS enables the internal decoded zero counter.

Mode at logic '1' selects internal crystal controlled clock regeneration and Mode at logic '0' selects external clock regeneration using, for example, a tuned circuit.

9. Ground

Zero volts.

10. Crystal In

input to amplifier forming crystal oscillator when crystal is connected between pins 10 and 12. This pin may also be used as a 16.384MHz clock input if one oscillator is to be shared over several HDB3 encoders/decoders.

-75-11-29

11. Error

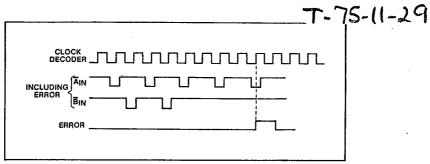

A logic '1' indicates that a violation of the HDB3 encoding law has been detected i.e. 3 '1's of the same polarity.

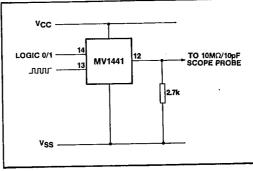

12. Clock R/Crystal Out

If pin 8 is at '0' pin 12 is Clock Regenerate, giving OR function of  $\overline{A}_{IN}$ ,  $\overline{B}_{IN}$  for clock regeneration when pin 14 = '0', OR function of O<sub>1</sub>, O<sub>2</sub> when pin 14 = '1'. If pin 8 is at '1' then pin 12 becomes Crystal Out and forms oscillator with pin 10. 13.15. Ain, Bin

Inputs representing the received ternary PCM signal.  $\overline{A}_{\text{IN}} =$ '0' represents a positive going '1',  $\overline{B}_{IN}$  = '0' represents a negative going '1',  $\overline{A}_{IN}$  and  $\overline{B}_{IN}$  are sampled by the positive going edge of the clock decoder. Ain and Bin may be interchanged.

14. Loop test enable

TTL input to select normal or loop back operation. Pin 14 = '0' selects normal operation, encode and decode are independent and asynchronous. When pin 14 = '1' O1, is connected internally to Ain and O₂ to Bin. Clock R becomes the OR function of O1, O2. N.B. A decode clock has to be supplied, or regenerated. The delay from NRZ in (pin 1) to NRZ out (pin 4) is about 71/2 clock periods in loop back. 16,17. O1, O2

Outputs representing the ternary encoded PCM HDB3 signal for line transmission. O1 and O2 are in Return to zero form and are clocked out on the positive going edge of the encode clock. The length of O1 and O2 pulses is set by the positive clock pulse length. Use suitable line drivers from these two outputs such that O 1 gives positive going pulse and Oz gives negative going pulse.

18. +Vcc

Positive 5V ± 10% supply.

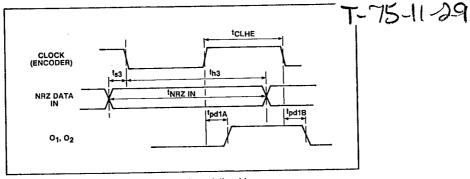

Fig.3 Encode waveforms

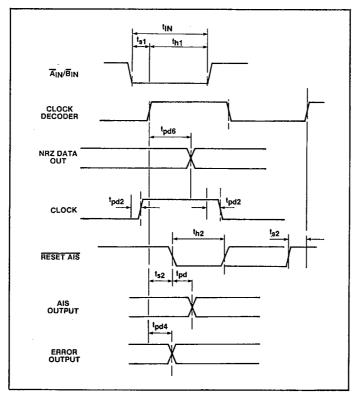

Fig.4 Decode waveforms

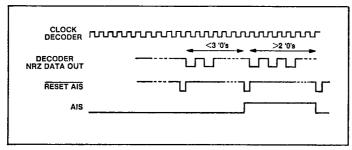

Fig.5 HDB3 error output waveforms

Fig.6 AIS error and Reset waveforms

Fig.7 Decoder timing relationship

Fig.8 Encoder timing relationship

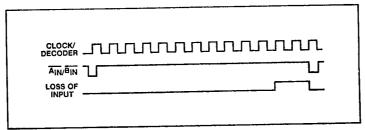

. Fig.9 Loss of input waveforms

Fig.11

Fig.12

Fig.13

53

Fig.14

Fig.15 Test timing definitions

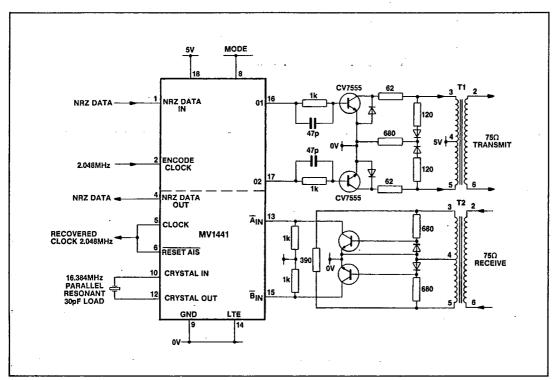

Fig.16 A typical application of the MV1441 with the interfacing to the transmission lines included