# Shock Sensor Signal Processor BU3892FV

The BU3892FV is an IC that processes the signals from shock sensors like those used in HDD and CD-ROM drives. This IC receives the faint signals output by shock sensors in response to vibration, and output a shock detection signal when they exceed a certain level.

ApplicationsHDD and CD-ROM drives

### Features

- 1) Single 5V power supply

- 2) Low-input bias current (CMOS)

- 3) Low power consumption mode

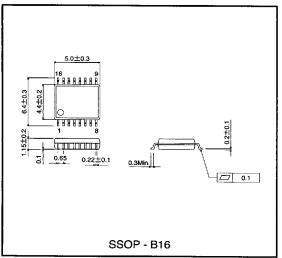

- 4) SSOP-B 16 pin package

### ●Absolute maximum ratings (Ta=25℃)

| Parameter            | Symbol | Limits         | Unit    |  |  |

|----------------------|--------|----------------|---------|--|--|

| Power supply voltage | Voo    | -0.3~7.0       | V<br>mW |  |  |

| Power dissipation    | PD     | 300*           |         |  |  |

| Storage temperature  | Тѕтс   | <b>−55~125</b> | c       |  |  |

| Input voltage        | Vin    | -0.3~Vpp+0.3   | ٧       |  |  |

| Output voltage Vout  |        | -0.3~Vpp+0.3   | ٧       |  |  |

<sup>\*</sup> Reduced by 3mW for each increase in Ta of 1°C over 25°C.

### ●Recommended operating conditions (Ta=25℃)

| Parameter                  | Symbol      | Limits      | Unit |  |

|----------------------------|-------------|-------------|------|--|

| Power supply voltage       | <b>V</b> DD | 4.5~5.5     | V    |  |

| Input voltage, LOW level   | VIL         | -0.3~1.5    | V    |  |

| lutput voltage, HIGH level | ViH         | 3.5~Vpp+0.3 | V    |  |

| Operating temperature      | Topr        | 0~70        | င    |  |

7828999 0021117 2T9 **=**

ROHM

443

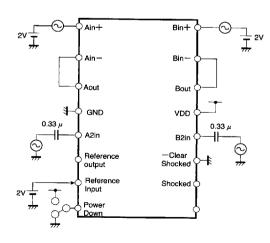

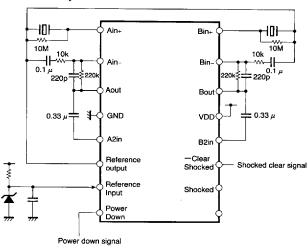

### Block diagram

### Pin descriptions

| Pin No. | Name             | Function                                                                                                                                             |  |  |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | Ain+             | Forward input of 1st stage operational amplifier A                                                                                                   |  |  |

| 2       | Ain-             | Reverse input of 1st stage operational amplifier A                                                                                                   |  |  |

| . 3     | Aout             | Output of 1st stage operational amplifier A                                                                                                          |  |  |

| 4       | GND              | Ground                                                                                                                                               |  |  |

| 5       | A2in             | Input of 2nd stage reversing amplifier                                                                                                               |  |  |

| 6       | Reference Output | Reference voltage output (typically 2 V)                                                                                                             |  |  |

| 7       | Reference Input  | Reference voltage input (typically 2 V)                                                                                                              |  |  |

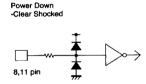

| 8       | Power Down       | Power-down signal input (The IC enters the power-down mode when the high-level signal is input)                                                      |  |  |

| 9       | N.C              | Not connected inside the IC.                                                                                                                         |  |  |

| 10      | Shocked          | Shock detection output. Outputs the high level when a shock is detected. (The high level is maintained until pin 11 input changes to the low level.) |  |  |

| 11      | —Clear Shocked   | Shocked clear input Shocked output is cleared when the level changes to low.                                                                         |  |  |

| 12      | B2in             | 2nd stage reversing amplifier input                                                                                                                  |  |  |

| 13      | Voo              | Power supply                                                                                                                                         |  |  |

| 14      | Bout             | 1st stage operational amplifier B output                                                                                                             |  |  |

| 15      | Bin-             | 1st stage operational amplifier B reverse input                                                                                                      |  |  |

| 16      | Bin+             | 1st stage operational amplifier B forward input                                                                                                      |  |  |

| 7828999 0021118 135 🖿

444

ROHM

# • Electrical characteristics (unless otherwise noted, $Ta=25^{\circ}C$ , $V_{DD}=4.5\sim5.5V$ )

| Parameter                      |                  | Symbo               | Min.  | Тур.  | Max.     | Unit                           | Conditions                                            | Measurement Circui |  |

|--------------------------------|------------------|---------------------|-------|-------|----------|--------------------------------|-------------------------------------------------------|--------------------|--|

| 1st STAGE                      | >                |                     |       |       |          |                                |                                                       |                    |  |

| input bias                     | Ta=25℃           | IIB <sub>1</sub> sτ | _     | 1     | 20       | pA                             | Measured at Ain+, Ain-, Bin+,<br>Bin- and GND*2       |                    |  |

|                                | Ta=75℃           |                     | _     |       | 2000     |                                |                                                       | Fig.1              |  |

| Maximum output current         |                  | IO <sub>1ST</sub>   | 0.5   |       | _        | mA                             |                                                       | Fig.1              |  |

| Supply voltage rejection ratio |                  | SVR1ST              | 65    | _     | _        | dB                             | *2                                                    | Fig.1              |  |

| Voltage gain l                 | bandwidth        | GB <sub>1ST</sub>   | _     | 1.4   | _        | MHz                            |                                                       | Fig.1              |  |

| High-amplitud                  | le voltage gain  | AV <sub>1ST</sub>   | 10    |       | _        | V/mV                           |                                                       | Fig.1              |  |

| (REFERENCE                     | CE INPUT)        |                     |       |       |          | L                              |                                                       | 1                  |  |

| Input current                  |                  | llref               | _     | _     | 10       | μА                             | Reference Input=2V                                    | Fig.1              |  |

| Output impedance               |                  | ROREF               | _     | _     | 30       | Ω                              | Reference Input=2V                                    | Fig.1              |  |

| ⟨2nd STAGE                     | )                |                     | ·     | ·     | <u> </u> |                                |                                                       |                    |  |

| Input current (A2in, B2in)     |                  | Iland               | -11   | -16   | -22      | μΑ                             | Reference Input=2V<br>A2in, B2in=1.8V                 | Fig.1              |  |

| Threshold vol<br>(A2in, B2in)  | tage, high level | DVH <sub>2nd</sub>  | +0.04 | +0.05 | +0.06    |                                | Reference Input=2V —Clear Shocked=0V                  |                    |  |

| Threshold voli<br>(A2in, B2in) | tage, low level  | DVH <sub>2nd</sub>  | -0.06 | -0.05 | -0.04    | V                              | Value relative to reference input                     | Fig.1              |  |

| <b>〈TOTAL〉</b>                 |                  |                     | L     |       |          |                                |                                                       |                    |  |

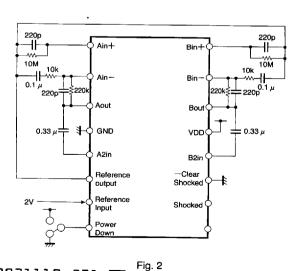

| Recovery time from power down  |                  | TROVRY              | _     | _     | 1        | mS                             | Time required for operation within specifications*2,3 | Fig.2              |  |

| Supply current                 | loo              | _                   | 4     | 6.5   | mA       | Input at power down low level  | Fig.1                                                 |                    |  |

| ——                             |                  | _                   | 15    | 100   | μA       | Input at power down high level | Fig.1                                                 |                    |  |

<sup>\*2</sup> Guaranteed performance

### Measurement circuit

Fig. 1

**■ 7828999 0021119 071**

ROHM

445

HDD shock sensor

מטח/מטני

<sup>\*3</sup> Shocked: The high level is output during transition in the power down low level.

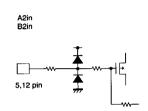

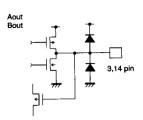

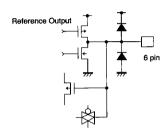

### Input/output circuits

### Circuit operation

Broadly speaking, the BU3892FV comprises 1st and 2nd stage operational amplifiers, which amplify the shock sensor signal; a comparator, which monitors the output level; and a latch circuit, which outputs and retains the shock detection signal.

(1) The 1st stage operational amplifier amplifies the shock sensor signal; gain and frequency characteristic can be set with external components. The 2nd stage operational amplifier also amplifies the shock sensor signal, but its gain is internally fixed at 20dB. The capacitor between the 1st and 2nd stage operational am-

plifier cuts the DC level to prevent adverse effects on the application device.

- (2) The comparator receives the signal from the 2nd stage operational amplifier and compares it to the comparator level, which depends on the DC level input from the reference input pin (the higher the DC level, the lower sensitivity becomes).

- (3) Signals detected by the comparator are latched by the latch circuit and output via the SHOCKED pin until reset input is received from the Clear Shocked pin.

**7828999 0021120 893**

# HDD shock sensor

## Operation notes

(1) Because the high impedance around the shock sensor makes it susceptible to noise (which can cause malfunctioning), design patterns carefully.

Fig. 3

# External dimensions (Units: mm)

7828999 0021121 72T **=**

ROHM