# (Dot Matrix Liquid Crystal Graphic **Display Common Driver**)

#### Description

The HD61103A is a common signal driver for dot matrix liquid crystal graphic display systems. It generates the timing signals (switch signal to convert LCD waveform to AC, frame synchronous signal) and supplies them to the column driver to control display. It provides 64 driver output lines and the impedance is low enough to drive a large screen.

As the HD61103A is produced by a CMOS process, it is fit for use in portable battery drive equipments utilizing the liquid crystal display's low power consumption. The user can easily construct a dot matrix liquid crystal graphic display system by combining the HD61103A and the column (segment) driver HD61102.

#### Features

- Dot matrix liquid crystal graphic display common driver with low impedance

- Low impedance: 1.5 kΩ max

- Internal liquid crystal display driver circuit: 64 circuits

- Internal dynamic display timing generator

- Selectable display duty ratio factor 1/48, 1/64, 1/96, 1/128

- Can be used as a column driver transferring data

- Low power dissipation: During display: 5 mW

- $V_{CC}$ : +5 V ± 10% Power supplies: V<sub>EE</sub>: 0 to -11.5 V

17.0 V max LCD driver level:

CMOS process

#### Ordering Information

| Type No. | Package                     |

|----------|-----------------------------|

| HD61103A | 100-pin plastic QFP(FP-100) |

# Absolute Maximum Ratings

| ltem                     | Symbol          | Limit                                          | Unit | Note |

|--------------------------|-----------------|------------------------------------------------|------|------|

| Power supply voltage (1) | v <sub>∞</sub>  | -0.3 to +7.0                                   | ٧    | 2    |

| Power supply voltage (2) | V <sub>EE</sub> | V <sub>CC</sub> -19.0 to V <sub>CC</sub> + 0.3 | ٧    | 5    |

| Terminal voltage (1)     | V <sub>T1</sub> | -0.3 to V <sub>CC</sub> + 0.3                  | ٧    | 2, 3 |

| Terminal voltage (2)     | V <sub>T2</sub> | $V_{EE} - 0.3$ to $V_{CC} + 0.3$               | ٧    | 4, 5 |

| Operating temperature    | Topr            | -20 to +75                                     | °C   |      |

| Storage temperature      | Tstg            | -55 to 125                                     | °C   |      |

Notes: 1.

- If LSIs are used beyond absolute maximum ratings, they may be permanently destroyed. We strongly recommend you to use the LSI within electrical characteristic limits for normal operation, because use beyond these conditions will cause malfunction and poor reliability.

- Based on GND = 0 V.

Applies to input terminals (except V1L, V1R, V2L, V2R, V5L, V5R, V6L, and V6R) and I/O

- Applies to V1L, V1R, V2L, V2R, V5L, V5R, V6L, and V6R.

- Apply the same value of voltages to V1L and V1R, V2L and V2R, V5L and V5R, V6L and V6R, V<sub>EE</sub> (23 pin) and V<sub>EE</sub> (58 pin) respectively. Maintain  $V_{CC} \ge V1L = V1R \ge V6L = V6R \ge V5L = V5R \ge V2L = V2R \ge V_{EF}$

**HITACHI**

556

4496204 0046352 666 📟

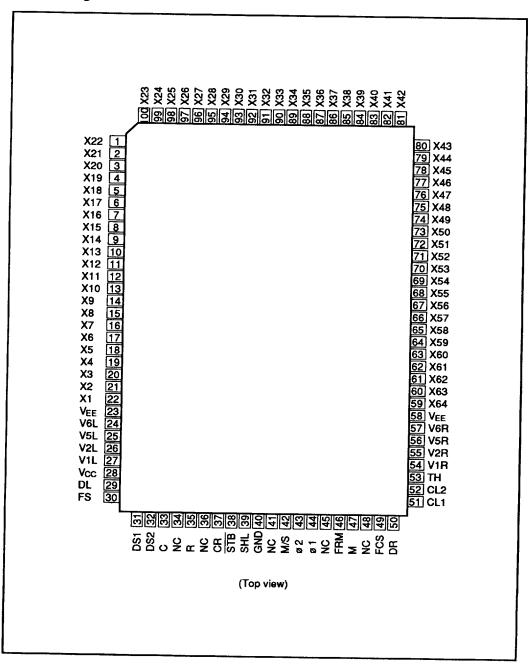

#### Pin Arrangement

#### HITACHI

■ 4496204 0046353 5T2 **■**

# Electrical Characteristics DC Characteristics ( $V_{CC}$ = +5 V ± 10%, GND = 0 V, $V_{EE}$ = 0 to -11.5 V, Ta = -20 to +75°C)

|                         |                  | Sp                    | eclfic | ations                | _    |                                                                     |       |

|-------------------------|------------------|-----------------------|--------|-----------------------|------|---------------------------------------------------------------------|-------|

| Test Item               | Symbol           | Min                   | Тур    | Max                   | Unit | Test Conditions                                                     | Note  |

| Input high voltage      | V <sub>IH</sub>  | 0.7 × VCC             |        | V <sub>CC</sub>       | ٧    |                                                                     | 1     |

| Input low voltage       | V <sub>IL</sub>  | GND                   | _      | 0.3 × V <sub>CC</sub> | ٧    |                                                                     | 1     |

| Output high voltage     | VoH              | V <sub>CC</sub> - 0.4 |        | _                     | ٧    | l <sub>OH</sub> = -0.4 mA                                           | 2     |

| Output low voltage      | VOL              |                       | -      | +0.4                  | ٧    | l <sub>OI</sub> = +0.4 mA                                           | 2     |

| Vi-Xj on resistance     | Pon              | _                     | _      | 1.5                   | kΩ   | V <sub>CC</sub> - V <sub>EE</sub> = 10 V<br>Load current<br>±150 μA | 3     |

| Input leakage current   | I <sub>IL1</sub> | -1.0                  |        | +1.0                  | μΑ   | Vin = 0 to V <sub>CC</sub>                                          | 4     |

| Input leakage current   | I <sub>IL2</sub> | -2.0                  | _      | +2.0                  | μA   | Vin = $V_{EE}$ to $V_{CC}$                                          | 5     |

| Operating frequency     | fopr1            | 50                    |        | 600                   | kHz  | In master mode<br>External clock<br>operation                       | 6     |

| Operating frequency     | fopr2            | 50                    |        | 1500                  | kHz  | In slave mode<br>Shift register                                     | 7     |

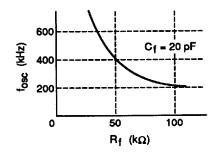

| Oscillation frequency   | fosc             | 315                   | 450    | 585                   | kHz  | Cf = 20 pF $\pm$ 5%<br>Rf = 47 k $\Omega$ $\pm$ 2%                  | 8, 13 |

| Dissipation current (1) | l <sub>GG1</sub> | -                     |        | 1.0                   | mA   | In master mode<br>1/128 duty cycle<br>Cf = 20 pF<br>Rf = 47 kΩ      | 9, 10 |

| Dissipation current (2) | I <sub>GG2</sub> | _                     |        | 200                   | μА   | In slave mode<br>1/128 duty cycle                                   | 9, 11 |

| Dissipation current     | lEE.             |                       | _      | 100                   | μА   | In master mode<br>1/128 duty cycle                                  | 9, 12 |

Notes: 1. Applies to input terminals FS, DS1, DS2, CR, STB, SHL, M/S, FCS, CL1, and TH and I/O common terminals DL, M, DR and CL2 in the input state.

- 2. Applies to output terminals, \$1, \$2, and FRM and I/O common terminals DL, M, DR, and CL2 in the output status.

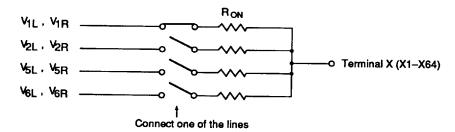

- Resistance value between terminal X (one of X1 to X64) and terminal V (one of V1L, V1R, V2L, V2R, V5L, V5R, V6L, and V6R) when load current is applied to each terminal X.

Equivalent circuit between terminal X and terminal V.

#### HITACHI

- Applies to input terminals FS, DS1, DS2, CR, STB, SHL, M/S, FCS, CL1, and TH, I/O common terminals DL, M, DR and CL2 in the input status and NC terminals.

- Applies to V1L, V1R, V2L, V2R, V5L, V5R, V6L, and V6R. Don't connect any lines to X1 to X64.

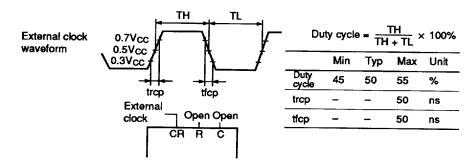

- 6. External clock is as follows

- 7. Applies to the shift register in the slave mode. For details, refer to AC Characteristics.

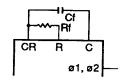

- Connect oscillation resistor (Rf) and oscillation capacitance (Cf) as shown in this figure.

Oscillation frequency (f<sub>OSC</sub>) is twice as much as the frequency (fφ) at φ1 or φ2.

Cf = 20 pF

Rf = 47 k

$$\Omega$$

fosc = 2 × fø

- No lines are connected to output terminals and current flowing through the input circuit is excluded. This value is specified at V<sub>IH</sub> = V<sub>CC</sub> and V<sub>IL</sub> = GND.

- 10. This value is specified for current flowing through GND in the following conditions: Internal oscillation circuit is used. Each terminal of DS1, DS2, FS, SHL, M/S, STB, and FCS is connected to V<sub>CC</sub> and each of CL1 and TH to GND. Oscillator is set as described in note 8.

- 11. This value is specified for current flowing through GND under the following conditions: Each terminals of DS1, DS2, FS, SHL, STB, FCS and CR is connected to V<sub>CC</sub>, CL1, TH, and M/S to GND and the terminals CL2, M, and DL are respectively connected to terminals CL2, M, and DL of the HD61103A under the conditions described in note 10.

#### HITACHI

559

**=** 4496204 0046355 **375 =**

- This value is specified for current flowing through V<sub>EE</sub> under the condition described in note

Don't connect any lines to terminal V.

- 13. This figure shows a typical relation among oscillation frequency, Rf and Cf. Oscillation frequency may vary with the mounting conditions.

# AC Characteristics ( $V_{CC}$ = +5 V $\pm$ 10%, GND = 0 V, $V_{EE}$ = 0 to -11.5 V, Ta = -20 to +75°C)

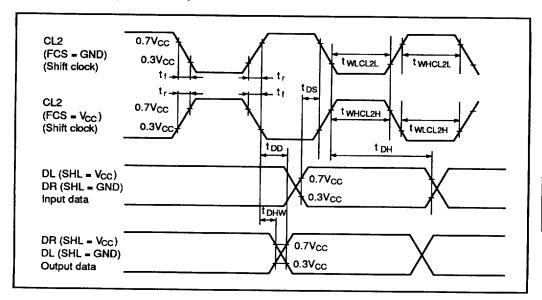

#### 1. Slave Mode (M/S = GND)

| Item                                          | Symbol           | Min | Тур | Max | Unit | Note |

|-----------------------------------------------|------------------|-----|-----|-----|------|------|

| CL2 low level width (FCS = GND)               | twlcl2L          | 450 | _   |     | ns   |      |

| CL2 high level width (FCS = GND)              | twHCL2L          | 150 |     |     | ns   |      |

| CL2 low level width (FCS = V <sub>CC</sub> )  | twlcl2H          | 150 |     |     | ns   |      |

| CL2 high level width (FCS = V <sub>CC</sub> ) | twhcl2H          | 450 | _   | _   | ns   |      |

| Data setup time                               | t <sub>DS</sub>  | 100 |     |     | ns   |      |

| Data hold time                                | t <sub>DH</sub>  | 100 |     |     | ns   |      |

| Data delay time                               | t <sub>DD</sub>  | _   |     | 200 | ns   | 1    |

| Data hold time                                | t <sub>DHW</sub> | 10  |     | _   | ns   |      |

| CL2 rise time                                 | tr               |     |     | 30  | ns   |      |

| CL2 fall time                                 | tf               |     | _   | 30  | ns   |      |

Note: 1. The following load circuit is connected for specification.

#### HITACHI ■ 4496204 0046357 148 ■

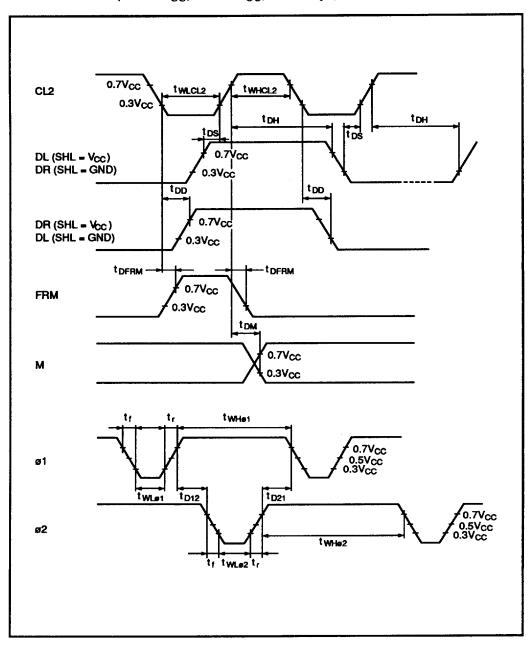

2. Master Mode (M/S =  $V_{CC}$ , FCS =  $V_{CC}$ , Cf = 20 pF, Rf = 47 k $\Omega$ )

562 **HITACHI**■ 4496204 0046358 084 ■

| Item                             | Symbol            | Min  | Тур          | Max | Unit | Note                                   |

|----------------------------------|-------------------|------|--------------|-----|------|----------------------------------------|

| Data setup time                  | tos               | 20   |              | _   | μs   |                                        |

| Data hold time                   | t <sub>DH</sub>   | 40   |              |     | μs   | ······································ |

| Data delay time                  | t <sub>DD</sub>   | 5    |              | _   | μs   |                                        |

| FRM delay time                   | t <sub>DFRM</sub> | -2   |              | +2  | μs   |                                        |

| M delay time                     | t <sub>DM</sub>   | -2   |              | +2  | μs   |                                        |

| CL <sub>2</sub> low level width  | twLCL2            | 35   | <del>-</del> |     | με   |                                        |

| CL <sub>2</sub> high level width | twHCL2            | 35   |              |     | μs   |                                        |

| ¢1 low level width               | tWL∳1             | 700  |              |     | ns   |                                        |

| 2 low level width                | tWL∳2             | 700  |              |     | ns   |                                        |

| 1 high level width               | tWH∳1             | 2100 | _            | _   | ns   |                                        |

| 2 high level width               | tWH∳2             | 2100 |              |     | ns   |                                        |

| 1- ¢2 phase difference           | t <sub>D12</sub>  | 700  | <del>-</del> |     | ns   |                                        |

| 2- ¢1 phase difference           | t <sub>D21</sub>  | 700  |              |     | ns   | ·                                      |

| 1, ¢2 rise time                  | tr                | _    |              | 150 | ns   |                                        |

| o1, ¢2 fali time                 | tf                |      |              | 150 | ns   |                                        |

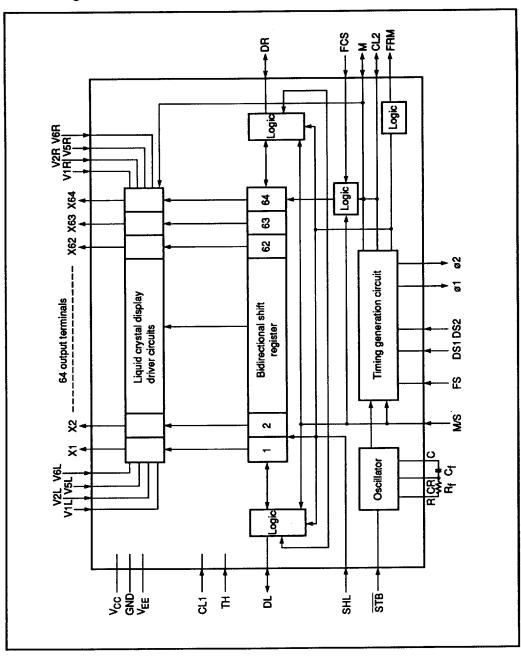

## **Block Diagram**

564 **HITACHI**■ 4496204 0046360 732 ■

#### **Block Functions**

#### Oscillator

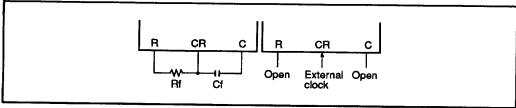

The CR oscillator generates display timing signals and operating clocks for the HD61102. It is required when the HD61103A is used with the HD61102. An oscillation resistor Rf and an oscillation capacitor Cf are attached as shown in figure 1 and terminal  $\overline{STB}$  is connected to the high level. When using an external clock, input the clock into terminal CR and don't connect any lines to terminal R and C.

Figure 1 Oscillator Connection with HD61102

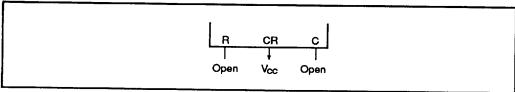

The oscillator is not required when the HD61103A is used with the HD61830. Connect terminal CR to the high level and don't connect any lines to terminals R and C (figure 2).

Figure 2 Oscillator Connection with HD61830

#### Timing Generator Circuit

The timing generator circuit generates display timing and operating clock for the HD61102. This circuit is required when the HD61103A is used with the HD61102. Connect terminal M/S to high level (master mode). It is not necessary when the display timing signal is supplied from other circuits, for example, from HD61830. In this case connect the terminals FS, DS1, and DS2 to high level and M/S to low level (slave mode).

#### Bidirectional Shift Register

A 64-bit bidirectional shift register. The data is shifted from DL to DR when SHL is at high level and from DR to DL when SHL is at low level. In this case, CL2 is used as shift clock. The lowest order bit of the bidirectional shift register, which is on the DL side, corresponds to X1 and the highest order bit on the DR side corresponds to X64.

HITACHI

565

■ 4496204 0046361 679 ■

#### Liquid Crystal Display Driver Circuit

The combination of the data from the shift register with the M signal allows one of the four liquid crystal display driver levels V1, V2, V5 and V6 to be transferred to the output terminals (table 1).

Table 1 Output Levels

| Data from the<br>Shift Register | M | Output Level |

|---------------------------------|---|--------------|

| 1                               | 1 | V2           |

| 0                               | 1 | V6           |

| 1                               | 0 | V1           |

| 0                               | 0 | V5           |

# **HD61103A Terminal Functions**

| Terminal<br>Name                   | Number of<br>Terminals | 1/0 | Connected<br>to        | Function                                                                                                                                                                                                                                                                   |

|------------------------------------|------------------------|-----|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vcc                                | 1                      |     | Power                  | V <sub>CC</sub> - GND: Power supply for internal logic.                                                                                                                                                                                                                    |

| OND<br>VEE                         | 1<br>2                 |     | supply                 | V <sub>CC</sub> - V <sub>EE</sub> : Power supply for driver circuit logic.                                                                                                                                                                                                 |

| V1L, V2L,                          | 8                      |     | Power                  | Liquid crystal display driver level power supply.                                                                                                                                                                                                                          |

| V5L, V6L,<br>V1R, V2R,<br>V5R, V6R |                        |     | supply                 | V1L (V1R), V2L (V2R): Selected level V5L (V5R), V6L (V6R): Non-selected level                                                                                                                                                                                              |

|                                    |                        |     |                        | Voltages of the level power supplies connected to V1L and V1R should be the same.                                                                                                                                                                                          |

| ···                                |                        |     |                        | (This applies to the combination of V2L & V2R, V5L & V5R and V6L & V6R respectively)                                                                                                                                                                                       |

| M/S                                | 1                      | 1   | V <sub>CC</sub> or GND | Selects master/slave.                                                                                                                                                                                                                                                      |

|                                    |                        |     |                        | M/S = V <sub>CC</sub> : Master mode                                                                                                                                                                                                                                        |

|                                    |                        |     |                        | When the HD61103A is used with the HD61102, timing generation circuit operates to supply display timing signals and operation clock to the HD61102. Each of I/O common terminals DL, DR, CL2, and M is in the output state.                                                |

|                                    |                        |     |                        | M/S = GND: Slave mode                                                                                                                                                                                                                                                      |

|                                    |                        |     |                        | The timing operation circuit stops operating. The HD61103A is used in this mode when combined with the HD61830. Even if combined with the HD61102, this mode is used when display timing signals (M, data, CL2, etc.) are supplied by another HD61103A in the master mode. |

|                                    |                        |     |                        | Terminals M and CL2 are in the input state.                                                                                                                                                                                                                                |

|                                    |                        |     |                        | When SHL is $V_{CC}$ , DL is in the input state and DR is in the output state.                                                                                                                                                                                             |

|                                    |                        |     |                        | When SHL is GND, DL is in the output state and DR is in the input state.                                                                                                                                                                                                   |

| FCS                                | 1                      | Į.  | V <sub>CC</sub> or GND | Selects shift clock phase.                                                                                                                                                                                                                                                 |

|                                    |                        |     |                        | FCS = V <sub>CC</sub> : Shift register operates at the rising edge of CL2. Select this condition when HD61103A is used with HD61102 or when MA of the HD61830 connects to CL2 in combination with the HD61830.                                                             |

|                                    |                        |     |                        | FCS = GND: Shift register operates at the fall of CL2. Select this condition when CL1 of HD61830 connects to CL2 in combination with the HD61830.                                                                                                                          |

HITACHI

## **HD61103A Terminal Functions (cont)**

| Terminal<br>Name | Number of<br>Terminals | 1/0 | Connected to           | Function                                                                                              |

|------------------|------------------------|-----|------------------------|-------------------------------------------------------------------------------------------------------|

| FS               | 1                      | ı   | V <sub>CC</sub> or GND | Selects frequency.                                                                                    |

|                  |                        |     |                        | When the frame frequency is 70 Hz, the oscillation frequency should be:                               |

|                  |                        |     |                        | fosc = 430 kHz at FCS = V <sub>CC</sub><br>fosc = 215 kHz at FCS = GND                                |

|                  |                        |     |                        | This terminal is active only in the master mode. Connect it to $V_{CC}$ in the slave mode.            |

| DS1, DS2         | 2                      | ı   | V <sub>CC</sub> or GND | Selects display duty factor.                                                                          |

| ·                |                        |     |                        | Display Duty Factor 1/48 1/64 1/96 1/128                                                              |

|                  |                        |     |                        | DS1 GND GND VCC VCC                                                                                   |

|                  |                        |     |                        | DS2 GND V <sub>CC</sub> GND V <sub>CC</sub>                                                           |

|                  |                        |     |                        | These terminals are valid only in the master mode. Connect them to V <sub>CC</sub> in the slave mode. |

| STB              | 1                      | 1   | V <sub>CC</sub> or GND | Input terminal for testing.                                                                           |

| TH               | 1                      |     |                        | Connect STB to V <sub>CC</sub> .                                                                      |

| CL1              | 1                      |     |                        | Connect TH and CL1 to GND.                                                                            |

| CR, R, C         | 3                      |     |                        | Oscillator.                                                                                           |

|                  |                        |     |                        | In the master mode, use these terminals as shown below.                                               |

|                  |                        |     |                        | Usage of these terminals in the master mode:                                                          |

|                  |                        |     |                        | Internal oscillation External clock                                                                   |

|                  |                        |     |                        | External                                                                                              |

|                  |                        |     |                        | Rf Cf Open Clock Open                                                                                 |

|                  |                        |     |                        |                                                                                                       |

|                  |                        |     |                        | R CR C   R CR C                                                                                       |

|                  |                        |     |                        | In the slave mode, stop the oscillator as shown below:                                                |

|                  |                        |     |                        |                                                                                                       |

|                  |                        |     |                        | Open Vcc Open                                                                                         |

|                  |                        |     |                        | R CR C                                                                                                |

| φ1, φ2           | 2                      | 0   | HD61102                | Operating clock output terminals for the HD61102.                                                     |

|                  |                        |     |                        | Master mode: Connect these terminals to terminals<br>\$1 and \$2 of the HD61102 respectively.         |

|                  |                        |     |                        | Slave mode: Don't connect any lines to these terminals.                                               |

**4**496204 0046364 388 **\*\*\***

# HD61103A Terminal Functions (cont)

| Terminal<br>Name | Number of<br>Terminals | i<br>1/0    | Connected<br>to                   |        | nction          |                                              |                         |                            |

|------------------|------------------------|-------------|-----------------------------------|--------|-----------------|----------------------------------------------|-------------------------|----------------------------|

| FRM              | 1                      | 0           | HD61102                           | Frai   | ne signal.      |                                              |                         |                            |

|                  |                        |             |                                   | K      | Aaster mode     | connect the                                  |                         | o terminal FRM             |

|                  |                        |             |                                   | S      | lave mode:      | Don't conn<br>terminal.                      | ect any line            | s to this                  |

| M                | 1                      | 1/0         | MB of                             | Sign   | al to conver    | t LCD driver                                 | signal into A           | iC.                        |

|                  |                        |             | HD61830 or<br>M of HD61102        | ā.     |                 | : Output terr                                | ninal<br>is terminal to | terminal M of              |

| •                |                        |             |                                   | S      | lave mode:      | Input termin<br>Connect this<br>of the HD61  | s terminal to           | terminal MB                |

| CL2              | 1                      | 1/0         | CL1 or MA                         | Shift  | clock.          |                                              |                         |                            |

|                  |                        |             | of HD61830<br>or CL of<br>HD61102 | М      | aster mode:     | Output term<br>Connect this<br>the HD6110    | s terminal to           | terminal CL of             |

|                  |                        |             |                                   | SI     | ave mode:       | Input termin<br>Connect this<br>or MA of the | s terminal to           | terminal CL1               |

| DL, DR           | 2                      | I/O         | Open or FLM                       | Data   | I/O termina     | ls of bidirecti                              | onal shift re           | gister.                    |

|                  |                        |             | of HD61830                        |        |                 | o X1's side a                                |                         |                            |

|                  |                        |             |                                   | Ma     | aster mode:     | Output com<br>Don't conne<br>terminals no    | ct any lines            | ng signal.<br>to these     |

|                  |                        |             |                                   | Sla    | ave mode:       | Connect terr<br>to DL (when<br>SHL = GND)    | $SHL = V_{CC})$         | the HD61830<br>or DR (when |

|                  |                        |             |                                   | M/S    | Vo              | cc                                           | GI                      | ND OIN                     |

|                  |                        |             |                                   | SHL    | V <sub>cc</sub> | GND                                          | Vcc                     | GND                        |

|                  |                        |             |                                   | DL     | Output          | Output                                       | Input                   | Output                     |

|                  |                        | <del></del> |                                   | DR     | Output          | Output                                       | Output                  | Input                      |

| NC               | 5                      |             | Open                              | Not us | sed.            |                                              |                         |                            |

| 01.11            |                        |             |                                   | Don't  | connect any     | lines to this                                | terminal.               |                            |

| SHL              | 1                      | ı           |                                   |        | s shift direc   | tion of bidire                               | ctional shift           | register.                  |

|                  |                        |             |                                   | SHL    | Shift Dire      | ction Com                                    | mon Scanni              | ng Direction               |

|                  |                        |             | -                                 | Vœ_    | DL→DR           | X1 →                                         | X64                     |                            |

|                  |                        |             |                                   | GND    | DL ← DR         | X1 ←                                         | X64                     |                            |

#### HITACHI

569

**4496204 0046365 214**

# HD61103A Terminal Functions (cont)

| Terminal<br>Name | Number of<br>Terminals | 1/0 | Connected to   | Function                                                                                                                                             |

|------------------|------------------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| X1-X64           | 64                     | 0   | Liquid crystal | Liquid crystal display driver output.                                                                                                                |

|                  |                        |     | display        | Output one of the four liquid crystal display driver levels V1, V2, V5, and V6 with the combination of the dat from the shift register and M signal. |

|                  |                        |     |                | M                                                                                                                                                    |

|                  |                        |     |                | Data1 0 1 0                                                                                                                                          |

|                  |                        |     |                | Output V2 V6 V1 V5                                                                                                                                   |

|                  |                        |     |                | Data 1: Selected level                                                                                                                               |

|                  |                        |     |                | 0: Non-selected level                                                                                                                                |

|                  |                        |     |                | When SHL is V <sub>CC</sub> , X1 corresponds to COM1 and X64 corresponds to COM64.                                                                   |

|                  |                        |     |                | When SHL is GND, X64 corresponds to COM1 and X1 corresponds to COM64.                                                                                |

# Example of Application

#### HD61103A Connection List

|    |     |            |     |           |     |            |          |    |                  | Ï       | H: V <sub>SS</sub>              |               | means "open".                                               |                       | Scilla | Rf: Oscillation resister           |                                    |                                                  |

|----|-----|------------|-----|-----------|-----|------------|----------|----|------------------|---------|---------------------------------|---------------|-------------------------------------------------------------|-----------------------|--------|------------------------------------|------------------------------------|--------------------------------------------------|

|    |     |            |     |           |     |            |          |    |                  | ت       | GND,                            | ,             |                                                             | 0 ;;                  | scilla | Cf: Oscillation capacitor          |                                    |                                                  |

| ı  | 378 | J/N/<br>HT | ု ၁ | ES<br>ECS |     | SSO<br>BTS | ATS      | СВ | .1               | 5       | <b>\$</b>                       | FRM           | Σ                                                           | CL2                   | SH     | 占                                  | 뚬                                  | X1-X64                                           |

| ⋖  | _   | <b>ب</b>   | _   | _         |     | I          | <b>=</b> | I  | i                | 1       | 1                               |               | from MB                                                     | from CL1              | Ŧ,     | from FLM<br>of<br>HD61830          | <br>  I<br>                        | COM1-COM64                                       |

|    | ĺ   | 1          |     |           | ſ   |            |          |    |                  |         |                                 |               | HD61830                                                     | HD61830               | _      | I                                  | from FLM<br>of<br>HD61830          | COM64-COM1                                       |

| 8  | _   | ب          | _   | I         | Ī   | I          | Ξ.       | I  | <br>             | !       | I                               | 1             | from MB                                                     | from MA               | ±      | from FLM<br>of<br>HD61830          | to DL/DR<br>of HD61103A<br>No. 2   | COM1-COM64                                       |

|    |     |            |     |           |     |            |          |    |                  |         |                                 |               | HD61830                                                     | HD61830               |        | to DL/DR of<br>HD61103A<br>No. 2   | from FLM<br>of<br>HD61830          | COM64-COM1                                       |

| ပ  | _   |            | _   | I         | I   | I<br>I     | I        | I  |                  | !       | 1                               | ı             | from MB                                                     | from MA               | E      | from DL/DR of<br>HD61103A<br>No. 1 |                                    | COM65-COM128                                     |

|    |     |            |     |           | ĺ   |            |          |    |                  |         |                                 |               | HD61830                                                     | HD61830               |        | 1                                  | from DL/DR<br>of HD61103A<br>No. 1 | from DL/DR COM128-COM65 of HD61103A COM128-COM65 |

| ۵  | I   | _          | _   | I         | · I | ᆿᅗ         | I        |    | ਹੱ<br>ਤੋਂ<br>ਤੋਂ |         | to<br>of<br>of                  | to FRM<br>of  | ð<br>M jo                                                   | 1<br>1<br>1<br>1<br>1 | r      | 1                                  | 1                                  | COM1-COM64                                       |

|    |     |            |     |           | İ   | 5          | }        | ರ  | }                | HD6110  | HD61102 HD61102 HD61102 HD61102 | : HD61102     | : HD61102                                                   | HD61102               | ر      | I                                  | ı                                  | COM64-COM1                                       |

| ш  | I   | _          | _   | Ī         | I   | ᇰᆫ         | I        | 莅  | Ċ<br>₹           |         | to <del>¢</del> 2<br>of         | to FRIM<br>of | Mot                                                         | to CL of<br>HD61102   | I      |                                    | to DL/DR<br>of HD61103A<br>No. 2   | COM1-COM64                                       |

| 1  | ĺ   |            |     | 1         |     | 3          |          | ច  |                  | HD6110, | 2 HD61102                       | HD61102       | HD61102 HD61102 HD61102 HD61102 to CL2 of HD61103A HD61103A | to CL2 of<br>HD61103A | ּ ב    | to DL/DR<br>of HD61103A<br>No. 2   | 1                                  | COM64-COM1                                       |

| ıL | _   | ب          | _   | I         | Ŧ   | I          | I        | I  | <br>             | 1       | I                               | 1             | from M                                                      | from CL2<br>of        | Ŧ      | from DL/DR<br>of HD61103A<br>No. 1 | l                                  | COM1-COM64                                       |

| 1  |     | İ          | - 1 | j         |     |            |          |    | į                |         |                                 |               | HD61103A HD61103A<br>No. 1 No. 1                            | HD61103A<br>No. 1     | ر ا    |                                    | from DL/DR<br>of HD61103A<br>No. 1 | COM64-COM1                                       |

|    |     |            |     |           |     |            |          |    |                  |         |                                 |               |                                                             |                       |        |                                    |                                    |                                                  |

#### HITACHI

📭 4496204 0046367 097 **==**

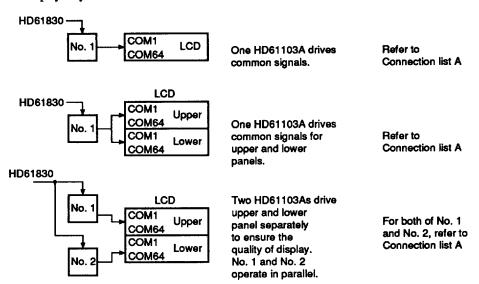

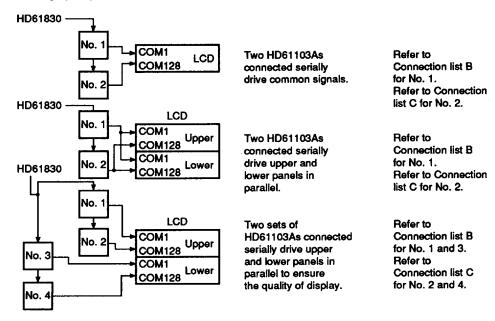

#### Outline of HD61103A System Configuration

- 1. Use with HD61830

- a. When display duty ratio of LCD is more than 1/64

b. When display duty ratio of LCD is from 1/65 to 1/128

HITACHI

■ 4496204 0046368 T23 **■■**

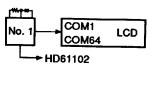

# 2. Use with HD61102 (1/64 duty ratio)

One HD61103A drives common signals and supplies timing signals to the HD61102s.

Refer to Connection list D

One HD61103A drives upper and lower panels and supplies timing signals to the HD61102s.

Refer to Connection list D

Two HD61103As drive upper and lower panels in parallel to ensure the quality of display.

No. 1 supplies timing signals to

No. 2 and the

HD61102s.

Refer to Connection list E for No. 1

Refer to Connection list F for No. 2

HITACHI

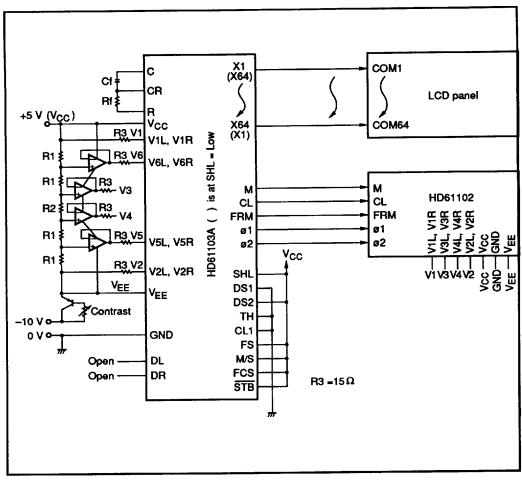

#### Connection Example 1

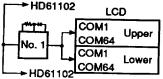

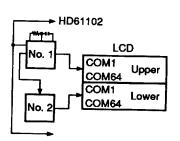

Use with HD61102 (RAM type segment driver).

a. 1/64 duty ratio (See Connection List D)

Figure 1 Example 1

Note: 1. The values of R1 and R2 vary with the LCD panel used.

When bias factor is 1/9, the values of R1 and R2 should satisfy

$$\frac{R1}{4R1 + R2} = \frac{1}{9}$$

For example,

$$R1 = 3 k\Omega$$

,  $R2 = 15 k\Omega$

HITACHI

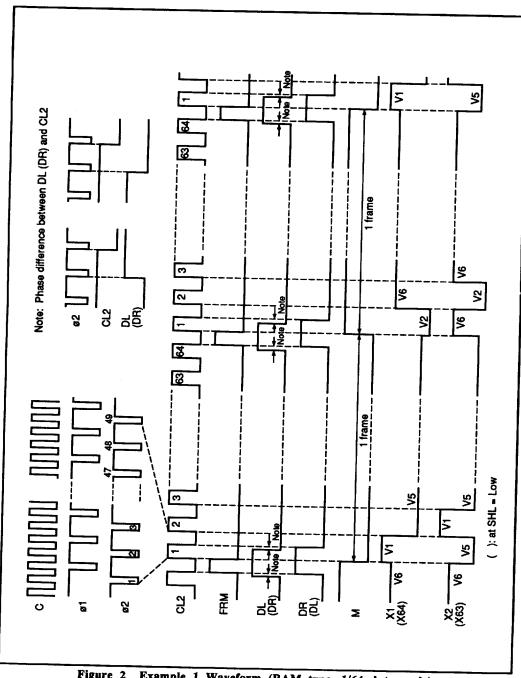

Figure 2 Example 1 Waveform (RAM type, 1/64 duty cycle)

**HITACHI** 575 4496204 0046371 518 📼

576

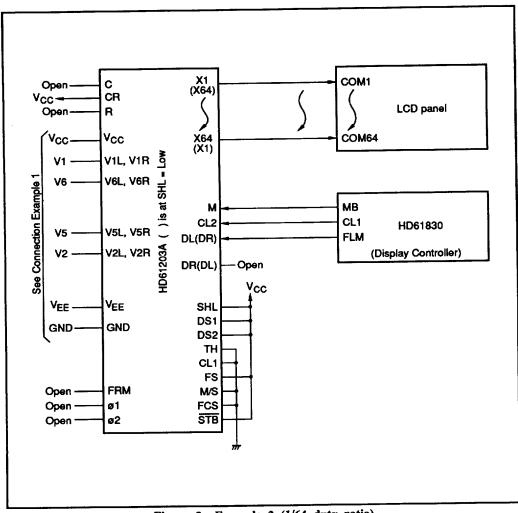

#### Connection Example 2

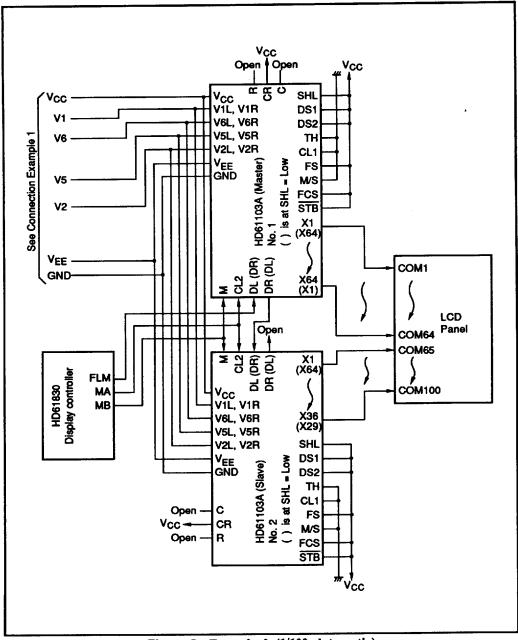

Use with HD61830 (Display controller).

a. 1/64 duty ratio (See Connection list A)

Figure 3 Example 2 (1/64 duty ratio)

HITACHI ■ 4496204 0046372 454 ■

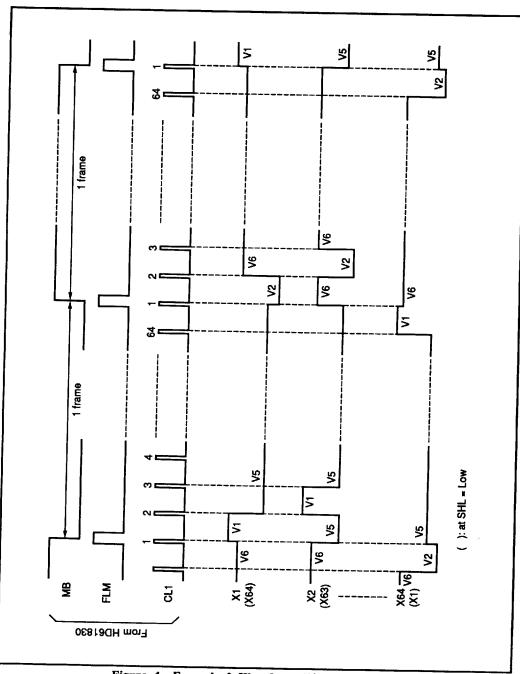

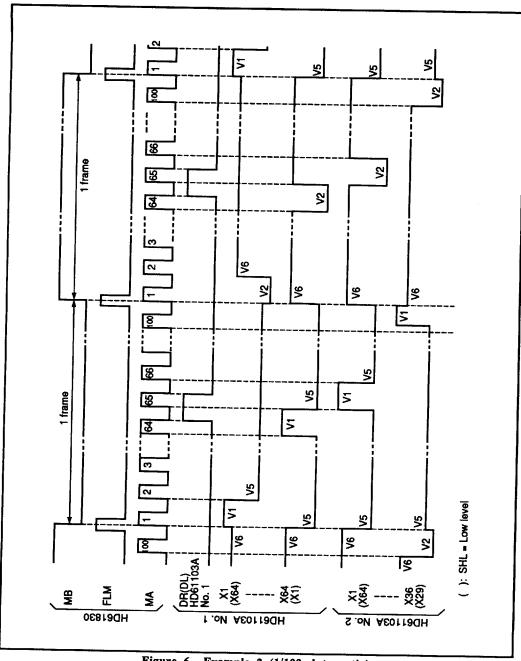

Figure 4 Example 2 Waveform (1/64 duty ratio)

HITACHI

4496204 0046373 390 🖿

#### b. 1/100 duty ratio (See Connection list B, C)

Figure 5 Example 2 (1/100 duty ratio)

*578* **HITACHI**■ 4496204 0046374 227 ■

Figure 6 Example 2 (1/100 duty ratio)

HITACHI 579 4496204 0046375 163 📟