#### CMOS 4-BIT MICROCONTROLLER

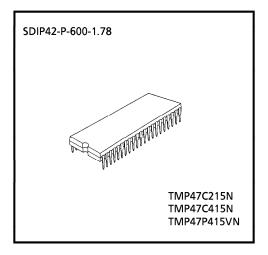

## TMP47C215N TMP47C415N

The 47C215/415 is a high speed and high performance 4-bit single chip microcomputer, integrating high current output port and the 4 bit A/D conversion input based on the TLCS-470 series.

| PART No.   | ROM          | RAM         | PACKAGE             | OTP              |

|------------|--------------|-------------|---------------------|------------------|

| TMP47C215N | 2048 × 8-bit | 128 × 4-bit | SDIP42-P-600-1.78   | TMP47P415VN      |

| TMP47C415N | 4096 × 8-bit | 256 × 4-bit | 3511 42-1 -000-1.70 | 11011 471 413010 |

#### **FEATURES**

- ◆4-bit single chip microcomputer

- ♦Instruction execution time: 1.0 µs (at 8 MHz),

244  $\mu$ s (at 32.8 kHz)

- ♦90 basic instructions

- Table look-up instructions

- 5-bit to 8-bit data conversion instruction

- ◆Subroutine nesting: 15 levels max.

- ◆5 interrupt sources (External: 1, Internal: 4)

All sources have independent latches each, and multiple interrupt control is available.

- ♦I/O port (36 pins)

- Input 1 ports 4 pins

Output 3 ports 12 pins

I/O 6 ports 20 pins

- ♦Interval Timer

- ◆Two 12-bit Timer / Counters

Timer, event counter, and pulse width measurement mode

- **♦**Watchdog Timer

- ◆Serial Interface with an 8-bit buffer

- Simultaneous transmission and reception capability

- External / internal clock, leading / trailing edge shift, and 4/8-bit mode

- ◆4-bit A/D conversion input 4 channels

- ◆High break down voltage outputs

VFT direct drive capability (23 bit)

◆High current outputs

LED direct drive capability (typ. 15 mA  $\times$  1 bits).

◆Dual-clock operation

High-speed / Low-power-consumption operating mode

♦ Hold function

Battery/Capacitor back-up

◆Real Time Emulator: BM47C415N0A

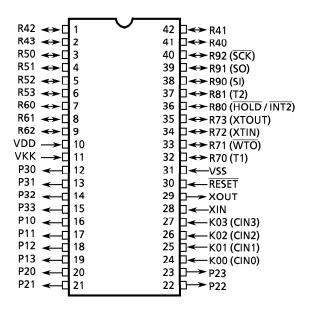

## **PIN ASSIGNMENTS (TOP VIEW)**

SDIP42-P-600-1.78

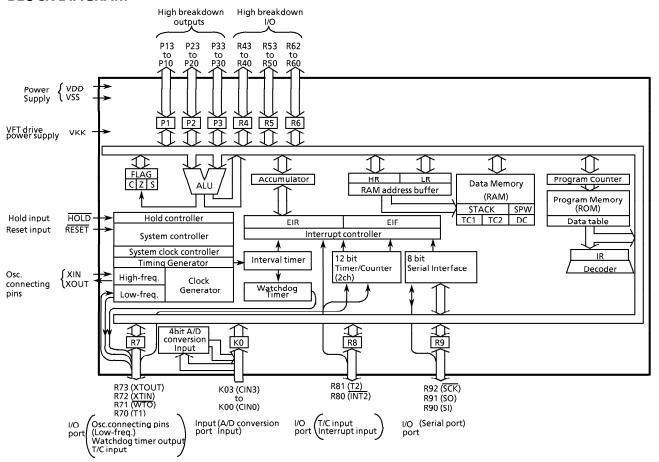

#### **BLOCK DIAGRAM**

# **PIN FUNCTION**

| PIN NAME                    | Input / Output | FUNCTION                                                                                                                                                   |                                                                          |  |  |

|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| K03 (CIN3)<br>to K00 (CIN0) | Input (Input)  | 4-bit input port                                                                                                                                           | A/D Conversion (comparator) Input                                        |  |  |

| P13 to P10 P23 to P20       | Output         | 4-bit high breakdown voltage output port with latch 8-bit data are output by t bit to 8-bit data conversion instruction [OUTB @ HL.]                       |                                                                          |  |  |

| P33 to P30                  | Output         | 4-bit high breakdown voltage output port wi                                                                                                                | ith latch                                                                |  |  |

| R43 to R40<br>R53 to R50    | I/O            | 4-bit high breakdown voltage I/O port with Ia                                                                                                              | atch                                                                     |  |  |

| R62 to R60                  |                | 3-bit high breakdown voltage I/O port with latch                                                                                                           |                                                                          |  |  |

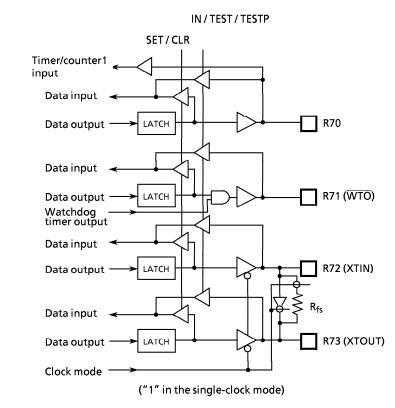

| R73 (XTOUT)                 | I/O (Output)   | 4-bit I/O port with latch.                                                                                                                                 | Resonator connecting pin (Low-freq.)                                     |  |  |

| R72 (XTIN)                  | I/O (Input)    | When using as the input port or watchdog timer output, the latch must be set to "1".                                                                       | For inputting external clock, XTIN is used and XTOUT is opend.           |  |  |

| R71 (WTO)                   | I/O (Output)   | Set to Dual-clock operating mode, when R73, R72 pin use as clock generator.                                                                                | Watchdog timer output                                                    |  |  |

| R70 (T1)                    | I/O (Input)    |                                                                                                                                                            | Timer / Counter 1 external input                                         |  |  |

| R81 (T2)                    | I/O (Input)    | 2-bit I/O port with latch. When used as the input port, external interrupt input pin, or timer / counter external input pin, the latch must be set to "1". | Timer / Counter 2 external input  External interrupt 2 or hold request / |  |  |

| R80 (INT2) / HOLD           | I/O (Input)    | external input pin, the latch must be set to "1".                                                                                                          | release signal input                                                     |  |  |

| R92 (SCK)                   | I/O (I/O)      | 3-bit I/O port with latch.                                                                                                                                 | Serial clock I/O                                                         |  |  |

| R91 (SO)                    | I/O (Output)   | When used as the input port or serial port,                                                                                                                | Serial data output                                                       |  |  |

| R90 (SI)                    | I/O (Input)    | the latch must be set to "1".                                                                                                                              | Serial data input                                                        |  |  |

| XIN                         | Input          | Resonator connecting pin (High-frequency).                                                                                                                 |                                                                          |  |  |

| хоит                        | Output         | For inputting external clock, XIN is used and XOUT is opened.                                                                                              |                                                                          |  |  |

| RESET                       | Input          | Reset signal input                                                                                                                                         |                                                                          |  |  |

| VDD                         |                | +5V                                                                                                                                                        |                                                                          |  |  |

| VSS                         | Power Supply   | 0 V (GND)                                                                                                                                                  |                                                                          |  |  |

| VKK                         |                | VFT drive power supply                                                                                                                                     |                                                                          |  |  |

#### **OPERATIONAL DESCRIPTION**

Concerning the 47C215/415 the configuration and functions of hardwares are described. As the description has been provided with priority on those parts differing from the 47C660/860, the technical data sheets for the 47C660/860 shall also be referred to.

#### 1. SYSTEM CONFIGURATION

#### **♦INTERNAL CPU FUNCTION**

They are the same as those of the 47C660/860 except program memory (ROM), data memory (RAM) system clock controller and interrupt function.

- **◆PERIPHERAL HARDWARE FUNCTION**

- ① Input / Output Ports

- 2 Interval Timer

- 3 Timer / Counters (TC1, TC2)

- Watchdog Timer

- **⑤** A/D Conversion (Comparator) input

- 6 Serial Interface

The description has been provide with priority on functions (1 and 5) added to and changed form 47C660/860.

#### 2. INTERNAL CPU FUNCTION

## 2.1 Program Memory (ROM)

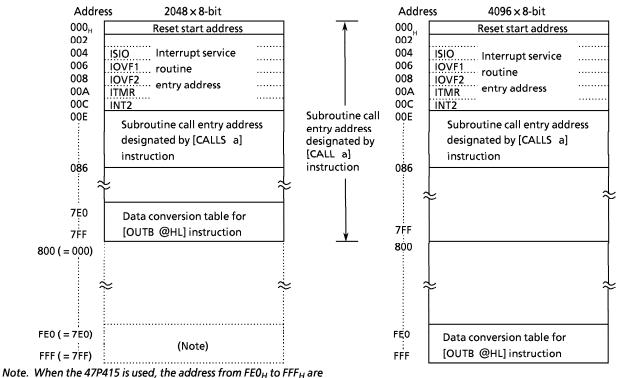

The 47C215 has 2048  $\times$  8 bits (addresses 000<sub>H</sub> through 7FF<sub>H</sub>) of program memory (mask ROM), the 47C415 has 4096  $\times$  8 bits (addresses 000<sub>H</sub> through FFF<sub>H</sub>).

Figure 2-1 shows the program memory map. Address  $000_{H}$  to  $086_{H}$  and  $FE0_{H}$  to  $FFF_{H}$  ( $000_{H}$  to  $086_{H}$  and  $7E0_{H}$  to  $7FF_{H}$  for the 47C215) of the program memory are also used for special purposes.

used as the data conversion table area.

(a) 47C215

(b) 47C415

Figure 2-1. Program Memory Map

On the 47C215, no physical program memory exists in the address range 800<sub>H</sub> through FFF<sub>H</sub>. However, if this space is accessed by program, the most significant bit of each address is always regarded as "0" and the contents of the program memory corresponding to the address 000<sub>H</sub> through 7FF<sub>H</sub> are read. For example, when outputting the data at address FF3<sub>H</sub> are read to ports by the [OUTB @HL] instruction, the data at address 7F3<sub>H</sub> is actually read. That is, on the 47C215, the conversion table is located in the address space 7E0<sub>H</sub> through 7FF<sub>H</sub>. When evaluating the 47C215 by using the 47P415. However, the conversion table must be allocated in the memory location addressed FE0<sub>H</sub> through FFF<sub>H</sub> also.

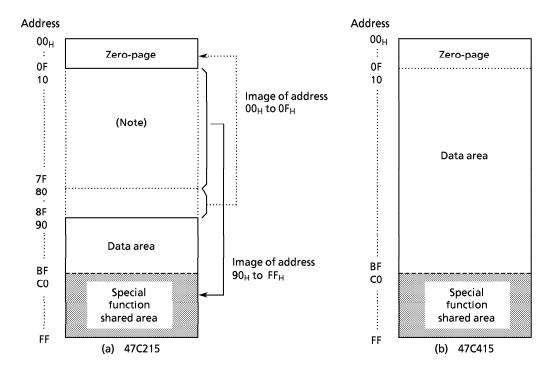

## 2.2 Data Memory (RAM)

The 47C415 has 256  $\times$  4 bits (addresses 00<sub>H</sub> through FF<sub>H</sub>) of the data memory (RAM), and the 47C215 has 128  $\times$  4 bits (addresses 00<sub>H</sub> through 0F<sub>H</sub>, and 90<sub>H</sub> through FF<sub>H</sub>).

Figure 2-2. Data Memory Capacity and Address Assignment

Note: With the 47C215, the most significant bit of the RAM address is always regarded as "0", so that addresses  $90_H$  to  $FF_H$  may be accessed as addresses  $10_H$  to  $7F_H$ . However, programming should be performed assuming that the RAM is assigned to addresses  $00_H$  to  $0F_H$  and  $90_H$  to  $FF_H$  as shown in Figure 2-2 by considering the application software evaluation with development tools.

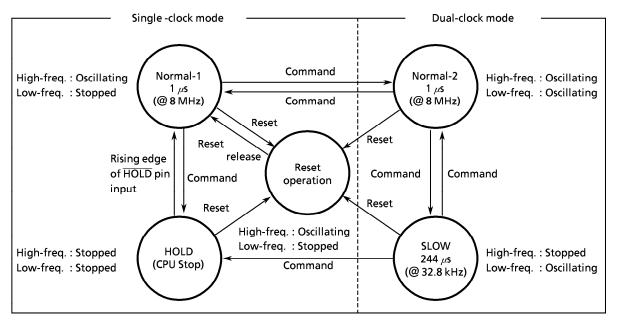

### 2.3 System Clock Controller

The system clock controller starts or stops the high-frequency and low-frequency clock oscillator and switches between the basic clocks. The operating mode is generally divided into the single-clock mode and the dual-clock mode, which are controlled by command. The 47C215/415 can swith from SLOW operation mode to HOLD operation mode.

After HOLD operation mode was released, Normal-1 operation mode is set.

Note. Normal-1 and Normal-2 operating modes are sometimes referred to as the Normal operating mode collectively.

Figure 2-3. Operating Mode Transition Diagram

Note. Returning from SLOW operation to Normal-2 operation

When returning from SLOW operation to Normal-2 operation, the warming up timer is used to change the operation frequency after getting stabilized oscillation of the low-frequency clock.

The watchdog timer counter is used to count the warming up time.

To count cerainly the warming up time, it is necessary to initialize the counter. When returning from SLOW operation to Normal-2 opertion, the watchdog timer must be cleared just before setting of the system clock control command register.

Example. Returning from SLOW operation to Normal-2 operation

| LD  | A,#0000B |

|-----|----------|

| OUT | A,%OP15  |

| LD  | A,#1100B |

| OUT | A,%OP16  |

#### 2.4 INTERRUPT FUNCTION

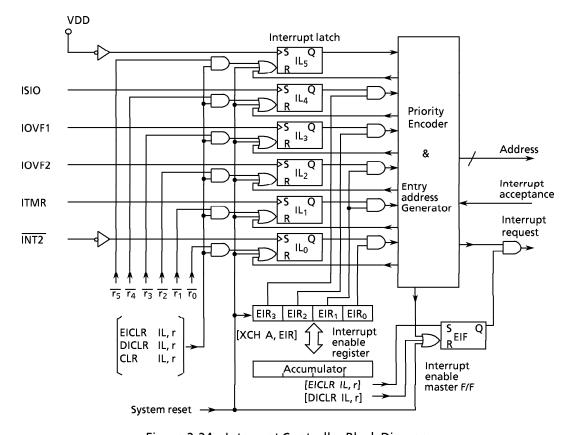

#### (1) Interrupt Controller

There are 5 interrupt sources (1 external and 4 internal).

The prioritized multiple interrupt capability is supported.

The interrupt latches (IL<sub>4</sub> through IL<sub>0</sub>) to hold interrupt requests are provided for the interrupt sources. Each interrupt latch is set to "1" when an interrupt request is made, asking the CPU to accept the interrupt. The acceptance of interrupt can be permitted or prohibited by program through the interrupt enable master flip-flop (EIF) and interrupt enable register (EIR). When two or more interrupts occur simultaneously, the one with the highest priority determined by hardware is serviced first.

|          | Sources                                      |         | Priority      | Interrupt<br>latch | Pertmit<br>conditions by<br>program | Entry<br>address  |

|----------|----------------------------------------------|---------|---------------|--------------------|-------------------------------------|-------------------|

|          | Serial interface interrupt                   | (ISIO)  | (High rank) 1 | IL <sub>4</sub>    | EIF = 1, EIR <sub>3</sub> = 1       | 0004 <sub>H</sub> |

|          | Timer / Counter 1 overflow interrupt (IOVF1) |         | 2             | IL <sub>3</sub>    | EIF = 1, EIR <sub>2</sub> = 1       | 0006 <sub>H</sub> |

| Internal | Timer / Counter 2 overflow interrupt         | (IOVF2) | 3             | IL <sub>2</sub>    |                                     | 0008 <sub>H</sub> |

|          | Interval timer interrupt                     | (ITMR)  | 4             | IL <sub>1</sub>    | EIF = 1, EIR <sub>1</sub> = 1       | 000A <sub>H</sub> |

| External | External interrupt 2                         | (INT2)  | (Low rank) 5  | IL <sub>0</sub>    | = 1, = 1K  = 1                      | 000C <sub>H</sub> |

Table 2-2. Interrupt Sources

Figure 2-24. Interrupt Controller Block Diagram

#### a. Interrupt enable master flip-flop (EIF)

The EIF controls the enable / disable of all interrupts. When this flip-flop is cleared to "0", all interrupts are disabled; when it is set to "1", the interrupts are enabled.

When an interrupt is accepted, the EIF is cleared to "0", temporarily disabling the acceptance of subsequent interrupts.

When the interrupt service program has been executed, the EIF is set to "1" by the execution of the interrupt return instruction [RETI], being put in the enabled state again.

Set or clear of the EIF in program is performed by instructions [EICLR IL,r] and [DICLR IL,r], respectively. The EIF is initialized to "0" during reset.

#### b. Interrupt enable register (EIR)

The EIR is a 4-bit register specifies the enable or disable of each interrupt except INT1. An interrupt is enabled when the corresponding bit of the EIR is "1", and an interrupt is disabled when the corresponding bit of the EIR is "0". Bit 1 (EIR<sub>1</sub>) of the EIR is shared by both IOVF2 and ITMR interrupts.

Read/write on the EIR is performed by executing [XCH A,EIR] instruction. The EIR is initialized to "0" during reset.

#### c. Interrupt latches (IL)

An interrupt latch is provided for each interrupt source. It is set to "1" when an interrupt request is made to ask the CPU for accepting the interrupt. Each latch is cleared to "0" upon acceptance of the interrupt. It is initialized to "0" during the reset.

The interrupt latches can be cleared independently by interrupt latch operation instructions ([EICLR IL,r], [DICLR IL,r], and [CLR IL,r] to make them cancel interrupt requests or initialize by program. When the value of instruction field(r) is "0", the interrupt latch is cleared; when the value is "1", the IL is held. Note that the interrupt latches cannot be set by instruction.

#### Example 1: To enable IOVF1 and INT2

```

LD A, #0101B ; EIR \leftarrow 0101_B XCH A, EIR EICLR IL, 111111B ; EIF \leftarrow 1

```

Example 2: To set the EIF to "1" and to clear the interrupt latches except ISIO to "0".

```

EICLR IL, 010000B; EIF\leftarrow1, IL<sub>5</sub>\leftarrow0, IL<sub>3</sub>-IL<sub>0</sub>\leftarrow0

```

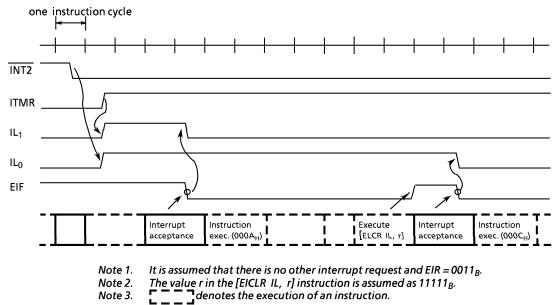

#### (2) Interrupt Processing

An interrupt request is held until the interrupt is accepted or the IL is cleared by reset or the interrupt latch operation instruction. The interrupt acknowledge processing is performed in 2 instruction cycles after the end of the current instruction execution (or after the timer/counter processing if any). The interrupt service program terminates upon execution of the interrupt return instruction [RETI]. The interrupt acknowledge processing consists of the following sequence:

- ① The contents of the program counter and the flags are saved on the stack.

- ② The interrupt entry address corresponding to the interrupt source is set to the program counter.

- 3 The status flag is set to "1".

- The EIF is cleared to "0", temporarily disabling the acceptance of subsequent interrupts.

- ⑤ The IL for the accepted interrupt source is cleared to "0".

- © The instruction stored at the interrupt entry address is executed. (Generally, in the program memory space at the interrupt entry address, the branch instruction to each interrupt processing program is stored. Note that the interrupt entry address is assigned every 2-byte, so that the long branch instruction can not be stored in the program normally. The interrupt service program is assigned to the memory locations 0000H through 0FFFH.)

To perform the multi-interrupt, EIF is set to "1" in the interrupt service program, and the acceptable interrupt source is selected by the EIR.

Figure 2-25. Interrupt Timing Chart (Example)

The interrupt return instruction [RETI] performs the following operations:

- ① Restores the contents of the program counter and the flags from the stack.

- ② Sets the EIF to "1" to provide the interrupt enable state again.

Note. When the time required for the interrupt service is longer than that for the interrupt request, only the interrupt service program is executed without executing the main program.

In the interrupt processing, the program counter and flags are automatically saved or restored but the accumulator and other registers (H or L register, DMB, DC, etc.) are not. If it is necessary to save or restore them, it must be performed by program as shown in the following example. To perform the multi-interrupt, the saving RAM area never be overlapped.

```

Example 1: To save/restore accumlator and HL register pair.

```

XCH HL, GSAV1; RAM[GSAV1] ↔ HL XCH A, GSAV1+2; RAM[GSAV1+2] ↔ Acc Note. The lower 2 bits of GSAV1 should be "0's".

#### (3) External Interrupt

When an external interrupt (INT2) occurs, the interrupt latch is set at the falling edge of the corresponding pin input (INT2).

The INT2 interrupt can be enabled / disabled by the EIR.

Therefore, the INT2 interrupt occurs at the falling edge of the pin input when R80 (INT2) pin is used for the I/O port.

But bit 0 of the EIR is only kept at "0" not accepting the interrupt request.

Because the external interrupt input is the hysteresis type, each of high and low level operation requires 2 or more instruction cycles for a correct interrupt operation.

#### 3. PERIPHERAL HARDWARE FUNCTION

## 3.1 Input / Ouput Ports

The 47C215/415 has 10 I/O ports (36 pins) each as follows:

K0 ; 4-bit input (shared with comparator inputs)

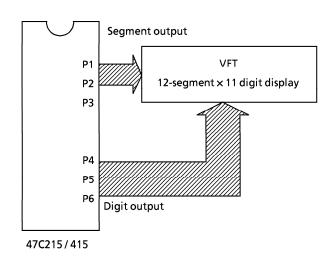

P1, P2, P3 ; 4-bit output (shared with segment autputs)

R4, R5 ; 4-bit input / output (shared with digit outputs)

R6 ; 3-bit input / output (shared with digit outputs)

© R7 ; 4-bit input / output (shared with the low-frequency reasonator

connecting pins, the watchdog timer output and timer/counter

input)

© R8 ; 2-bit input / output (shared with external interrupt request input

and timer / counter input)

7 R9; 3-bit input / output(shared with serial port)

Each output port contains a latch, which holds the output data. The input ports have no latch; therefore, it is desired hold data exterenally until it is read or to read twice or more before processing it.

| Port            |                                         | Port                             |                 |                        |                         | Input/(    | Input/Output instruction | tion                   |                           |                             |

|-----------------|-----------------------------------------|----------------------------------|-----------------|------------------------|-------------------------|------------|--------------------------|------------------------|---------------------------|-----------------------------|

| Address (**)    | Input (IP**)                            | Output                           | (OP**)          | IN %p, A<br>IN %p, @HL | OUT A, %p<br>OUT @HL,%p | OUT #k, %p | оотв @нг                 | SET %p, b<br>CLR %p, b | TEST %p, b<br>TESTP %p, b | SET @L<br>CLR @L<br>TEST @L |

| H00             | K0 input port<br>(A/D conversion input) | P0 output port                   | (Note 2)        | 0                      | 0                       | 0          | l                        | I                      | 0                         | I                           |

| 10              | P1 output latch                         | P1 output port                   |                 | 0                      | 0                       | 0          | 0                        | 0                      | 0                         | ı                           |

| 05              | P2 output latch                         | P2 output port                   |                 | 0                      | 0                       | 0          | (INOLE 3)                | 0                      | 0                         | ı                           |

| 03              | P3 output latch                         | P3 output port                   |                 | 0                      | 0                       | 0          | ı                        | 0                      | 0                         | 1                           |

| 9 6<br>4 1      | R4 input port                           | R4 output port                   |                 | 00                     | 0(                      | 0(         | ı                        | 00                     | 0(                        | 00                          |

| ა<br>ა          | R5 input port                           | R5 output port                   |                 | )(                     | )(                      | )(         | ı                        | )(                     | )(                        | )(                          |

| 90 2            | R6 input port                           | R6 output port                   |                 | )(                     | ЭС                      | )(         | I                        | )(                     | )(                        | )(                          |

| ) &             | R8 input port                           | R8 output port                   |                 | C                      | ЭС                      | C          | 1 1                      | ) C                    | C                         | ) ו                         |

| 60              | R9 input port                           | R9 output port                   |                 | 0                      | ) ()                    | ) ()       | ı                        | )()                    | ) ()                      | ı                           |

| 6               |                                         |                                  |                 | ı                      | ı                       | ı          | ı                        | ı                      | ı                         | I                           |

| 08              | I                                       |                                  |                 | I                      | ı                       | ı          | ı                        | ı                      | I                         | ı                           |

| 2               |                                         |                                  |                 | ı                      | ı                       | I          | ı                        | ı                      | ı                         | ı                           |

| 9               |                                         |                                  |                 | ı                      | ı                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 90              | Status input (Note 4)                   |                                  |                 | 0                      | I                       | ı          | ı                        | ı                      | 0                         | ı                           |

| 0F              | Serial receive buffer                   | Serial transmit buffer           | uffer           | 0                      | 0                       | 0          | 1                        | _                      | 1                         | _                           |

| 10 <sub>H</sub> | Undefined                               | Hold operating mode control      | mode control    | ı                      | 0                       | _          | ı                        | 1                      | ı                         | 1                           |

| 7               | Undefined                               |                                  |                 | 1                      | ſ                       | I          | ı                        | ı                      | ı                         | 1                           |

| 12              | Undefined                               | A/D conversion input control     | nput control    | I                      | 0                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 13              | SK0 status                              | K0 port input selector           | lector          | 0                      | 0                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 14              | Undefined                               |                                  |                 | I                      | ı                       | ı          | ı                        | ı                      | ı                         | 1                           |

| 15              | Undefined                               | Watchdog timer control           | control         | I                      | 0                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 16              | Undefined                               | System clock control             | ıtrol           | ı                      | 0                       | 1          | 1                        | ı                      | ı                         | I                           |

| 17              | Undefined                               |                                  |                 | ı                      | ı                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 8               | Undefined                               |                                  |                 | ı                      | ı                       | ı          | ı                        | ı                      | ı                         | I                           |

| 19              | Undefined                               | Interval timer interrupt control | terrupt control | ı                      | 0                       | ı          | ı                        | ı                      | I                         | 1                           |

| 4               | Undefined                               |                                  |                 | I                      | Ì                       | ı          | ı                        | 1                      | ı                         | ı                           |

| 18              | Undefined                               |                                  |                 | ı                      | ı                       | ı          | 1                        | I                      | ı                         | ı                           |

| 7               | Undefined                               | Timer/counter 1                  | er 1 control    | ı                      | 0                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 5               | Undefined                               | Timer/counter 2                  | er 2 control    | Ī                      | 0                       | ı          | ı                        | ı                      | ı                         | ı                           |

| 1               | Undefined                               | Serial interface control 1       | control 1       | ı                      | 0                       | 1          | ı                        | 1                      | ſ                         | ı                           |

| 4               | Undefined                               | Serial interface control         | control 2       | 1                      | 0                       | ı          | 1.                       | 1                      | ı                         | 1                           |

Note 2 As concerns the port address "00". In and TEST instructions operate port K0, and out instruction operates port P0. Note 3 The 5-bit to 8-bit data conversion instruction [OUTB @ HL], automatic access to ports P1 and P2. Note 4 The status input of serial interface, clock generator, and  $\overline{\text{HOLD}}$  ( $\overline{\text{KE0}}$ ) pin. Note 1 "---"means the reserved state. Unavailable for the user programs.

Table 3-1. Port Address Assignments and Available I/O Instructions

## 3.1.1 I/O port

## (1) K0 (K03 to K00) PORT

The 4-bit input port. Port K0 is shared with the A/D converter (comparator) input. The K0 port input selector (OP13) determines whether this port is to be used for digital or comparator input. The most significant bit of the K0 port input selector is set to "1" for digital input and to "0" for comparator input. The K0 port input selector is initialized to "0" during reset.

## (2) P1 (P13 to P10), P2 (P23 to P20), P3 (P33 to P30) port

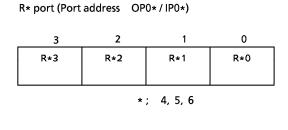

The 4-bit high breakdown voltage output ports with latch, which can directly drive Vacuum Fluorescent Tubes (VFT). The latch data can be read by input instruction. The latch is initialized to "0" during reset.

P\* port (Port address OP0\* / IP0\*)

Figure 3-2. Ports P1, P2, P3

Figure 3-3. Example of driving a VFT

(3) Ports R4 (R43 to R40), R5 (R53 to R50), R6 (R62 to R60), R7 (R73 to R70)

These ports are 4-bit I/O ports with a latch. When used as an input port, the latch (R4, R5 and R6) must be set to "0" and the latch (R7) must be set to "1". The latch (R4, R5 and R6) is initialized to "0" during reset. The R7 latch is initialized to "1" during Reset. These 4 ports (16 pins) can be set, cleared, and tested for each bit as specified by L register indirect addressing bit manipulation instructions [SET @L], [CLR @L], and [TEST @L]. Table 3-2 lists the pins (I/O ports) that correspond to the L register contents.

Example: To clear R43 pin as specified by the L register indirect addressing bit manipulation instruction.

LD L, #0011B; Set R43 pin address to L register

CLR @L ; R43←0

|   | L reg | iste | r | Pin  |

|---|-------|------|---|------|

| 3 | 2     | 1    | 0 | FIII |

| 0 | 0     | 0    | 0 | R40  |

| 0 | 0     | 0    | 1 | R41  |

| 0 | 0     | 1    | 0 | R42  |

| 0 | 0     | 1    | 1 | R43  |

|   | Lreg | jiste | r | Pin  |

|---|------|-------|---|------|

| 3 | 2    | 1     | 0 | PIII |

| 0 | 1    | 0     | 0 | R50  |

| 0 | 1    | 0     | 1 | R51  |

| 0 | 1    | 1     | 0 | R52  |

| 0 | 1    | 1     | 1 | R53  |

|   | Lreg | Pin |   |      |

|---|------|-----|---|------|

| 3 | 2    | 1   | 0 | PIII |

| 1 | 0    | 0   | 0 | R60  |

| 1 | 0    | 0   | 1 | R61  |

| 1 | 0    | 1   | 0 | R62  |

| 1 | 0    | 1   | 1 | -    |

|   | Lreg | jiste | Pin |      |

|---|------|-------|-----|------|

| 3 | 2    | 1     | 0   | FIII |

| 1 | 1    | 0     | 0   | R70  |

| 1 | 1    | 0     | 1   | R71  |

| 1 | 1    | 1     | 0   | R72  |

| 1 | 1    | 1     | 1   | R73  |

Table 3-2. Relationship between L register contents and I/O port bits

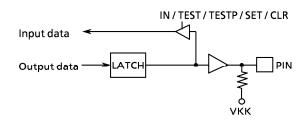

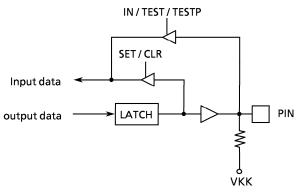

a. R4 (R43 to R40), R5 (R53 to R50), R6 (R62 to R60) port

The 4-bit high breakdown voltage I/O ports with latch, which can directly drive Vacuum Fluorescent Tubes (VFT). The latch should be cleared to "0" when used as an input port. The is initialized to "0" during reset.

Figure 3-4. R4, R5, R6 port

※ VFT drive power supply (VKK)

The 23 pins of the P1, P2, P3, R4, R5, R6 ports are P-channel open drain construction with pulldown resistor. Each pin is connected to a VKK pin via a pulldown resistor (TYP. 80 k $\Omega$ ). Thus, Vacuum Fluorescent Tubes (VFT) can be driven by applying a negative ( – ) voltage to the VKK pin, without using external resistor.

b. Port R7 is shared by the low-frequency resonator connection pins (XTIN, XTOUT), the timer / counter1 input pin and the watchdog timer output pin (WTO). For the dual-clock mode operation, the low-frequency resonator(32.768 kHz) is connected to R72 (XTIN) and R73 (XTOUT) pins. For the single-clock mode operation, R72 and R73 pins are used for the ordinary I/O ports. When the watchdog timer is used, R71 (WTO) becomes the watchdog timer output pin. The watchdog timer output is the logical AND output with the port R71 output latch. To use the R71 pin for an ordinary I/O port, the watchdog timer must be disabled (with the watchdog timer output set to "1"). When used as a timer / counter1, R70 lactch must be set to "1". To use it for an ordinary I/O port, the event counter / pulse width measurement modes of the timer / counter1 must be disabled.

Port R7 (Port address OP07 / IP07)

|   | 3       | 2      | 1     | 0    |

|---|---------|--------|-------|------|

| İ | R73     | R72    | R71   | R70  |

|   | (XTOUT) | (XTIN) | (WTO) | (T1) |

Figure 3-5. Port R7

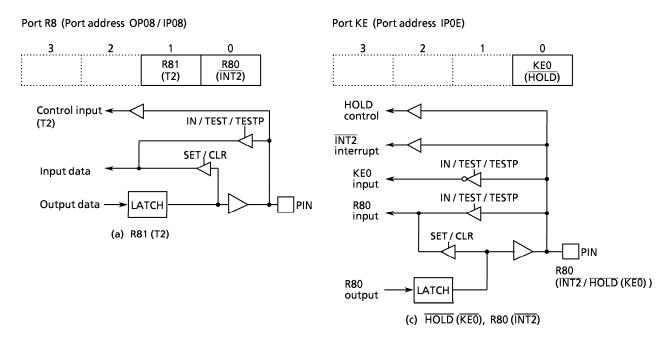

- (4) PORT R8 (R80 to R81) and HOLD / (INT2) pin

- a. R80 (INT2 / HOLD (KE0))

Port KE (KE0) is a 1bit sense input port shared with the hold request/release signal input pin (HOLD), the external interrupt 2 input pin and the R80 I/O pin. This input port (KE0) is assigned to the least significant bit of port address IP0E and is processed as the data with inverted polality. For example, if an input instruction is executed with the pin on the high level, "0" is read. The bit1 through bit3 of port KE, an uncertain value is read when an input instruction is executed.

#### b. R81

Port R81 is a I/O port with a latch. When used as input port, the latch must be set to "1". The latch is initializes to "1" during reset. Port R81 is shared with the timer / counter2 input pin. To use this port for the timer / counter2 input pin, the latch should be set to "1". To use it for an ordinaly I/O port, the event countre / pulese width measurement modes of the timer/counter should be disabled.

Figure 3-6. Port R8 and port KE

Note: When HOLD (INT2) pin is used for an I/O port, external interrupt 2 occurs upon detection of the falling edge of pin input therefore a bit 0 of the interrupt enable resister (EIR0) should be clear to "0".

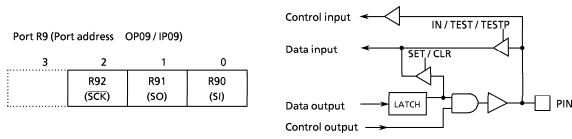

#### (5) Port R9 (R92 to R90)

Potr R9 is a 3-bit I/O port with latch. When used as an input, the latch must be set to "1". The latch is initialized to "1" during reset. Port R9 is shared with the serial port.

To use port R9 for the serial port, the latch should be set to "1". To use port R9 for an ordinary I/O port, the serial port must be disabled. Although R93 pin does not exist actually, execution of the set or clear instruction for R93 ([SET %OP09,3] or [CLR %OP09,3]) affects the operation of the internal CPU. Therefore, these instructions should not be execution on R93. However, other instructions may be used, in which an uncertain value is read upon execution of an input instruction.

Figure 3-7. Port R9

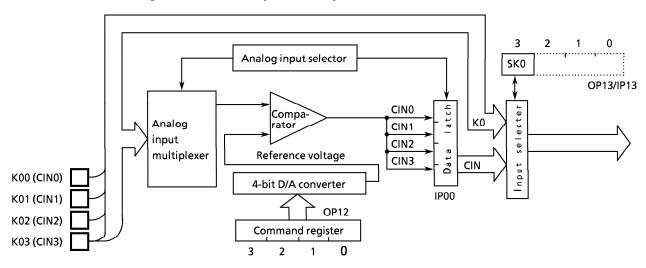

## 3.2 4bit A/D Conversion (Comparator) Input

The comparator input is analog input to discriminate key input or AFC (Auto Frequency Control) signal. It's composed of 4-bit D/A converter, comparator and control circuit. Analog input level (CIN0 to CIN3) can be detected as 16-stage by setting reference voltage.

The comparator input can also be used as K0 port (digital input). To use as K0 port, set the most significant bit of the port address OP13 to "1". Which port is selected digital (K0) or comparator (CIN) input can be monitored by accessing the port address IP13.

# 3.2.1 Circuit Configuration of Comparator Input

Figure 3-8. Circuit of Comparator Input

## 3.2.2 Control of Comparator Input

K0 port input selector command register

(Port address : OP13 / IP13) (Initial value 1\*\*\*)

3 2 1 0

SK0

SK0 Select K0 input mode

0: CIN comparator input1: K0 digital input

Figure 3-9. Command Register, Status Register

Reference voltage (Vref) is set by command register (port address OP12), and it is determined by the following form.

$$V_{REF} = V_{DD} \times (n + 1) / 16 [V] \quad (n = 0 \text{ to } 15)$$

After initialization sequence, 4-channel comparator inputs continue comparison operation successively.

Since 2-instruction cycles are required to complete comparison of 1-channel, it is necessary to wait for 8-instruction cycles after setting a reference voltage to read data from the comparator. When analog input voltage is higher than reference voltage, comparator data latch is set to "1". At the initialization sequence, OP12 is set to "0". There is not latch when used to port K0.

| OP12 |   |   |   | Vref. |

|------|---|---|---|-------|

| 3    | 2 | 1 | 0 | [V]   |

| 0    | 0 | 0 | 0 | 0.31  |

| 0    | 0 | 0 | 1 | 0.62  |

| 0    | 0 | 1 | 0 | 0.94  |

| 0    | 0 | 1 | 1 | 1.25  |

| 0    | 1 | 0 | 0 | 1.56  |

| 0    | 1 | 0 | 1 | 1.87  |

| 0    | 1 | 1 | 0 | 2.19  |

| 0    | 1 | 1 | 1 | 2.50  |

| 1    | 0 | 0 | 0 | 2.81  |

| 1    | 0 | 0 | 1 | 3.12  |

| 1    | 0 | 1 | 0 | 3.44  |

| 1    | 0 | 1 | 1 | 3.75  |

| 1    | 1 | 0 | 0 | 4.06  |

| 1    | 1 | 0 | 1 | 4.37  |

| 1    | 1 | 1 | 0 | 4.69  |

| 1    | 1 | 1 | 1 | 5.00  |

Table 3-3. Reference Voltage

Note. When the comparator input is selected, the comparator consumes typically 700  $\mu$ A current at VDD = 5 V. To reduce the power consumption, K0 port should be set to digital input mode. In the HOLD mode, the comparator current is automatically cut off by hardware. Further, during the slow operating mode, A/D conversion input is automatically disabled by hardware to reduce the power consumption.

# INPUT/OUTPUT CIRCUITRY

# (1) Control pins

The input / output circuitries of the 47C215/415 control pins are shown below.

| CONTROL PIN   | I/O             | CIRCUITRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REMARKS                                                                                                                                                                                     |

|---------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN<br>XOUT   | Input<br>Output | OSC. enable $R_f$ $R_f$ $R_0$ $R_0$ $R_1$ $R_1$ $R_2$ $R_3$ $R_4$ $R_5$ $R_0$ $R_1$ $R_2$ $R_3$ $R_4$ $R_5$ | Resonator connecting pins $ \begin{array}{ll} R &= 1 \ k\Omega & \mbox{(typ.)} \\ R_f &= 1.5 \ M\Omega & \mbox{(typ.)} \\ R_0 &= 2 \ k\Omega & \mbox{(typ.)} \\ \end{array} $               |

| XTIN<br>XTOUT | Input<br>Output | OSC. enable R <sub>fs</sub> R <sub>0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Resonator connecting pins $ \begin{array}{ll} R &= 1 \ k\Omega & (\text{typ.}) \\ R_{\text{fs}} &= 6 \ \text{M}\Omega & (\text{typ.}) \\ R_0 &= 220 \ k\Omega & (\text{typ.}) \end{array} $ |

| RESET         | Input           | R <sub>IN</sub> R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hysteresis input $Pull-up\ resistor$ $R_{IN}=220\ k\Omega  \mbox{(typ.)}$ $R=1\ k\Omega  \mbox{(typ.)}$                                                                                     |

# (2) I/O ports

The input / output circuitries of the 47C215/415 I/O ports are shown below, any one of the circuitries can be chosen by a code (MA - MC) as a mask option.

| PORT           | I/O    |         | REMARKS                                                                                                                                   |                 |                                                                                                                                                |

|----------------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                |        | MA      | Input / Output Circuitry (Code)  MB                                                                                                       | MC              | Pull-up /                                                                                                                                      |

| К0             | Input  |         | R <sub>IN</sub> R                                                                                                                         | R <sub>IN</sub> | Pull-down resistor $R_{\text{IN}} = 70 \text{ k}\Omega \text{ (typ.)}$ $R = 1 \text{ k}\Omega \text{ (typ.)}$                                  |

| P1<br>P2<br>P3 | Output | _       | OVDD<br>R <sub>K</sub> X<br>VKK O                                                                                                         |                 | Source open drain output Initial "Hi-Z" High-breakdown voltage $R_K = 80 \ k\Omega$ (typ.)                                                     |

| R4<br>R5<br>R6 | I/O    |         | Source open drain output Initial "Hi-Z" High-breakdown voltage $R_{K}=80~\text{k}\Omega~\text{(typ.)}$ $R=1~\text{k}\Omega~\text{(typ.)}$ |                 |                                                                                                                                                |

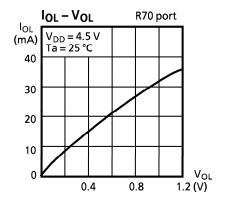

| R7             | 1/0    | R70     | R71, R72                                                                                                                                  | , R73           | Sink open drain output Initial "Hi-Z" Hysteresis input (R70) $R = 1 \text{ k}\Omega$ (typ.) High current (R70) $I_{OL} = 15 \text{ mA}$ (typ.) |

| R8<br>R9       | I/O    | Initial | "Hi-Z"                                                                                                                                    |                 | Sink open drain output Initial "Hi-Z" Hysteresis input $R=1~k\Omega$ (typ.)                                                                    |

## **ELECTRICAL CHARACTERISTICS**

ABSOLUTE MAXIMUM RATINGS  $(V_{SS} = 0 V)$

| PARAMETER                                   | SYMBOL             | PINS                     | RATING                                        | UNIT     |  |

|---------------------------------------------|--------------------|--------------------------|-----------------------------------------------|----------|--|

| Supply Voltage                              | V <sub>DD</sub>    |                          | – 0.3 to 6.5                                  | >        |  |

| Input Voltage                               | V <sub>IN</sub>    |                          | - 0.3 to V <sub>DD</sub> + 0.3                | <b>V</b> |  |

|                                             | V <sub>OUT1</sub>  | R7, R8, R9, XOUT         | $-0.3$ to $V_{DD} + 0.3$                      | V        |  |

| Output Voltage                              | V <sub>OUT3</sub>  | P1, P2, P3, R4, R5, R6   | V <sub>DD</sub> – 40 to V <sub>DD</sub> + 0.3 |          |  |

|                                             | I <sub>OUT1</sub>  | R70                      | 30                                            |          |  |

|                                             | I <sub>OUT2</sub>  | R71 to R73, R80, R81, R9 | 3.2                                           | mA       |  |

| Output Current (per 1 pin)                  | I <sub>OUT3</sub>  | P1, P2, P3               | - 12                                          |          |  |

|                                             | I <sub>OUT4</sub>  | R4, R5, R6               | <b>- 25</b>                                   |          |  |

|                                             | ΣI <sub>OUT3</sub> | P1, P2, P3               | - 80                                          |          |  |

| Output Currnent (Total)                     | ΣI <sub>OUT4</sub> | R4, R5, R6               | - 100                                         | mA       |  |

| Power Dissipation [T <sub>opr</sub> = 70°C] | PD                 |                          | 600                                           | mW       |  |

| Soldering Temperature (time)                | Tsld               |                          | 260 (10 s)                                    | °C       |  |

| Storage Temperature                         | Tstg               | – 55 to 12               |                                               | °C       |  |

| Operating Temperature                       | Topr               |                          | – 30 to 70                                    | °C       |  |

Note. Output voltage  $V_{OUT3}$ : The  $V_{OUT3}$  of OTP (TMP47P415VN) is from  $V_{DD}$  – 38 (V) to VDD + 0.3 (V).

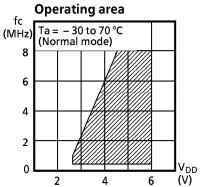

RECOMMENDED OPERATING CONDITIONS  $(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER            | SYMBOL           | PINS                    | CONDITIONS            | Min.                   | Max.                   | UNIT |

|----------------------|------------------|-------------------------|-----------------------|------------------------|------------------------|------|

|                      |                  |                         | In the Normal mode    | 4.5                    |                        |      |

| Supply Voltage       | V <sub>DD</sub>  |                         | In the SLOW mode      | 2.7                    | 5.5                    | V    |

|                      |                  |                         | In the HOLD mode      | 2.0                    |                        |      |

|                      | V <sub>IH1</sub> | Except Hysteresis Input |                       | $V_{DD} \times 0.7$    |                        |      |

| Input - High Voltage | V <sub>IH2</sub> | Hysteresis Input        | V <sub>DD</sub> ≥4.5V | V <sub>DD</sub> × 0.75 | $V_{DD}$               | V    |

|                      | V <sub>IH3</sub> |                         | V <sub>DD</sub> <4.5V | $V_{DD} \times 0.9$    |                        |      |

|                      | V <sub>IL1</sub> | Except Hysteresis Input |                       |                        | $V_{DD} \times 0.3$    |      |

| Input - Low Voltage  | V <sub>IL2</sub> | Hysteresis Input        | V <sub>DD</sub> ≧4.5V | 0                      | V <sub>DD</sub> × 0.25 | v    |

|                      | V <sub>IL3</sub> |                         | V <sub>DD</sub> <4.5V |                        | V <sub>DD</sub> × 0.1  |      |

|                      | fc               | XIN, XOUT               |                       | 0.4                    | 8.0                    | MHz  |

| Clock Frequency      | fs               | XTIN, XTOUT             |                       | 30.0                   | 34.0                   | kHz  |

Note. Input voltage VIH3, VIL3: in the SLOW or HOLD mode

D.C. CHARACTERISTICS

$(V_{SS} = 0 \text{ V}, T_{opr} = -30 \text{ to } 70 \text{ °C})$

| PARAMETER                              | SYMBOL            | PINS                           | CONDITIONS                                        | Min. | Тур. | Max. | UNIT       |

|----------------------------------------|-------------------|--------------------------------|---------------------------------------------------|------|------|------|------------|

| Hysteresis Voltage                     | V <sub>HS</sub>   | Hysteresis Input               |                                                   | _    | 0.7  | _    | <          |

|                                        | I <sub>IN1</sub>  | KO, RESET                      | V <sub>DD</sub> = 5.5 V,                          |      |      |      |            |

| Input Current                          | I <sub>IN2</sub>  | R ports (open drain)           | V <sub>IN</sub> = 5.5 V / 0 V                     | _    | -    | ± 2  | μ <b>Α</b> |

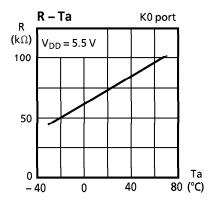

|                                        | R <sub>IN1</sub>  | KO port with pull-up/pull-down |                                                   | 30   | 70   | 150  |            |

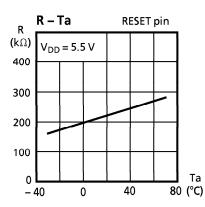

| Input Resistance                       | R <sub>IN2</sub>  | RESET                          |                                                   | 100  | 220  | 450  | kΩ         |

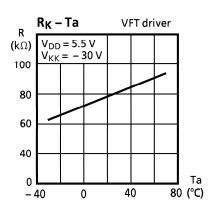

| Pull-down resistance                   | R <sub>K</sub>    | source open drain              | $V_{DD} = 5.5 \text{ V}, V_{KK} = -30 \text{ V}$  | _    | 80   | _    |            |

|                                        | I <sub>LO1</sub>  | sink open drain                | $V_{DD} = 5.5 \text{ V}, V_{IN} = 5.5 \text{ V}$  | _    | _    | 2    |            |

| Output Leakage Current                 | I <sub>LO2</sub>  | source open drain              | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = -30 V | _    | _    | -2   | μA         |

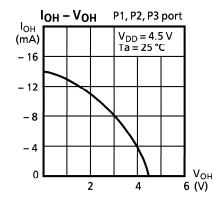

| Output Level High Voltage              | V <sub>OH</sub>   | P1, P2, P3                     | V <sub>DD</sub> = 4.5 V, I <sub>OH</sub> = -5 mA  | 2.4  | _    | _    | ٧          |

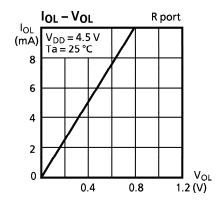

| Output Level Low Voltage               | V <sub>OL</sub>   | R71 to R73, R80, R81, R9       | V <sub>DD</sub> = 4.5 V, I <sub>OL</sub> = 1.6 mA | _    | _    | 0.4  | ٧          |

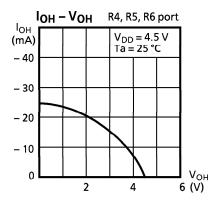

| Output Level High Current              | Іон               | R4, R5, R6                     | $V_{DD} = 4.5 \text{ V}, V_{OL} = 2.4 \text{ V}$  | _    | -15  | _    | mA         |

| Output Level Low Current               | l <sub>OL</sub>   | R70                            | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$  | _    | 15   | _    | mA         |

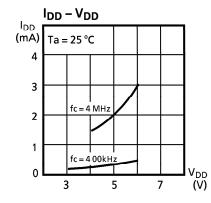

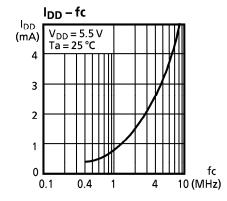

| Supply Current<br>(in the Normal mode) | I <sub>DD</sub>   |                                | V <sub>DD</sub> = 5.5 V, fc = 4 MHz               | _    | 3    | 6    | mA         |

| Supply Current<br>(in the SLOW mode)   | I <sub>DD\$</sub> |                                | V <sub>DD</sub> = 3.0 V, fs = 32.768 kHz          | _    | 30   | 60   | μA         |

| Supply Current<br>(in the HOLD mode)   | I <sub>DDH</sub>  |                                | V <sub>DD</sub> = 5.5 V                           | _    | 0.5  | 10   | μΑ         |

Note 1. Typ. values show those when Topr =  $25 \,^{\circ}$ C, VDD =  $5 \,^{\circ}$ V

Note 2. Input Current I<sub>IN1</sub>

; The current through resistor is not included, when the input resistor (pull-up / pull-down) is contained.

Supply Current  $I_{DD}$ ,  $I_{DDH}$ ;  $V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$ Note 3.

The KO port is open when the input resistor is contained. The voltage applied to the R port is within the valid range.

> IDDS ;  $V_{IN} = 2.8 \text{ V} / 0.2 \text{ V}$ , low frequency clock is only oscillated (connecting XTIN, XTOUT).

at comparator input is disabled.

A/D conversion characteristics

$(VSS = 0 \text{ V}, VDD = 4.5 \text{ to } 5.5 \text{ V}, Topr = -30 \text{ to } 70 ^{\circ}\text{C})$

| PARAMETER            | SYMBOL           | PINS         | CONDITIONS | Min.            | Тур. | Max.            | UNIT |

|----------------------|------------------|--------------|------------|-----------------|------|-----------------|------|

| Analog Input Voltage | V <sub>AIN</sub> | CIN3 to CIN0 |            | V <sub>SS</sub> | 1    | V <sub>DD</sub> | V    |

| A/D conversion error |                  |              |            | 1               | 1    | ± 1/2           | LSB  |

A.C. CHARACTERISTICS

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, T_{opr} = -30 \text{ to } 70 ^{\circ}\text{C})$

| PARAMETER                    | SYMBOL           | CONDITIONS          | Min.                      | Тур. | Max. | UNIT     |  |

|------------------------------|------------------|---------------------|---------------------------|------|------|----------|--|

|                              | t <sub>cy</sub>  | In the Normal mode  | 1.0                       | _    | 20   | 20<br>μs |  |

| Instruction Cycle Time       |                  | In the SLOW mode    | 235                       | _    | 267  |          |  |

| High level clock pulse width | t <sub>WCH</sub> |                     |                           |      |      |          |  |

| Low level clock pulse width  | t <sub>WCL</sub> | External clock mode | 80                        | _    | _    | ns       |  |

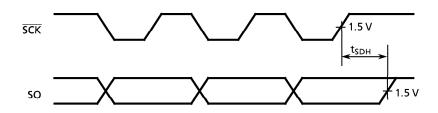

| Shift Data Hold Time         | t <sub>SDH</sub> |                     | 0.5 t <sub>cy</sub> – 300 | _    | _    | ns       |  |

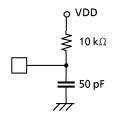

Note. External circuit for SCK Pin and

SO pin

Serial port (completion of Transmission)

## **RECOMMENDED OSCILLATING CONDITIONS**

$(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 6.0 \text{ V}, T_{opr} = -30 \text{ to } 70 ^{\circ}\text{C})$

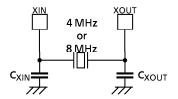

(1) 8 MHz

**Ceramic Resonator**

CSA8.00MT (MURATA)  $C_{XIN} = C_{XOUT} = 30 pF$ KBR8.00M (KYOCERA)  $C_{XIN} = C_{XOUT} = 30 pF$

(2) 4 MHz

**Ceramic Resonator**

CSA4.00MG (MURATA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$ KBR-4.00MS (KYOCERA)  $C_{XIN} = C_{XOUT} = 30 \text{ pF}$

**Crystal Oscillator**

204B-6F 4.0000 (TOYOCOM)  $C_{XIN} = C_{XOUT} = 20 pF$

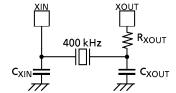

(3) 400 kHz

**Ceramic Resonator**

CSB400B (MURATA)  $C_{XIN} = C_{XOUT} = 220 \text{ pF}, R_{XOUT} = 6.8 \text{ } k\Omega$ KBR-400B (KYOCERA)  $C_{XIN} = C_{XOUT} = 100 \text{ pF}, R_{XOUT} = 10 \text{ } k\Omega$

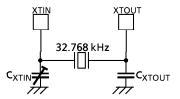

(4) 32.768 kHz (V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 2.7 to 6.0 V, T<sub>opr</sub> = -30 to 70 °C)

Crystal Oscillator C<sub>XTIN</sub>, C<sub>XTOUT</sub>; 10 to 33 pF

Note: In order to get the accurate oscillation frequency, the adjustment of capacitors must be required.

#### **TYPICAL CHARACTERISTICS**