# Regulators ICs for Digital Cameras and Camcorders

# System Switching Regulator IC with Built-in FET (10V)

**BD8355MWV** No.11036EAT20

# Description

BD8355MWV is a system switching regulator for Li 2 cell composed of 6 step-down synchronous rectification channels and 1 step-up Di rectification channel for LED application. Using a charge-pump system for high side FET driver and including power MOSFET reduce the number of peripheral devices and realize high efficiency.

### Functions

- 1) Includes step-down 6 CH (CH1~6), step-up for LED 1CH (7CH) total 7CH included.

- 2) Includes Power MOSFET for all channels.

- 3) Includes Charge-pump circuit for high side driver.

- 4) Operating frequency of 750 kHz.

- 5) CH1 and 4 are common, 3 and 5 are also common, and others are possible to turn ON/OFF independently.

- 6) Includes Short Circuit Protection (SCP), Under Voltage Lock Out (UVLO) and Thermal Shut Down (TSD).

- 7) Includes Short Circuit Protection for CH6 (SCP6).

- 8) Includes Over Voltage Protection for CH7.

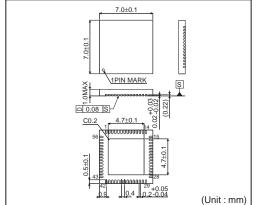

- 9) Thermally enhanced UQFN056V7070 package (7mm×7mm, 0.4mm pitch)

### Applications

For digital single-lens reflex camera, digital video camera

### ●Absolute maximum ratings (Ta=25°C)

| Parameter             | Symbol                      | Ratings   | Unit |

|-----------------------|-----------------------------|-----------|------|

|                       | VCC, VBAT, VHx1~6           | -0.3~11.0 | V    |

|                       | VLx1~6                      | -0.3~VHx  | V    |

|                       | VLx7                        | -0.3~28.0 | V    |

| Power Supply Voltage  | HVREG                       | -0.3~15.0 | V    |

|                       | CTL14, CTL2,<br>CTL35, CTL6 | -0.3~11.0 | V    |

|                       | CTL7                        | -0.3~7.0  | V    |

|                       | IomaxLx1, Lx4, Lx5          | ±1.5      | Α    |

| Maximum Current       | IomaxLx2, Lx3               | ±0.8      | Α    |

| Maximum Current       | IomaxLx6                    | ±2.0      | Α    |

|                       | IomaxLx7                    | +1.0      | Α    |

| Davier Dissination    | Pd                          | 420 (*1)  | mW   |

| Power Dissipation     | Pa                          | 930 (*2)  | mW   |

| Operating Temperature | Topr                        | -25~+85   | °C   |

| Storage Temperature   | Tstg                        | -55~+125  | °C   |

| Junction Temperature  | Tjmax                       | 125       | °C   |

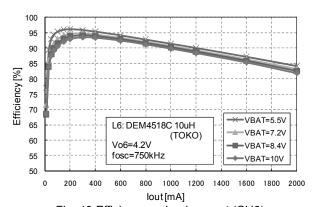

<sup>\*1</sup> Without external heat sink, power dissipation degrades by 4.2mW/°C above 25°C.

<sup>\*2</sup> Power dissipation degrades by 9.3mW/°C above 25°C, when mounted on a 74.2mm×74.2mm×1.6mmt grass epoxy PCB.

● Recommended Operating Conditions(Ta=-25~+85°C)

| Parameter              | Symbol            |       | Unit |      |       |

|------------------------|-------------------|-------|------|------|-------|

| Parameter              | Symbol            | Min.  | Тур. | Max. | Ullit |

| Power Supply Voltage   | VCC, VBAT, VHx1~6 | 4.0   | 7.2  | 10.0 | V     |

| VREGA Output Capacitor | CVREGA            | 0.47  | 1.0  | 2.2  | μF    |

| VREGD Output Capacitor | CVREGD            | 0.47  | 1.0  | 2.2  | μF    |

| HVREG Output Capacitor | CHVREG            | 0.47  | 1.0  | 2.2  | μF    |

| Flying Capacitor       | CFLY              | 0.047 | 0.1  | 0.22 | μF    |

| Oscillator Frequency   | Fosc              | 500   | 750  | 1800 | kHz   |

| Timing Resistor        | RRT               | 15    | 47   | 82   | kΩ    |

| Parameter                       | Symbol   | Limits        |               |       | Unit  | Conditions             |

|---------------------------------|----------|---------------|---------------|-------|-------|------------------------|

| Falanielei                      | Syllibol | Min.          | і. Тур. Ма    |       | Offic | Conditions             |

| [Reference Voltage]             |          |               |               |       |       |                        |

| VREGA Output Voltage            | VREGA    | 3.54          | 3.60          | 3.66  | V     | VREGA=-1mA             |

| Line Regulation                 | DVIi     | -             | -             | 10    | mV    | VCC=4V~10V, VREGA=-1mA |

| Load Regulation                 | DVIo     | -             | -             | 10    | mV    | VREGA=-1mA~-5mA        |

| [Bias Voltage]                  | ·        |               |               |       |       |                        |

| VREGD Output Voltage            | VREGD    | 3.50          | 3.60          | 3.70  | V     | VREGD=-10mA            |

| 【Charge Pump】                   | 1        |               |               |       |       |                        |

| HVREG Output Voltage            | HVREG    | VBAT<br>+3.50 | VBAT<br>+3.60 | -     | V     | lout=0mA, FB=2.5V      |

| Output Impedance                | RHVREG   | -             | 24            | 40    | Ω     | lout=-30mA, CFLY=0.1µF |

| [Oscillator]                    |          |               |               |       |       |                        |

| Oscillator Frequency            | fosc     | 650           | 750           | 850   | kHz   | RT=47kΩ                |

| Oscillator Frequency cofficient | Df       | -             | 0             | 2     | %     | VCC=4V~10V             |

| [PWM Comparator]                |          |               |               |       |       |                        |

| CH7 0% Duty Threshold Voltage   | Vth0     | 0.2           | 0.3           | -     | V     |                        |

| CH7 Max Duty                    | Dmax     | 86            | 92            | 96    | %     |                        |

| [Error Amplifier 1] (CH1)       |          |               |               |       |       |                        |

| Threshold Voltage               | Veth1    | 0.790         | 0.800         | 0.810 | V     |                        |

| Output Voltage L                | VFBL1    | -             | 0.03          | 0.2   | V     | INV1=0.9V              |

| Output Voltage H                | VFBH1    | 3.3           | 3.5           | -     | V     | INV1=0.7V              |

| Output Sink Current             | Isink1   | 4.0           | 17.0          | -     | mA    | INV1=0.9V, FB1=1.75V   |

| Output Source Current           | Isource1 | -             | -140          | -70   | μΑ    | INV1=0.7V, FB1=1.75V   |

| Input Bias Current              | Ibias1   | -100          | 0             | 100   | nA    | INV1=0V                |

| [Error Amplifier 2] (CH2~6)     |          |               |               |       |       |                        |

| Threshold Voltage               | Veth     | 0.990         | 1.000         | 1.010 | V     |                        |

| Output Voltage L                | VFBL     | -             | 0.03          | 0.2   | V     | INV=1.1V               |

| Output Voltage H                | VFBH     | 3.3           | 3.5           | -     | V     | INV=0.9V               |

| Output Sink Current             | Isink    | 4.0           | 17.0          | -     | mA    | INV=1.1V, FB=1.75V     |

| Output Source Current           | Isource  | -             | -140          | -70   | μΑ    | INV=0.9V, FB=1.75V     |

| Input Bias Current              | Ibias    | -100          | 0             | 100   | nA    | INV=0V                 |

| [Error Amplifier 3] (CH7)       | 1        |               |               |       |       |                        |

| Threshold Voltage               | Veth7    | 0.285         | 0.300         | 0.315 | V     |                        |

| Output Voltage L                | VFBL7    | -             | 0.03          | 0.2   | V     | INV=0.4V               |

| Output Voltage H                | VFBH7    | 3.3           | 3.5           | -     | V     | INV=0.2V               |

| Output Sink Current             | Isink7   | 4.0           | 17.0          | -     | mA    | INV=0.4V, FB=1.75V     |

| Output Source Current           | Isource7 | -             | -140          | -70   | μA    | INV=0.2V, FB=1.75V     |

| Input Bias Current              | Ibias7   | -50           | 0             | 50    | nA    | INV7=0V                |

| Parame                     | eter          | Symbol    |      | Limits | Т    | Unit | Conditions                             |

|----------------------------|---------------|-----------|------|--------|------|------|----------------------------------------|

|                            | 0-4-0-41      |           | Min. | Тур.   | Max. |      |                                        |

| [Soft Start]               |               |           | П    | Т      | Т    | Т    |                                        |

| CH1 Soft Start Time        | Tss1          | 1.3       | 2.5  | 3.7    | msec | CH1  |                                        |

| CH2-6 Soft Start Time      |               | Tss2-6    | 1.5  | 3.1    | 4.6  | msec | CH2 <sup>6</sup>                       |

| CH7 Duty Restriction Ti    | me            | TDTC7     | 12.0 | 15.0   | 18.0 | msec | CH7                                    |

| [ Driver]                  |               |           | Ī    | T      | T    | 1    |                                        |

| CH1~6 Lx Pull-down Re      | esistor       | RLx       | 300  | 500    | 700  | Ω    | CTL=0V                                 |

| CH1 High Side Nch FE       | Γ On Resistor | RonH1     | -    | 0.27   | 0.44 | Ω    | Lx1=-50mA                              |

| CH1 Low Side Nch FET       | On Resistor   | RonL1     | -    | 0.15   | 0.24 | Ω    | Lx1=50mA                               |

| CH2 High Side Nch FE       | Γ On Resistor | RonH2     | -    | 0.42   | 0.68 | Ω    | Lx2=-50mA                              |

| CH2 Low Side Nch FET       | On Resistor   | RonL2     | -    | 0.30   | 0.48 | Ω    | Lx2=50mA                               |

| CH3 High Side Nch FE       | Γ On Resistor | RonH3     | -    | 0.52   | 0.84 | Ω    | Lx3=-50mA                              |

| CH3 Low Side Nch FET       | On Resistor   | RonL3     | -    | 0.20   | 0.32 | Ω    | Lx3=50mA                               |

| CH4 High Side Nch FE       | Γ On Resistor | RonH4     | -    | 0.20   | 0.32 | Ω    | Lx4=-50mA                              |

| CH4 Low Side Nch FET       | On Resistor   | RonL4     | -    | 0.30   | 0.48 | Ω    | Lx4=50mA                               |

| CH5 High Side Nch FE       | Γ On Resistor | RonH5     | -    | 0.23   | 0.37 | Ω    | Lx5=-50mA                              |

| CH5 Low Side Nch FET       | On Resistor   | RonL5     | -    | 0.22   | 0.36 | Ω    | Lx5=50mA                               |

| CH6 High Side Nch FE       | Γ On Resistor | RonH6     | _    | 0.22   | 0.36 | Ω    | Lx6=-50mA                              |

| CH6 Low Side Nch FET       |               | RonL6     | -    | 0.30   | 0.48 | Ω    | Lx6=50mA                               |

| CH7 Nch FET On Resis       | stor          | Ron7      | _    | 0.50   | 0.80 | Ω    | Lx7=50mA                               |

| Under Voltage Lock O       |               |           |      |        |      |      |                                        |

| Threshold Voltage1         | , ,-          | Vthuvlo1  | 3.3  | 3.4    | 3.5  | V    | VCC pin voltage                        |

| Hysteresis Voltage         |               | DVuv      | 25   | 100    | 200  | mV   | VCC pin voltage                        |

| Threshold Voltage2         |               | Vthuvlo2  | _    | 2.5    | 2.7  | V    | VREGA pin voltage                      |

| Threshold Voltage3         |               | Vthuvlo3  | _    | 3.15   | 3.35 | V    | VREGD pin voltage                      |

| Short Circuit Protection   | n(SCP)]       | 1         |      |        |      | -    | The particular                         |

| Timer Start Voltage        | 1(001 )1      | Vstart    | 2.65 | 2.8    | 2.95 | V    | FB1~5, 7 pin v oltage                  |

| CH6 Timer Start Voltage    |               | Vstart6   | 0.45 | 0.50   | 0.55 | V    | INV6 pin voltage                       |

| SCP pin Threshold Voltage  |               | Vscpth    | 0.43 | 1.0    | 1.1  | V    | iivo piii voitage                      |

| SCP6 pin Threshold Vol     |               | Vscp6th   | 0.9  | 1.0    | 1.1  | V    |                                        |

|                            |               |           | -1.4 | -1.0   | -0.6 | -    | SCP=0.1V                               |

| SCP pin Source Curren      |               | Iscp      |      |        |      | μΑ   |                                        |

| SCP6 pin Source Curre      |               | Iscp6     | -1.4 | -1.0   | -0.6 | μA   | SCP6=0.1V                              |

| SCP pin Stand-by Volta     |               | Vstscp    | -    | 10     | 100  | mV   | CTL=3V, FB=0V                          |

| SCP6 pin Stand-by Volt     |               | Vstscp6   | -    | 10     | 100  | mV   | CTL6=3V, INV6=1.0V                     |

| Over Voltage Protection    |               | \ (O) (D7 | 00.5 | 00.0   | 00.5 |      | \/.\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| CH7 OVP Threshold Vo       | itage         | VOVP7     | 26.5 | 28.0   | 29.5 | V    | Vo7 pin voltage                        |

| [Control]                  | A . C         | \         | _    |        | 1/00 | .,   |                                        |

| CTL1-6                     | Active        | VCTLH     | 2    | -      | VCC  | V    |                                        |

| Control Voltage            | Non-Active    | VCTLL     | -0.3 | -      | 0.4  | V    |                                        |

| CTL7                       | Active        | VCTLH     | 2    | -      | 5.5  | V    |                                        |

| Control Voltage Non-Active |               | VCTLL     | -0.3 | -      | 0.4  | V    |                                        |

| CTL pin Pull-Down Res      | istor         | RCTL      | 0.6  | 1.0    | 1.4  | МΩ   |                                        |

| [Whole device]             |               | 1         |      | I      | I    | I    | T                                      |

|                            | VCC pin       | Istb1     | -    | 0      | 5    | μA   | CTL=0V                                 |

| Stand-by Current           | Hx pin        | Istb2     | -    | 0      | 5    | μΑ   | Hx1~6=10V, sum of Hx1~6                |

|                            | Lx7 pin       | Istb3     | -    | 0      | 5    | μA   | Lx7=28V                                |

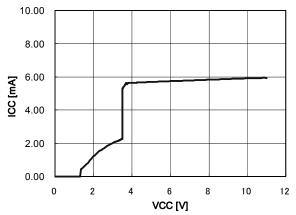

| Circuit Current            |               | Icc       | -    | 6.0    | 9.0  | mA   | CTL=3V, FB=2.5V                        |

<sup>©</sup>This product is not designed for normal operation within a radioactive environment.

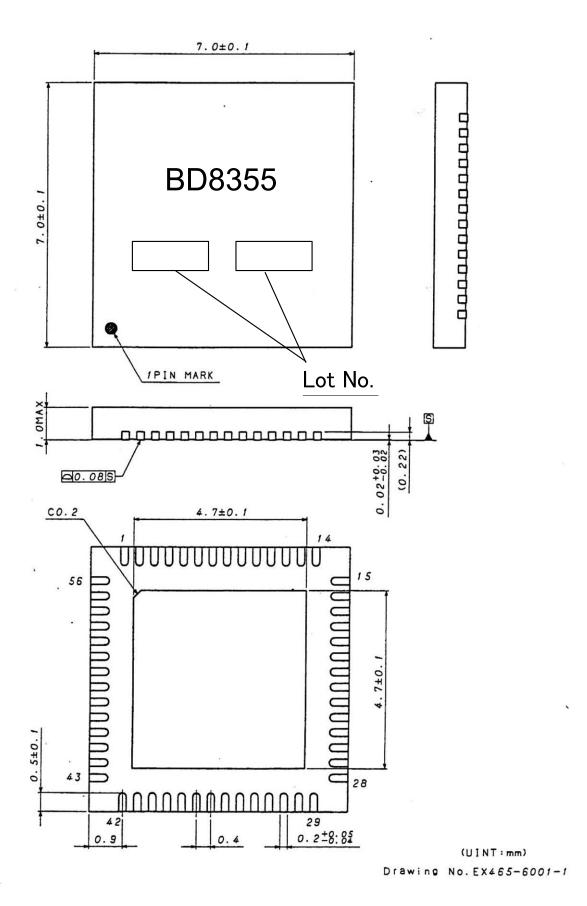

# ●Package dimensions

Fig. 1 Package dimension

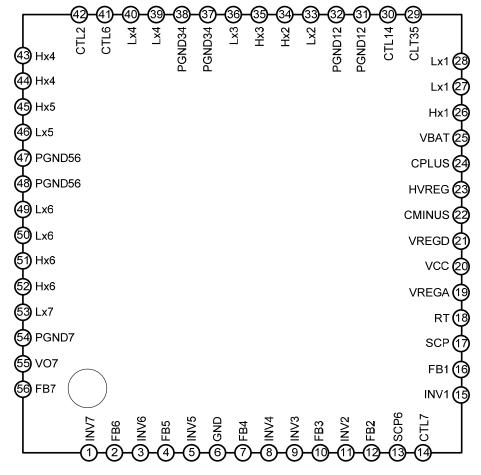

●PIN Assignments

| D: 10 | D: N     | D: D : ::                                                                   | D: 11   | D: 11    | D: D                                                  |

|-------|----------|-----------------------------------------------------------------------------|---------|----------|-------------------------------------------------------|

|       | Pin Name | Pin Descriptions                                                            | Pin No. | Pin Name | Pin Descriptions                                      |

| 1     | INV7     | CH7 Error Amplifier Negative Input Pin                                      | 29      | CTL35    | CH3, 5 ON/OFF Control Pin                             |

| 2     | FB6      | CH6 Error Amplifier Output Pin                                              | 30      | CTL14    | CH1, 4 ON/OFF Control Pin                             |

| 3     | INV6     | CH6 Error Amplifier Negative Input Pin                                      | 31      | PGND12   | Ground Pin for CH1, 2 Output                          |

| 4     | FB5      | CH5 Error Amplifier Output Pin                                              | 32      | PGND12   | Ground Pin for CH1, 2 Output                          |

| 5     | INV5     | CH5 Error Amplifier Negative Input Pin                                      | 33      | Lx2      | Pin for Connecting to Inductor of CH2                 |

| 6     | GND      | Ground Pin                                                                  | 34      | Hx2      | CH2 Highside Transistor and Driver Supply Voltage     |

| 7     | FB4      | CH4 Error Amplifier Output Pin                                              | 35      | Hx3      | CH3 Highside Transistor and Driver Supply Voltage     |

| 8     | INV4     | CH4 Error Amplifier Negative Input Pin                                      | 36      | Lx3      | Pin for Connecting to Inductor of CH3                 |

| 9     | INV3     | CH3 Error Amplifier Negative Input Pin                                      | 37      | PGND34   | Ground Pin for CH3, 4 Output                          |

| 10    | FB3      | CH3 Error Amplifier Output Pin                                              | 38      | PGND34   | Ground Pin for CH3, 4 Output                          |

| 11    | INV2     | CH2 Error Amplifier Negative Input Pin                                      | 39      | Lx4      | Pin for Connecting to Inductor of CH4                 |

| 12    | FB2      | CH2 Error Amplifier Output Pin                                              | 40      | Lx4      | Pin for Connecting to Inductor of CH4                 |

| 13    | SCP6     | CH6 Short Circuit Protection Delay Time Setting Pin with External Capacitor | 41      | CTL6     | CH6 ON/OFF Control Pin                                |

| 14    | CTL7     | CH7 ON/OFF Control Pin                                                      | 42      | CTL2     | CH2 ON/OFF Control Pin                                |

| 15    | INV1     | CH1 Error Amplifier Negative Input Pin                                      | 43      | Hx4      | CH4 Highside Transistor and Driver Supply Voltage     |

| 16    | FB1      | CH1 Error Amplifier Output Pin                                              | 44      | Hx4      | CH4 Highside Transistor and Driver Supply Voltage     |

| 17    | SCP      | CH1-5 and CH7 Short Circuit Protection Delay Time Setting                   | 45      | Hx5      | CH5 Highside Transistor and Driver Supply Voltage Pin |

| 18    | RT       | Oscillator Frequency Adjustment Pin with External                           | 46      | Lx5      | Pin for Connecting to Inductor of CH5                 |

| 19    | VREGA    | 3.6V Reference Output Voltage Pin                                           | 47      | PGND56   | Ground Pin for CH5, 6 Output                          |

| 20    | VCC      | Input Supply Voltage Pin                                                    | 48      | PGND56   | Ground Pin for CH5, 6 Output                          |

| 21    | VREGD    | 3.6V Lowside Transistor Bias Voltage Output Pin                             | 49      | Lx6      | Pin for Connecting to Inductor of CH6                 |

| 22    | CMINUS   | Pin for Connecting Chargepump Flying Capacitor                              | 50      | Lx6      | Pin for Connecting to Inductor of CH6                 |

| 23    | HVREG    | Chargepump Voltage Output Pin                                               | 51      | Hx6      | CH6 Highside Transistor and Driver Supply Voltage     |

| 24    | CPLUS    | Pin for Connecting Chargepump Flying Capacitor                              | 52      | Hx6      | CH6 Highside Transistor and Driver Supply Voltage     |

| 25    | VBAT     | Chargepump Input Supply Voltage Pin                                         | 53      | Lx7      | Pin for Connecting to Inductor of CH7                 |

| 26    | Hx1      | CH1 Highside Transistor and Driver Supply Voltage                           | 54      | PGND7    | Ground Pin for CH7 Output                             |

| 27    | Lx1      | Pin for Connecting to Inductor of CH1                                       | 55      | Vo7      | Voltage Monitor Pin for CH7 Over Voltage Protection   |

| 28    | Lx1      | Pin for Connecting to Inductor of CH1                                       | 56      | FB7      | CH7 Error Amplifier Output Pin                        |

# ●PIN Assignments

Fig. 2 Pin Assignments

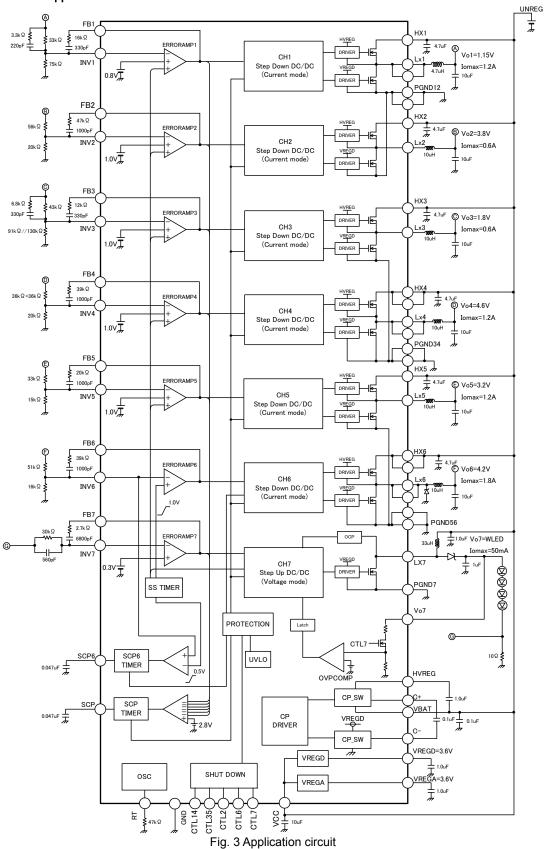

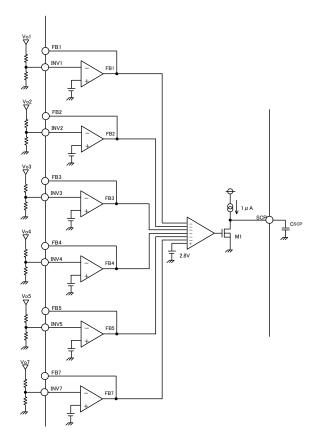

## Block diagram and application circuit

\* We are confident that the above applied circuit diagram should be recommended, but please thoroughly confirm its characteristics when using it. In addition, when using it with the external circuit's constant changed, please make a decision that allows a sufficient margin in light of the fluctuations of external components and ROHM's IC in terms of not only static characteristic but also transient characteristic.

BD8355MWV Technical Note

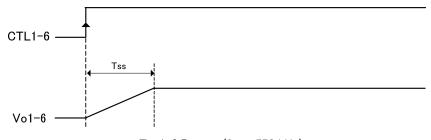

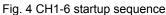

# ●Timing chart

Tss1: 2.5 msec (fosc=750 kHz)

Tss2-6: 3.1 msec (fosc=750 kHz)

TDTC7 (CH7 duty restriction time): 15 msec (fosc=750 kHz)

\*\*Turn on any CTL1-6 and wait more than 500 usec before turn on CTL7.

Fig. 5 CH7 startup sequence

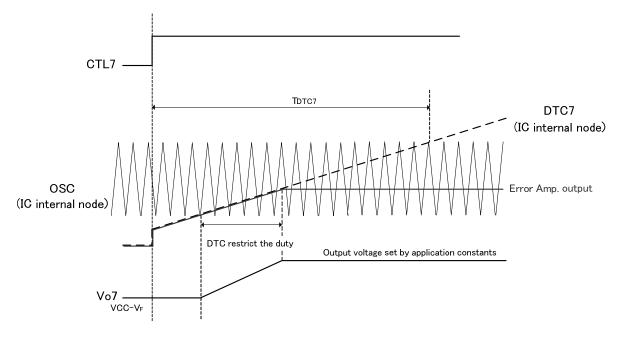

Fig. 6 stop sequence

### ●Functional Description / peripheral devices setting

Internal Regulator (VREGA, VREGD)

Both VREGA and VREGD are internal regulator of 3.6 V output. Bypass VREGA/VREGD to GND with a capacitor between 0.47 µF and 2.2 µF. In addition, it needs care for the voltage between VREGA and VREGD not to excess 0.3 V to avoid IC malfunctions.

# Control block (SHUT DOWN)

Inputting voltages to CTL14, 2, 35, 6, and 7 control ON/OFF of respective channels. Note that it is impossible to independently control CH1 and 4, and to independently control CH3 and 5. In addition, turn on any CTL1-6 and wait 500 usec before turning on CTL7. Input higher voltage than 2 V to CTL14, 2, 35, or 6 to turn on each channel. Open or input voltage -0.3 ~ 0.4 V to those to turn off. Input 2 ~ 5.5 V to CTL7 to turn on CH7. Open or input voltage -0.3 ~ 0.4 V to CTL7 to turn off. The states of output terminals (Lx1-7), FB terminals, SCP/SCP6 terminals, and internal regulator (VREGA and VREGD) are written below.

Each CTL terminal contains pull down resistor of  $1M\Omega$  (typ.)

|    |    | CTL |    |   |    |          |   | Lx |    |    |     |    |    |    | FB |    |    |   | VPEGA | VPEGD  | SCD. | SCP6  |

|----|----|-----|----|---|----|----------|---|----|----|----|-----|----|----|----|----|----|----|---|-------|--------|------|-------|

| 14 | 2  | 35  | 6  | 7 | 1  | 2        | 3 | 4  | 5  | 6  | 7   | 1  | 2  | 3  | 4  | 5  | 6  | 7 | VILOA | VINEOD | 5    | 301 0 |

| L  | L  | L   | L  | L | L  | L        | L | L  | L  | L  | H-Z | L  | L  | L  | L  | L  | L  | L | L     | L      | L    | L     |

| Н  | L  | Ь   | L  | L | Α  | Ш        | ٦ | Α  | Ш  | L  | H-Z | Α  | L  | L  | Α  | L  | L  | L | Α     | Α      | Α    | L     |

| L  | Η  | Ь   | L  | L | L  | Α        | ٦ | L  | Ш  | L  | H-Z | Ш  | Α  | L  | L  | L  | L  | L | Α     | Α      | Α    | L     |

| L  | L  | Η   | L  | L | L  | Ш        | Α | L  | Α  | L  | H-Z | Ш  | L  | Α  | L  | Α  | L  | L | Α     | Α      | Α    | L     |

| L  | L  | L   | Η  | L | L  | Ш        | ٦ | L  | Ш  | Α  | H-Z | Ш  | L  | L  | L  | L  | Α  | L | Α     | Α      | Ш    | Α     |

| L* | L* | L*  | L* | Η | L* | <u>*</u> | Ľ | Ľ* | Ľ* | L* | Α   | Ľ* | L* | Ľ* | L* | Ľ* | L* | Α | Α     | Α      | Α    | L*    |

| Н  | Н  | Η   | Н  | Н | Α  | Α        | Α | Α  | Α  | Α  | Α   | Α  | Α  | Α  | A  | Α  | Α  | Α | Α     | A      | Α    | Α     |

<sup>\*</sup> Turn on any CTL1-6 before turn on CTL7. Conditions of Lx1 ~ 6, FB1 ~ 6, SCP6 are A: active changed with active channel.

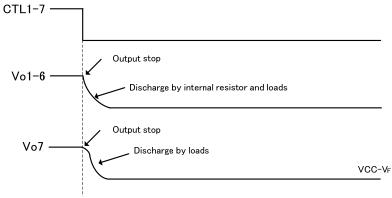

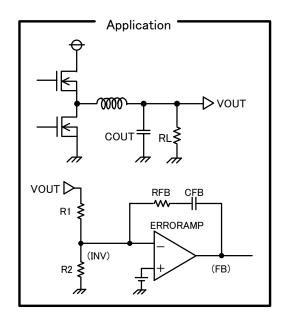

### 3. Output voltage/current setting

Fig. 7 Setting of feedback resistance

# (a) Setting output voltage of CH1-6

The reference voltages of ERROR AMP. are 0.8 V (CH1) and 1 V (CH2-6). The output voltages are determined as equation (1) and (2). Set the value of feedback resistance R1 and R2 which are connected to INV1-6 pin.

# (b) Setting output current of CH7

The reference voltage of CH7 ERROR AMP. is 0.3 V. The current flowing LED is determined as equation (3). Set the value of feedback resistance R3, considering the tolerance current of LED.

### Startup/Stop sequence

To avoid rush current on startup, each channel has soft start function. The output voltage of CH1 reaches to the target in Tss1=2.5msec (typ.) and the output voltage of CH2 ~ 6 reaches to the target in Tss2-6=3.1msec (typ.). In case of CH7, the output of error amplifier is restricted in TDTC7=15msec (typ.).

Note that Tss1-6, TDTC7 vary from typical value Ttyp as following with setting of switching frequency.

$$T_{ss1-6}$$

,  $T_{DTC7}$ ,  $T_{stop1} = T_{typ} \times \frac{750}{fosc[kHz]}$  [msec]

# Protection matrix

The following table displays state of outputs when protection is operating.

| to ming table displays state of suspate mish protestion is sportating. |       |     |     |       |     |       |       |              |     |      |

|------------------------------------------------------------------------|-------|-----|-----|-------|-----|-------|-------|--------------|-----|------|

|                                                                        | Lx1-5 | Lx6 | Lx7 | FB1-6 | FB7 | VREGA | VREGD | <b>HVREG</b> | SCP | SCP6 |

| Short Circuit Protection (CH1-5,7)                                     | H-Z   | Α   | H-Z | Α     | Α   | Α     | Α     | Α            | -   | Α    |

| Short Circuit Protection (CH6)                                         | Α     | H-Z | Α   | Α     | Α   | Α     | Α     | Α            | Α   | -    |

| Under Voltage Lockout (VCC)                                            | H-Z   | H-Z | H-Z | NA    | NA  | Α     | Α     | NA           | NA  | NA   |

| Under Voltage Lockout (VREGA)                                          | H-Z   | H-Z | H-Z | NA    | NA  | -     | Α     | NA           | NA  | NA   |

| Under Voltage Lockout (VREGD)                                          | H-Z   | H-Z | H-Z | NA    | NA  | Α     | ı     | NA           | NA  | NA   |

| Under Voltage Lockout (HVREG)                                          | H-Z   | H-Z | Α   | NA    | Α   | Α     | Α     | -            | NA  | NA   |

| Thermal Shutdown (TSD)                                                 | H-Z   | H-Z | H-Z | NA    | NA  | NA    | NA    | NA           | NA  | NA   |

A: active NA: non-active

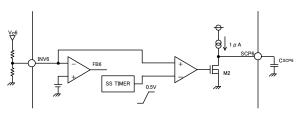

### 6. Short circuit protection (SCP, SCP6)

For CH1  $\sim$  5 and 7, monitoring the output voltages of error amplifier (FB voltage), if the voltages become more than 2.8 V, the output of SCPCOMP will become "L" level, and transistor "M1" will turn off. Thus the current "1 $\mu$ A" be supplied to CSCP the capacitor connected to SCP terminal. The outputs stop when SCP terminal voltage reaches 1 V. The time from short circuit detect to outputs stop (tscp) is set as shown below.

$$tSCP[s] = 1.0 \times CSCP[\mu F]$$

On the other hand, short circuit of CH6 is detected when the error amplifier input of CH6 (INV6) becomes less than 0.5 V. The time from short circuit detect to output stop (tscp6) is set with CSCP6 as tscp.

To release from short circuit protection latch state, turn CTL terminal to "L" level. Connect SCP/SCP6 terminal to GND when the function of short circuit protection is not used.

### 7. Over voltage protection(OVP)

In CH7, when LED is open, INV7 become L and output voltage increase suddenly. If that condition continues Lx7 voltage increase and exceed break down voltage.CH7 has over voltage protection circuit (OVP) not to exceed break down voltage. When the voltage of VO7 terminal becomes more than 28V (typ.), OVP function works and CH7 stops operating. Once OVP is detected, CH7 becomes latch state. To release from latch state, turn off CTL7.

### 8. Thermal shutdown circuit (TSD)

The TSD circuit protects the IC against thermal runaway and heat damage. The TSD thermal sensor detects junction temperature. When the temperature reaches the TSD threshold (typ: 175 ), the circuit switches the outputs of all channels, VREGA, and VREGD OFF. At the same time, it sets the FB1-7 terminals "L" level. The hysteresis width (typ: 15 ) provided between the TSD function start temperature (threshold) and the stop temperature serves to prevent malfunctions from temperature fluctuations.

# 9. Under Voltage Lockout (UVLO)

Under voltage lockout prevents IC malfunctions that could otherwise occur due to power supply fluctuation at power ON or abrupt power OFF. This system turns OFF each channel output when the VCC voltage becomes lower than 3.4 V. The UVLO detect voltage has 0.1 V hysteresis to prevent malfunctions from power supply fluctuation.

In addition, UVLO works when an internal regulator voltage drops down. The outputs of all channels are turned OFF when VREGD becomes lower than 3.15 V or VREGA becomes lower than 2.4 V. Moreover, the outputs of CH1-6 are turned OFF when HVREG becomes lower than VCC+2.5 V.

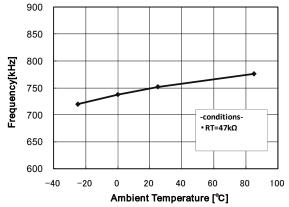

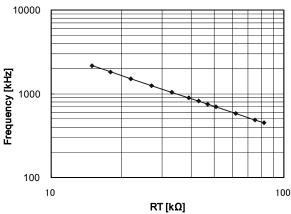

The switching frequency

The switching frequency is set by the resistor connected to the RT terminal. Set the frequency with referring fig. 19.

Fig. 8 Block diagram of short circuit protection circuit.

Fig. 9 Block diagram of short circuit protection6 circuit.

### 10. Selection of output inductor

A combination of the output inductor and the output capacitor form a second-order smoothing filter for switch waveform and provide DC output voltage. If the inductance is low, its package size is minimized, but the penalty is higher ripple current, with lower efficiency and an increase of output noise. Conversely, higher inductance increases the package size, but lowers ripple current, consequently, and suppress the output ripple voltage. Generally, set inductance as that the ripple current is about 20-50 % of their output current. Below equations are the relations of between inductance and ripple current.

(step down)

$$L[H] = \frac{(VIN[V]-VOUT[V])}{\triangle IL[A]} \times \frac{VOUT[V]}{VIN[V]} \times \frac{1}{fosc\ [Hz]}$$

(step up)

$$L[H] = \frac{(V \cup T[V] - V \cap V[V])}{\Delta I L[A]} \times \frac{V \cap V[V]}{V \cup U \cap V[V]} \times \frac{1}{f \circ sc \ [Hz]}$$

L: inductance V<sub>IN</sub>: input voltage

$V_{\text{OUT}}$ : output voltage  $\Delta I_L$ : ripple current fosc: switching frequency  $I_{\text{OUT}}$ : output load current

In addition, set larger values than I<sub>peak</sub> that is calculated from below equation.

(step down) Ipeak=IOUT + ⊿IL/2

(step up) Ipeak= $\{IOUT \times (VOUT/VIN)/(\eta/100)\}+ \Delta IL/2$  ( $\eta$ : efficiency[%])

### 11. Phase Compensation

The components shown will add poles and zeros to the loop gain as given by the following expression:

· CFB adds a pole whose frequency is given by:

fp (CFB) =

$$\frac{1}{2\pi \times A \times CFB \times (R1//R2)}$$

(A: error amplifier open loop gain)

• RFB adds a zero whose frequency is given by:

$$fz (RFB) = \frac{1}{2\pi \times CFB \times RFB}$$

• The output capacitor adds both a pole and a zero to the loop:

fz (COUT) =

$$\frac{1}{2\pi \times ESR \times COUT}$$

fp (COUT) =

$$\frac{1}{2\pi \times RL \times COUT}$$

Fig. 10 Phase compensation setting

Where, RL is output load resistance, and ESR is the equivalent series resistance of the output capacitor. CFB forms a pole and a zero. Changing the value of CFB moves the frequency of both the pole and the zero. The CFB pole is typically referred to as the dominant pole, and its primary function is to roll off loop gain and reduce the bandwidth. The RFB zero is required to add some positive phase shift to offset some of the negative phase shift from the two low-frequency poles. Without this zero, these two poles would cause -180° of phase shift at the unity-gain crossover, which is clearly unstable.

### 12. Precaution in the layout of Printed Circuit Board

- When switching regulator is operating, large current flow through the path of Power Supply Inductor Output Capacitor. In laying a pattern of the board, make this line as short and wide as possible to decrease impedance.

- The switching noise on INV1-7 terminals may cause the output oscillation. To avoid interference of the noise, make the line between voltage divider resistor and INV terminals as shortened as possible and not crossed at switching line.

### ●Reference data

Fig. 11 Circuit current vs supply voltage (all cannels ON)

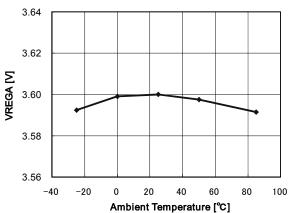

Fig. 13 VREGA vs ambient temperature

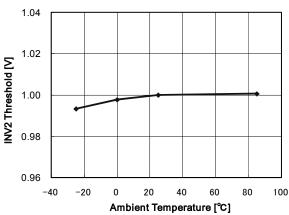

Fig. 15 CH2 ErrorAmp. INV threshold vs ambient temperature

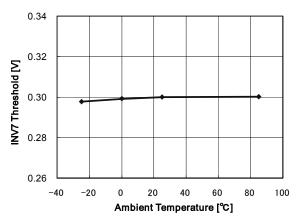

Fig. 17 CH7 ErrorAmp. INV threshold vs ambient temperature

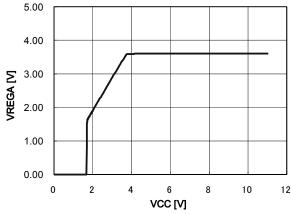

Fig. 12 VREGA vs supply voltage

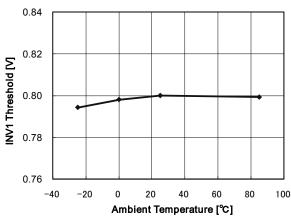

Fig. 14 CH1 ErrorAmp. INV threshold vs ambient temperature

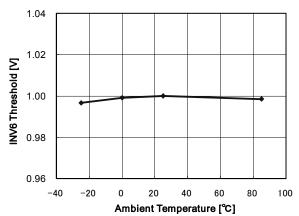

Fig. 16 CH6 ErrorAmp. INV threshold vs ambient temperature

Fig. 18 Frequency vs ambient temperature

Fig. 19 Switching frequency vs timing resistance

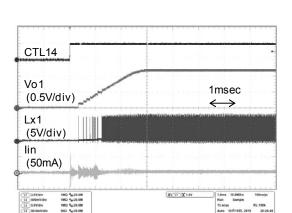

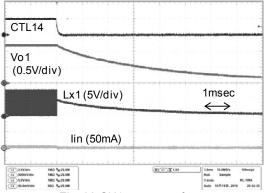

Fig. 21 CH1 startup waveform

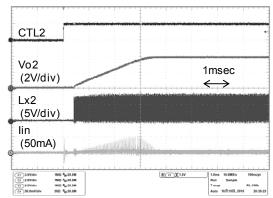

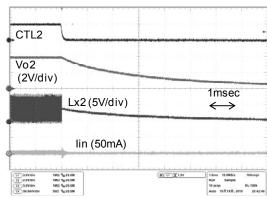

Fig. 23 CH2 startup waveform

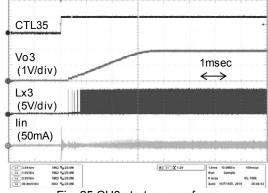

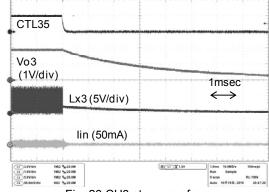

Fig. 25 CH3 startup waveform

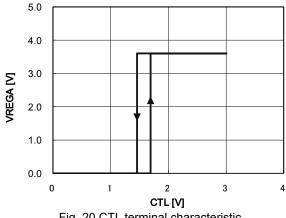

Fig. 20 CTL terminal characteristic

Fig. 22 CH1 stop waveform

Fig. 24 CH2 stop waveform

Fig. 26 CH3 stop waveform

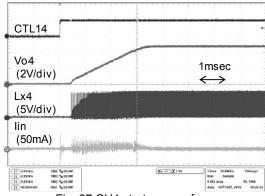

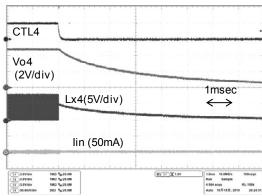

Fig. 27 CH4 startup waveform

Fig. 29 CH5 startup waveform

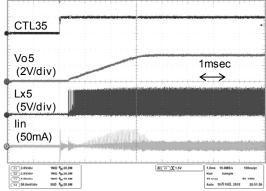

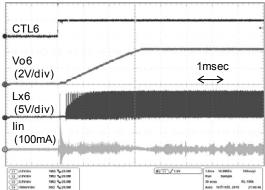

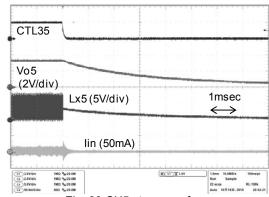

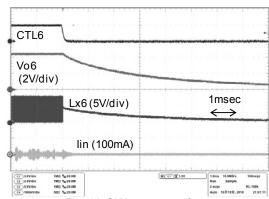

Fig. 31 CH6 startup waveform

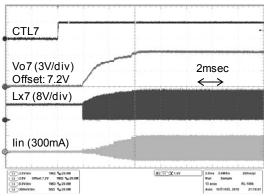

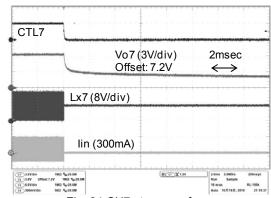

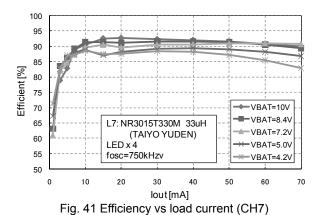

Fig. 33 CH7 startup waveform

Fig. 28 CH4 stop waveform

Fig. 30 CH5 stop waveform

Fig. 32 CH6 stop waveform

Fig. 34 CH7 stop waveform

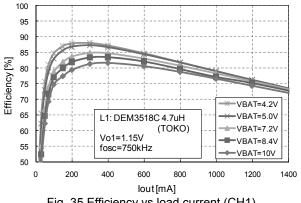

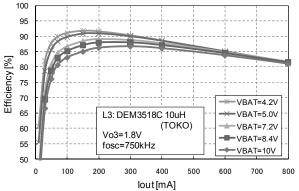

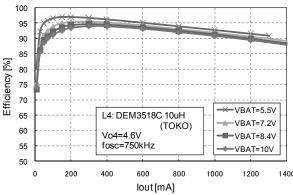

Fig. 35 Efficiency vs load current (CH1)

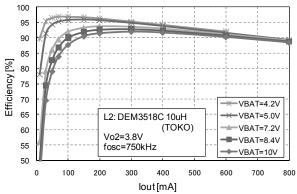

Fig. 37 Efficiency vs load current (CH3)

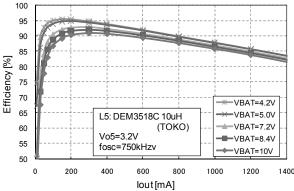

Fig. 39 Efficiency vs load current (CH5)

Fig. 36 Efficiency vs load current (CH2)

Fig. 38 Efficiency vs load current (CH4)

Fig. 40 Efficiency vs load current (CH6)

# ●Power Dissipation Reduction

Fig. 42 Power dissipation vs ambient temperature

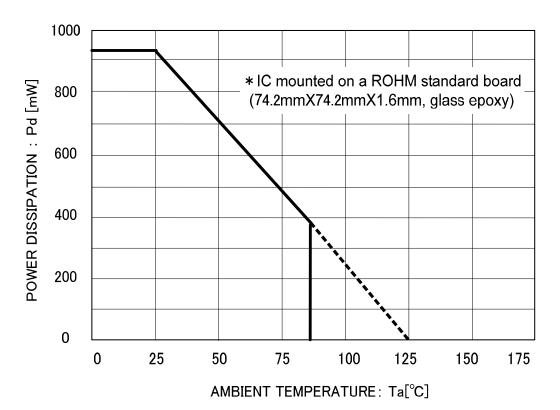

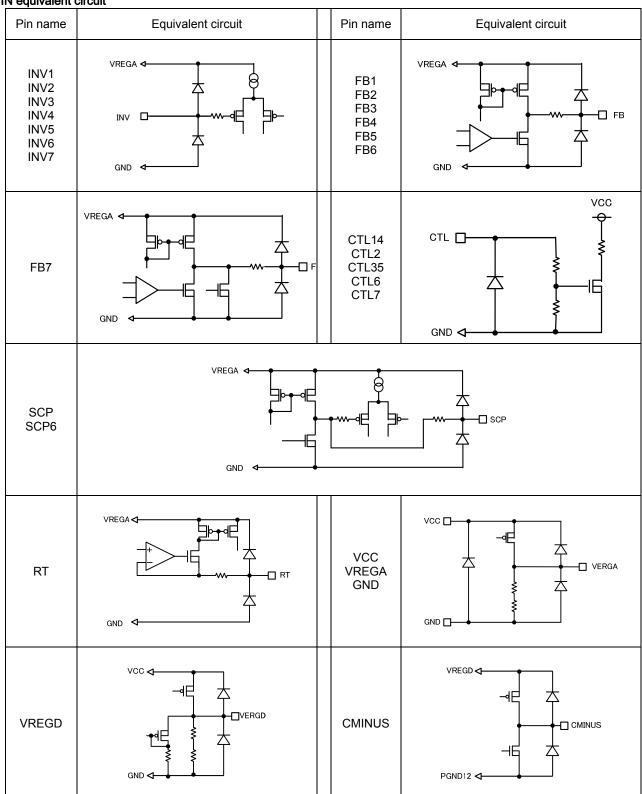

●PIN equivalent circuit

| Pin name               | Equivalent circuit                | Pin name                                                                                                       | Equivalent circuit           |

|------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------------|

| HVREG<br>CPLUS<br>VBAT | HVREG CPLUS  VCC CPLUS  VBAT  GND | HX1<br>LX1<br>HX2<br>LX2<br>PGND12<br>HX3<br>LX3<br>HX4<br>LX4<br>PGND34<br>HX5<br>LX5<br>HX6<br>LX6<br>PGND56 | HX HVREG VREGD VREGD LX PGND |

| Lx7<br>PGND7           | PGND7 GND                         | Vo7                                                                                                            | VREGA Vo7  PGND7  GND        |

### Notes for use

### 1.) Absolute maximum ratings

This product is produced with strict quality control. However, the IC may be destroyed if operated beyond its absolute maximum ratings. If the device is destroyed by exceeding the recommended maximum ratings, the failure mode will be difficult to determine (e.g. short mode, open mode). Therefore, physical protection counter-measures (like fuse) should be implemented when operating conditions beyond the absolute maximum ratings anticipated.

### 2.) GND potential

Ensure a minimum GND pin potential in all operating conditions. In addition, ensure that no pins other than the GND pin carry a voltage lower than or equal to the GND pin, including during actual transient phenomena.

### 3.) Thermal design

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

### 4.) Inter-pin shorts and mounting errors

Use caution direction and position the IC for mounting on printed circuit boards. Improper mounting may result in damage the IC. In addition, Output-output short and output-power supply/ground short condition may destroy the IC

# 5.) Operation in a strong electromagnetic field

Exposing the IC within a strong electric/magnetic field may cause malfunction.

### 6.) Common impedance

Power supply and ground wiring should reflect consideration of the need to lower common impedance and minimize ripple as much as possible (by making wiring as short and thick as possible or rejecting ripple by incorporating inductance and capacitance).

# 7.) Voltage of CTL pins

The threshold voltage of CTL pins are 0.4 V and 2.0 V. Standby state is set below 0.4 V while running state is set beyond 2.0 V. The region between 0.4 V and 2.0 V is not recommended and may cause improper operation. The rise and fall time must be under 10 msec. In case to put capacitors to CTL pins, it is recommended using under 0.01 p.

The maximum permissible voltage of CTL7 is 5.5 V. CTL7 pin should not be connected to VCC voltage. Turn on any CTL1-6 and wait more than 500 usec before turn on CTL7.

### 8.) Thermal shutdown circuit (TSD circuit)

The IC incorporates a built-in thermal shutdown circuit (TSD circuit). The TSD circuit is designed only to shut the IC off to prevent runaway thermal operation. It is not designed to protect the IC or guarantee its operation. Do not continue to use the IC after operating this circuit or use the IC in an environment where the operation of this circuit is assumed.

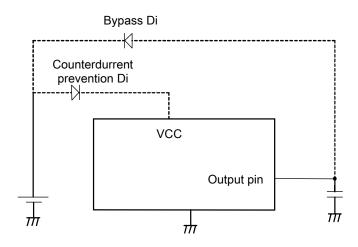

9.) Applications with modes that VCC/GND and other pins except Lx and HVREG potential are reversed may cause damage internal IC circuits. In addition, modes that each pins sink current may also cause damage the circuits. Therefore, It is recommended to insert a diode to prevent back current flow or bypass diodes.

- 10.) Rush current at the time of power supply injection.

An IC which has plural power supplies could have momentary rush current at the time of power supply injection. Please take care about power supply coupling capacity and width of power Supply and GND pattern wiring

- 11.) Please use it so that VCC and PVCC terminal should not exceed the absolute maximum ratings. Ringing might be caused by L element of the pattern according to the position of the input capacitor, and ratings be exceeded. Please will assume the example of the reference ,the distance of IC and capacitor, use it by 5.0mm or less when thickness of print pattern are 35um, pattern width are 1.0mm.

- 12.) Testing on application boards

When testing the IC on an application board, connecting a capacitor to a pin with low impedance subjects the IC to stress. Always discharge capacitors after each process or step. Ground the IC during assembly steps as an antistatic measure, and use similar caution when transporting or storing the IC. Always turn the IC's power supply off before connecting it to or removing it from a jig or fixture during the inspection process.

- 13.) Thermal fin.

- There is no problem in the operating of IC even if the thermal fin on the back of package doesn't connect anywhere. But it is recommended to connect GND on the PCB board for radiation.

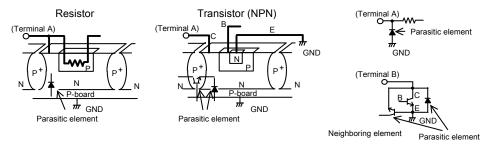

- 14.) IC Terminal Input

This IC is a monolithic IC that has a P- board and P+ isolation for the purpose of keeping distance between elements. A P-N junction is formed between the P-layer and the N-layer of each element, and various types of parasitic elements are then formed. For example, an application where a resistor and transistor are connected to a terminal (shown in Fig.43)

- OWhen GND > (terminal A) at the resistor and GND > (terminal B) at the transistor (NPN), the P-N junction operates as a parasitic diode

- OWhen GND > (terminal B) at the transistor (NPN), a parasitic NPN transistor operates as a result of the N layers of other elements in the proximity of the aforementioned parasitic diode.

Parasitic elements are structurally inevitable in the IC due to electric potential relationships. The operation of parasitic elements induces the interference of circuit operations, causing malfunctions and possibly the destruction of the IC. Please be careful not to use the IC in a way that would cause parasitic elements to operate. For example, by applying a voltage that is lower than the GND (P-board) to the input terminal.

Fig. 43 Simple Structure of Bipolar IC (Sample)

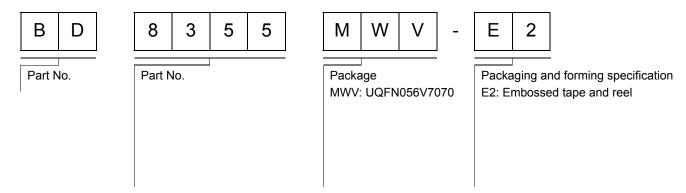

# Ordering part number

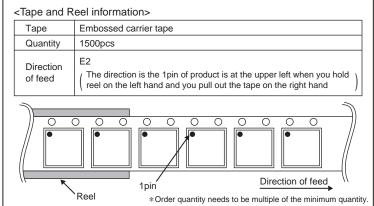

# UQFN056V7070

### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/