## 32K x 8 PROM Power-Switched and Reprogrammable

#### **Features**

- CMOS for optimum speed/power

- Windowed for reprogrammability

- High speed

- -30 ns (commercial)

- -35 ns (military)

- · Low power

- --- 660 mW (commercial)

- 715 mW (military)

- · Super low standby power

- Less than 165 mW when deselected

- EPROM technology 100% programmable

- Slim 300-mil package (7C271)

- Direct replacement for bipolar PROMs

- Capable of withstanding > 2001V static discharge

#### **Functional Description**

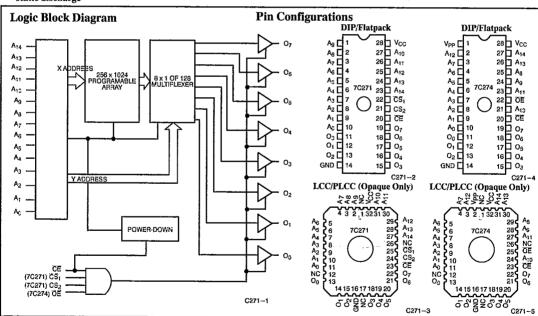

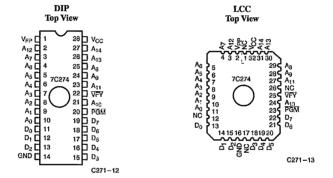

The CY7C271 and CY7C274 are highperformance 32,768-word by 8-bit CMOS PROMs. When disabled (CE HIGH). the 7C271/7C274 automatically powers down into a low-power stand-by mode. The CY7C271 is packaged in the 300-mil slim package. The CY7C274 is packaged in the industry standard 600-mil package. Both the 7C271 and 7C274 are available in a cerDIP package equipped with an erasure window to provide for reprogrammability. When exposed to UV light, the PROM is erased and can be reprogrammed. The memory cells utilize proven EPROM floating gate technology and byte-wide intelligent programming algorithms.

The CY7C271 and CY7C274 offer the advantage of lower power, superior performance, and programming yield. The EPROM cell requires only 12.5V for the super voltage, and low current requirements allow for gang programming. The EPROM cells allow each memory location to be tested 100% because each location is written into, erased, and repeatedly exercised prior to encapsulation. Each PROM is also tested for AC performance to guarantee that after customer programming, the product will meet DC and AC specification limits.

Reading the 7C271 is accomplished by placing active LOW signals on CS1 and CE, and an active HIGH on CS2. Reading the 7C274 is accomplished by placing active LOW signals on OE and CE. The contents of the memory location addressed by the address lines  $(A_0 - A_{14})$ will become available on the output lines  $(O_0 - O_7)$ .

#### **Selection Guide**

|                                |          | 7C271-30<br>7C274-30 | 7C271-35<br>7C274-35 | 7C271-45<br>7C274-45 | 7C271-55<br>7C274-55 |

|--------------------------------|----------|----------------------|----------------------|----------------------|----------------------|

| Maximum Access Time            | e (ns)   | 30                   | 35                   | 45                   | 55                   |

| Maximum Operating Current (mA) | Com'l    | 120                  | 120                  | 120                  | 120                  |

|                                | Military |                      | 130                  | 130                  | 130                  |

| Standby Current (mA)           | Com'l    | 30                   | 30                   | 30                   | 30                   |

|                                | Military |                      | 40                   | 40                   | 40                   |

**Maximum Ratings**

(Above which the useful life may be impaired. For user guidelines, not tested.)

Storage Temperature ..... - 65°C to +150°C

Ambient Temperature with

Power Applied ...... – 55°C to +125°C Supply Voltage to Ground Potential . . . . . - 0.5V to +7.0V

DC Voltage Applied to Outputs in High Z State . . . . . . . . - 0.5V to +7.0V DC Input Voltage ..... -3.0V to +7.0V

Static Discharge Voltage .....>2001V (per MIL-STD-883, Method 3015)

Electrical Characteristics O

Latch-Up Current ......>200 mA

#### **Operating Range**

| Range                     | Ambient<br>Temperature | v <sub>cc</sub> |

|---------------------------|------------------------|-----------------|

| Commercial                | 0°C to +70°C           | 5V ±10%         |

| Industrial <sup>[1]</sup> | -40°C to +85°C         | 5V ±10%         |

| Military <sup>[2]</sup>   | -55°C to +125°C        | 5V ±10%         |

|                   |                                             |                                                  |            |          | , 35, 45, 55<br>, 35, 45, 55 |    |

|-------------------|---------------------------------------------|--------------------------------------------------|------------|----------|------------------------------|----|

| Parameter         | Description                                 | Test Condition                                   | Min.       | Max.     | Unit                         |    |

| V <sub>OH</sub>   | Output HIGH Voltage                         | $V_{CC} = Min., I_{OH} = -2.0 \text{ m/s}$       | A          | 2.4      |                              | V  |

| V <sub>OL</sub>   | Output LOW Voltage                          | $V_{CC} = Min., I_{OL} = 8.0 \text{ mA}^{[4]}$   |            |          | 0.4                          | V  |

| $V_{\mathrm{IH}}$ | Input HIGH Level                            | Guaranteed Input Logical H.<br>All Inputs        | 2.0        | $V_{CC}$ | V                            |    |

| V <sub>IL</sub>   | Input LOW Level                             | Guaranteed Input Logical LO<br>Inputs            |            | 0.8      | V                            |    |

| I <sub>IX</sub>   | Input Current                               | $GND \le V_{IN} \le V_{CC}$                      | - 10       | +10      | μA                           |    |

| I <sub>OZ</sub>   | Output Leakage Current                      | $GND \le V_{OUT} \le V_{CC}$ , Output Disabled   |            | -40      | +40                          | μA |

| I <sub>OS</sub>   | Output Short Circuit Current <sup>[5]</sup> | $V_{CC} = Max., V_{OUT} = GND$                   |            | -20      | -90                          | mA |

| $I_{CC}$          | Power Supply Current                        | $V_{CC} = Max., V_{IN} = 2.0V,$                  | Commercial |          | 120                          | mA |

|                   |                                             | $I_{OUT} = 0 \text{ mA}, \overline{CE} = V_{IL}$ | Military   |          | 130                          | 1  |

| $I_{SB}$          | Standby Supply Current                      | $V_{CC} = Max., \overline{CE} = V_{IH},$         | Commercial |          | 30                           | mA |

|                   |                                             | $I_{OUT} = 0 \text{ mA}$                         | Military   |          | 40                           |    |

| V <sub>PP</sub>   | Programming Supply Voltage                  |                                                  |            | 12       | 13                           | V  |

| Ipp               | Programming Supply Current                  |                                                  |            |          | 50                           | mA |

| $V_{IHP}$         | Input HIGH Programming Voltage              |                                                  |            | 3.0      |                              | V  |

| V <sub>ILP</sub>  | Input LOW Programming Voltage               |                                                  |            |          | 0.4                          | V  |

#### Capacitance<sup>[6]</sup>

| Parameter        | Description        | Test Conditions                              | Max. | Unit |

|------------------|--------------------|----------------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance  | $T_A = 25^{\circ} C$ , $f = 1 \text{ MHz}$ , | 10   | pF   |

| C <sub>OUT</sub> | Output Capacitance | $V_{CC} = 5.0V$                              | 10   | pF   |

- Contact a Cypress representative for information on industrial temperature range specifications.

- $T_{\Lambda}$  is the "instant on" case temperature.

- See the last page of this specification for Group A subgroup testing information.

- 6.0 mA military

- 5. For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

- See Introduction to CMOS PROMs in this Data Book for general information on testing.

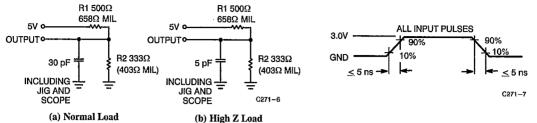

#### AC Test Loads and Waveforms<sup>[6]</sup>

Equivalent to:

THÉVENIN EQUIVALENT

$200\Omega$ 2.00V COMMERCIAL

$250\Omega$ **OUTPUT** o 1.90V MILITARY

C271-8

Switching Characteristics Over the Operating Range[3, 6]

|                   |                                                                                                          | 7C271-<br>7C274- |      |          |      | 7C271-45<br>7C274-45 |          | 7C271-55<br>7C274-55 |      |      |  |

|-------------------|----------------------------------------------------------------------------------------------------------|------------------|------|----------|------|----------------------|----------|----------------------|------|------|--|

| Parameter         | Description                                                                                              | Min.             | Max. | Min.     | Max. | Min.                 | Max.     | Min.                 | Max. | Unit |  |

| t <sub>AA</sub>   | Address to Output Valid                                                                                  |                  | 30   |          | 35   |                      | 45       |                      | 55   | ns   |  |

| t <sub>HZCS</sub> | Chip Select Inactive to High $Z(\overline{CS}_1 \text{ and } CS_2, 7C271 \text{ Only})$                  |                  | 20   |          | 25   |                      | 30       |                      | 30   | ns   |  |

| t <sub>ACS</sub>  | Chip Select Active to Output Valid ( $\overline{\text{CS}}_1$ and $\overline{\text{CS}}_2$ , 7C271 Only) |                  | 20   |          | 25   |                      | 30       |                      | 30   | ns   |  |

| t <sub>HZOE</sub> | Output Enable Inactive to High Z (OE, 7C274 Only)                                                        |                  | 20   | <u> </u> | 20   |                      | 25       |                      | 25   | ns   |  |

| t <sub>OE</sub>   | Output Enable Active to Output Valid (OE, 7C274 Only)                                                    |                  | 20   |          | 20   |                      | 25       |                      | 25   | ns   |  |

| t <sub>HZCE</sub> | Chip Enable Inactive to High Z (CE Only)                                                                 |                  | 35   |          | 40   |                      | 50       |                      | 60   | ns   |  |

| t <sub>ACE</sub>  | Chip Enable Active to Output Valid (CE Only)                                                             |                  | 35   |          | 40   |                      | 50       |                      | 60   | ns   |  |

| t <sub>PU</sub>   | Chip Enable Active to Power Up                                                                           | 0                |      | 0        |      | 0                    |          | 0                    |      | ns   |  |

| t <sub>PD</sub>   | Chip Enable Inactive to Power Down                                                                       |                  | 35   |          | 40   |                      | 50       |                      | 60   | ns   |  |

| t <sub>OH</sub>   | Output Hold from Address Change                                                                          | 0                |      | 0        |      | 0                    | <b> </b> | 0                    |      | ns   |  |

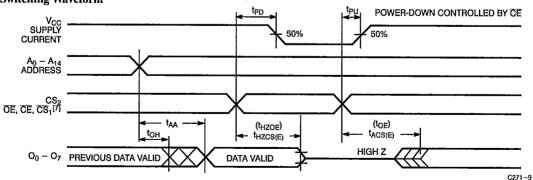

#### **Switching Waveform**

Note: 7.  $CS_2$  and  $\overline{CS_1}$  are used on the 7C271 only.  $\overline{OE}$  is used on the 7C274 only.

#### **Erasure Characteristics**

Wavelengths of light less than 4000 angstroms begin to erase the 7C271 and 7C274 in the windowed package. For this reason, an opaque label should be placed over the window if the PROM is exposed to sunlight or fluorescent lighting for extended periods of time.

The recommended dose of ultraviolet light for erasure is a wavelength of 2537 angstroms for a minimum dose (UV intensity × exposure time) of 25 Wsec/cm<sup>2</sup>. For an ultraviolet lamp with a 12 mW/cm<sup>2</sup> power rating, the exposure time would be approximately 35 minutes. The 7C271 or 7C274 needs to be within 1 inch of the lamp during erasure. Permanent damage may result if the PROM is exposed to high-intensity UV light for an extended period of time. 7258 Wsec/cm<sup>2</sup> is the recommended maximum dosage.

#### **Programming Modes**

Programming support is available from Cypress as well as from a number of third-party software vendors. For detailed programming information, including a listing of software packages, please see the PROM Programming Information located at the end of this section. Programming algorithms can be obtained from any Cypress representative.

Table 1. CY7C271 Mode Selection

|        | T                      | 1                                | _,, ,             | Pin Function <sup>[8]</sup>        |                          |                                 |

|--------|------------------------|----------------------------------|-------------------|------------------------------------|--------------------------|---------------------------------|

|        | Read or Output Disable | A <sub>14</sub> A <sub>0</sub>   | CE                | CS <sub>2</sub>                    | $\overline{\text{CS}}_1$ | O <sub>7</sub> - O <sub>0</sub> |

| Mode   | Other                  | A <sub>14</sub> - A <sub>0</sub> | VFY               | PGM                                | V <sub>PP</sub>          | $D_7 - D_0$                     |

| Read   |                        | A <sub>14</sub> - A <sub>0</sub> | $V_{IL}$          | V <sub>IH</sub>                    | $V_{IL}$                 | $O_7 - O_0$                     |

| Power  | Down                   | A <sub>14</sub> - A <sub>0</sub> | $V_{\mathrm{IH}}$ | X                                  | X                        | High Z                          |

| Output | t Disable              | A <sub>14</sub> A <sub>0</sub>   | Х                 | V <sub>IL</sub>                    | X                        | High Z                          |

| Output | t Disable              | $A_{14} - A_0$                   | X                 | X                                  | $V_{IH}$                 | High Z                          |

| Progra | m                      | A <sub>14</sub> - A <sub>0</sub> | $V_{IHP}$         | V <sub>ILP</sub>                   | V <sub>PP</sub>          | $D_7 - D_0$                     |

| Progra | m Verify               | A <sub>14</sub> - A <sub>0</sub> | V <sub>ILP</sub>  | V <sub>IHP</sub> /V <sub>ILP</sub> | V <sub>PP</sub>          | $O_7 - O_0$                     |

| Progra | m Inhibit              | A <sub>14</sub> - A <sub>0</sub> | V <sub>IHP</sub>  | V <sub>IHP</sub>                   | V <sub>PP</sub>          | High Z                          |

| Blank  | Check                  | $A_{14} - A_0$                   | V <sub>ILP</sub>  | V <sub>IHP</sub> /V <sub>ILP</sub> | $V_{PP}$                 | $O_7 - O_0$                     |

Table 2, CY7C274 Mode Selection

|        |                        |                                  |                  | Pin Function <sup>[8]</sup>        | <u> </u>        |             |

|--------|------------------------|----------------------------------|------------------|------------------------------------|-----------------|-------------|

|        | Read or Output Disable | $A_{14} - A_0$                   | ŌĒ               | CE                                 | V <sub>PP</sub> | $O_7 - O_0$ |

| Mode   | Other                  | $A_{14} - A_0$                   | VFY              | PGM                                | V <sub>PP</sub> | $D_7 - D_0$ |

| Read   | . <b>.</b>             | $A_{14} - A_0$                   | V <sub>IL</sub>  | V <sub>IL</sub>                    | Note 9          | $O_7 - O_0$ |

| Output | t Disable              | A <sub>14</sub> - A <sub>0</sub> | V <sub>IH</sub>  | X                                  | X               | High Z      |

| Power  | Down                   | A <sub>14</sub> - A <sub>0</sub> | X                | V <sub>IH</sub>                    | X               | High Z      |

| Progra | m                      | $A_{14} - A_0$                   | V <sub>IHP</sub> | V <sub>ILP</sub>                   | V <sub>PP</sub> | $D_7 - D_0$ |

| Progra | m Verify               | A <sub>14</sub> - A <sub>0</sub> | V <sub>ILP</sub> | V <sub>IHP</sub> /V <sub>ILP</sub> | V <sub>PP</sub> | $O_7 - O_0$ |

| Progra | m Inhibit              | A <sub>14</sub> - A <sub>0</sub> | V <sub>IHP</sub> | V <sub>IHP</sub>                   | V <sub>PP</sub> | High Z      |

| Blank  | Check                  | $A_{14} - A_0$                   | V <sub>ILP</sub> | V <sub>IHP</sub> /V <sub>ILP</sub> | $V_{PP}$        | $O_7 - O_0$ |

Notes:

<sup>8.</sup> X can be VIL (VILP) or VIH (VIHP).

<sup>9.</sup>  $V_{PP}$  should be tied to  $V_{CC} \pm 5\%$  in read mode.

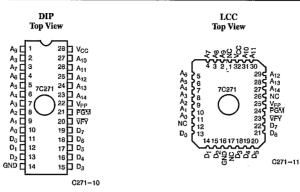

Figure 1. Programming Pinouts

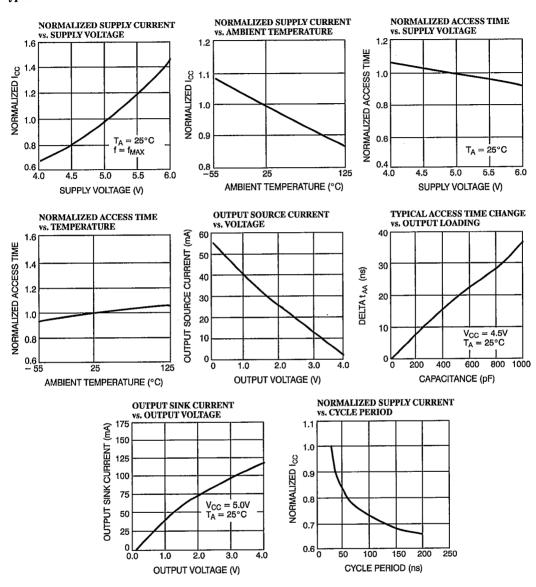

Typical DC and AC Characteristics

C271-14

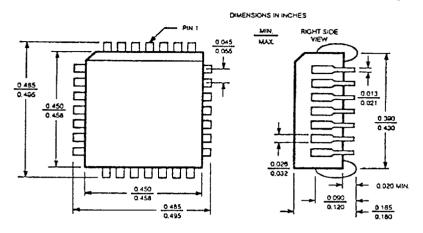

#### Ordering Information[10]

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                      | Operating<br>Range |

|---------------|---------------|-----------------|---------------------------------------------------|--------------------|

| 30            | CY7C271-30JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C271-30PC  | P21             | 28-Lead (300-Mil) Molded DIP                      |                    |

|               | CY7C271-30WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

| 35            | CY7C271-35JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C271-35PC  | P21             | 28-Lead (300-Mil) Molded DIP                      |                    |

|               | CY7C271-35WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

|               | CY7C271-35DMB | D22             | 28-Lead (300-Mil) CerDIP                          | Military           |

|               | CY7C271-35KMB | K74             | 28-Lead Rectangular Cerpack                       |                    |

|               | CY7C271-35LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier          |                    |

|               | CY7C271-35QMB | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier |                    |

|               | CY7C271-35WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

| 45            | CY7C271-45JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C27145PC   | P21             | 28-Lead (300-Mil) Molded DIP                      |                    |

|               | CY7C271-45WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

|               | CY7C271-45DMB | D22             | 28-Lead (300-Mil) CerDIP                          | Military           |

|               | CY7C271-45KMB | K74             | 28-Lead Rectangular Cerpack                       |                    |

|               | CY7C271-45LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier          |                    |

|               | CY7C271-45QMB | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier |                    |

|               | CY7C271-45TMB | T74             | 28-Lead Windowed Cerpack                          |                    |

|               | CY7C271-45WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

| 55            | CY7C271-55JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C271-55PC  | P21             | 28-Lead (300-Mil) Molded DIP                      |                    |

|               | CY7C271-55WC  | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

|               | CY7C271-55DMB | D22             | 28-Lead (300-Mil) CerDIP                          | Military           |

|               | CY7C271-55KMB | K74             | 28-Lead Rectangular Cerpack                       |                    |

|               | CY7C271-55LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier          |                    |

|               | CY7C271-55QMB | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier |                    |

|               | CY7C271-55TMB | T74             | 28-Lead Windowed Cerpack                          |                    |

|               | CY7C271-55WMB | W22             | 28-Lead (300-Mil) Windowed CerDIP                 |                    |

Note:

10. Most of these products are available in industrial temperature range.

Contact a Cypress representative for specifications and product availability.

#### Ordering Information<sup>[10]</sup> (continued)

| Speed<br>(ns) | Ordering Code | Package<br>Name | Package Type                                      | Operating<br>Range |

|---------------|---------------|-----------------|---------------------------------------------------|--------------------|

| 30            | CY7C274-30JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C274-30PC  | P15             | 28-Lead (600-Mil) Molded DIP                      |                    |

|               | CY7C274-30WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP                 |                    |

| 35            | CY7C274-35JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C274-35PC  | P15             | 28-Lead (600-Mil) Molded DIP                      | 1                  |

|               | CY7C274-35WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP                 | ]                  |

|               | CY7C274-35DMB | D16             | 28-Lead (600-Mil) CerDIP                          | Military           |

|               | CY7C274-35KMB | K74             | 28-Lead Rectangular Cerpack                       | ]                  |

|               | CY7C27435LMB  | L55             | 32-Pin Rectangular Leadless Chip Carrier          |                    |

|               | CY7C27435QMB  | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier | 1                  |

|               | CY7C274-35TMB | T74             | 28-Lead Windowed Cerpack                          | 1                  |

|               | CY7C274-35WMB | W16             | 28-Lead (600-Mil) Windowed CerDIP                 | 1                  |

| 45            | CY7C274-45JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C274-45PC  | P15             | 28-Lead (600-Mil) Molded DIP                      | 1                  |

|               | CY7C274-45WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP                 |                    |

|               | CY7C274-45DMB | D16             | 28-Lead (600-Mil) CerDIP                          | Military           |

|               | CY7C274-45KMB | K74             | 28-Lead Rectangular Cerpack                       | 1                  |

|               | CY7C274-45LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier          | 1                  |

|               | CY7C274-45QMB | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier |                    |

|               | CY7C274-45TMB | T74             | 28-Lead Windowed Cerpack                          |                    |

|               | CY7C274~45WMB | W16             | 28-Lead (600-Mil) Windowed CerDIP                 | ]                  |

| 55            | CY7C274-55JC  | J65             | 32-Lead Plastic Leaded Chip Carrier               | Commercial         |

|               | CY7C274-55PC  | P15             | 28-Lead (600-Mil) Molded DIP                      |                    |

|               | CY7C274-55WC  | W16             | 28-Lead (600-Mil) Windowed CerDIP                 |                    |

|               | CY7C274-55DMB | D16             | 28-Lead (600-Mil) CerDIP                          | Military           |

|               | CY7C274-55KMB | K74             | 28-Lead Rectangular Cerpack                       |                    |

|               | CY7C274-55LMB | L55             | 32-Pin Rectangular Leadless Chip Carrier          |                    |

|               | CY7C274-55QMB | Q55             | 32-Pin Windowed Rectangular Leadless Chip Carrier |                    |

|               | CY7C274-55TMB | T74             | 28-Lead Windowed Cerpack                          |                    |

|               | CY7C274-55WMB | W16             | 28-Lead (600-Mil) Windowed CerDIP                 |                    |

## MILITARY SPECIFICATIONS Group A Subgroup Testing

#### **DC Characteristics**

| Parameter         | Subgroups |

|-------------------|-----------|

| V <sub>OH</sub>   | 1, 2, 3   |

| $V_{OL}$          | 1, 2, 3   |

| $V_{\mathrm{IH}}$ | 1, 2, 3   |

| V <sub>II</sub>   | 1, 2, 3   |

| $I_{IX}$          | 1, 2, 3   |

| I <sub>OZ</sub>   | 1, 2, 3   |

| $I_{CC}$          | 1, 2, 3   |

| $I_{SB}$          | 1, 2, 3   |

#### **Switching Characteristics**

| Parameter              | Subgroups       |

|------------------------|-----------------|

| t <sub>AA</sub>        | 7, 8, 9, 10, 11 |

| t <sub>ACS1</sub> [11] | 7, 8, 9, 10, 11 |

| t <sub>OE</sub> [12]   | 7, 8, 9, 10, 11 |

| t <sub>ACE</sub>       | 7, 8, 9, 10, 11 |

11. 7C274 and 7C271 (CS2, CS3 and CS4 only).

12. 7C271 only.

#### **SMD Cross Reference**

| SMD<br>Number | Suffix | Cypress<br>Number |

|---------------|--------|-------------------|

| 5962-89817    | 01XX   | CY7C271-55WMB     |

| 5962-89817    | 01YX   | CY7C271-55TMB     |

| 5962-89817    | 01ZX   | CY7C271-55QMB     |

| 5962-89817    | 02XX   | CY7C271-45WMB     |

| 5962-89817    | 02YX   | CY7C271-45TMB     |

| 5962-89817    | 02ZX   | CY7C271-45QMB     |

Document #: 38-00068-G

T-90-20

# PLCC and CLCC Packaging for High-Speed Parts

The semiconductor industry is constantly searching for package options that enhance the capabilities of high-performance devices. For fast device performance with minimal ground bounce, electrical characteristics must include low inductance and capacitance from external pin to die bond-wire pad. A package should also furnish good thermal characteristics for reliability over extended temperature ranges.

Other major properties sought after are low cost, as well as standardized outline/pin configurations for compatibility, ease of manufacturing, and handling throughput. The package must also work with surface mount technology and have a small footprint to save board space.

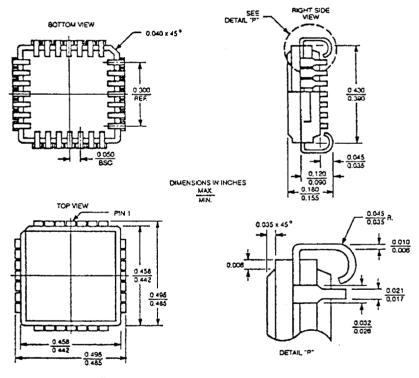

The package that best meets all these requirements is the PLCC (plastic leaded chip carrier). In the past, utilization of PLCCs was not practical for high-power, bipolar devices. However, the advent of low-power bipolar and BiCMOS ECL-compatible SRAMs and PLDs now provides the opportunity for high-volume usage. As manufacturers switch from bipolar to BiCMOS, the lower power dissipation of high-density ECL SRAMs and complex PLDs promise to give PLCC packages a bright future. For military applications and extended temperature environments or for devices with higher power dissipation, you can substitute the CLCC (ceramic leaded chip carrier).

The PLCC has many desirable qualities:

- Suitable for surface mounting with J-type leads

- Small footprint to save board space

- Low inductance and capacitance for high speed with little ground-bounce

- Good thermal characteristics for reliability over temperature range

- Ease of manufacturing and handling for production throughput

- Low cost compared to CERDIP, flatpack, LCC

- Standard package outline and pin-configuration compatibility

The PLCC's J-type surface-mount leads have the advantage over gull-wing leads, which are susceptible to

fatigue. J leads also enhance handling ease in test and burn-in fixtures. The PLCC's 1-pF capacitance compares favorably with the 3 and 6 pF for plastic DIPs and CERDIPs, and inductance is equally impressive: 2 nH versus 6 and 11 nH for plastic DIP and CERDIP. Unlike flatpacks, PLCCs are available in standard tooling. PLCCs come in a variety of pin configurations, from 18 to over 200 pins, versus a maximum of 40 pins for plastic DIPs.

#### The Ceramic Leaded Chip Carrier

For high-temperature environments and high-power devices, you can make use of the ceramic leaded chip carrier (CLCC, Y package), which can also be surface mounted. The Y package has the same footprint and J leads as the PLCC (Figure 1) and works well for the faster PLDs and SRAMs.

If you do not know system temperature in the early stages of a design, you can substitute the Y package for the PLCC and vice versa, so long as the device's die junction temperature does not exceed 150°C. The Y package is slightly more expensive than the PLCC, but with a thermal resistance from junction to ambient ( $\Theta_{JA}$ ) of 35°C/W at 500 LFPM, the Y package can dissipate heat more efficiently.

#### Reliability

Cypress's bipolar and BiCMOS products in PLCC and CLCC packages go through extensive burn-in and testing at elevated temperature to guarantee package integrity. Cypress strongly recommends 500-LFPM system forced air flow but guarantees reliability in systems with or without the flow if the ambient air does not cause the junction temperature (T<sub>J</sub>) to exceed 150°C.

The PLCC's  $\Theta_{JA}$  is approximately 45°C/W. The SRAMs have power dissipation that ranges from 780 mW max for the CY100E422L-5 up to 1097 mW max for the CY10E474L-5. This dissipation results in junction temperature rises from 35 to 49°C. The 16P4-type PLD (CY100E302L-6) has a temperature rise of 39°C, and the

28-Lead Plastic Leaded Chip Carrier J64

T-90-20

28-Pin Ceramic Leaded Chip Carrier Y64

Figure 1. Diagrams of 28-Lead Chip Carriers

T-90-20

#### PLCC and CLCC Packaging

16P8-type PLD (CY10E301L-6) has a temperature rise of 47°C. The CLCC package's  $\Theta_{\rm IA}$  equals 35°C/W for temperature rises of up to 55°C (CY10E474-3).

#### Finding Chip-Level Junction Temperature

The following relationship determines chip-level junction temperature for the PLCC package:

$T_J = \Delta T + T_A$

where

$\Delta T = P_D \times \Theta_{JA}$

and  $\Delta I = FD \wedge$

$\Theta_{JA} = \Theta_{JC} + \Theta_{CS} + \Theta_{SA}$

To calculate worst case junction temperature (Tj) use maximum supply VEE and IEE for power dissipation and maximum TA for the temperature range of interest. For the 10K/10KH CY10E301L in a PLCC, for example, device IEE = 170 mA max and VEE = 5.46V max for PD = 928 mW. Add 15 mW per output for a total output PD = 120 mW. Therefore, the total PD = 1048 mW.

For a PLCC,  $\Theta_{JA} = 45^{\circ}\text{C/W}$  at 500 LFPM, and  $\Theta_{JA} = 64^{\circ}\text{C/W}$  for still air.

For a CLCC,  $\Theta_{JA}$  = 35°C/W at 500 LFPM, and  $\Theta_{JA}$  = 54°C/W for still air.

Because

calculations.

$T_J = total P_D \times \Theta_{JA} + T_A$

and

$T_A = 75$  °C worst-case commercial temperature range, for the PLCC:

$T_J = (1.048 \text{ W})(45^{\circ}\text{C/W}) + 75^{\circ}\text{C} = 122^{\circ}\text{C}$  at 500 LFPM  $T_J = (1.048 \text{ W})(64^{\circ}\text{C/W}) + 75^{\circ}\text{C} = 142^{\circ}\text{C}$  in still air

This calculation is for absolute worst-case data sheet conditions. The burn-in temperature used by Cypress (TJ) is much higher than the device will ever see in a system. Note that most systems will not run at worst case due to guard-banding. For this reason, use Veenom = 5.2V or 4.5V and IEENOM = (IEEMAX)(85%) for nominal-condition

#### Real-World Values

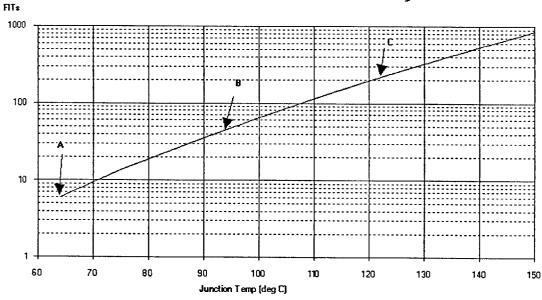

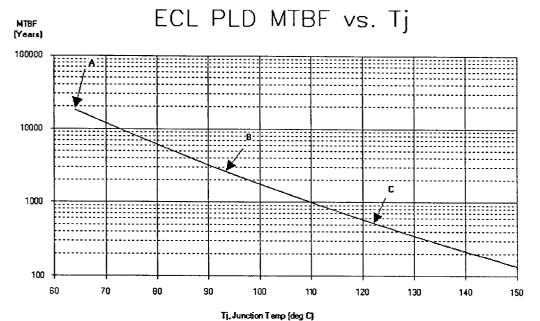

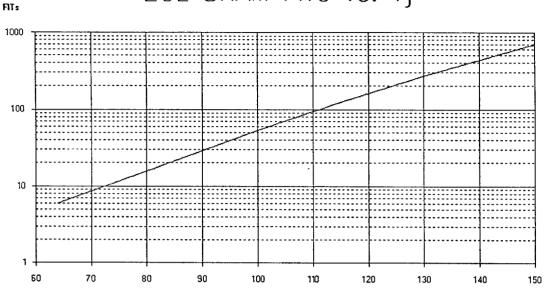

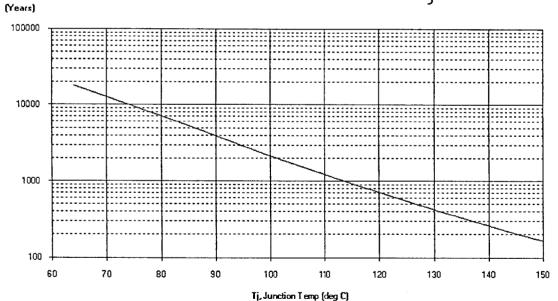

Obviously, most systems do not operate at the worstcase conditions. Therefore, Figures 2 through 5 show graphs over different operating conditions to determine failures in time (FITs) and mean time between failure (MTBF) for a typical system or in a worst-case scenario. The graphs are based on a linear method of interpreting the failures observed at burn-in and indicate the longterm reliability of Cypress devices. You can use the graphs to determine MTBF and FITs for any Cypress device in any package after calculating the appropriate AT.

The X-axis on the graphs indicates junction temperature. These values are determined by adding the  $\Delta T$  to ambient temperature, as described earlier. As an example, Figures 2 and 3 note the following critical points for a CY10E301L ECL PLD under three different operating conditions:

- Point A 10K/10KH typical data sheet conditions: 25°C ambient, nominal VEE and IEE, 50Ω loads, 500 LFPM air flow, T<sub>J</sub> = 64°C, FITs = 7, MTBF = 18,000 yrs.

- Point B 10K/10KH typical operating conditions:

55°C ambient, nominal VEE and IEE, 50Ω loads, 500 LFPM air flow, T<sub>J</sub> = 94°C, FITs = 45, MTBF = 2800 yrs.

- Point C 10K/KH absolute worst-case conditions: 75°C ambient, 5.46 V max and 170 mA max, 50Ω loads, 500 LFPM air flow, T<sub>J</sub> = 122°C, FiTs = 225, MTBF = 525 yrs.

The activation energy used for the MTBF and FITs information is 0.7 eV. This is an average number for diesurface-related defects, such as metal and oxide pinholes, etc., but is very conservative for silicon defects or mechanical interfaces to packages. The number is usually 1.0 eV. A small change here results in a significant change in MTBF or FITs. A change to 0.8 eV equates to a 33% reduction in FITs rate or a 50% increase in MTBF.

#### The Packages of Choice

The PLCC and CLCC are accepted as the packages of choice by many manufacturers of high-speed devices. Motorola Semiconductor uses the PLCC as the only package for the company's very high speed ECLINPS ECL logic family, which stands for "ECL in picoseconds" and is pronounced "eclipse." This family has set-up times and propagation delays in the sub-nanosecond range, with power dissipation of over 1W. Fully compatible with Cypress SRAMs and PLDs, the ECLINPS family includes many 10K, 10KH, and 100K standard logic gates, building blocks, and transceivers.

### PLCC and CLCC Packaging

T-90-20

# ECL PLD FITs vs. Tj

Figure 2. Failures in Time vs Junction Temperature

Figure 3. Mean Time Between Failures vs Junction Temp.

MTBF

#### PLCC and CLCC Packaging

T-90-20

## ECL SRAM FITs vs. Tj

Tj. Junction Temp (deg C)

Figure 4. Failures in Time vs Junction Temperature

# ECL SRAM MTBF vs. Tj

Figure 5. Mean Time Between Failure vs Junction Temp.