T-46-19-09

#### • PROGRAMMABLE HIGH DENSITY LOGIC

- Member of Lattice's pLSI Family

- High Speed Global Interconnects

- 32 VO Pins, Four Dedicated Inputs

- 96 Registers

- Wide Input Gating for Fast Counters, State Machines, Address Decoders, etc.

- Small Logic Block Size for Random Logic

- Security Cell Prevents Unauthorized Copying

#### • HIGH PERFORMANCE E2CMOS2 TECHNOLOGY

- fmax = 80 MHz Maximum Operating Frequency

- tpd = 15 ns Propagation Delay

- TTL Compatible Inputs and Outputs

- --- Electrically Erasable and Re-Programmable

- --- 100% Tested

#### • COMBINES EASE OF USE AND THE FAST SYSTEM SPEED OF PLDs WITH THE DENSITY AND FLEX-**IBILITY OF FIELD PROGRAMMABLE GATE ARRAYS**

- Complete Programmable Device can Combine Glue Logic and Structured Designs

- 100% Routable at 80% Utilization

- Three Dedicated Clock Input Pins Synchronous and Asynchronous Clocks

- Flexible Pin Placement

- Optimized Global Routing Pool Allows Global Interconnectivity

#### . pLSI/spLSIM DEVELOPMENT SYSTEM (pDSIM)

- Boolean Logic Compiler

- Automatic Place and Route

- Manual Partitioning

- PC Platform

- Easy to Use Windows Interface

#### • ADVANCED pLSiispLSI DEVELOPMENT SYSTEM

- Industry Standard, Third Party Design Environments

- Schematic Capture

- Fully Automatic Partitioning

- Automatic Place and Route

- Comprehensive Logic and Timing Simulation

- PC and Workstation Platforms

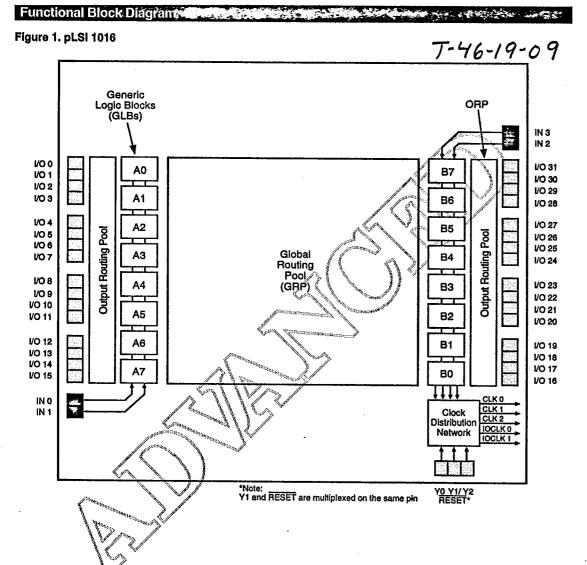

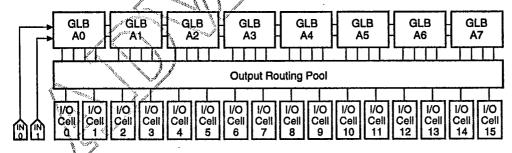

#### Functional Block Diagram

#### Description

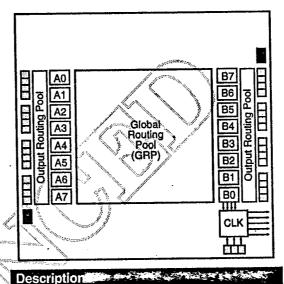

The Lattice pLSI 1016 is a High Density Programmable Logic Device which contains 96 Registers, 32 Universal I/O pins, four Dedicated Input Pins, three Dedicated Clock Input Pins and a Global Routing Pool (GRP). The GRP provides complete interconnectivity between all of these elements.

The basic unit of logic on the pLSI 1016 device is the Generic Logic Block (GLB). The GLBs are labeled A0, A1 ..B7, (see figure 1). There are a total of 16 GLBs in the pLSI 1016 device. Each GLB has 18 inputs, a programmable AND/OR/Exclusive OR array, and four outputs which can be configured to be either combinatorial or registered. Inputs to the GLB come from the GRP. All of the GLB outputs are brought back into the GRP so that they can be connected to the inputs of any other GLB on the device.

Copyright © 1991 Lattice Semiconductor Corp. GAL®, E\*CMOS®, and UkraMOS® are registered trademarks of Lattice Semiconductor Corp. pLStra, lapLStra, pDSra and Generic Array Logicia are trademarks of Lattice Semiconductor Corp. The specifications and information herein are subject to change without notice.

January 1992. Rev. A

LATTICE SEMICONDUCTOR CORP., 5555 Northeast Moore Ct., Hillsboro, Oregon 97124, U.S.A. Tel. 1-800-LATTICE (528-8423); FAX (503) 681-3037

LATTICE SEMICONDUCTOR

46E D 5386949 0001465 8 53LAT

LATTICE SEMICONDUCTOR

46E D 386949 0001466 T MLAT

#### Description (continued)

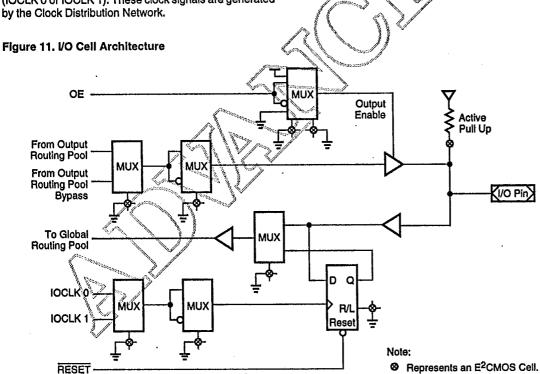

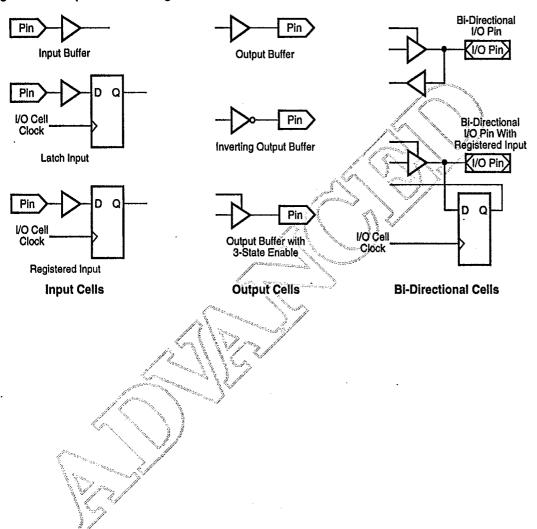

The device also has 32 I/O Cells, each of which is directly connected to an I/O pin. Each I/O cell can be individually programmed to be a combinatorial input, registered input, latched input, output or bi-directional I/O pin with 3-state. The signal levels are TTL compatible voltages and the output drivers can source 4 mA or sink 8 mA.

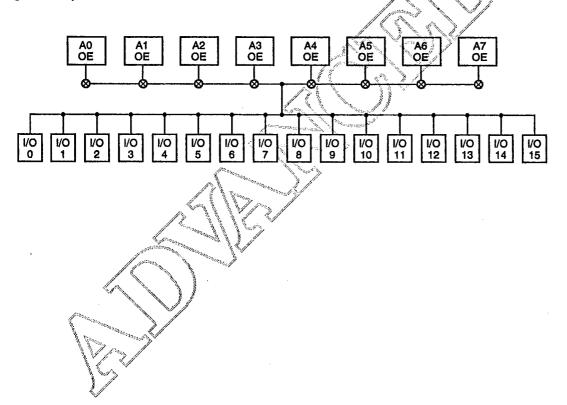

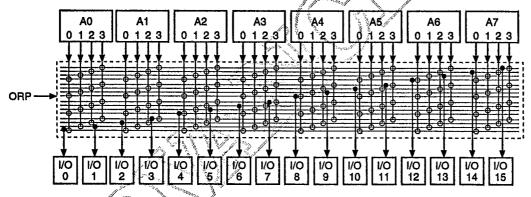

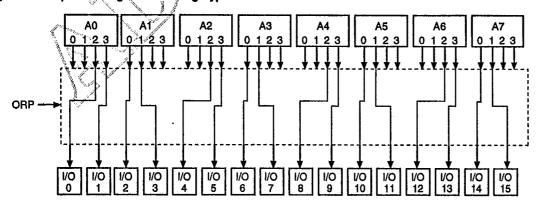

The 32 I/O Cells are grouped into two sets of 16 each as shown in figure 1. Each of these I/O groups is associated with a logic Megablock through the use of the Output Routing Pool (ORP) and shares a common Output Enable (OE) signal.

Eight GLBs, 16 I/O Cells and one ORP are connected together to make a logic Megablock. The Megablock is defined by the resources that it shares. The outputs of the eight GLBs are connected to a set of 16 universal I/O cells by the ORP. The pLSI 1016 Device contains two of these Megablocks.

The GRP has as its inputs the outputs from all of the GLBs and all of the inputs from the bi-directional I/O cells. All of these signals are made available to the inputs of the GLBs. Delays through the GRP have been equalized to minimize timing skew and logic glitching.

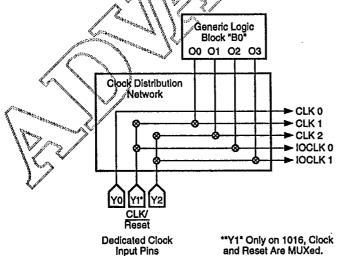

Clocks in the pLSI 1016 device are selected using the Clock Distribution Network. Three dedicated clock pins (Y0 to Y2) are brought into the distribution network, and five outputs (CLK 0 to CLK 2 and IOCLK 0, IOCLK 1) are provided to route clocks to the GLBs and I/O cells. The Clock Distribution Network can also be driven from a special GLB (B0 on the pLSI 1016 device). The logic of this GLB allows the user to create an internal clock from a combination of internal signals within the device.

The pLSI 1016 device is part of Lattice's programmable Large Scale Integration (pLSI) family. This family contains a range of devices from the pLSI 1016, with 96 registers, to the pLSI 1048 with 288 registers. The pLSI Family Product Selector Guide below lists key attributes of the devices along with the number of resources available.

4.4

#### pLSI Family Product Selector Guide

| DEVICE           | pLSI 1016 | pLSI 1024 | pLSI 1032 | pLSI 1048 |

|------------------|-----------|-----------|-----------|-----------|

| GLBs             | 76.       | 24        | 32        | 48        |

| Registers        | 96        | 144       | 192       | 288       |

| VO Pins          | 32        | 48        | 64        | 96        |

| Dedicated Inputs | 4         | 6         | 8         | 10        |

| Pin Count        | 44        | 68        | 84        | 120       |

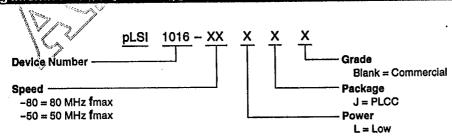

#### Ordering Information

LATTICE SEMICONDUCTOR

46E D

5386949 0001467 1 MMLAT

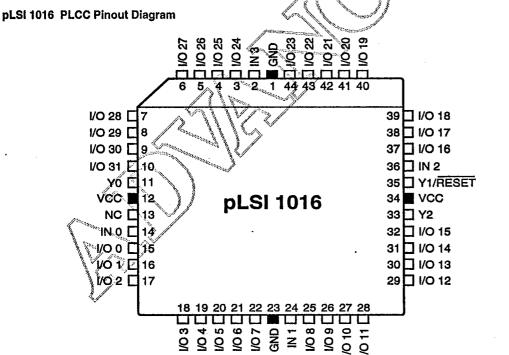

### Pin Description

| Name                                                                                                                                            | PLC                                          | C Pin                                        | Num                                          | bers                                         | Description                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V/O 0 - V/O 3<br>V/O 4 - V/O 7<br>V/O 8 - V/O 11<br>V/O 12 - V/O 15<br>V/O 16 - V/O 19<br>V/O 20 - V/O 23<br>V/O 24 - V/O 27<br>V/O 28 - V/O 31 | 15,<br>19,<br>25,<br>29,<br>37,<br>41,<br>3, | 16,<br>20,<br>26,<br>30,<br>38,<br>42,<br>4, | 17,<br>21,<br>27,<br>31,<br>39,<br>43,<br>5, | 18,<br>22,<br>28,<br>32,<br>40,<br>44,<br>6, | Input/Output Pins - These are the general purpose I/O pins used by the logic array.                                                                                                                                                 |

| IN 0 - IN 3                                                                                                                                     | 14,                                          | 24,                                          | 36,                                          | 2                                            | Dedicated input pins to the device.                                                                                                                                                                                                 |

| Y1/RESET                                                                                                                                        | 11<br>35                                     |                                              |                                              |                                              | Dedicated Clock input. This clock input is connected to one of the clock inputs of all of the GLBs on the device.  This pin performs two functions:  — Dedicated clock input. This clock input is brought into the Clock            |

|                                                                                                                                                 |                                              |                                              |                                              |                                              | Distribution Network, and can optionally be routed to any GLB and/or I/O Cell on the device.  - Active Low (0) Reset pin which resets all of the GLB and I/O registers in the device.                                               |

| Y2                                                                                                                                              | 33                                           |                                              |                                              |                                              | Dedicated Clock input. This clock input is brought into the clock distribution network, and can optionally be routed to any I/O Cell in the device. This is a factory test pin and it should be left floating or tied to $V_{cc}$ . |

| NC .                                                                                                                                            | 13                                           |                                              |                                              | <u> </u>                                     | This is a factory test pin and it should be left floating or tied to V <sub>cc</sub> .                                                                                                                                              |

| GND<br>VCC                                                                                                                                      | 1,<br>12,                                    | 23<br>34                                     | 1                                            |                                              | Ground (GND)                                                                                                                                                                                                                        |

LATTICE SEMICONDUCTOR

46E D = 5386949 0001468 3 = LAT

### Absolute Maximum Ratings

Supply Voltage V<sub>cc</sub>.....-0.5 to +7.0V

Input Voltage Applied. . . . . . . . . -2.5 to V<sub>CC</sub> +1.0V

Off-State Output Voltage Applied . . . . . -2.5 to V<sub>CC</sub> +1.0V

Ambient Temp, with Power Applied .....55 to 125°C

Stresses above those listed under the "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation of the device at these or at any other conditions above those indicated in the operational sections of this specification is not implied (while programming, follow the programming specifications).

#### DC Recommended Operating Condition

| SYMBOL | PARAMETER           |                      | MIN.       | MAX.            | UNITS |

|--------|---------------------|----------------------|------------|-----------------|-------|

| TA     | Ambient Temperature | Annual Marie Comment | <i>d</i> 0 | 70              | °C    |

| Vcc    | Supply Voltage      | La germania          | 4.75       | 5.25            | ٧     |

| VIL    | Input Low Voltage   |                      | 0          | 8.0             | V     |

| VIH    | Input High Voltage  |                      | 2.0        | V <sub>cc</sub> | V     |

#### Capacitance (T=25°C,f=1.0 MHz)

| SYMBOL | PARAMETER          | MAXIMUM <sup>1</sup> | UNITS | TEST CONDITIONS                              |

|--------|--------------------|----------------------|-------|----------------------------------------------|

| C,     | Input Capacitance  | 8                    | pf    | V <sub>cc</sub> =5.0V, V <sub>IN</sub> =2.0V |

| C,     | I/O, Y Gapacitance | 10                   | pf    | V <sub>cc</sub> =5.0V, VI/O, Y=2.0V          |

1. Guaranteed but not 100% tested

#### Data Retention Specifications

| PARAMETER              | MINIMUM | MAXIMUM | UNITS  |

|------------------------|---------|---------|--------|

| Data Retention         | 20      | _       | YEARS  |

| Erase/Reprogram Cycles | -       | 100     | CYCLES |

4

LATTICE SEMICONDUCTOR

46E D

5386949 0001469 5 **M**LAT

### Switching Test Conditions

| Input Pulse Levels             | GND to 3.0V    |

|--------------------------------|----------------|

| Input Rise and Fall Times      | 3ns 10% to 90% |

| Input Timing Reference Levels  | 1.5V           |

| Output Timing Reference Levels | 1.5V           |

| Output Load                    | See Figure 2   |

3-state levels are measured 0.5V from steady-state active level.

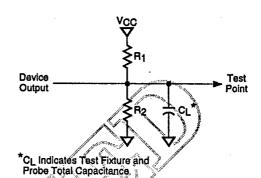

#### Figure 2. Test Load

#### **Output Load Conditions (see figure 2)**

| Tes | t Condition                                   | R1   | R2   | CL   |  |

|-----|-----------------------------------------------|------|------|------|--|

| 1   |                                               | 470Ω | 390Ω | 35pF |  |

| 2   | Active High                                   | ∞    | 390Ω | 35pF |  |

|     | Active Low                                    | 470Ω | 390Ω | 35pF |  |

| 3   | Active High to Z<br>at V <sub>OH</sub> - 0.5V | ∞    | 390Ω | 5pF  |  |

|     | Active Low to Z<br>at V <sub>o.</sub> + 0.5V  | 470Ω | 390Ω | 5pF  |  |

#### DC Electrical Characteristics

#### Over Recommended Operating Conditions

| SYMBOL           | PARAMETER                         | CONDITION                         | MIN. | TYP. | MAX. | UNITS |

|------------------|-----------------------------------|-----------------------------------|------|------|------|-------|

| <b>V</b> OL      | Output Low Voltage                | t <sub>ot.</sub> =8 mA.           | _    |      | 0.4  | ٧     |

| <b>V</b> OH      | Output High Voltage               | l <sub>oн</sub> =-4 mA.           | 2.4  |      | _    | ٧     |

| lı.              | Input or I/O Low Leakage Current  | $0V \le V_{iN} \le V_{iL}$ (MAX.) | -    | _    | -10  | μА    |

| IIH 《            | Input or I/O High Leakage Current | $V_{H} \le V_{H} \le V_{CC}$      | -    | _    | 10   | μА    |

| los <sup>1</sup> | Quiput Short Circuit Current      | $V_{cc} = 5V, V_{out} = 0.5V$     | -60  | _    | -200 | mA    |

| ICC <sup>2</sup> | Operating Power Supply Current    | $V_{K} = 0.5V, V_{H} = 3.0V$      | _    | _    | _    | mA    |

|                  |                                   | $F_{TOGGLE} = 20 MHz$             | 1    |      | ĺ    |       |

1. One output at a time for a maximum duration of one second. (Vout = 0.5V)

2. Measured at a frequency of 20 MHz using four 16-bit counters.

LATTICE SEMICONDUCTOR

46E D

5386949 0001470 1 MILAT

### External Switching Characteristics 1223

#### pLSF 1016-80\*

#### **Over Recommended Operating Conditions**

| PARAMETER    | TEST 6<br>COND. | #  | DESCRIPTION                                    | MIN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TYP. | MAX. | UNITS |

|--------------|-----------------|----|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|

| <b>t</b> pd1 | 1               | 1  | Data Propagation Delay, 4PT bypass, ORP bypass |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12   | 15   | ns    |

| tpd2         | 1               | 2  | Data Propagation Delay                         | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15   | 20   | ns    |

| tco15        | 1               | 3  | External Clock to Output Delay, ORP bypass     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8    | 11   | ns    |

| tco25        | 1               | 4  | External Clock to Output Delay                 | e de la companya de l | . 9  | 14   | ns    |

| tco3         | 1               | 5  | Internal Synch. Clock to Output Delay          | ana 🗺                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 15   | 20   | ns    |

| tco4         | 1               | 6  | Asynchronous Clock to Output Delay             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13   | 20   | ns    |

| <b>t</b> r1  | 1               | 7  | External Pin Reset to Output Delay             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13   | 20   | ns    |

| tr2          | 1               | 8  | Asynchronous PT Reset to Output Delay          | <b>\-</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 15   | 22   | ns    |

| <b>t</b> en  | 2               | 9  | Input to Output Enable                         | \&/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 13   | 20   | ns    |

| <b>t</b> dis | 3               | 10 | Input to Output Disable                        | 1-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13   | 20   | ns    |

#### External AC Recommended Operating Conditions 1223 pLSI 1016-80

#### **Over Recommended Operating Conditions**

| PARAMETER         | TEST 6<br>COND. | #     | DESCRIPTION                                            | MIN. | TYP. | MAX.       | UNITS |

|-------------------|-----------------|-------|--------------------------------------------------------|------|------|------------|-------|

| fmax <sup>4</sup> | 1               | 11    | Clock Frequency with Internal Feedback                 | -    | 100  | 80         | MHz   |

| fmax (External)   | 1               | 12    | Clock Frequency with External Feedback                 |      | 70   | 50         | MHz   |

| <b>t</b> su1      | -               | 13    | Setup Time before External Synch. Clock, 4PT bypass    | 9    | 6    | -          | ns    |

| <b>t</b> su2      | -               | 14    | Setup Time before External Synch Clock                 | 12   | 8    | _          | ns    |

| tsu3              | _               | 15    | Setup Time before Internal Synch. Clock                | 9    | 3    | <u> </u>   | ns    |

| tsu4              | -               | 16    | Setup Time before Asynchronous Clock                   | 9    | 4    | _          | ns    |

| <b>t</b> h1       | - ,,            | /17   | Hold time after External Synchronous Clock, 4PT bypass | 2    | -1   | _          | ns    |

| th2               | 120             | 18    | Hold time after External Synchronous Clock             | 2    | -1   | <u> </u> - | ns    |

| th3               | <b>/</b> -      | 19    | Hold time after Internal Synchronous Clock             | 8    | 2    | -          | ns    |

| th4               | -/              | 20    | Hold time after Asynchronous Clock                     | 8    | 1    | -          | ns    |

| trw1              | -               | 21    | External Reset Pulse Duration                          | 10   | 8    |            | ns    |

| trw2              | 2:40 m          | 22    | Asynchronous Reset Pulse Duration                      | 10   | 8    |            | ns    |

| twh1, twl1        | 200,-           | 23,24 | External Synchronous Clock Pulse Duration, High, Low   | 6    | 5    | _          | ns    |

| twh2, twl2        |                 | 25,26 | Asynchronous Clock Pulse Duration, High, Low           | 6    | 5    | -          | ns    |

- 1. External Parameters are tested and guaranteed.

- 2. See Timing Technical Note for further details.

3. Unless noted, all parameters use ORP, GRP fanout of four, PTSA, and are measured with 16 outputs switching.

- 4. Standard 16-bit counter implementation using GRP feedback.

5. Clock to output specifications include a maximum skew of 2 ns.

- 6. Refer to Switching Test Conditions section.

LATTICE SEMICONDUCTOR

46E D

5386949 0001471 3 **E**LAT

pLSF1016-80

### Switching Characteristics 1/2/3

### Using I/O Cell

| PARAMETER    | TEST <sup>4</sup><br>COND. | #     | DESCRIPTION                                  |    | MIN. | TYP. | MAX. | UNITS |

|--------------|----------------------------|-------|----------------------------------------------|----|------|------|------|-------|

| <b>t</b> su5 | _                          | 27    | Setup Time before External Synchronous Clock |    | 5    | 0    | -    | ns    |

| <b>t</b> su6 | _                          | 28    | Setup Time before Internal Synchronous Clock |    | 0    | -3   | T -  | ns    |

| <b>t</b> h5  | _                          | 29    | Hold Time after External Synchronous Clock   |    | 8    | 4    | _    | ns    |

| th6          | _                          | 30    | Hold Time after Internal Synchronous Clock   | 0  | 15   | 11   | _    | ns    |

| twh3, twi3   | _                          | 31,32 | Clock Pulse Duration, High, Low              | 10 | 6 %  | 5    | _    | ns    |

External Parameters are tested and guaranteed.

See Timing Technical Note for further details.

3. Unless noted, all parameters use ORP, GRP fanout of four, PTSA, and are measured with 16 outputs switching.

4. Refer to Switching Test Conditions section.

1/92. Rev. A

LATTICE SEMICONDUCTOR

46E D

5386949 0001472 5 **E**LAT

pLSI-1016-50

### External Switching Characteristics 15,2,3 **Over Recommended Operating Conditions**

| PARAMETER                 | TEST 6<br>COND. | #  | DESCRIPTION                                    | MIN.                       | TYP.    | MAX. | UNITS |

|---------------------------|-----------------|----|------------------------------------------------|----------------------------|---------|------|-------|

| tpd1                      | 1               | 1  | Data Propagation Delay, 4PT bypass, ORP bypass |                            | 16      | 20   | ns    |

| tpd2                      | 1               | 2  | Data Propagation Delay, ORP                    | _                          | 19      | 25   | ns    |

| tco15                     | 1               | 3  | External Clock to Output Delay, ORP bypass     | -                          | 12      | 16   | ns    |

| <b>t</b> co2 <sup>5</sup> | 1               | 4  | External Clock to Output Delay                 | e pro <del>cess</del> ions | <u></u> | 20   | ns    |

| tco3                      | 1               | 5  | Internal Synch. Clock to Output Delay          | ~*/~                       | 21      | 28   | ns    |

| tco4                      | 1               | 6  | Asynchronous Clock to Output Delay             | \                          | 21      | 28   | ns    |

| <b>t</b> r1               |                 | 7  | External Pin Reset to Output Delay             | 1                          | 21      | 28   | ns    |

| tr2                       |                 | 8  | Asynchronous PT Reset to Output Delay          | -                          | /24     | 30   | ns    |

| ten                       | 2               | 9  | Input to Output Enable                         | 2-/                        | 21      | 28   | ns    |

| <b>t</b> dis              | 3               | 10 | Input to Output Disable                        | <b>&gt;</b> -              | 21      | 28   | ns    |

#### pLSI-1016-50 External AG Recommended Operating Conditions 12-3

#### **Over Recommended Operating Conditions**

| PARAMETER         | TEST 6<br>COND. | #     | DESCRIPTION                                            | MIN. | TYP. | MAX.     | UNITS |

|-------------------|-----------------|-------|--------------------------------------------------------|------|------|----------|-------|

| fmax <sup>4</sup> | 1               | 11    | Clock Frequency with Internal Feedback                 |      | 70   | 50       | MHz   |

| fmax (External)   | 1               | 12    | Clock Frequency with External Feedback                 | _    | 45   | 33       | MHz   |

| <b>t</b> su1      | _               | 13    | Setup Time before External Synch. Clock, 4PT bypass    | 14   | 10   | _        | ns    |

| tsu2              | -               | 14    | Setup Time before External Synch Clock                 | 17   | 13   |          | ns    |

| tsu3              |                 | 15    | Setup Time before Internal Synch. Clock                | 13   | 9    |          | ns    |

| tsu4              | _               | 16.   | Setup Time before Asynchronous Clock                   | 13   | 9    | _        | ns    |

| th1               | -,              | °″17  | Hold time after External Synchronous Clock, 4PT bypass | 7    | 3    | _        | ns    |

| th2               | 1/4             | 18    | Hold time after External Synchronous Clock             | 7    | 3    |          | ns    |

| <b>t</b> h3       | <b>√</b> -      | √19   | Hold time after Internal Synchronous Clock             | 11   | 5    | -        | ns    |

| th4               | -7              | 20    | Hold time after Asynchronous Clock                     | 11   | 5    | -        | กร    |

| trw1              |                 | 21    | External Reset Pulse Duration                          | 15   | 13   | <u> </u> | ns    |

| trw2              | 100 to 100      | 22    | Asynchronous Reset Pulse Duration                      | 15   | 13   | <u> </u> | ns    |

| twh1, twl1        | 10-7/           | 23,24 | External Synchronous Clock Pulse Duration, High, Low   | 10   | 8    | -        | ns    |

| twh2, twl2        | T Z             | 25,26 | Asynchronous Clock Pulse Duration, High, Low           | 10   | 8    |          | ns    |

- 1. External Parameters are tested and guaranteed.

- 2. See Timing Technical Note for further details.

3. Unless noted, all parameters use ORP, GRP fanout of four, PTSA, and are measured with 16 outputs switching.

4. Standard 16-bit counter implementation using GRP feedback.

- 5. Clock to output specifications include a maximum skew of 2 ns.

- 6. Refer to Switching Test Conditions section.

## T-46-19-09

### Specifications **pLSI** 1016

LATTICE SEMICONDUCTOR

46E D

TALES 7 5386949 0001473 7 551LAT

#### Switching Characteristics 1 213

#### pLSI 1016-50

### Using I/O Cell

| PARAMETER   | TEST <sup>4</sup><br>COND. | #     | DESCRIPTION                                  |    | MIN. | TYP. | MAX. | UNITS |

|-------------|----------------------------|-------|----------------------------------------------|----|------|------|------|-------|

| tsu5        | _                          | 27    | Setup Time before External Synchronous Clock |    | 10   | 5    | -    | ns    |

| tsu6        |                            | 28    | Setup Time before Internal Synchronous Clock |    | 0    | -5   | -    | ns    |

| <b>t</b> h5 | _                          | 29    | Hold Time after External Synchronous Clock   |    | 12   | 6    | _    | ns    |

| th6         | <b>-</b>                   | 30    | Hold Time after Internal Synchronous Clock   | 1  | 20   | 15   | _    | ns    |

| twh3, twl3  |                            | 31,32 | Clock Pulse Duration, High, Low              | 10 | 10   | 8    | _    | ns    |

External Parameters are tested and guaranteed.

See Timing Technical Note for further details.

Unless noted, all parameters use ORP, GRP fanout of four, PTSA, and are measured with 16 outputs switching.

4. Refer to Switching Test Conditions section.

CARLES CONTRACTOR

LATTICE SEMICONDUCTOR

46E D

5386949 0001474 9 🖼 LAT

#### Architectural Description

### The Generic Logic Block

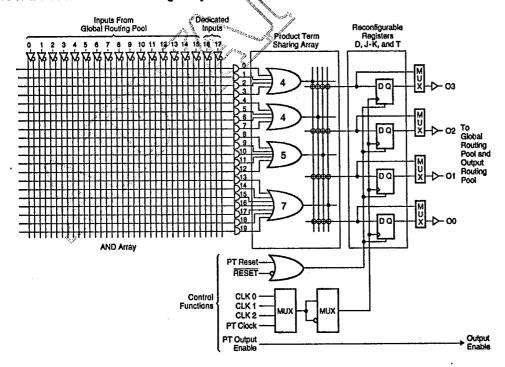

The Generic Logic Block (GLB) is the standard logic block of the Lattice High Density pLSI Device. This GLB has 18 inputs, four outputs and the logic necessary to implement most standard logic functions. The internal logic of the GLB is divided into four separate sections (see figure 3). The AND Array, the Product Term Sharing Array (PTSA), the Reconfigurable Registers, and the Control Functions. The AND array consists of 20 product terms which can produce the logical sum of any of the 18 GLB inputs. Sixteen of the inputs come from the Global Routing Pool, and are either feedback signals from any of the 16 GLBs or inputs from the external I/O Cells. The two remaining inputs come directly from two dedicated input pins. These signals are available to the product terms in both the logical true and the complemented forms which makes boolean logic reduction easier.

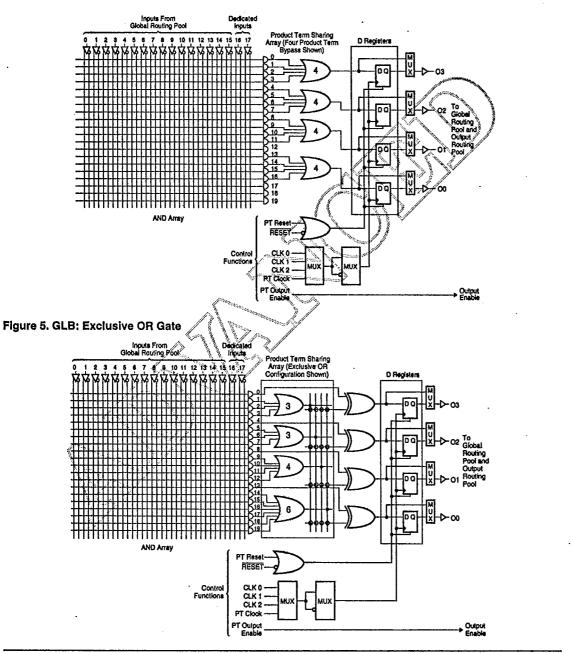

The PTSA takes the 20 product terms and allocates them to the four GLB outputs. There are four OR gates, with four, four, five and seven product terms (see figure 3). The

output of any of these gates can be routed to any of the four GLB outputs, and if more product terms are needed, the PTSA can combine them as necessary. If the users' main concern is speed, the PTSA can use a bypass circuit with four product terms to increase the performance of the cell (see figure 4). This can be done to any or all of the four outputs from the GLB.

The Reconfigurable Registers consist of four D-type flipflops with an Exclusive OR Gate on the input. The Exclusive OR gate in the GLB can be used either as a logic element or to reconfigure the D-type flip-flop to emulate a J-K, or T-type flip-flop (see figure 5). This greatly simplifies the design of counters, comparators and ALU type functions. The registers can be bypassed if the user needs a combinatorial output. Each register output is brought back into the Global Routing Pool and is also brought to the I/O cells via the Output Routing Pool. Reconfigurable registers are not available when the four product term bypass is used.

Figure 3. GLB: Product Term Sharing Array

### T-46-19-09

### Specifications pLSI 1016

LATTICE SEMICONDUCTOR

TALE D 5386949 0001475 0 ELAT

Architectural Description

Figure 4. GLB: Four Product Term Bypass

LATTICE SEMICONDUCTOR 46E D 1888 5386949 0001476 2 1888 LAT

#### Architectural Description

#### The Generic Logic Block (continued)

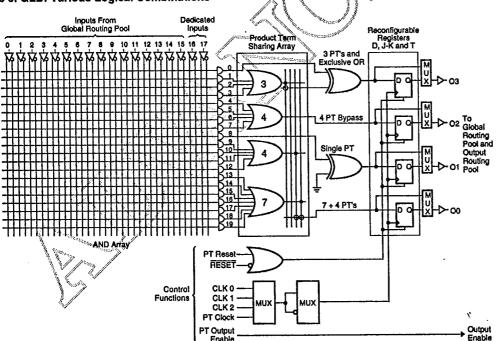

The PTSA is flexible enough to allow these features to be used in virtually any combination that the user desires. In the GLB shown in figure 6, Output Three (O3) is configured using the XOR Gate and Output Two (O2) is configured using the four Product Term Bypass. Output One (O1) uses one of the inputs from the five Product Term OR gate while Output Zero (O0) combines the remaining four product terms with all of the product terms from the seven Product Term OR gate for a total of eleven (7+4).

Various signals which control the operation of the GLB are developed in the Control Function section. The clock for the registers can come from any of three sources developed in

the Clock Distribution Network (See Clock Distribution Network Section) or from a product term within the GLB. The Reset Signal for the GLB can come from the Global Reset pin or from a product term within the block. The Output Enable for the I/O cells associated with the GLB comes from a product term within the block. Use of a product term for a control function makes that product term unavailable for use as a logic term. Refer to the following table to determine which logic functions are affected.

There are many additional features in a GLB which allow implementation of logic intensive functions. These features are accessible using the hard Macros from the software and require no intervention on the part of the user.

25

LATTICE SEMICONDUCTOR

46E D

5386949 0001477 4 **m**lat

#### Architectural Description

#### **Product Term Sharing Matrix**

| Product<br>Term #                | Stand                                 | lard (<br>ulpul                         | Config<br>Num | guration<br>aber                        |    |   | Product Term Single Product Term Output Number |   |   | XOR Function<br>Output Number |        |   |   |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | Alternate<br>Function |      |                    |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------|---------------------------------------|-----------------------------------------|---------------|-----------------------------------------|----|---|------------------------------------------------|---|---|-------------------------------|--------|---|---|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|------|--------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | 3                                     | 2                                       | 1             | 0                                       | 3  | 2 | 1                                              | 0 | 3 | 2                             | 1      | 0 | 3 | 3           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2           | 1                     | 1    | 0                  | 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0<br>1<br>2<br>3                 | #<br>#<br>#                           |                                         |               | **                                      | ** |   |                                                |   |   |                               |        |   |   | =           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | /                     | J pa | gallelle<br>Carace |   | Application of the Control of the Co |

| 4<br>5<br>6<br>7                 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | ======================================= |               | H<br>H<br>H                             |    |   |                                                |   |   | •                             |        |   | 1 |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | \\<br>><br>\\ \       |      | \\<br>\\           |   | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8<br>9<br>10<br>11<br>12         |                                       |                                         | *             | ¥<br>¥<br>¥                             |    |   |                                                |   |   | ,                             | •<br>• | ( |   | <b>&gt;</b> | The second secon | \<br>\<br>\ |                       |      | ,                  |   | <b>■</b> CLK/Rese                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |