**Vishay Siliconix**

100 mA Buck-Boost Regulator Demonstration Board

### FEATURES

- SiP1759 Demonstration Board includes the required components to evaluate the IC's performance

- Easy hook-up to demonstrate performance of the IC, stand alone or in a system

- Charge pump based IC

- 100 mA output

#### DESCRIPTION

The Siliconix SiP1759DB Demonstration Board contains all the circuitry required to demonstrate the fully integrated buck-boost regulator. This demonstration board utilizes the adjustable output voltage version of the SiP1759, while the fixed output version may be preferable in an actual application.

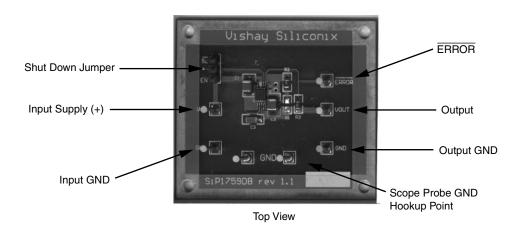

### **DEMONSTRATION BOARD HOOK UP**

### APPLICATIONS

- 1-Cell Li Ion Battery Powered Equipment

- 2- to 3-Cell NiMH Battery Powered Equipment

- 2- to 3-Cell Alkaline Battery Powered Equipment

- Backup Battery Boost Converters

In addition to allowing evaluation of the SiP1759's performance, the layout shows the small amount of PC board area required for implementation.

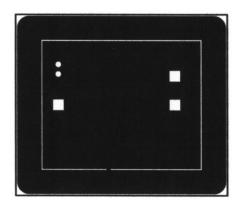

Bottom View

# SiP1759DB

Vishay Siliconix

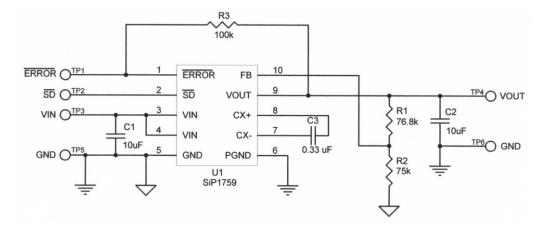

# SCHEMATIC DIAGRAM

### **DEMONSTRATION BOARD OPERATION**

- 1) To use the demo Board, connect a 1.6 to 5.5 V power supply to the Vin (TP3) & GND (TP5) pins.

- Place a jumper between the center and EN pin to enable the regulator's operation. Connecting the center pin to the SD pin with disable or shut down the regulator.

- A Load Resistor or Electronic Load should be connected to the V<sub>OUT</sub> (TP4) & GND (TP6) pins in order to simulate typical loaded conditions for this type of circuit.

| BILL | BILL OF MATERIAL |            |            |                    |           |                  |  |

|------|------------------|------------|------------|--------------------|-----------|------------------|--|

| Item | Qty              | Designator | Part Type  | Description        | Footprint | Manufacturer     |  |

| 1    | 2                | C1, C2     | 10 µF      | Cap, Ceramic, 10 V | 1206      | VISHAY           |  |

| 2    | 1                | C3         | 0.33 μF    | Cap, Ceramic, 10 V | 1206      | VISHAY           |  |

| 3    | 1                | R1         | 76.8 k     | Res Suface Mount   | 1206      | VISHAY/DALE      |  |

| 4    | 1                | R2         | 75 k       | Res Suface Mount   | 1206      | VISHAY/DALE      |  |

| 5    | 1                | R3         | 100 k      | Res Suface Mount   | 1206      | VISHAY/DALE      |  |

| 6    | 1                | U1         | SiP1759DH  | Power IC           | MSOP-10   | VISHAY/SILICONIX |  |

| 7    | 6                | TP1-6      | Test Point | 1 Pin Header       | TP1       | MULTI-SOURCE     |  |

# **CHOICE OF COMPONENTS**

#### **Output Voltage**

The SiP1759 regulated output is set at 2.5 V for shipment. It can be adjusted from 2.5 V to 5.5 V via resistor divider network from  $V_{OUT}$  to GND. R1 and R2 should be kept in the 50 k $\Omega$  to 100 k $\Omega$  range for low power consumption, while maintaining adequate noise immunity. The value R1 is calculated using the following formula:

$$R1 = R2((VOUT/VFB)-1)$$

VFB is nominally 1.235 V.

### **Capacitor Selection**

The value for the  $C_{IN}$  and  $C_{OUT}$  capacitors is 10  $\mu F$  and the value of the  $C_X$  capacitor is 0.33  $\mu F.$

Capacitor selection for  $C_{IN}$ ,  $C_{OUT}$  and CX will have an impact on the voltage output ripple, output current and overall physical size of the circuit.

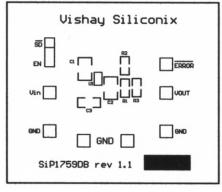

# PRINTED CIRCUIT BOARD

Ceramic capacitors are recommenced for their low ESR, ( $\leq 20 \text{ m}\Omega$ ), which will help keep the output voltage ripple at a minimum.

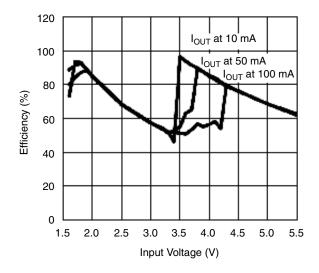

# **Output Voltage Ripple**

The SiP1759 automatically decides whether to be in step up mode or step down mode depending on the  $V_{IN}, V_{OUT}$  and current load conditions, therefore the voltage output ripple will vary. In step-up mode the voltage output ripple is higher than step-down mode. But unless  $V_{IN}$  is significant larger than  $V_{OUT}$  ( $V_{IN} \geq V_{OUT} + 1$  V), in heavy load the IC will slip from buck mode to boost mode as necessary to charge the transfer capacitor and the ripple will increase. Reducing the  $C_X$  capacitor value will cause an increase in the swit-ching frequency and a reduction of the output ripple.

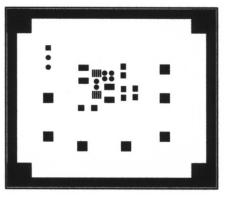

Top Silk Screen

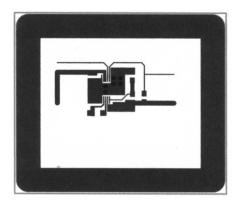

Top Layer

Bottom Layer

# SiP1759DB

Vishay Siliconix

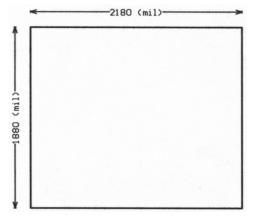

# PRINTED CIRCUIT BOARD

Top Solder Mask

Bottom Solder Mask

Mechanical

SiP1759DB

Vishay Siliconix

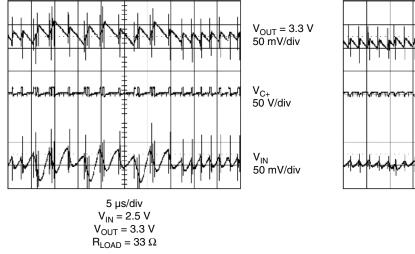

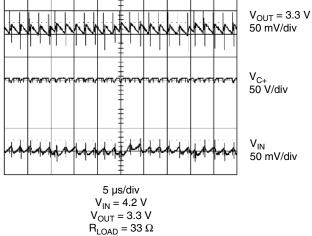

#### **TYPICAL WAVEFORMS**

Figure 1. Typical Switching Waveform ( $V_{OUT} > V_{IN}$ )

Figure 2. Typical Switching Waveform ( $V_{OUT} < V_{IN}$ )

| ORDERING INFORMATION |           |                   |  |  |  |

|----------------------|-----------|-------------------|--|--|--|

| Part Number          | Marking   | Temperature Range |  |  |  |

| SiP1759DB            | SiP1759DB | - 40 to 85 °C     |  |  |  |