PRELIMINARY

## 2048× 9 Bit CMOS Parallel FIFO

#### **Features**

- First-in, First-out dual port memory

- 2048 x 9 organization,

- Pin and functionally equivalent to IDT 7203

- Asynchronous and simultaneous read/write

- Empty and full warning flags

- Half full flag capability in single device mode

- Auto retransmit capability

- Multiple device expansion modes

- TTL-Compatible interface

- Very low power consumption: 50 mW (typ.)

- High performance architecture:

High throughput dual-port RAM architecture eliminates

1-2µsec fallthrough delays of shift register type FIFOs

28.5 MHz Operation: 35-120 ns Access times

- High-performance CMOS double metal technology Electrostatic discharge tolerance to 4000V. Latch-up protection to 100 mA

#### **General Description**

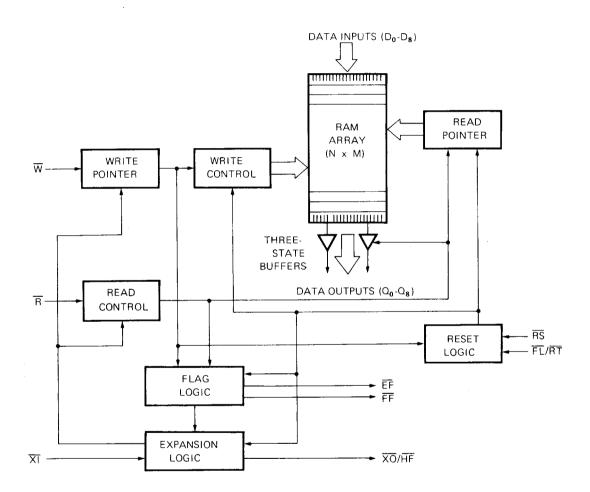

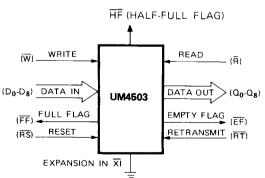

The UM4503 is a dual port FIFO memory which implements first-in, first-out sequential storage of 2048 nine-bit data words. The device supports asynchronous read and write operations. Full and empty flags are provided to prevent data overflow and underflow. Expansion control signals allow the FIFO to be easily cascaded, allowing multiple word widths and depths (i. e. 4096 x 9, 2048 x 18, etc.). A Half-Full Flag is available in the single device mode and width expansion modes.

The dual port RAM array is addressed internally using

ring counter pointers. The Write pointer addresses the location where data is to be written next, and the Read pointer addresses the location to be read next.

This high performance architecture reduces costly fall-through delays associated with shift register FIFOs. The worst-case fall-through delay associated with this dual port RAM FIFO is the time required to update the pointers (35-120ns), not the time required for data to propagate through the full depth of a shift register array  $(1-2\mu\text{sec})$ .

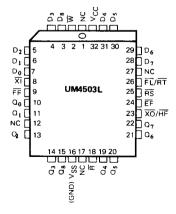

#### Pin Configurations

# Pin Designations

## **Block Diagram**

#### Absolute Maximum Ratings\*

| Terminal Voltage with Respect to GND $\dots -0.5$ to +7.0V                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Temperature $\dots \dots \dots$ |

| Storage Temperature                                                                                                                       |

| Power Dissipation                                                                                                                         |

| DC Output Current                                                                                                                         |

#### **DC Electrical Characteristics**

$(V_{CC} = 5V \pm 10\%, T_A = 0 - 70^{\circ}C)$

#### \*Comments

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol           | Parameter                                                                                                      | Min. | Тур. | Max. | Units | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------------|

| l <sub>iL</sub>  | Input Leakage Current (Any Input)                                                                              | -1   | _    | 1    | μΑ    | 1            |

| loL              | Output Leakage Current                                                                                         | -10  | -    | 10   | μΑ    | 2            |

| V <sub>OH</sub>  | Output Logic "1" Voltage I <sub>OUT</sub> = -2 mA                                                              | 2.4  | _    | -    | V     | <del>-</del> |

| V <sub>OL</sub>  | Output Logic "0" Voltage I <sub>OUT</sub> = 8 mA                                                               |      | _    | 0.4  | V     | -            |

| l <sub>CC1</sub> | Active Power Supply Current                                                                                    |      | -    | 40   | mA    | 3            |

| l <sub>CC2</sub> | Average Standby Current $(\overline{R} = \overline{W} = \overline{RS} = \overline{FL}/\overline{RT} = V_{IH})$ | _    | -    | 8    | mA    | 3            |

| Іссз             | Power Down Current<br>(All Inputs = V <sub>CC</sub> - 0.2V)                                                    | -    | -    | 500  | μΑ    | 3            |

Notes: 1. Measurements with  $0.4 \le V_{1N} \le V_{OUT}$ .

- 2,  $R \ge V_{HH}$ ,  $0.4 \le V_{OUT} \le V_{CC}$ .

- 3. I<sub>CC</sub> measurements are made with outputs open.

### **Recommended DC Operating Conditions**

| Symbol          | Parameter                | Min. | Тур. | Max.  |

|-----------------|--------------------------|------|------|-------|

| V <sub>cc</sub> | Supply Voltage           | 4.5V | 5.0V | 5.5V  |

| GND             | Ground                   | 0V   | 0∨   | 0V    |

| V <sub>IH</sub> | High Voltage, All Inputs | 2.0V | -    | _     |

| V <sub>IL</sub> | Low Voltage, All Inputs  |      | _    | 0.8V* |

<sup>\*1.5</sup>V undershoots are allowed for 10 ns, once per cycle.

<sup>\*</sup>Includes jig and scope capacitances.

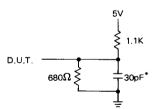

Figure 1. A.C. Testing Load Circuit

#### FIFO Applications

Acting as temporary storage buffers, FIFOs allow datarate matching between asynchronously timed data buses. Thus, data from an input device can load a FIFO at a different rate than the output device takes data from the FIFO.

FIFOs provide circuit savings and reduce system overhead by not requiring addresses for memory access. Because FIFOs do not utilize address and chip select inputs, they have been called "zero address RAMs". FIFO applications include data transfer rate matching between microprocessors and peripherals such as printers, disk drives, and streaming tape units. FIFOs are well suited in local-area network and communication protocol controller applications. They are also used to send and receive data to and from both D/A and A/D converters in digital signal processing applications. FIFOs are also used to decouple input data bursts from memories in high speed graphics processors, eliminating synchronization circuits.

## **AC** Characteristics

$(V_{CC} = 5V \pm 10\%, T_A = 0 - 70^{\circ}C, Timings referenced as in AC Test Conditions)$

| Symbol           | Parameters                            | UM4  | 503/35   | UM4  | 503/50 | UM4      | 503/65   | UM45     | 03/80        | 0 UM4503/12 |          |       |          |

|------------------|---------------------------------------|------|----------|------|--------|----------|----------|----------|--------------|-------------|----------|-------|----------|

| 3 yiii boi       | r ar arrive Cer s                     | Min. | Max.     | Min. | Max.   | Min.     | Max.     | Min.     | Max.         | Min.        | Max.     | Units | Notes    |

| t <sub>RC</sub>  | Read Cyle Time                        | 45   | -        | 65   | _      | 80       | _        | 100      |              | 140         | _        | ns    | _        |

| t <sub>A</sub>   | Access Time                           | -    | 35       | -    | 50     | _        | 65       |          | 80           |             | 120      | ns    |          |

| t <sub>RR</sub>  | Read Recovery Time                    | 10   | <u>-</u> | 15   | _      | 15       | T -      | 20       | -            | 20          | _        | ns    |          |

| t <sub>RPW</sub> | Read Pulse Width                      | 35   | -        | 50   | _      | 65       | _        | 80       |              | 120         | =        | ns    | 1        |

| t <sub>RLZ</sub> | Read Pulse Low to Data Bus at Low Z   | 5    | _        | 10   | _      | 10       | -        | 10       |              | 10          |          | ns    | 2        |

| twLZ             | Write Pulse High to Data Bus at Low Z | 10   | -        | 15   | -      | 15       | -        | 20       | _            | 20          | -        | ns    | 2        |

| t <sub>DV</sub>  | Data Valid from Read Pulse High       | 5    | -        | 5    | _      | 5        | -        | 5        | -            | 5           | _        | ns    |          |

| t <sub>RHZ</sub> | Read Pulse High to Data Bus at High Z | _    | 20       |      | 30     | -        | 30       | _        | 30           | _           | 35       | ns    | 2        |

| twc              | Write Cycle Time                      | 45   | -        | 65   | _      | 80       | -        | 100      |              | 140         | _        | ns    | _        |

| t <sub>WPW</sub> | Write Pulse Width                     | 35   | -        | 50   | _      | 65       | -        | 80       | _            | 120         | _        | ns    | 1        |

| t <sub>WR</sub>  | Write Recovery Time                   | 10   | -        | 15   | _      | 15       | İ —      | 20       | -            | 20          | _        | ns    | -        |

| t <sub>DS</sub>  | Data Setup Time                       | 18   | _        | 30   | _      | 30       | <u> </u> | 40       | _            | 40          | _        | ns    | -        |

| <sup>t</sup> DH  | Data Hold Time                        | 0    | _        | 5    | _      | 10       | <b> </b> | 10       |              | 10          | _        | ns    | _        |

| t <sub>RSC</sub> | Reset Cycle Time                      | 45   | -        | 65   | _      | 80       |          | 100      | _            | 140         |          | ns    |          |

| t <sub>RS</sub>  | Reset Pulse Width                     | 35   |          | 50   | _      | 65       | _        | 80       | _            | 120         | _        | ns    | 1        |

| t <sub>RSR</sub> | Reset Recovery Time                   | 10   | _        | 15   | _      | 15       | -        | 20       | <del>-</del> | 20          | -        | ns    |          |

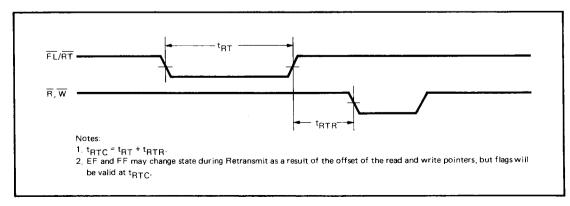

| t <sub>RTC</sub> | Retransmit Cycle Time                 | 45   | -        | 65   | _      | 80       | _        | 100      |              | 140         | <b>—</b> | ns    | -        |

| t <sub>RT</sub>  | Retransmit Pulse Width                | 35   | _        | 50   | _      | 65       | _        | 80       | -            | 120         | _        | ns    | 1        |

| t <sub>RTR</sub> | Retransmit Recovery Time              | 10   | _        | 15   | _      | 15       | _        | 20       | _            | 20          | _        | ns    | T -      |

| t <sub>EFL</sub> | Reset to Empty Flag Low               | -    | 45       | _    | 65     | <u> </u> | 80       | _        | 100          | -           | 140      | ns    | _        |

| t <sub>REF</sub> | Read Low to Empty Flag Low            | -    | 30       | _    | 45     | -        | 60       | _        | 60           |             | 60       | ns    | -        |

| t <sub>RFF</sub> | Read High to Full Flag High           | _    | 30       | _    | 45     | -        | 60       | _        | 60           | _           | 60       | ns    | <u> </u> |

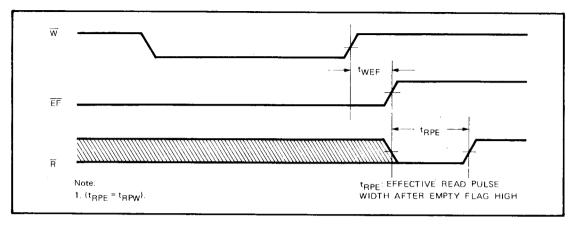

| <sup>t</sup> weF | Write High to Empty Flag High         | T -  | 30       | _    | 45     | _        | 60       | -        | 60           | _           | 60       | ns    | _        |

| t <sub>WFF</sub> | Write Low to Full Flag Low            | -    | 30       | _    | 45     | _        | 60       | <u> </u> | 60           | _           | 60       | ns    | T -      |

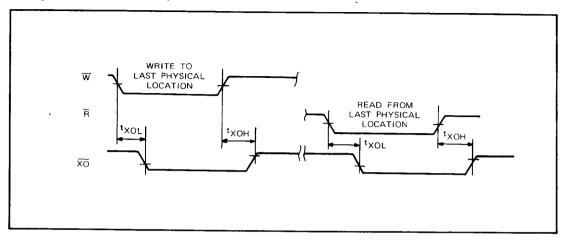

| <sup>t</sup> xoL | Read/Write to XO Low                  | -    | 35       | _    | 50     | _        | 65       | -        | 80           |             | 120      | ns    | _        |

| <sup>t</sup> xoн | Read/Write to XO High                 | -    | 35       | _    | 50     | -        | 65       | <u> </u> | 80           |             | 120      | ns    | -        |

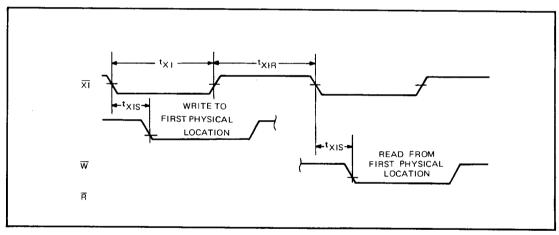

| t <sub>XIP</sub> | XI Pulse Width                        | 35   | -        | 50   |        | 65       | _        | 80       | -            | 120         | =        | ns    | -        |

| t <sub>XIR</sub> | XI Recovery Time                      | 10   | -        | 10   |        | 10       |          | 10       | -            | 10          | _        | ns    | -        |

| <sup>t</sup> xis | XI Set-up Time                        | 15   | -        | 15   | _      | 15       | -        | 15       | -            | 15          | <b> </b> | ns    | -        |

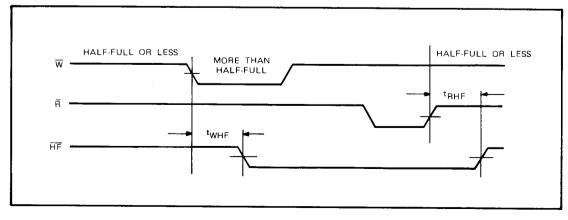

| twhF             | Write Low to Half Full Flag Low       | -    | 45       | -    | 65     | _        | 80       |          | 100          | -           | 140      | ns    | -        |

| t <sub>RHF</sub> | Read High to Half Full Flag High      |      | 45       | _    | 65     | _        | 80       | <u> </u> | 100          |             | 140      | ns    | <u> </u> |

Notes: 1. Pulse widths less than minimum value are not allowed.

2. Values guaranteed by design, not currently tested.

## **AC Test Conditions**

| Input Pulse Levels            | GND to 3.0V  |

|-------------------------------|--------------|

| Input Rise and Fall Times     | 5ns          |

| Input Timing Reference Levels | 1.5V         |

| Output Reference Levels       | 1.5V         |

| Output Load                   | See Figure 1 |

|                               |              |

## Capacitance

| Symbol           | Item                  | Conditions            | Maximum | Notes |

|------------------|-----------------------|-----------------------|---------|-------|

| C <sub>IN</sub>  | Input<br>Capacitance  | V <sub>IN</sub> *= 0V | 7 pF    | 2     |

| c <sub>out</sub> | Output<br>Capacitance | V <sub>OUT</sub> = 0V | 12 pF   | 1, 2  |

Notes: 1. With output deselected.

2. Characterized values, not currently tested.

#### Signal Descriptions

#### **Data Inputs**

### Data In $(D_0 - D_8)$

These data inputs accept nine-bit data words for sequential storage in the FIFO during the Write cycle,

#### Control Signals and Flags

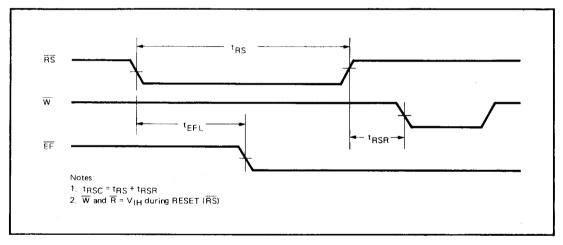

#### Reset (RS)

This active-low control line input resets both the internal Read and Write pointers to their initial state (the first word location). An RS signal is required after power-up. before a Write operation can occur. Both the READ EN-ABLE (R) and the WRITE ENABLE (W) must be in the inactive high state during RESET.

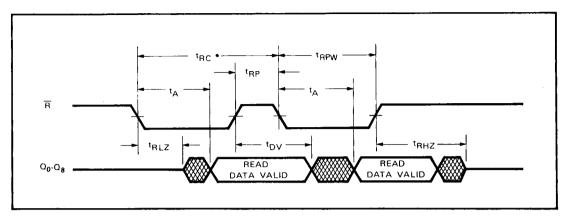

#### Read Enable (R)

The falling edge of the READ ENABLE (R) signal initiates a Read cycle, as long as the EMPTY FLAG (EF) is not set. Data words are accessed on a first-in, first-out basis, Current read addresses are generated internally by ring counter logic, Read cycle timing is listed in "AC Characteristics". I

Read operations are independent of Write operations. After the read cycle, READ ENABLE (R) goes inactivehigh, causing the Data Outputs (Do -D8) to go into high impedance (high-Z) state until the next Read operation.

When all of the data has been read from the FIFO, the EMPTY FLAG (EF) goes active-low, and subsequent Read operations are inhibited. The flag is cleared upon completion of a valid write operation (after tweet).

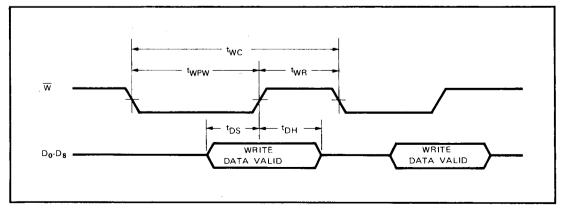

#### Write Enable (W)

The falling edge of the active-low WRITE ENABLE (W) signal initiates a Write cycle, as long as the FULL FLAG (FF) is not set. Data words are stored in the RAM array sequentially. Current write addresses are generated internally by ring counter logic. Write operations are independent of Read operations.

To be valid, data being written to the FIFO must meet setup and hold time requirements with respect to the rising edge of the WRITE ENABLE (W) signal. Write Cycle timing is listed in "AC Characteristics".

When the word capacity of the FIFO has been reached, the FULL FLAG (FF) goes active-low to prevent data overflow. The FULL FLAG (FF) is cleared upon the completion of a valid Read operation (after table).

#### Expansion In (XI)

This input pin serves two purposes. When grounded, it indicates that the FIFO is being operated in Single Device Mode (see Operating Modes).

In Multiple Device Mode it is connected to the EXPAN-SION OUT (XO) line of the previous device when the FIFO is configured in Depth Expansion or Daisy Chain Mode.

#### Expansion Out/Half Full Flag (XO/HF)

This is a dual purpose output. In the single device mode when EXPANSION IN (XI) is grounded, this output acts as an indication of a half full memory.

After half of the memory is filled, and at the falling edge of the next write operation, the HALF FULL FLAG (HF) will be set to low and will remain set until the difference between the write pointer and the read pointer is less than or equal to one half of the total memory of the device. The HALF FULL FLAG (HF) is then reset by the rising edge of the read operation.

In the Multiple Device Mode, EXPANSION IN  $(\overline{XI})$  is connected to EXPANSION OUT (XO) of the previous device. This output acts as a signal to the next device in the Daisy Chain by providing a pulse to the next device when the previous device reaches the last location of memory,

#### Firstload/Retransmit (FL/RT)

The output pin serves two purposes. In Single Device Mode, the pin serves as the RETRANSMIT ENABLE (RT) signal. In Multiple Device Mode (see Operating Modes), the pin is the FIRST LOAD (FL) pin.

When this line is pulsed active-low in Single Device Mode, a Retransmit operation is enabled. Retransmit resets the internal Read pointer to the first location, but does not affect the write pointer. READ ENABLE (R) and WRITE ENABLE (W) must be inactive (high) during Retransmit. RETRANSMIT ENABLE (RT) is generally used when less than 2048 writes are performed between resets. This feature can not be used in Multiple Device Mode.

When used in Multiple Device Mode, the FIRST LOAD (FL) pin on the first FIFO in the Daisy Chain to be loaded with data is grounded (see Operating Modes). The remaining FL pins in the Daisy Chain are tied to Vcc.

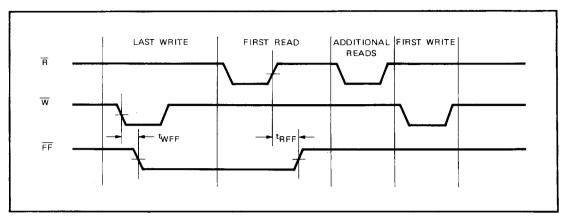

#### Full Flag (FF)

When the word capacity of the FIFO has been reached. the FULL FLAG (FF) goes active-low when the Write pointer is one word location from the Read pointer, to prevent data overflow. The signal inhibits Write operations and is cleared when a valid Read operation completes (after trff). Both the FULL FLAG (FF) and the EMPTY FLAG (EF) may be used as clock-enables to control asynchronous timing.

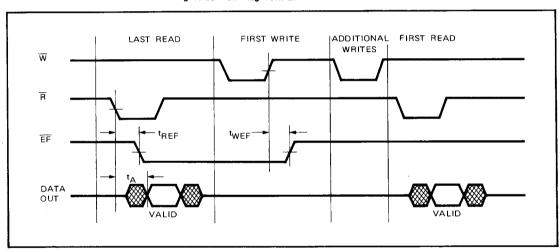

#### Empty Flag (EF)

When all of the data has been read from the device, the EMPTY FLAG (EF) goes active-low (when the Read pointer is one word location from the Write pointer). The EMPTY FLAG (EF) inhibits Read operations by causing the Data Outputs to go into high-Z state. It is cleared when a valid Write operation completes (after Twef),

#### **Data Outputs**

#### Data Outputs $(Q_0 - Q_8)$

These nine lines are the data-word outputs. These lines 5—7 are in high-Z state whenever READ (R) is inactive.

## **Timing Waveforms**

Figure 3. Asynchronous Read Operation

Figure 2. Reset

Figure 4. Asynchronous Write Operation

## **Timing Waveforms (Continued)**

Figure 5. Full Flag from Last Write to First Read

Figure 6. Empty Flag from Last Read to First Write

Figure 7. Retransmit

## **Timing Waveforms (Continued)**

Figure 8. Empty Flag Timing

Figure 9, Full Flag Timing

Figure 10. Half-Full Flag Timing

#### **Timing Waveforms (Continued)**

Figure 11. Expansion Out

Figure 12. Expansion In

### **Operating Modes**

#### Single Device Mode

When one UM4503 is used standalone in Single Device Mode, the Expansion In  $(\overline{XI})$  control input pin must be grounded. See Figure 13.

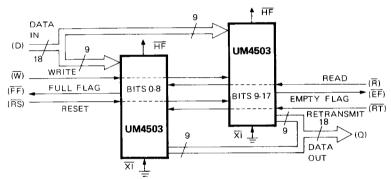

#### Width Expansion Mode

Word width may be expanded by connecting the corresponding control input signals of multiple devices together. The EMPTY FLAG FULL FLAG and HALF FULL FLAG (EF, FF and HF) can be detected by any particular device. Figure 14 shows an 18-bit wide configuration using two devices. They may be configured to any word width in this manner,

Figure 13. Single Device Mode

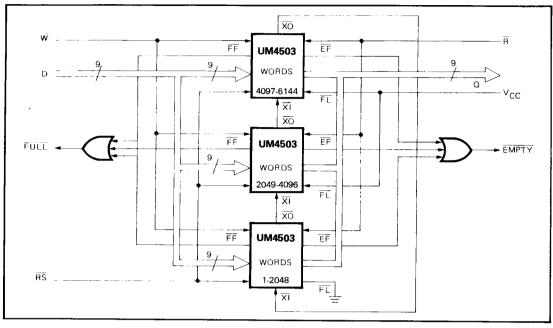

#### Depth Expansion (Daisy Chain) Mode

Word depths may be expanded in multiples of 2048 words by Daisy Chaining the devices together as follows:

- The FIRST LOAD (FL) control signal of the first device must be grounded. This FIFO represents words 1-2048.

- 2. All other devices in the Daisy Chain must have the FIRST LOAD  $(\overline{FL})$  control signal tied to  $V_{CC}$ , in the inactive-high state.

- The EXPANSION OUT (XO) pin of each device must be connected to the EXPANSION IN (XI) pin of the next device as shown in Figure 16.

- External logic is required to generate a common FULL FLAG (FF) and EMPTY FLAG (EF) signal by ORing all of the FFs together and ORing all of the EFs together.

The Retransmit (RT) function and Half-Full Flag (HF) are not available in Daisy Chain Mode.

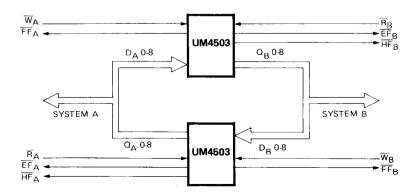

#### **Bidirectional Mode**

Data buffering between two systems can be achieved by pairing two FIFO arrays as shown in Figure 15. This allows each system to READ and WRITE shared data. The FULL FLAG ( $\overline{\text{FF}}$ ) must be monitored on the FIFO where WRITE ENABLE ( $\overline{\text{W}}$ ) is used, and the EMPTY FLAG ( $\overline{\text{EF}}$ ) must be monitored on the FIFO where READ ENABLE ( $\overline{\text{R}}$ ) is used. Both Width Expansion and Depth Expansion Modes may be used in combination with Bidirectional Mode.

#### Compound Expansion Mode

Both Width Expansion Mode and Depth Expansion (Daisy Chain) Mode can be used together to configure a large FIFO array (See Figure 14 and 16).

Notes:

Flag detection is accomplished by monitoring the FF, HF and EF, on device used in the Width Expansion Mode. Do not connect output control signals together.

Figure 14. Width Expansion Mode

Figure 15. Bidirectional FIFO Mode

Figure 16. Block Diagram of a 6144 x 9 FIFO Memory (Depth Expansion)

### **Truth Tables**

Single Device Configuration/Width Expansion Mode

Table 1. Reset and Retransmit

| Mode       |    | Inputs |    | Internal Status          |                          |    |       | Outputs |  |  |

|------------|----|--------|----|--------------------------|--------------------------|----|-------|---------|--|--|

|            | RS | RT     | Χī | Read Pointer             | Write Pointer            | EF | FF    | HF      |  |  |

| Reset      | 0  | ×      | 0  | Location Zero            | Location Zero            | 0  | 1     | 1       |  |  |

| Retransmit | 1  | 0      | 0  | Location Zero            | Unchanged                | X  | X     | ×       |  |  |

| Read/Write | 1  | 1      | 0  | Increment <sup>(1)</sup> | Increment <sup>(1)</sup> | X  | 1 x 1 | ×       |  |  |

Note: 1. Pointer will increment if flag is high.

## Depth Expansion/Compound Expansion Mode

Table 2. Reset and Firstload

| Mode                    |    | Inputs |     | Interna       | Outputs       |    |    |

|-------------------------|----|--------|-----|---------------|---------------|----|----|

|                         | RS | FL     | ΧĪ  | Read Pointer  | Write Pointer | ĒF | FF |

| Reset-First Device      | 0  | 0      | (1) | Location Zero | Location Zero | 0  | 1  |

| Reset all Other Devices | 0  | 1      | (1) | Location Zero | Location Zero | 0  | 1  |

| Read/Write              | 1  | ×      | (1) | X             | ×             | X  | X  |

Notes: 1.  $\overline{XI}$  is connected to  $\overline{XO}$  of previous device. See Figure 16.  $\overline{RS}$  = Reset Input,  $\overline{FL/RI}$  = First Load/Retransmit.  $\overline{EF}$  = Empty Flag Output.  $\overline{FF}$  = Full Flag Output,  $\overline{XI}$  = Expansion Input. 5–13

## **Ordering Information**

| Part Number | Access Time | Package  |

|-------------|-------------|----------|

| UM4503-12   | 120ns       | 28L DIP  |

| UM4503-80   | 80ns        | 28L DIP  |

| UM4503-65   | 65ns        | 28L DIP  |

| UM4503-50   | 50ns        | 28L DIP  |

| UM4503-35   | 35ns        | 28L DIP  |

| UM4503L-12  | 120ns       | 32L PLCC |

| UM4503L-80  | 80ns        | 32L PLCC |

| UM4503L-65  | 65ns        | 32L PLCC |

| UM4503L-50  | 50ns        | 32L PLCC |

| UM4503L-35  | 35ns        | 32L PLCC |