# **XRT86SH221**

### SDH-TO-PDH FRAMER/MAPPER WITH INTEGRATED 21-CHANNEL E1 SH LIU

MAY 2007 REV. P1.0.5

#### **GENERAL DESCRIPTION**

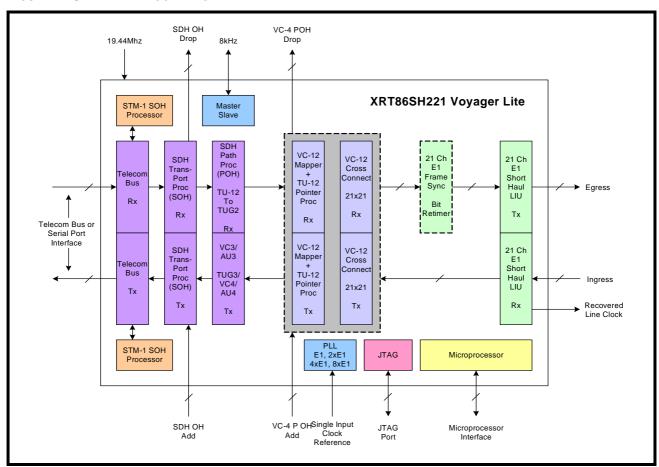

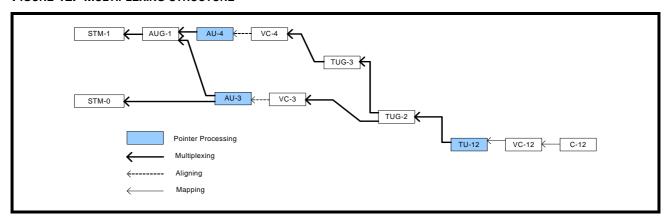

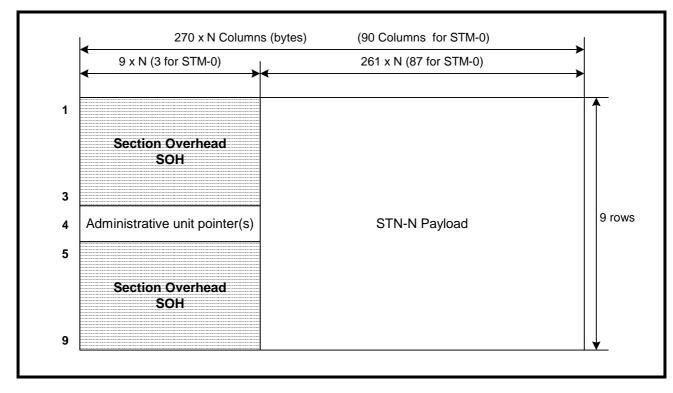

The XRT86SH221 (Voyager-Lite) is a physical layer SDH to PDH mapper/demapper which enables E1 aggregation to STM-1 via standard VC-12 to AU-3 and TUG-3/AU-4 mapping protocols. Voyager-Lite supports all the framing, mapping and grooming functions required for STM-1 mapper applications. The device generates and terminates all SDH Regenerator Section, Multiplexer Section and Path Overhead including the low-order Virtual Container (VC) Path Overhead. E1 framing is transparent; therefore, the device neither generates nor terminates the E1 frame.

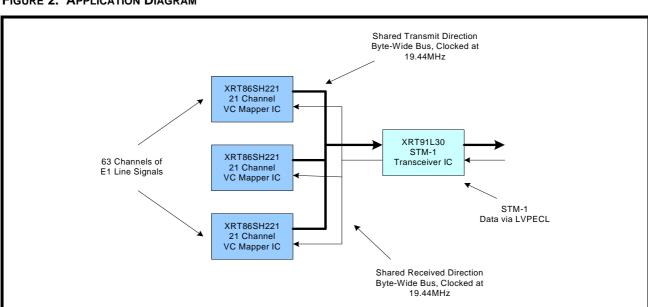

A single Voyager-Lite performs mapping of 21 asynchronous E1 spans to either VC-12/TU-12/TUG-2/ VC-3/AU-3/STM-0 or VC-12/TU-12/TUG-2/TUG-3/ STM-0. Mapping to STM-1 requires (3) Voyager-Lite devices with one acting as "master" framer and two acting as "slave" framers. In this configuration, Voyager-Lite performs all the necessary framing, pointer processing and mapping functions required for mapping of 63xE1 spans to either VC-12/TU-12/TUG-2/VC-3/AU-3/STM-1 or VC-12/TU-12/TUG-2/TUG-3/VC-4/AU-4/STM-1 as shown in the block diagram.

FIGURE 1. SIMPLIFIED BLOCK DIAGRAM

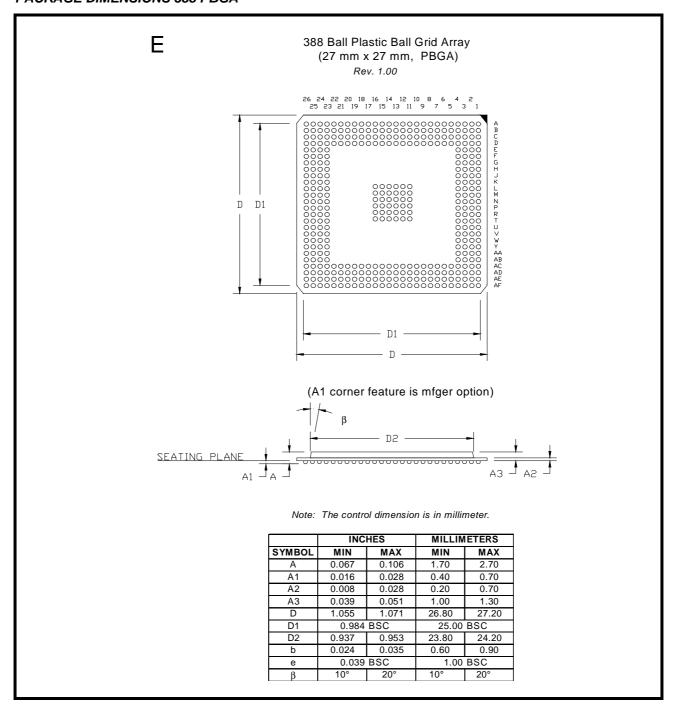

#### PACKAGE ORDERING INFORMATION

| Product Number | PACKAGE TYPE | OPERATING TEMPERATURE RANGE |  |

|----------------|--------------|-----------------------------|--|

| XRT86SH221IB   | 388 PBGA     | -40℃ to +85℃                |  |

### **PRELIMINARY**

### SDH-TO-PDH FRAMER/MAPPER WITH INTEGRATED 21-CHANNEL E1 SH LIU

#### **FEATURES**

### **VT Mapper**

- Maps up to 21 synchronous or asynchronous E1 signals to SDH AU-3 via TUG-2 and TU-12, or to SDH STM-0 payload capacity via VT Groups and VT2.

- Dynamic VT/TU size selection.

- Inserts valid V5 bit interleaved parity BIP-2 in the transmit direction.

- Detects and counts V5 BIP-2 errors for performance monitoring.

- Configurable remote error indication REI-V insertion for V5 BIP-2 errors.

- Supports proprietary V5 remote loopcodes.

- Detects and counts remote errors.

- Automatic receive monitor functions include VT/TU remote defect indication RDI-V, VT/TU remote failure indication RFI-V, VT/TU remote error indication REI-V, BIP-2 errors, VT/TU AIS, VT/TU Automatic Protection Switching (APS) signalling for low order path level, and VT/TU loss of pointer LOP-V.

- Automatic receive monitoring functions can be configured to provide an interrupt to the control system, or the device can be operated in a polled mode.

- Test pattern generation and detection/dropping for setup and maintenance.

- User configurable for VT/TU label, AIS-V, RDI-V, RFI-V, REI-V, APS, force BIP-2 errors, or unequipped tributary insertion.

#### **E1 Receive Framing Synchronizer**

- Provides a standard compliant 2.048 Mbits PCM30 CRC-4 E1 framer.

- Provides off-line framer.

- Complies with standards such as: ITU-T G.703, G.704, G.706 (including Annex B), G.732, G.735, G.736, G.737, G.761, G.823, I.431 and ETS 300 011, 300 233.

- Supports FAS, Signaling Multiframe, and CRC-4 framing structure.

- FAS reframe time is 625μs maximum.

- Provides Loss Of Frame (LOF), Loss of Multiframe detection.

- Provides Change Of Frame Alignment (COFA) detection.

- Provides Change Of signaling MultiFrame Alignment (COMFA) detection.

- Provides a 2-frame slip buffer for bit retiming.

**XRT86SH221**

#### SDH-TO-PDH FRAMER/MAPPER WITH INTEGRATED 21-CHANNEL E1 SH LIU

#### **SDH Transmitter**

- Performs standard STM-0/STM-1 transmit processing.

- Conforms to ITU-T I.432, ANSI T1.105, and Bellcore-253

- Provides a 51.84MHz STM-0 serial interface or 6MHz / 19MHz 8-bit STM-0 / STM-1 parallel interface.

- Performs SDH frame insertion and accepts external frame synchronization.

- Performs optional transmit data scrambling.

- Performs POH, SDH OH generation/insertion.

- Generates transmit payload pointer (H1, H2) (fixed at 522) with NDF insertion.

- Inserts A1/A2 with optional error mask.

- Computes and inserts BIP-8 (B1, B2) with optional error mask.

- Generates AIS-L, REI-L and RDI-L according to receiver state with option of SW or HW insertion.

- Inserts LOS, forces SEF by software.

- Generates RDI-P and REI-P automatically with optional SW or HW override.

- Inserts fixed-stuff columns, calculates and inserts B3 error code.

#### **SDH Receiver**

- Performs standard STM-0/STM-1 receive processing.

- Conforms to ITU-T I.432, ANSI T1.105, and Bellcore-253.

- Provides fully programmable threshold detection for SD and SF conditions.

- Provides a 51.84MHz STM-0 serial interface or 6MHz / 19MHz 8-bit STM-0 / STM-1 parallel interface.

- Provides section trace buffer with mismatch detection and invalid message detection.

- Performs SDH frame synchronization.

- Supports NDF, positive stuff and negative stuff for pointer processor.

- Performs receive data de-scrambling.

- Performs POH, SDH OH interpretation/extraction.

- Interprets payload pointer (H1, H2).

- Detects Out Of Frame (OOF), Loss Of Frame (LOF), Loss Of Signal (LOS), APS failure.

- Detects Line Alarm Indication(L-AIS), Line remote Defect Indication (L-RDI), Loss Of Pointer.

- Detects Path Alarm Indication, Path remote Defect Indication, Path extended RDI.

- Provides signal label monitor with PLM detection.

- Supports path trace buffer with TIM-P and invalid message detection.

- Computes and compares B3, REI-L and REI-P errors.

- Computes and compares BIP-8 (B1, B2) and counts the errors.

# **TABLE OF CONTENTS**

| GENERAL DESCRIPTION                                                       | 1  |

|---------------------------------------------------------------------------|----|

| Figure 1. Simplified Block Diagram                                        |    |

| PACKAGE ORDERING INFORMATION                                              |    |

| FEATURES                                                                  | 2  |

| TABLE OF CONTENTS                                                         | 1  |

| 1.0 PIN DESCRIPTIONS                                                      |    |

| 1.1 MICROPROCESSOR INTERFACE PINS                                         |    |

| 1.2 BOUNDARY SCAN AND OTHER TEST PINS                                     |    |

| 1.3 GENERAL PURPOSE INPUT AND OUTPUT PINS                                 |    |

| 1.4 TIMING AND CLOCK SIGNALS                                              | 7  |

| 1.5 LOW SPEED LINE INTERFACE SIGNALS                                      | 9  |

| 1.6 HIGH SPEED SERIAL INTERFACE                                           |    |

| 1.7 HIGH SPEED TELECOM BUS INTERFACE                                      |    |

| 1.8 HIGH SPEED SECTION AND PATH OVERHEAD BUS                              |    |

| 1.9 HIGH SPEED TU POH OVERHEAD BUS                                        |    |

| 1.10 POWER AND GROUND PINS                                                | 18 |

| 2.0 APPLICATIONS AND PHYSICAL INTERFACE GENERAL OVERVIEW                  |    |

| FIGURE 2. APPLICATION DIAGRAM                                             |    |

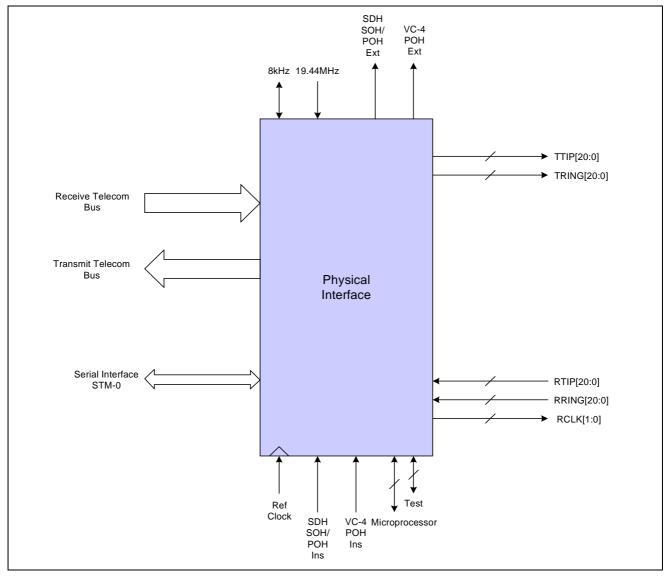

| 2.1 PHYSICAL INTERFACE                                                    | 21 |

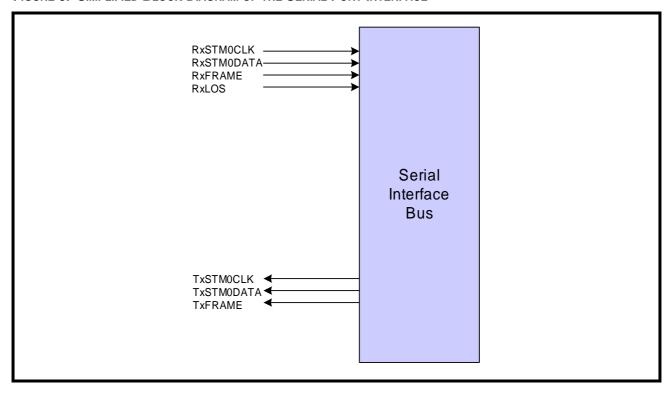

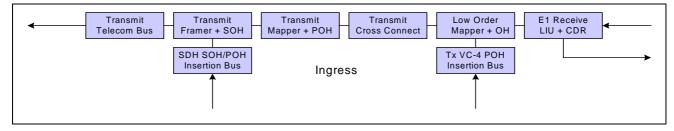

| FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE PHYSICAL INTERFACE              |    |

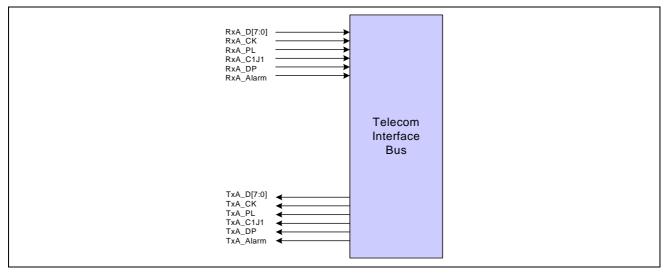

| 2.2 TELECOM BUS INTERFACE                                                 |    |

| 2.3 STM-0 SERIAL INTERFACE SDH FRAME SYNCHRONIZATION AND TIMING INTERFACE |    |

| FIGURE 5. SIMPLIFIED BLOCK DIAGRAM OF THE SERIAL PORT INTERFACE           |    |

| 2.4 SDH FRAME SYNCHRONIZATION AND TIMING INTERFACE                        |    |

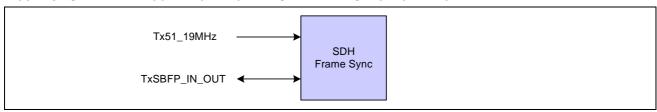

| FIGURE 6. SIMPLIFIED BLOCK DIAGRAM OF THE SDH FRAME SYNCHRONIZATION       |    |

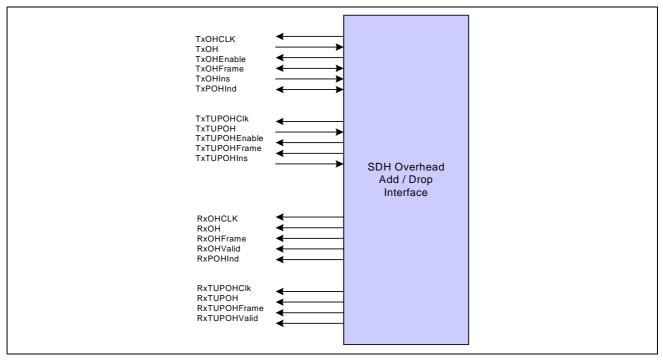

| 2.5 SDH OVERHEAD ADD-DROP INTERFACES                                      | 25 |

| FIGURE 7. SIMPLIFIED BLOCK DIAGRAM OF THE SDH OVERHEAD ADD-DROP INTERFACE |    |

| 2.6 E1 SHORT HAUL LINE INTERFACE                                          |    |

| 2.7 E1 TIMING INTERFACE                                                   |    |

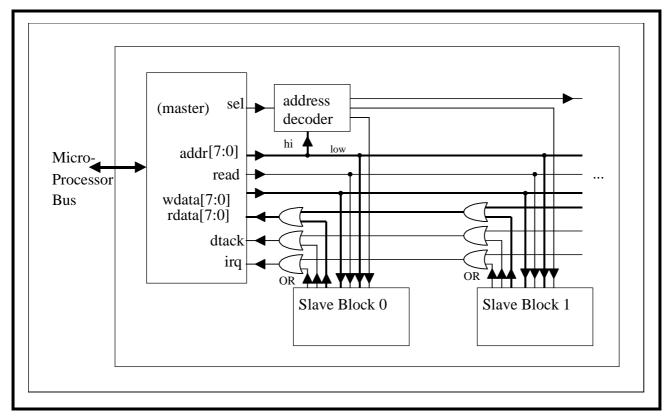

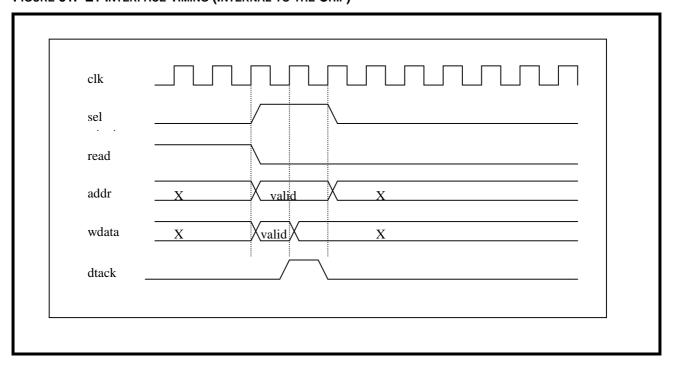

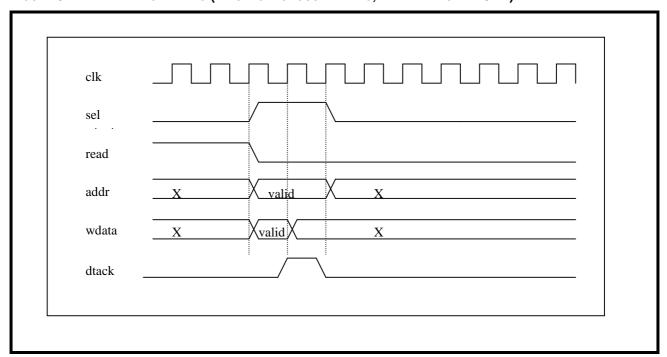

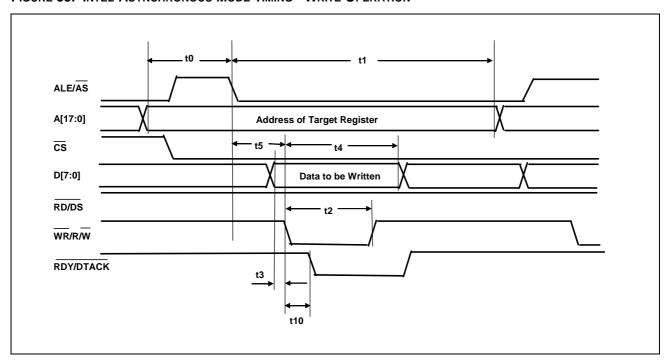

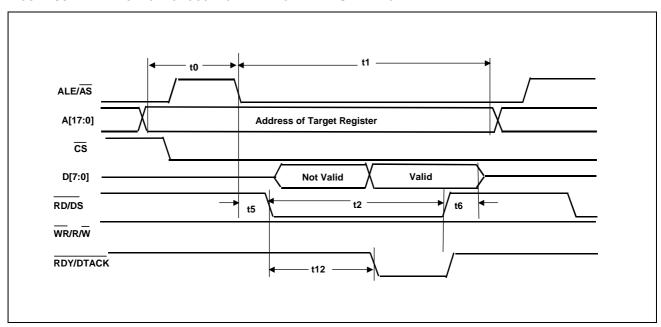

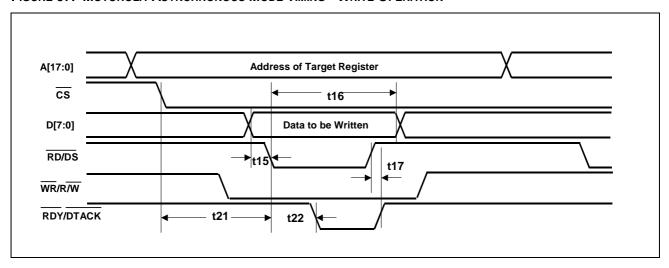

| 2.8 MICROPROCESSOR INTERFACE                                              |    |

| 3.0 FUNCTIONAL DESCRIPTION                                                |    |

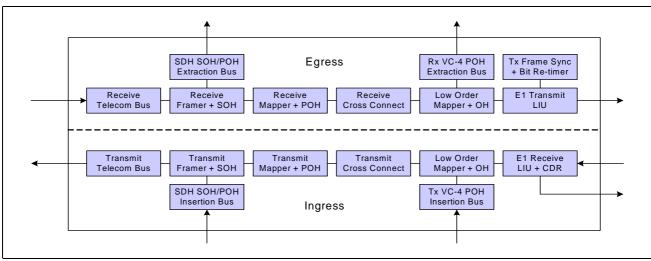

| FIGURE 8. FUNCTIONAL BLOCK DIAGRAM                                        |    |

| 3.1 INGRESS DATA PATH FUNCTIONAL BLOCKS                                   |    |

| FIGURE 9. SIMPLIFIED BLOCK DIAGRAM OF THE INGRESS DATA PATH               |    |

| 3.2 E1 RECEIVE LIU (RXE1LIU)                                              |    |

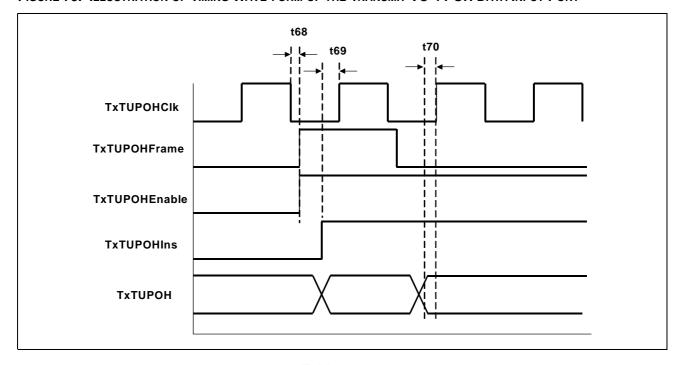

| 3.3 TRANSMIT LOW-ORDER (TU) OVERHEAD INSERTION BUS (TXTUPOH)              |    |

| 3.5 VC-12 TRANSMIT COW-ORDER MAPPER AND OVERHEAD PROCESSOR (TXLOPOHPROC)  |    |

| 3.6 TRANSMIT SDH SOH/POH INSERTION BUS (TXOH)                             |    |

| 3.7 SDH TRANSMIT MAPPER AND PATH OVERHEAD PROCESSOR (TXPOHPROC)           | 30 |

| 3.8 SDH TRANSMIT FRAMER AND SECTION OVERHEAD PROCESSOR (TXSOHPROC)        | 32 |

| 3.9 TRANSMIT TELECOM BUS (TXTBUS)                                         |    |

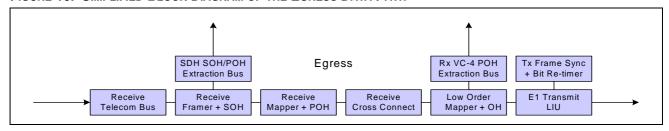

| 3.10 EGRESS DATA PATH FUNCTIONAL BLOCKS                                   |    |

| FIGURE 10. SIMPLIFIED BLOCK DIAGRAM OF THE EGRESS DATA PATH               |    |

| 3.11 RECEIVE TELECOM BUS (RXTBUS)                                         |    |

| 3.12 SDH RECEIVE FRAMER AND SECTION OVERHEAD PROCESSOR (RXSOHPROC)        | 35 |

| 3.13 SDH RECEIVE MAPPER AND PATH OVERHEAD PROCESSOR (RXPOHPROC)           | 36 |

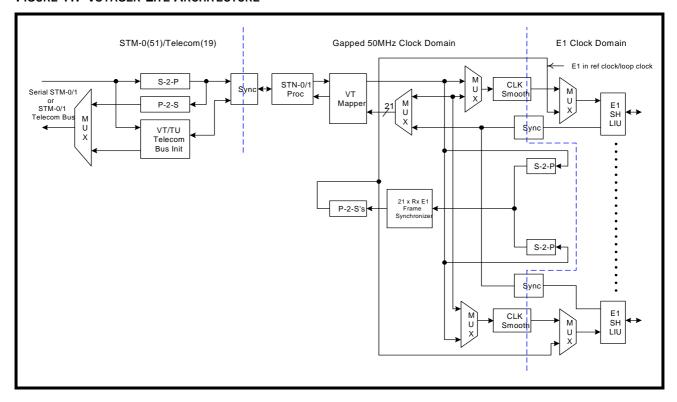

| 4.0 VOYAGER-LITE HARDWARE ARCHITECTURE AND ALGORITHMS                     | 37 |

| Figure 11. Voyager-Lite Architecture                                      | 37 |

| 4.1 MULTIPLEXING STRUCTURE                                                |    |

| FIGURE 12. MULTIPLEXING STRUCTURE                                         |    |

| 4.2 FUNCTIONAL BLOCKS                                                     |    |

| 4.3 SDH TRANSMIT DATA FLOW                                                |    |

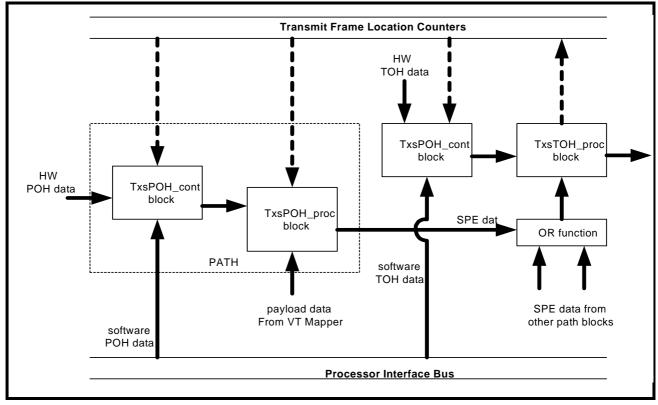

| FIGURE 13. SDH TRANSMITTER GENERAL STRUCTURE                              |    |

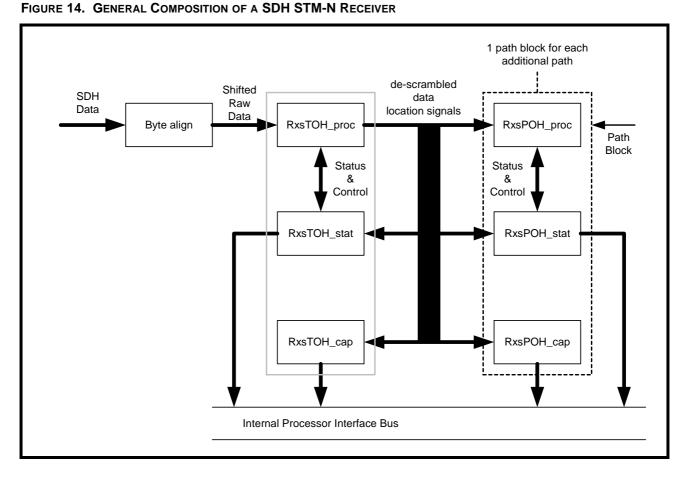

| FIGURE 14. GENERAL COMPOSITION OF A SDH STM-N RECEIVER                    |    |

| 4.5 VT MAPPER                                                             |    |

|                                                                           |    |

### REV. P1.0.5

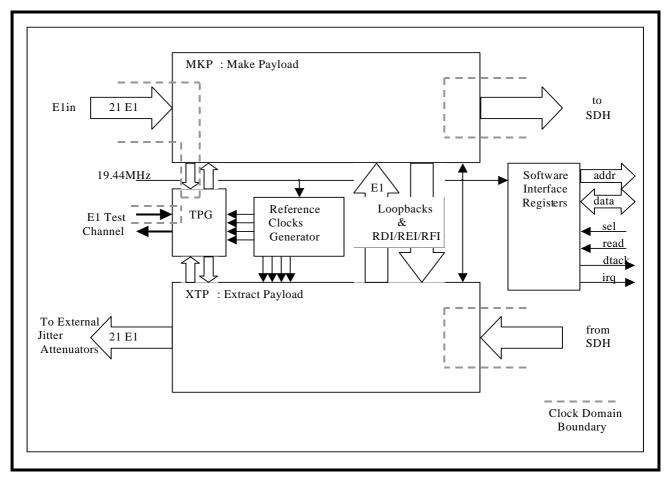

| FIGURE 15. TOP LEVEL BLOCK DIAGRAM                                            |    |

|-------------------------------------------------------------------------------|----|

| 4.6 INTERRUPTS AND STATUS                                                     |    |

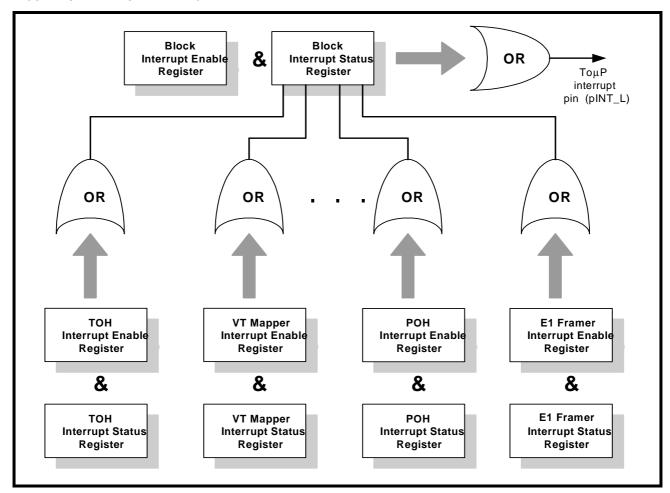

| Figure 16. Interrupt Hierarchy                                                |    |

| 4.7 INTERRUPT PROCESSING AND CONTROL                                          |    |

| 4.8 STM-0/1 RECEIVE TRANSPORT PROCESSOR                                       | 44 |

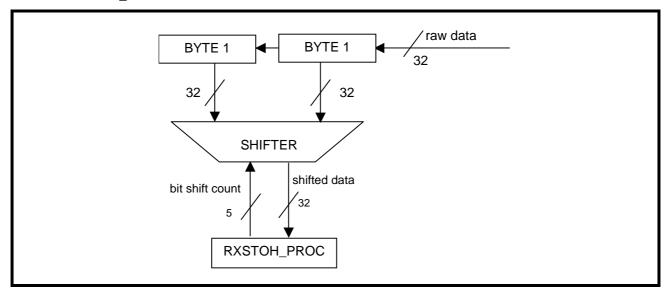

| Figure 17. BYTE_ALIGN BLOCK FUNCTIONAL DIAGRAM                                | 44 |

| TABLE 1: 16-BYTE FRAME FOR TRAIL APID                                         | 49 |

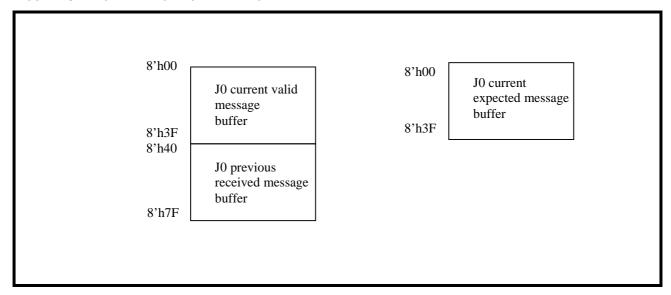

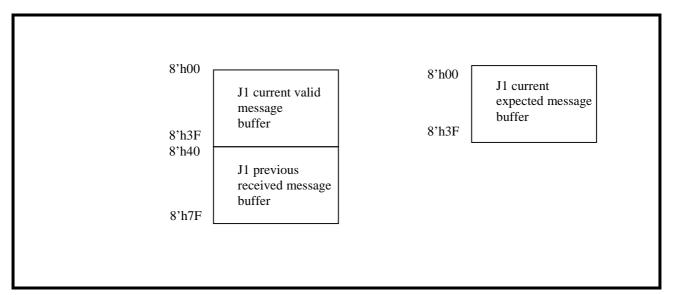

| Figure 18. Receive Trace Buffer Memory                                        |    |

| TABLE 2: ADDRESSING SCHEME USED TO ACCESS THE SDH OH BYTES                    |    |

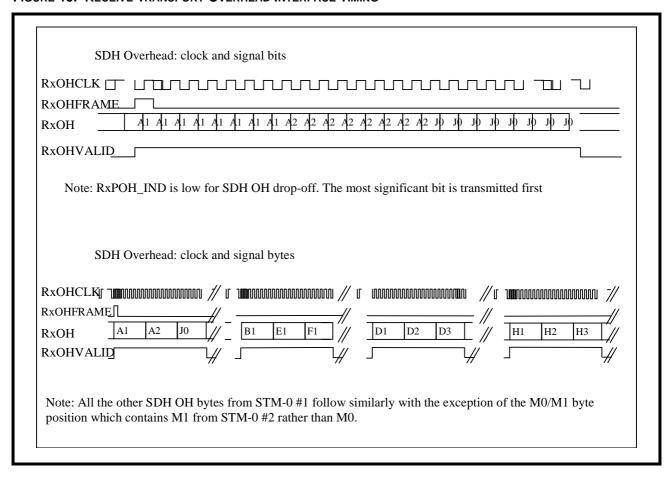

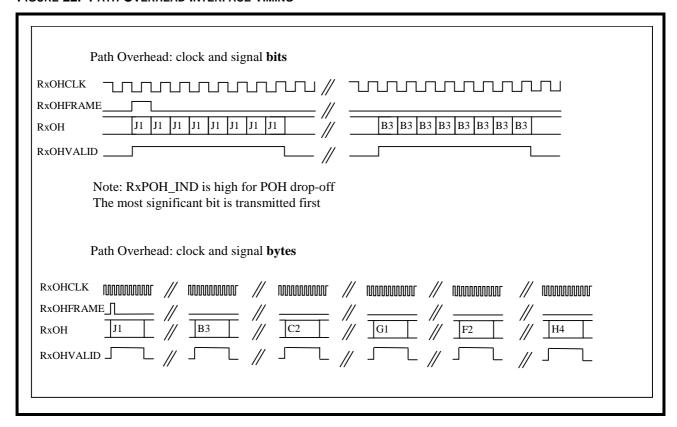

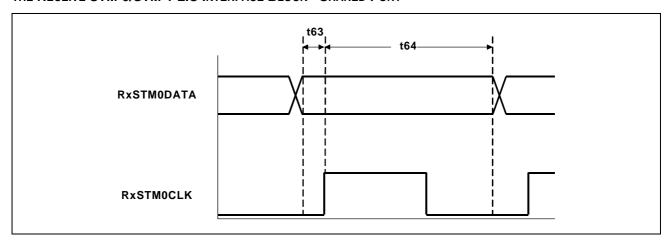

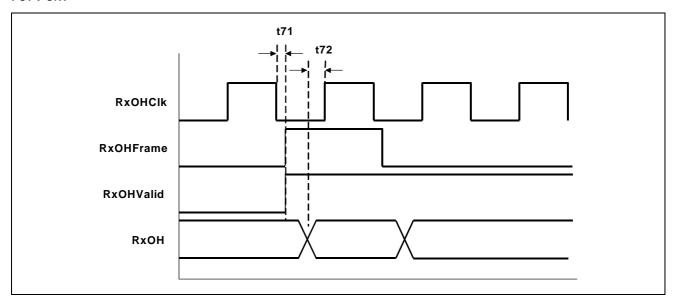

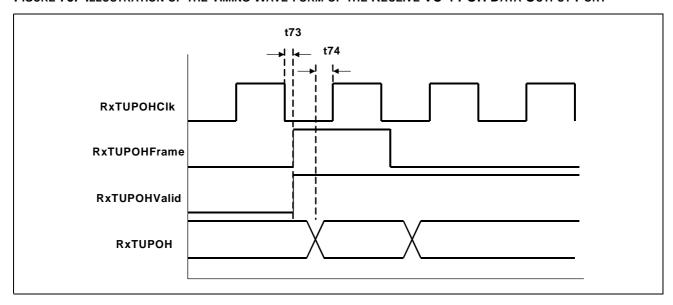

| FIGURE 19. RECEIVE TRANSPORT OVERHEAD INTERFACE TIMING                        |    |

| STM-0/1 RECEIVE PATH PROCESSOR                                                | 53 |

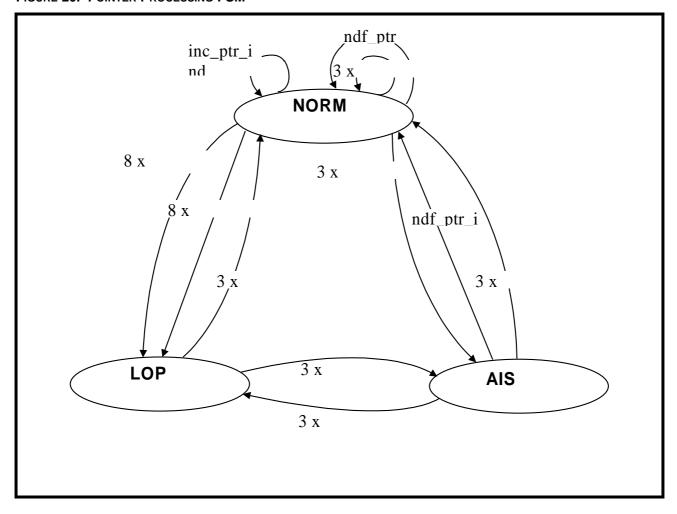

| Figure 20. Pointer Processing FSM                                             |    |

| Table 3: SDH Pointer Event Types                                              |    |

| FIGURE 21. CONCATENATED POINTER INDICATOR PROCESSING FSM                      |    |

| TABLE 4: RDI-P SETTINGS AND INTERPRETATION                                    |    |

| TABLE 5: STS SIGNAL LABEL MISMATCH DEFECT CONDITIONS                          |    |

| TABLE 6: TRUTH TABLE FOR PATH LABEL ERROR CONDITIONS                          |    |

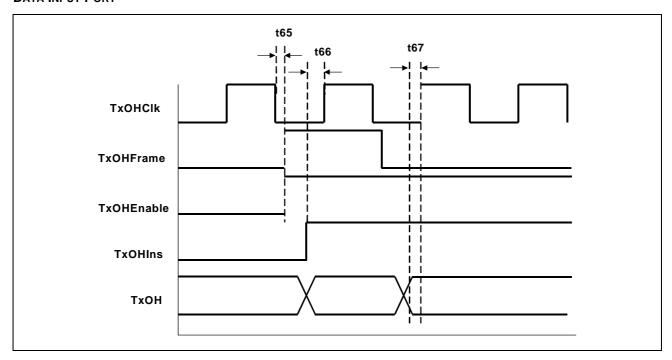

| FIGURE 22. PATH OVERHEAD INTERFACE TIMING                                     |    |

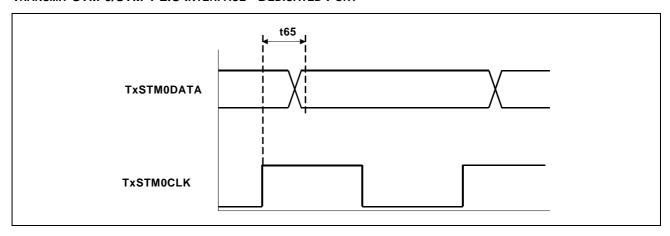

| FIGURE 23. TRANSMIT TRANSPORT OVERHEAD INTERFACE TIMING                       |    |

| 4.9 TELECOM BUS INTERFACE                                                     |    |

| 4.9.1 TRANSMIT TELECOM BUS                                                    |    |

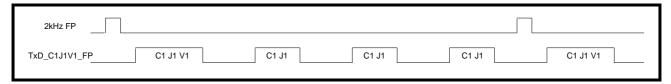

| 4.9.2 2KHZ MODE IN STM-1                                                      |    |

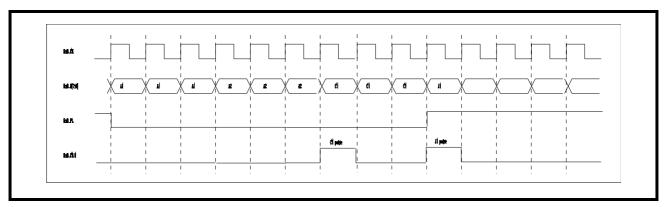

| Figure 25. C1J1V1 Pulse in STM-1 2kHz Mode                                    |    |

| 4.9.3 RECEIVE TELECOM BUS                                                     |    |

| Figure 26. Receive Telecom Bus Interface Timing                               |    |

| 4.10 VT MAPPER                                                                |    |

| Figure 27. Internal Bus Structure                                             |    |

| Figure 28. Mid Bus Interface                                                  |    |

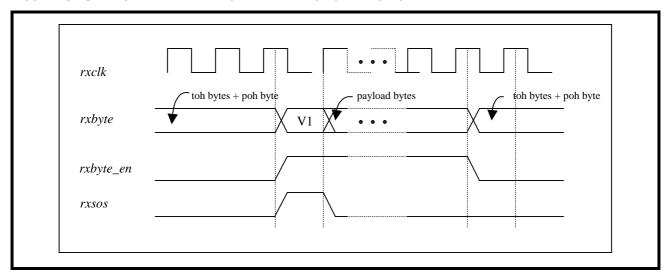

| FIGURE 29. SDH TO VTM DATA TRANSFER WITH ZERO POINTER OFFSET                  |    |

| FIGURE 30. VTM TO SDH DATA TRANSFER                                           |    |

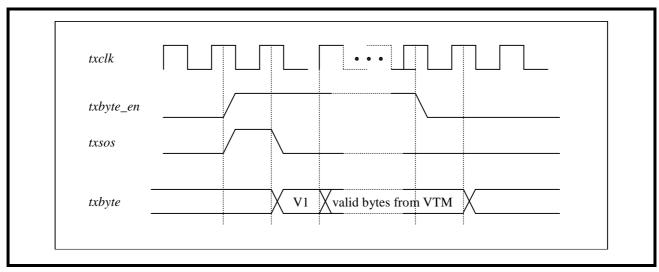

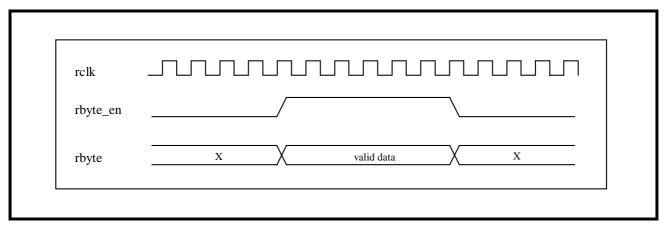

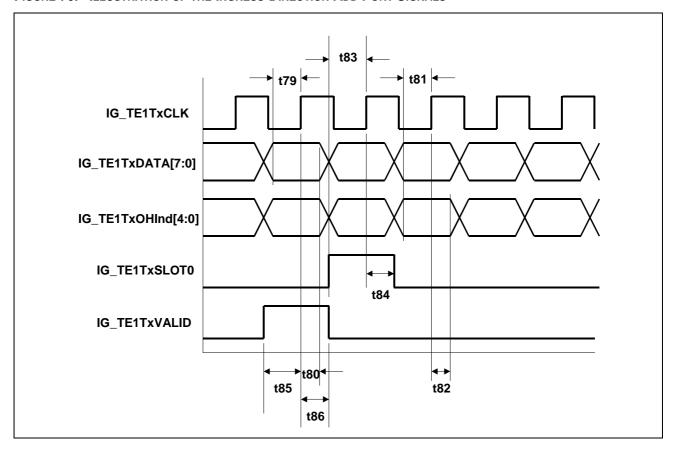

| FIGURE 31. E1 INTERFACE TIMING (INTERNAL TO THE CHIP)                         |    |

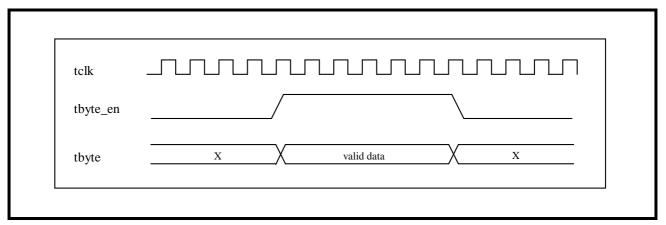

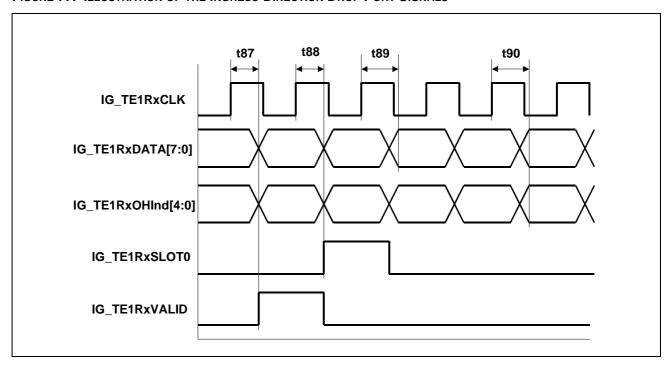

| FIGURE 32. E1 INTERFACE TIMING (E1 SYNCHRONOUS MAPPING, INTERNAL TO THE CHIP) |    |

| TABLE 7: V5 - VT PATH ERROR CHECKING, SIGNAL LABEL AND PATH STATUS            | 76 |

| TABLE 8: N2 BYTE STRUCTURE                                                    |    |

| TABLE 9: B7-B8 MULTIFRAME STRUCTURE                                           |    |

| Table 10: Structure of frames # 73 - 76 of the b7-b8 multiframe               |    |

| Table 11: K4 (b5-b7) coding and interpretation                                |    |

| TABLE 12: Z7/K4 - VT PATH GROWTH AND VT PATH REMOTE DEFECT INDICATION         |    |

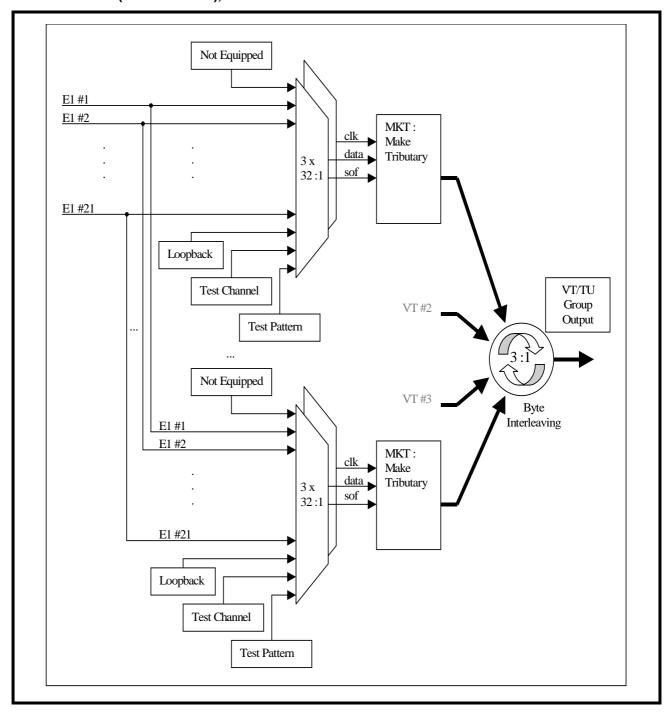

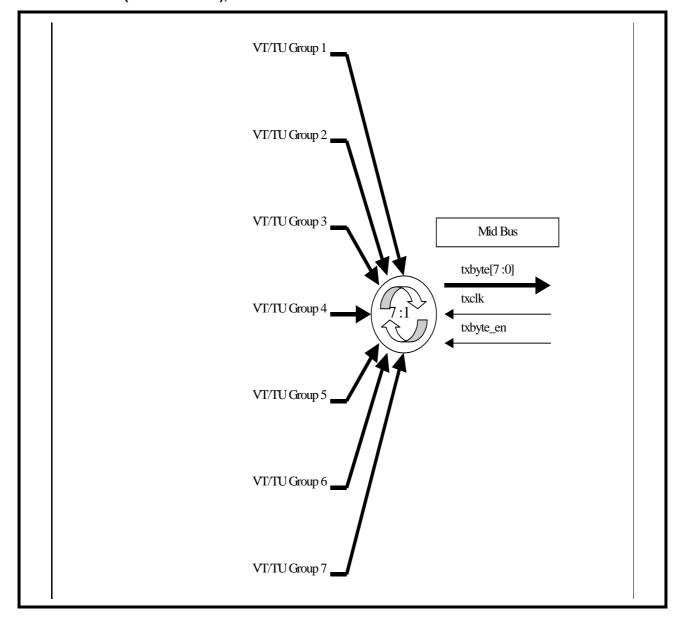

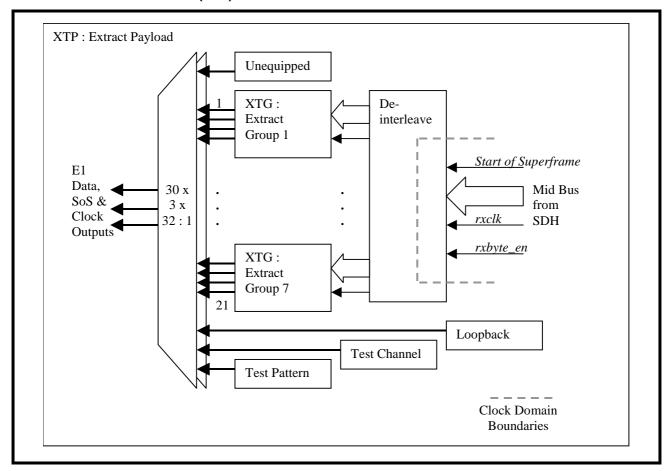

| FIGURE 33. MKP (MAKE PAYLOAD), ONE OF SEVEN MKG: MAKE VT/TU GROUP             |    |

| FIGURE 34. MKP (MAKE PAYLOAD), VT/TU GROUP INTERLEAVING                       |    |

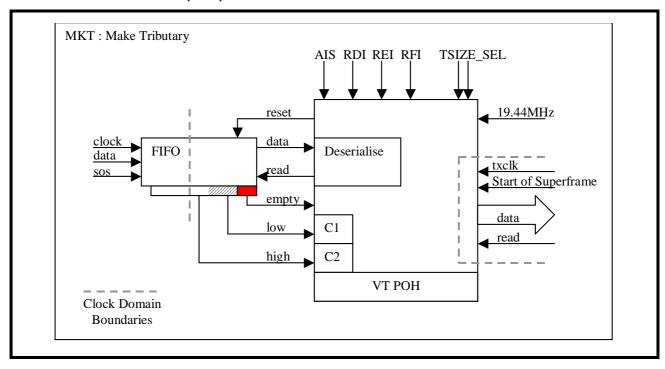

| FIGURE 35. MAKE TRIBUTARY (MKT)                                               |    |

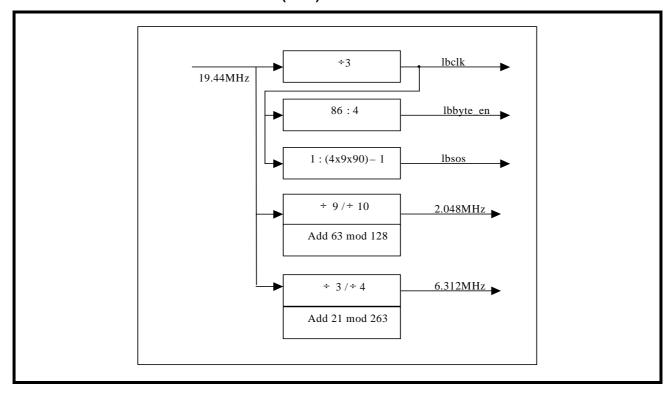

| FIGURE 37. REFERENCE CLOCKS GENERATOR (RCG)                                   | 00 |

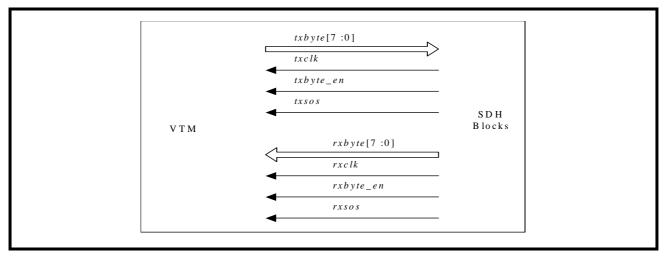

| DATA INTERFACE BETWEEN SDH/FRAMER AND MAPPER                                  |    |

| FIGURE 38. RECEIVE SDH/FRAMER-ATM INTERFACE                                   | -  |

| FIGURE 39. TRANSMIT SDH/FRAMER-ATM INTERFACE                                  |    |

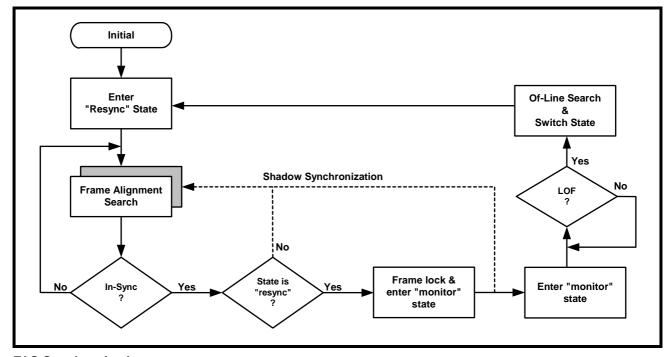

| FIGURE 40. E1 FRAMER SYNCHRONIZATION FLOW DIAGRAM                             | _  |

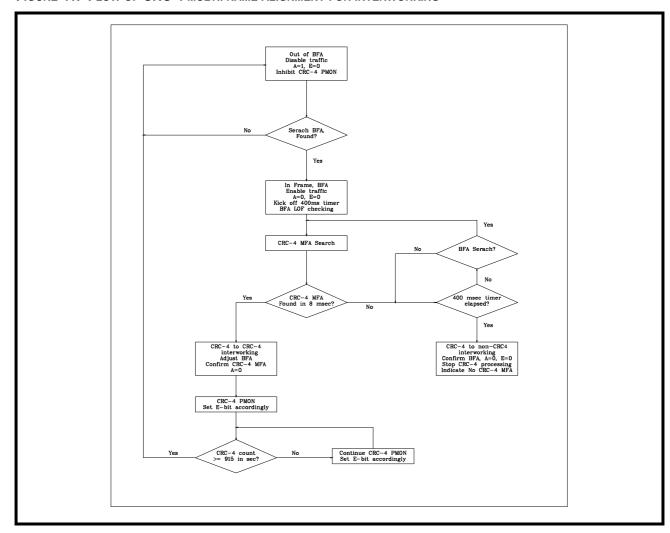

| FIGURE 41. FLOW OF CRC-4 MULTIFRAME ALIGNMENT FOR INTERWORKING                |    |

| 4.11 E1 PHY LOOPBACK DIAGNOSTICS                                              |    |

| 4.11.1 E1 LOOPBACKS                                                           |    |

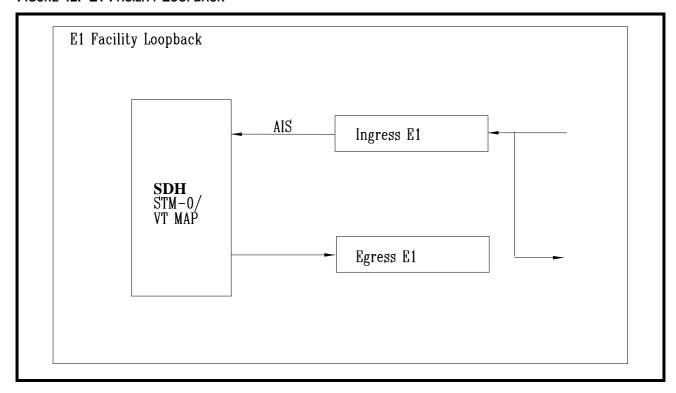

| FIGURE 42. E1 FACILITY LOOPBACK.                                              |    |

| 4.11.2 E1 FACILITY VO LOOPBACK                                                | 94 |

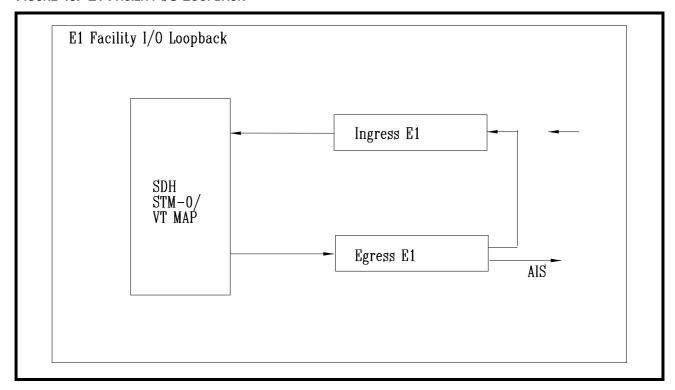

| FIGURE 43. E1 FACILITY I/O LOOPBACK                                           | 94 |

| 4.11.3 E1 MODULE LOOPBACK                                                     | 95 |

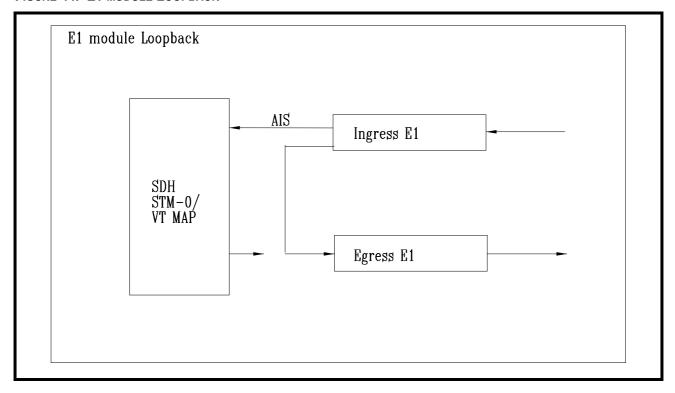

| FIGURE 44. E1 MODULE LOOPBACK                                                 | 95 |

| 4.11.4 ALARM AND AUTO AIS                                                     | 96 |

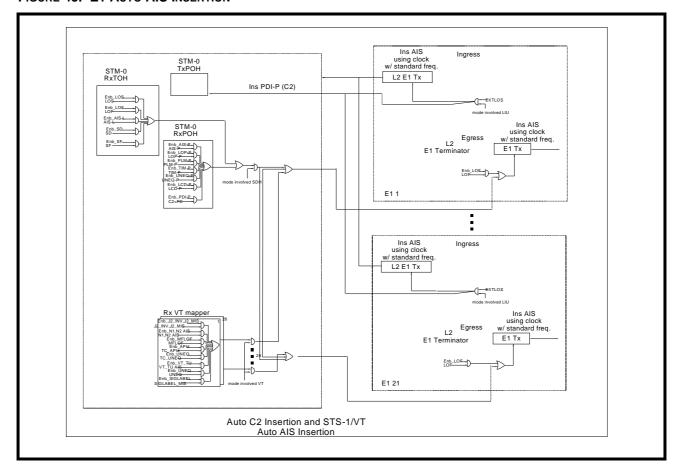

| Figure 45. E1 Auto AIS Insertion                                              |    |

| TABLE 13: E1 TO STM-0 - RESPONSE TIME < 125 US                                |    |

| TABLE 14: STM-0 TO E1 - RESPONSE TIME < 125 USEC                              |    |

| 5.0 ANALOG FRONT END / LINE INTERFACE UNIT (LIU) SECTION                      |    |

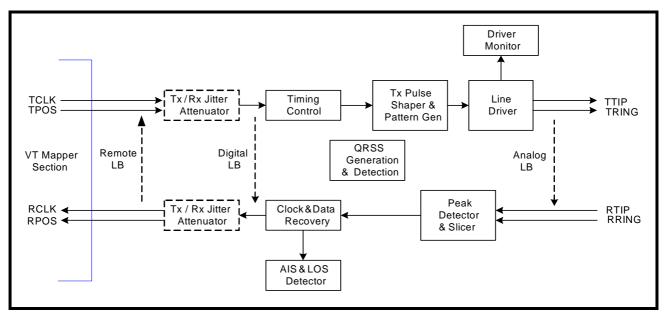

| FIGURE 46. SIMPLIFIED BLOCK DIAGRAM OF THE LIU SECTION                        |    |

| 5.1 TRANSMIT LINE INTERFACE UNIT                                              |    |

| 5.1.1 JITTER ATTENUATOR                                                       |    |

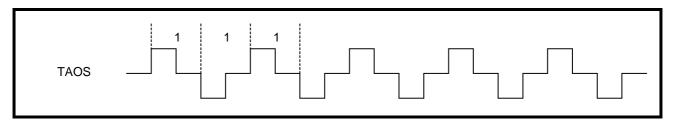

| 5.1.2 TAOS (TRANSMIT ALL ONES)                                                | 99 |

## XRT86SH221

| FIGURE 47. TAOS (TRANSMIT ALL ONES)                                                                                                    |     |

|----------------------------------------------------------------------------------------------------------------------------------------|-----|

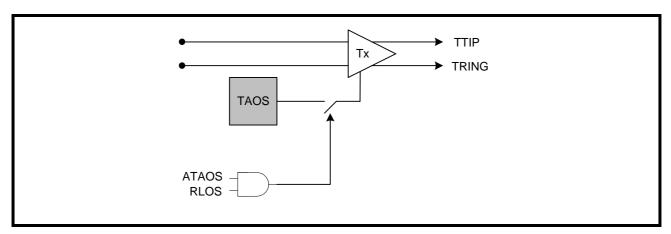

| 5.1.3 ATAOS (AUTOMATIC TRANSMIT ALL ONES)                                                                                              | 99  |

| FIGURE 48. SIMPLIFIED BLOCK DIAGRAM OF THE ATAOS FUNCTION                                                                              |     |

| 5.1.4 QRSS/PRBS GENERATION                                                                                                             |     |

| 5.1.5 TRANSMIT PULSE SHAPER AND FILTER                                                                                                 |     |

| 5.1.6 DMO (DIGITAL MONITOR OUTPUT)                                                                                                     |     |

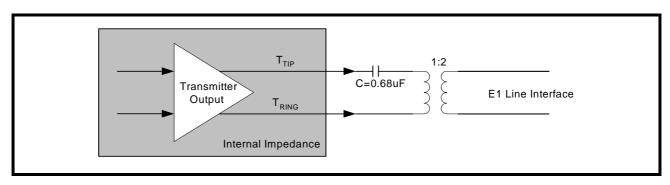

| 5.2 LINE TERMINATION (TTIP/TRING)                                                                                                      |     |

| FIGURE 49. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                                                                       |     |

| 5.3 RECEIVE PATH LINE INTERFACE                                                                                                        |     |

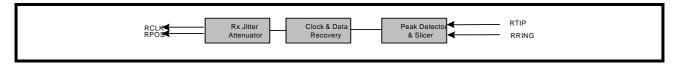

| FIGURE 50. SIMPLIFIED BLOCK DIAGRAM OF THE RECEIVE PATH                                                                                |     |

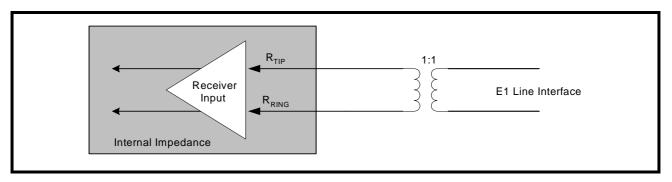

| 5.3.1 LINE TERMINATION (RTIP/RRING)                                                                                                    |     |

| FIGURE 51. TYPICAL CONNECTION DIAGRAM USING INTERNAL TERMINATION                                                                       |     |

| 5.3.2 CLOCK AND DATA RECOVERY                                                                                                          |     |

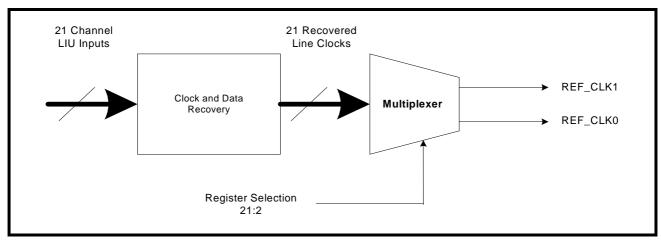

| 5.3.3 RECOVERED LINE CLOCK OUTPUTS                                                                                                     |     |

| FIGURE 53. REF_REC[1:0] RECOVERED LINE CLOCK SELECTION TO OUTPUT PINS                                                                  |     |

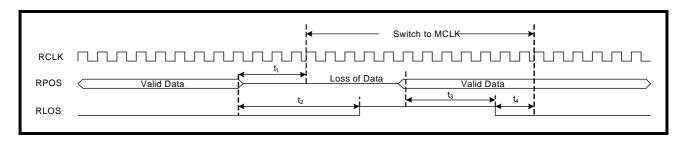

| 5.3.4 RLOS (RECEIVER LOSS OF SIGNAL)                                                                                                   |     |

| 5.3.5 EXLOS (EXTENDED LOSS OF SIGNAL)                                                                                                  |     |

| 5.3.6 JITTER ATTENUATOR                                                                                                                |     |

| 5.3.7 RXMUTE (RECEIVER LOS WITH DATA MUTING)                                                                                           |     |

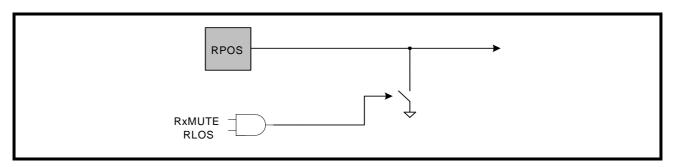

| FIGURE 54. SIMPLIFIED BLOCK DIAGRAM OF THE RXMUTE FUNCTION                                                                             |     |

| 6.0 MEMORY AND REGISTER MAP                                                                                                            | 104 |

| 6.1 MEMORY MAPPED I/O ADDRESSING                                                                                                       |     |

| TABLE 15: CHANNEL MAPPING SCHEME                                                                                                       |     |

| 6.2 OVERVIEW OF CONTROL REGISTERS                                                                                                      |     |

| TABLE 16: MEMORY MAP - E1 FRAMERS                                                                                                      | 104 |

| 6.3 SDH OPERATION CONTROL REGISTER DESCRIPTIONS                                                                                        | 105 |

| TABLE 17: INTERRUPT TYPE SELECT (ITS 0x0001H)                                                                                          |     |

| TABLE 18: RECEIVE STM CLOCK DETECT (RSTMCD 0x0003H)                                                                                    |     |

| TABLE 19: DEVICE ID REGISTER (DEVID 0x0004H)                                                                                           | 106 |

| TABLE 20: REVISION ID REGISTER (REVID 0x0005H)                                                                                         |     |

| TABLE 21: TELECOM BUS PARITY ENABLE (TBPE 0x000BH)                                                                                     |     |

| TABLE 22: TELECOM BUS PARITY ERROR ENABLE (TBPEE 0x000FH)                                                                              |     |

| TABLE 23: OPERATION BLOCK INTERRUPT REGISTER 1 (OPIR1 0x0012H)                                                                         |     |

| TABLE 24: OPERATION BLOCK INTERRUPT REGISTER BYTE 0 (OPIRO 0x0013H)                                                                    |     |

| TABLE 25: OPERATION BLOCK INTERRUPT ENABLE REGISTER BYTE 1 (OPIER1 0x0016H)                                                            |     |

| TABLE 26: OPERATION BLOCK INTERRUPT ENABLE REGISTER BYTE 0 (OPIER0 0x0017H)                                                            |     |

| TABLE 27: DE-SYNC AND AU3 MAPPING CONTROL (DSAU3MC 0X00TBH)  TABLE 28: SDH LOOP BACK SELECT (SDHLBS 0X001FH)                           |     |

| TABLE 29: HIGH BYTE FRAME BOUNDARY LATENCY (HBFBL 0X0034H)                                                                             |     |

| TABLE 30: LOW BYTE FRAME BOUNDARY LATENCY (LBFBL 0x0034H)                                                                              |     |

| TABLE 31: TELECOM BUS CONTROL 1 (TBC1 0x0036H)                                                                                         |     |

| TABLE 32: TELECOM BUS CONTROL 0 (TBC0 0x0037h)                                                                                         |     |

| TABLE 33: GENERAL PURPOSE INPUT/OUTPUT (GPIO 0x0047H)                                                                                  |     |

| TABLE 34: GENERAL PURPOSE INPUT/OUTPUT DIRECTION (GPIOD 0x004BH)                                                                       | 114 |

| TABLE 35: RECOVERED LINE CLOCK REFERENCE 1 (RLCR1 0x004DH)                                                                             | 114 |

| TABLE 36: RECOVERED LINE CLOCK REFERENCE 0 (RLCR0 0x004EH)                                                                             |     |

| TABLE 37: RECOVERED LINE CLOCK SELECT FOR RCLK_REC1 AND RCLK_REC0 HARDWARE PINS                                                        |     |

| TABLE 38: CHANNEL INTERRUPT INDICATION REGISTER 11 (CHIIR11 0x0054H)                                                                   |     |

| TABLE 39: CHANNEL INTERRUPT INDICATION REGISTER 10 (CHIIR10 0x0055H)                                                                   |     |

| TABLE 40: CHANNEL INTERRUPT INDICATION REGISTER 9 (CHIIR9 0x0056H)                                                                     |     |

| TABLE 41: CHANNEL INTERRUPT INDICATION REGISTER 8 (CHIIR8 0x0057H)                                                                     |     |

| TABLE 42: CHANNEL INTERRUPT INDICATION REGISTER 7 (CHIIR7 UXUU36H)  TABLE 43: CHANNEL INTERRUPT INDICATION REGISTER 6 (CHIIR6 0X0059H) |     |

| TABLE 44: CHANNEL INTERRUPT INDICATION REGISTER 6 (CHIIR6 0X0059H)  TABLE 44: CHANNEL INTERRUPT INDICATION REGISTER 5 (CHIIR5 0X005AH) |     |

| TABLE 44. CHANNEL INTERRUPT INDICATION REGISTER 5 (CHIIRS 0X005AH)  TABLE 45: CHANNEL INTERRUPT INDICATION REGISTER 4 (CHIIR4 0X005BH) |     |

| TABLE 46: CHANNEL INTERRUPT INDICATION REGISTER 3 (CHIIR3 0x005CH)                                                                     |     |

| TABLE 47: CHANNEL INTERRUPT INDICATION REGISTER 2 (CHIIR2 0x005DH)                                                                     |     |

| Table 48: Channel Interrupt Indication Register 1 (CHIIR1 0x005Eh)                                                                     |     |

| Table 49: Channel Interrupt Indication Register 0 (CHIIRO 0x005Fh)                                                                     |     |

| 6.4 RECEIVE TRANSPORT OVERHEAD OPERATION CONTROL REGISTER DESCRIPTIONS                                                                 |     |

| Table 50: Receive STM-0/STM-1 Transport Control Register 1 (RTCR1 = 0x0202)                                                            |     |

| TABLE 51: RECEIVE STM-0/STM-1 TRANSPORT CONTROL REGISTER 0 (RTCR0 = 0x0203)                                                            |     |

| TABLE 52: RECEIVE STM-0/STM-1 TRANSPORT STATUS REGISTER 1 (RTSR1 = 0x0206)                                                             |     |

| TABLE 53: RECEIVE STM-0/STM-1 TRANSPORT STATUS REGISTER 0 (RTSR0 = 0x0207)                                                             |     |

| TABLE 54: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT STATUS REGISTER 2 (RTISR2 = 0x0209)                                                  | 124 |

| TABLE 55: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT STATUS REGISTER 1 (RTISR1 = 0x020A)           | 125               |

|-------------------------------------------------------------------------------------------------|-------------------|

| TABLE 56: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT STATUS REGISTER 0 (RTISR0 = 0x020B)           | 127               |

| TABLE 57: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT ENABLE REGISTER 2 (RTIER2 = 0x020D)           |                   |

| TABLE 58: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT ENABLE REGISTER 1 (RTIER1 = 0x020E)           |                   |

| TABLE 59: RECEIVE STM-0/STM-1 TRANSPORT INTERRUPT STATUS REGISTER 0 (RTIERO = 0x020F)           |                   |

|                                                                                                 |                   |

| TABLE 60: RECEIVE STM-0/STM-1 TRANSPORT - B1 BYTE ERROR COUNT REGISTER 3 (B1BECR3 = 0x0210)     |                   |

| TABLE 61: RECEIVE STM-0/STM-1 TRANSPORT - B1 BYTE ERROR COUNT REGISTER 2 (B1BECR2 = 0x0211)     |                   |

| TABLE 62: RECEIVE STM-0/STM-1 TRANSPORT - B1 BYTE ERROR COUNT REGISTER 1 (B1BECR1 = 0x0212)     | 134               |

| TABLE 63: RECEIVE STM-0/STM-1 TRANSPORT - B1 BYTE ERROR COUNT REGISTER 0 (B1BECR0 = 0x0213)     | 135               |

| TABLE 64: RECEIVE STM-0/STM-1 TRANSPORT - B2 BYTE ERROR COUNT REGISTER 3 (B2BECR3= 0x0214)      |                   |

| TABLE 65: RECEIVE STM-0/STM-1 TRANSPORT - B2 BYTE ERROR COUNT REGISTER 2 (B2BECR2 = 0x0215)     |                   |

|                                                                                                 |                   |

| TABLE 66: RECEIVE STM-0/STM-1 TRANSPORT - B2 BYTE ERROR COUNT REGISTER 1 (B2BECR1 = 0x0216)     |                   |

| TABLE 67: RECEIVE STM-0/STM-1 TRANSPORT - B2 BYTE ERROR COUNT REGISTER 0 (B2BECR0 = 0x0217)     |                   |

| TABLE 68: RECEIVE STM-0/STM-1 TRANSPORT - REI-L EVENT COUNT REGISTER 3 (REILECR3 = 0x0218)      |                   |

| TABLE 69: RECEIVE STM-0/STM-1 TRANSPORT - REI-L EVENT COUNT REGISTER 2 (REILECR2 = 0x0219)      | 138               |

| TABLE 70: RECEIVE STM-0/STM-1 TRANSPORT - REI-L EVENT COUNT REGISTER 1 (REILECR1 = 0x021A)      |                   |

| TABLE 71: RECEIVE STM-0/STM-1 TRANSPORT - REI-L EVENT COUNT REGISTER 0 (REILECR0 = 0x021B)      |                   |

|                                                                                                 |                   |

| TABLE 72: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVED K1 BYTE VALUE REGISTER (RK1BVR = 0x021F)     |                   |

| TABLE 73: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVED K2 BYTE VALUE REGISTER (RK2BVR = 0x0223)     |                   |

| TABLE 74: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVED S1 BYTE VALUE REGISTER (RS1BVR = 0x0227)     | 140               |

| TABLE 75: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE IN-SYNC THRESHOLD REGISTER (RISTR = 0x022B)   | 140               |

| TABLE 76: RECEIVE STM-0/STM-1 TRANSPORT - LOS THRESHOLD VALUE 1 (LOSTV1 = 0x022E)               |                   |

| TABLE 77: RECEIVE STM-0/STM-1 TRANSPORT - LOS THRESHOLD VALUE 0 (LOSTV0 = 0x022F)               |                   |

|                                                                                                 |                   |

| TABLE 78: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL 2 (RSFSMI2= 0x0231) . |                   |

| TABLE 79: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL 1 (RSFSMI1 = 0x0232)  |                   |

| TABLE 80: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE SF SET MONITOR INTERVAL 0 (RSFSMI0 = 0x0233)  |                   |

| TABLE 81: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE SF SET THRESHOLD 1 (RSFST1= 0x0236)           | 143               |

| TABLE 82: RECEIVE STM-0/STM-1 TRANSPORT - RECEIVE SF SET THRESHOLD 0 (RSFST0 = 0x0237)          | 144               |

| TABLE 83: RECEIVE STM-0 TRANSPORT - RECEIVE SF CLEAR THRESHOLD 2 (RSFCT2= 0x023A)               |                   |

| TABLE 84: RECEIVE STM-0 TRANSPORT - RECEIVE SF CLEAR THRESHOLD 1 (RSFCT1 = 0x023B)              |                   |

|                                                                                                 |                   |

| TABLE 85: RECEIVE STM-0 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL 0 (RSFCT0 = 0x023D)         |                   |

| TABLE 86: RECEIVE STM-0 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL 1 (RSDSMI1 = 0x023E)        |                   |

| TABLE 87: RECEIVE STM-0 TRANSPORT - RECEIVE SD SET MONITOR INTERVAL 0 (RSDSMI0 = 0x023F)        | 146               |

| TABLE 88: RECEIVE STM-0 TRANSPORT - RECEIVE SD SET THRESHOLD 1 (RSDST1= 0x0242)                 | 146               |

| TABLE 89: RECEIVE STM-0 TRANSPORT - RECEIVE SD SET THRESHOLD 0 (RSDST0 = 0x0243)                | 147               |

| TABLE 90: RECEIVE STM-0 TRANSPORT - RECEIVE SD CLEAR THRESHOLD 1 (RSDCT1= 0x0246)               |                   |

| TABLE 91: RECEIVE STM-0 TRANSPORT - RECEIVE SD CLEAR THRESHOLD 0 (RSDCT0 = 0x0247)              |                   |

|                                                                                                 |                   |

| TABLE 92: RECEIVE STM-0 TRANSPORT - FORCE SEF DEFECT CONDITION REGISTER (FSDCR = 0x024B)        |                   |

| TABLE 93: RECEIVE STM-0 TRANSPORT - RECEIVE SECTION TRACE MESSAGE BUFFER CONTROL REGISTER (RST  | MBCR = 0x024F)    |

| 149                                                                                             |                   |

| TABLE 94: RECEIVE STM-0 TRANSPORT - RECEIVE SD BURST ERROR TOLERANCE 1 (RSDBET1 = 0x0252)       | 150               |

| TABLE 95: RECEIVE STM-0 TRANSPORT - RECEIVE SD BURST ERROR TOLERANCE 0 (RSDBET0 = 0x0253)       | 150               |

| TABLE 96: RECEIVE STM-0 TRANSPORT - RECEIVE SF BURST ERROR TOLERANCE 1 (RSFBET1 = 0x0256)       |                   |

|                                                                                                 |                   |

| TABLE 97: RECEIVE STM-0 TRANSPORT - RECEIVE SF BURST ERROR TOLERANCE 0 (RSFBET0 = 0x0257)       |                   |

| TABLE 98: RECEIVE STM-0 TRANSPORT - RECEIVE SD CLEAR MONITOR INTERVAL 2 (RSDCMI2= 0x0259)       |                   |

| TABLE 99: RECEIVE STM-0 TRANSPORT - RECEIVE SD CLEAR MONITOR INTERVAL 1 (RSDCMI1 = 0x025A)      |                   |

| TABLE 100: RECEIVE STM-0 TRANSPORT - RECEIVE SD CLEAR MONITOR INTERVAL 0 (RSDCMI0 = 0x025B)     | 153               |

| TABLE 101: RECEIVE STM-0 TRANSPORT - RECEIVE SF CLEAR MONITOR INTERVAL 2 (RSFCMI2= 0x025D)      | 153               |

| TABLE 102: RECEIVE STM-0 TRANSPORT - RECEIVE SF CLEAR MONITOR INTERVAL 1 (RSFCMI1 = 0x025E)     |                   |

| TABLE 103: RECEIVE STM-0 TRANSPORT - RECEIVE SF CLEAR MONITOR INTERVAL 0 (RSFCMI0 = 0x025F)     |                   |

|                                                                                                 |                   |

| TABLE 104: RECEIVE STM-0 TRANSPORT - AUTO AIS CONTROL REGISTER (AAISCR = 0x0263)                |                   |

| TABLE 105: RECEIVE STM-0/STM-1 TRANSPORT - A1, A2 BYTE ERROR COUNT REGISTER 1 (A1A2BE1 = 0x026) |                   |

| TABLE 106: RECEIVE STM-0/STM-1 TRANSPORT - A1, A2 BYTE ERROR COUNT REGISTER 0 (A1A2BE0 = 0x026) | F) 158            |

| 6.5 RECEIVE PATH OVERHEAD OPERATION CONTROL REGISTER DESCRIPTIONS                               | 159               |

| Table 107: Receive STM-0 Path - Receive Control Register 0 (RCR0 = 0x0283)                      | 150               |

| TABLE 108: RECEIVE STM-0 PATH - CONTROL REGISTER (PCR = 0x0286)                                 |                   |

|                                                                                                 |                   |

| TABLE 109: RECEIVE STM-0 PATH - SDH RECEIVE POH STATUS (RPOHS = 0x0287)                         |                   |

| TABLE 110: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT STATUS 2 (RPIS2 = 0x0289)            |                   |

| TABLE 111: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT STATUS 1 (RPIS1 = 0x028A)            | 163               |

| TABLE 112: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT STATUS 0 (RPIS0 = 0x028B)            |                   |

| TABLE 113: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT ENABLE 2 (RPIE2 = 0x028D)            |                   |

| TABLE 114: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT ENABLE 1 (RPIE1 = 0x028E)            |                   |

| TABLE 117. NEOLIVE OTHER TATE OF TRECLIVE FAIR INTERNOFT LIVABLE I (N. ILI - UNUZOL)            | 160               |

| TABLE 115: DECEME STM O DATH. SDU DECEME DATH INTERDUST FARDLE O (DDIEG. OVOCCE)                |                   |

| TABLE 115: RECEIVE STM-0 PATH - SDH RECEIVE PATH INTERRUPT ENABLE 0 (RPIE0 = 0x028F)            | 171               |

| TABLE 116: RECEIVE STM-0 PATH - SDH RECEIVE RDI-P REGISTER (RRDIPR = 0x0293)                    | 171<br>173        |

| ,                                                                                               | 171<br>173<br>173 |

# **PRELIMINARY**

| TABLE                                                                                                                                                                                                                                                                                                                               | 119:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - B3 BYTE ERROR COUNT REGISTER 3 (B3BECR3 = 0x0298)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 174                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| TABLE                                                                                                                                                                                                                                                                                                                               | 120:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - B3 BYTE ERROR COUNT REGISTER 2 (B3BECR2 = 0x0299)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 175                                                                                                             |

| TABLE                                                                                                                                                                                                                                                                                                                               | 121:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - B3 BYTE ERROR COUNT REGISTER 1 (B3BECR1 = 0x029A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 175                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - B3 BYTE ERROR COUNT REGISTER 0 (B3BECR0 = 0x029B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - REI-P EVENT COUNT REGISTER 3 (REIPECR3 = 0x029C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - REI-P EVENT COUNT REGISTER 2 (REIPECR2 = 0x029D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - REI-P EVENT COUNT REGISTER 2 (REIP ECR2 = 0x029E)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - REI-P EVENT COUNT REGISTER 0 (REIPECR0 = 0x029F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | $\textit{Receive STM-0 Path - Receive Path Trace Message Buffer Control Register (RPTMBCR = 0x02A3) \}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - POINTER VALUE 1 (PV1 = 0x02A6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                 |

| TABLE                                                                                                                                                                                                                                                                                                                               | 129:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - POINTER VALUE 0 (PV0 = 0x02A7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 180                                                                                                             |

| TABLE                                                                                                                                                                                                                                                                                                                               | 130:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - RECEIVE AUTO AIS - C2 BYTE VALUE REGISTER (AISC2VR = 0x02B9)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 180                                                                                                             |

| TABLE                                                                                                                                                                                                                                                                                                                               | 131:                                                                                                                                                                                                 | RECEIVE STM-0 PATH - RECEIVE AUTO AIS - C2 BYTE CONTROL REGISTER (AISC2CR = 0x02BA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 180                                                                                                             |

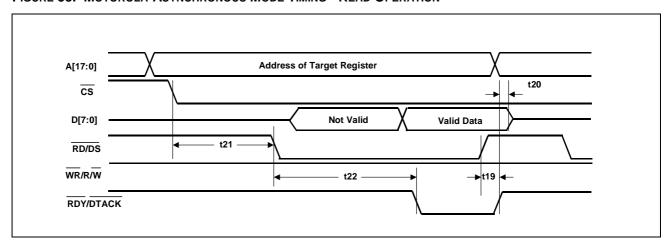

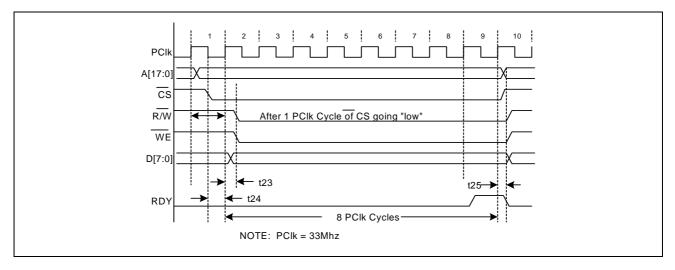

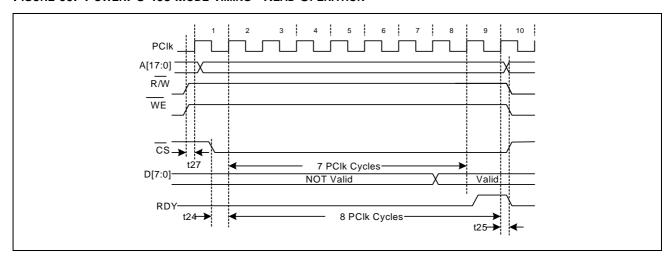

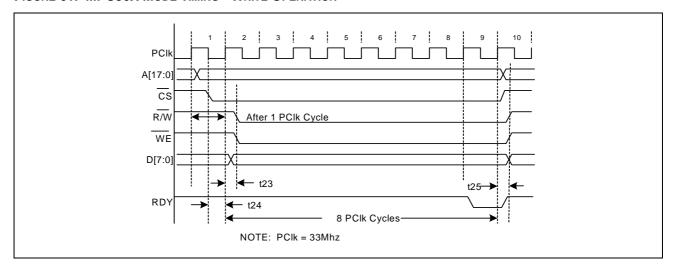

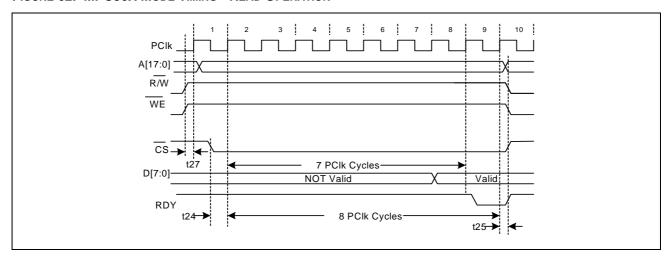

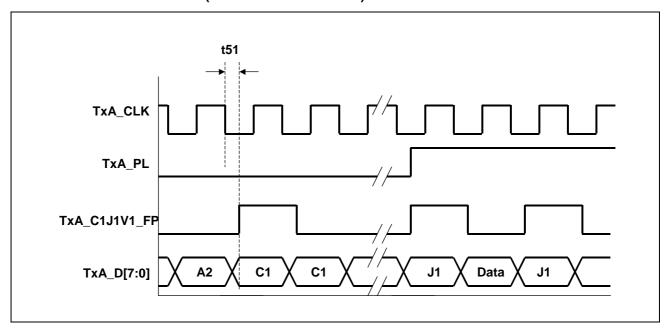

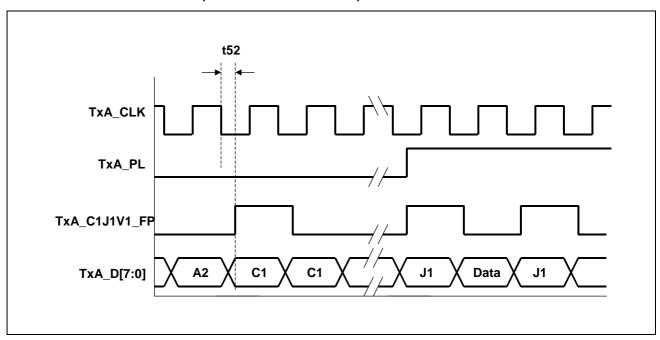

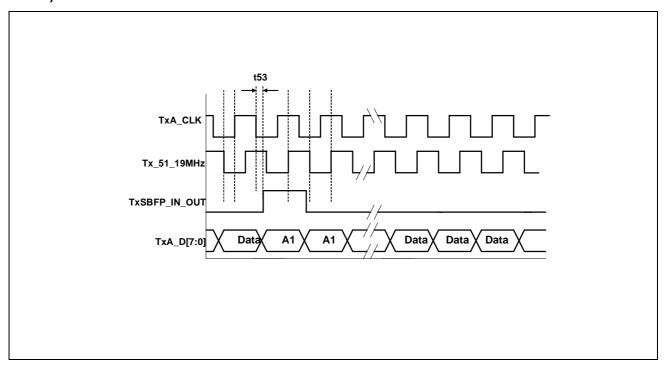

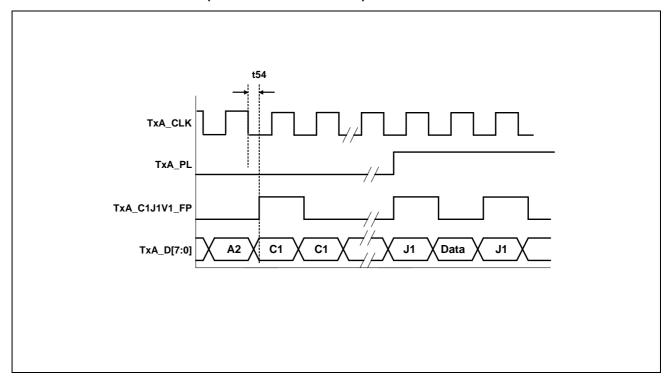

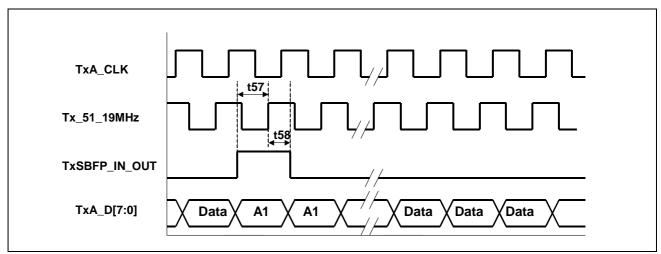

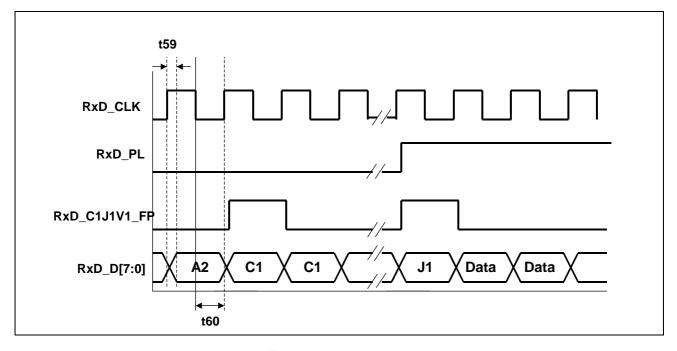

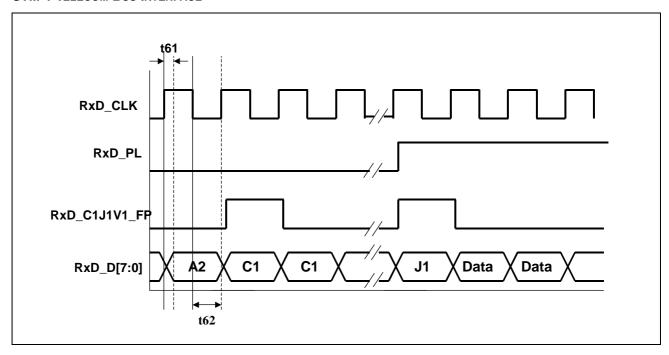

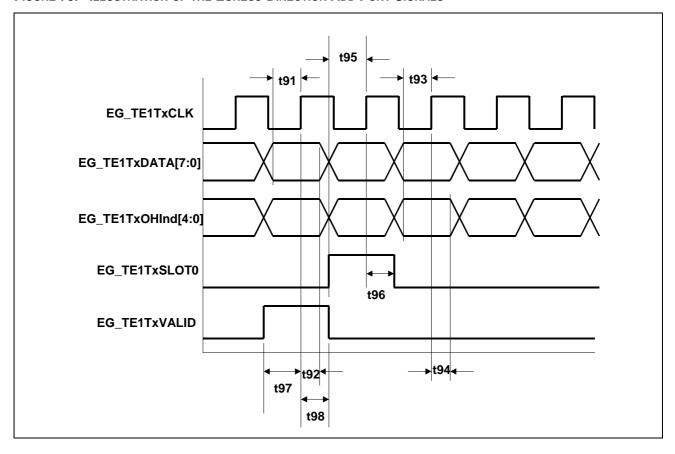

|                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                      | RECEIVE STM-0 PATH - AUTO AIS CONTROL REGISTER (AUTOACR = 0x02BB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                 |