# **80C03** AutoDUPLEX<sup>™</sup> CMOS Ethernet Data Link Controller

96253

### Features

- Low Power CMOS Technology

- Optimized for Embedded Ethernet Applications

- Meets ANSI/IEEE 802.3 and ISO 8802-3 Standards for Ethernet (10Base-5) Thin Net (10Base-2) (10Base-T) and Twisted Pair

- 10 MHz Serial/Parallel Conversion

- Preamble Generation and Removal

- Automatic 32-Bit FCS (CRC) Generation and Checking

- Collision Handling, Transmission Deferral and Retransmission with Automatic Jam and Backoff Functions

- Error Interrupt and Status Generation

- Available as "Ethernet Core" for Custom ASIC Applications

- Single 5 V± 10% Power Supply

- Standard CPU and Peripheral Interface Control Signals

- Loopback Capability for Diagnostics

- Single Phase Clock

- Inputs and Outputs TTL Compatible

Note: Check for latest Data Sheet revision before starting any designs.

SEEQ Data Sheets are now on the Web, at www.lsilogic.com.

This document is an LSI Logic document. Any reference to SEEQ Technology should be considered LSI Logic.

- Compatible with SEEQ 8003 and Provides Additional Features

- 64 bit Multicast Filter

- Transmit Collision Counter

- Total Collision Counter

- Reports Status of "Carrier" and "SQE" During Transmits

- Transmit No CRC Mode

- Transmit No Preamble Mode

- Transmit Packet Autopadding Mode

- Receive CRC Mode

- Receive Own Transmit Disable Mode

- Group Address Mode

- Fast Receive Discard Mode

- Full Duplex Mode

- Supports AutoDUPLEX Mode for Automatic Full Duplex Operation— Provides 20 MBits/sec Bandwidth for Switched Networks

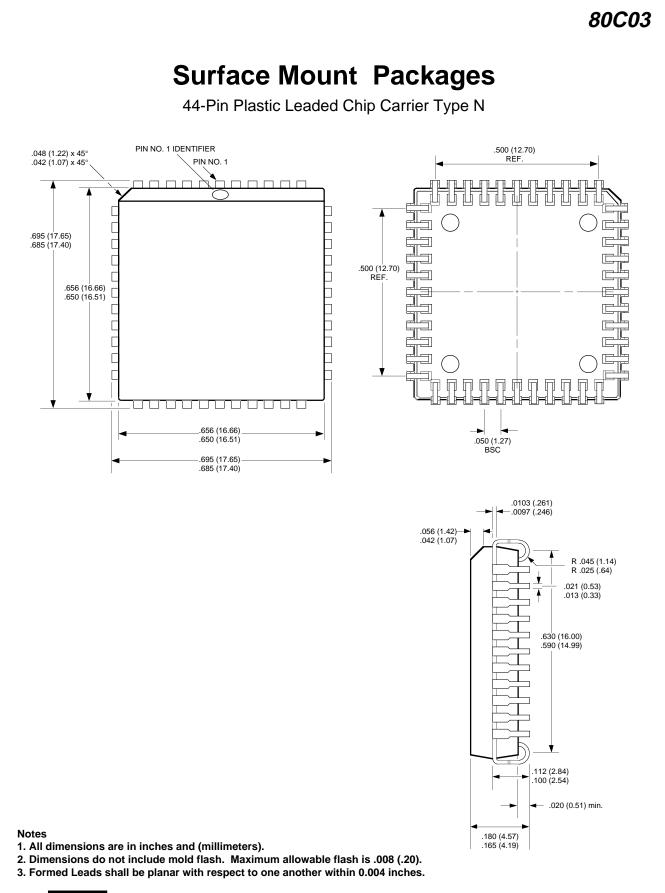

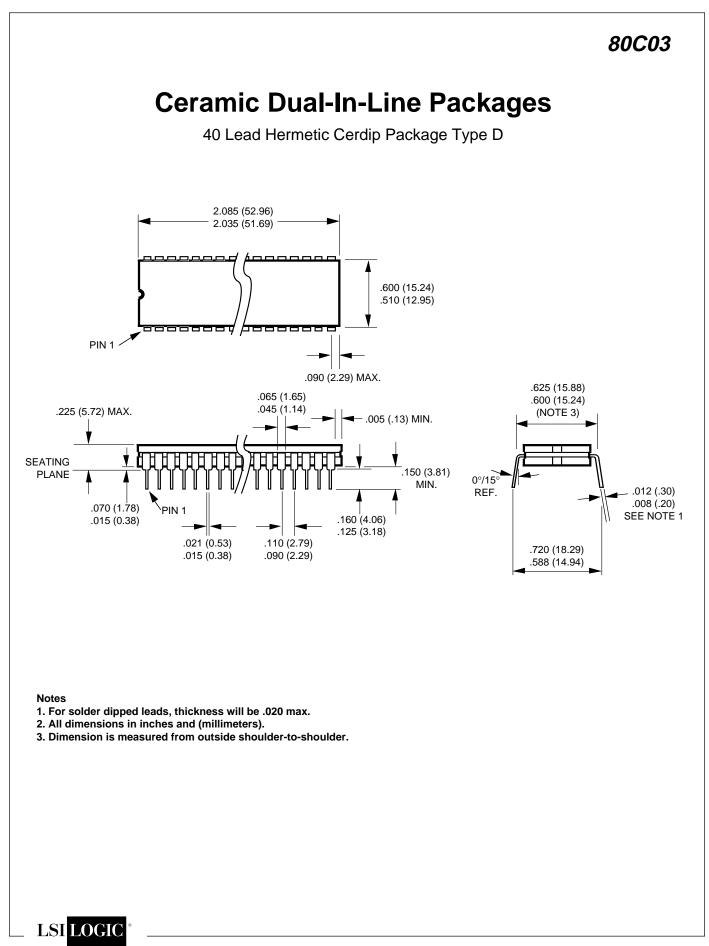

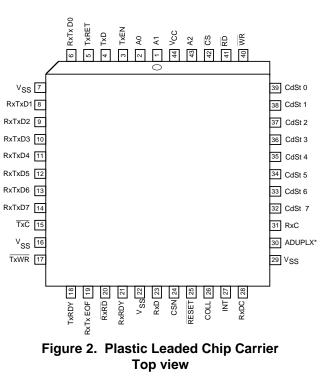

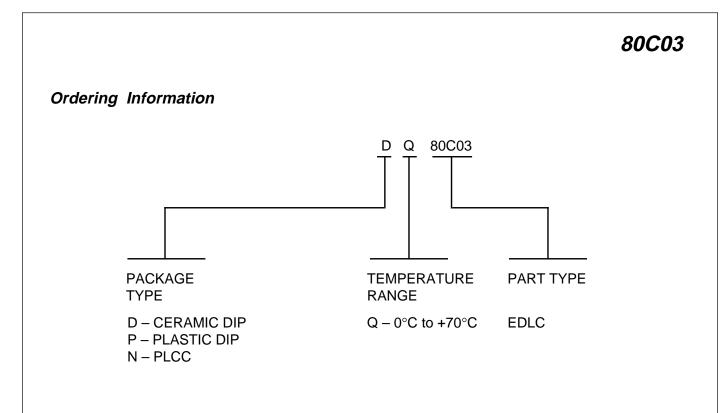

- 40 Pin DIP Package, 44 Pin PLCC

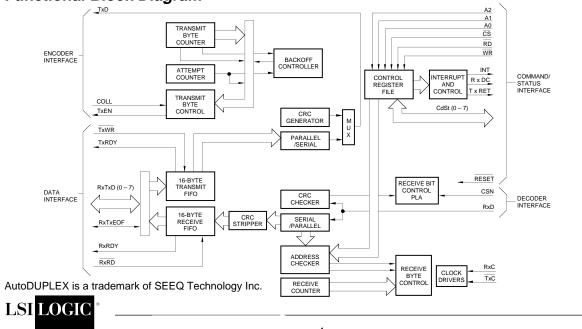

### Functional Block Diagram

### Description

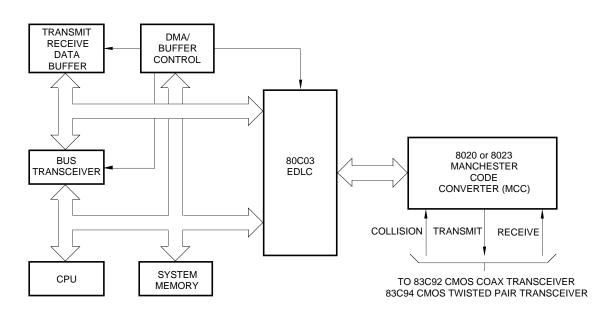

The SEEQ Ethernet Data Link Controller (EDLC®) is designed to support Data Link Layer (layer 2) of the Ethernet specification for Local Area Networks (LAN). The system interface is optimized for ease of connection to commonly available DMA Controllers and specifically for BURST MODE OPERATION. The 80C03 interfaces directly to the 8023A and 8020 Manchester Code Converters (MCC<sup>TM</sup>) to complete the station resident Ethernet functions. The protocol used is Carrier Sense, Multiple Access with Collision Detection (CSMA/CD). The 80C03 EDLC chip is a single VLSI device which is designed to greatly simplify the development of Ethernet communication in computer based systems. The 80C03 provides an economic solution for the construction of an Ethernet node, providing high speed data communication at 10 Megabits/second and sees applications in terminals, workstations, personal computers, small business systems, and large computer systems, in both the office and industrial environment. The 80C03 EDLC chip has a universal system interface compatible with almost any microprocessor, microcomputer, or system bus, allowing the system designer to make the price/performance tradeoffs for each application. The transmit and receive sections of the EDLC chip are independent and can operate simultaneously to allow reception of a transmitted frame for use in loopback diagnostics modes.

The 80C03 is compatible with SEEQ 8003 and provides additional programmable features. The features enabled

| A1      | 1  | 40 | Vcc   |

|---------|----|----|-------|

| A0 🗌    | 2  | 39 | A2    |

| TxEN    | 3  | 38 | 🗋 cs  |

| TxD     | 4  | 37 |       |

| TxRET   | 5  | 36 | WR    |

| RxTxD0  | 6  | 35 | CdSt0 |

| RxTxD1  | 7  | 34 | CdSt1 |

| RxTxD2  | 8  | 33 | CdSt2 |

| RxTxD3  | 9  | 32 | CdSt3 |

| RxTxD4  | 10 | 31 | CdSt4 |

| RxTxD5  | 11 | 30 | CdSt5 |

| RxTxD6  | 12 | 29 | CdSt6 |

| RxTxD7  | 13 | 28 | CdSt7 |

| TxC     | 14 | 27 | RxC   |

| TxWR    | 15 | 26 | RxDC  |

| TxRDY   | 16 | 25 | INT   |

| RXTXEOF | 17 | 24 | COLL  |

| RxRD    | 18 | 23 | RESET |

| RxRDY   | 19 | 22 | CSN   |

| Vss 🗌   | 20 | 21 | RxD   |

|         |    |    |       |

### Figure 1. Dual-In-Line Top View

EDLC is a registered trademark of SEEQ Technology Inc. MCC is a trademarks of SEEQ Technology Inc.

MD400121/C

on demand are: 64 bit Multicast filter, Transmit Collision Counter, Total Collision Counter, Status Reporting of Carrier and SQE during transmits, Transmit no CRC, Transmit no Preamble, Transmit Packet Autopadding, Receive CRC, Receive Own Transmit disable, Receive Group Address mode, Fast Receive Discard Mode, and Full Duplex Mode.

### **Functional Description**

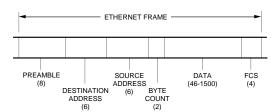

### Frame Format

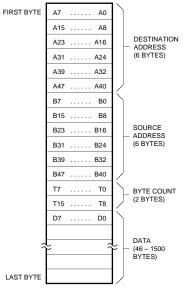

On an Ethernet communication network, information is transmitted and received in packets or frames. An Ethernet frame consists of a preamble, two address fields, a byte-count field, a data field and a frame check sequence (FCS). Each field has a specific format which is described in detail below. An Ethernet frame has a minimum length of 64 bytes and a maximum length of 1518 bytes exclusive of the preamble. The Ethernet frame format is shown below.

### NOTE:

Field length in bytes in parentheses.

2

**Preamble:** The preamble is a 64-bit field consisting of 62 alternating "1"s and "0"s followed by a "11" End-of-Preamble indicator.

**Destination Address:** The Destination Address is a 6byte field containing either a specific Station Address, a Broadcast Address, or a Multicast Address to which this frame is directed.

**Source Address:** The Source Address is a 6-byte field containing the specific Station Address from which this frame originated.

**Byte-Count Field:** The Byte-Count Field consists of two bytes providing the number of valid data bytes in the Data Field, 46 to 1500. This field is uninterpreted at the Data Link Layer, and is passed through the EDLC chip to be handled at the Client Layer.

**Data Field:** The Data Field consists of 46 to 1500 bytes of information which are fully transparent in the sense that any arbitrary sequence of bytes may occur.

**Frame Check Sequence:** The Frame Check Sequence (FCS) field is a 32-bit cyclic redundancy check (CRC) value computed as a function of the Destination Address Field, Source Address Field, Type Field and Data Field. The FCS is appended to each transmitted frame, and used at reception to determine if the received frame is valid.

#### Transmitting

The transmit data stream consists of the Preamble, four information fields, and the FCS which is computed in real time by the EDLC chip and automatically appended to the frame at the end of the serial data. The Preamble is also generated by the EDLC chip and transmitted immediately prior to the Destination Address. Destination Address, Source Address, Type Field and Data Field are prepared in the buffer memory prior to initiating transmission. The

### Figure 3. Typical Frame Buffer Format for Byte-Organized Memory

EDLC chip encapsulates these fields into an Ethernet frame by inserting a preamble prior to these information fields and appending a CRC after the information fields. The chip can be programmed to exclude inclusion of the preamble and/or the FCS from the transmit data stream. In this case it is assumed that the preamble and FCS are provided as part of the data written to the chip.

#### Transmission Initiation/Deferral

The Ethernet node initiates a transmission by storing the entire information content of the frame to be transmitted in an external buffer memory, and then transferring initial frame bytes to the EDLC Transmit FIFO. "Transmit-buffer to FIFO" transfers are coordinated via the TxWR and TxRDY handshake interface, i.e., bytes are written to the

FIFO via TxWR only when TxRDY is HIGH. Actual transmission of the data onto the network will only occur if the network has not been busy for the minimum defer time (9.6  $\mu$ s) and any Backoff time requirements have been satisfied. When transmission begins, the EDLC chip activates the transmit enable (TxEN) line concurrently with the transmission of the first bit of the Preamble and keeps it active for the duration of the transmission.

### Collision

When concurrent transmissions from two or more Ethernet nodes occur (collision), the EDLC chip halts the transmission of the data bytes in the Transmit FIFO and transmits a Jam pattern consisting of 55555555 hex. At the end of the Jam transmission, the EDLC chip issues a TxRET signal to the CPU and begins the Backoff wait period.

To reinitiate transmission, the initial bytes of the frame information fields must be reloaded into the EDLC Transmit FIFO. The TxRET is used to indicate to the buffer manager the need for frame reinitialization. The reloading of the Transmit FIFO may be done prior to the Backoff interval elapsing, so that no additional delay need be incurred to retransmission.

Scheduling of retransmission is determined by a controlled randomization process called Truncated Binary Exponential Backoff. The EDLC chip waits a random interval between 0 and  $2^{\kappa}$  slot times (51.2 µs per slot time) before attempting retransmission, where "K" is the current transmission attempt number (not to exceed 10).

When 16 consecutive attempts have been made at transmission and all have been terminated due to collision, the EDLC Transmit Control sets an error status bit and issues an interrupt to the CPU if enabled.

### Terminating Transmission

Transmission Terminates under the following conditions:

**Normal:** The frame has been transmitted successfully without contention. Loading of the last data byte into the Transmit FIFO is signaled to the EDLC chip by activation of the RxTxEOF signal concurrently with the last byte of data loaded into the Transmit FIFO. This line acts as a ninth bit in the Transmit FIFO. When this last byte is serialized, if the chip is not in Transmit No CRC mode, then the CRC is appended and transmitted concluding frame transmission. The Transmission Successful bit of the Transmit Status Register will be set by a normal termination.

**Collision:** Transmission attempted by two or more Ethernet nodes. The Jam sequence is transmitted, the Colli-

sion status bit is set, transmit Collision Counter is updated, the TxRET signal is generated, and the Backoff interval begun.

**Underflow:** Transmit data is not ready when needed for transmission. Once transmission has begun, the EDLC chip on average requires one transmit byte every 800 ns in order to avoid Transmit FIFO underflow (starvation). If this condition occurs, the EDLC chip terminates the transmission, issues a TxRET signal, and sets the Transmit-Underflow status bit.

**16 Transmission Attempts:** If a Collision occurs for the sixteenth consecutive time, the 16-Transmission-Attempts status bit is set, the Collision status bit is set, the TxRET signal is generated, and the Backoff interval begun. The counter that keeps track of the number of collisions is modulo 16 and therefore rolls over on the 17th collision. Bits 15 to 11 on the Collision Count Registers (80C03 mode) indicates the attempt counter used for Collision back-off. These can be read and cleared as described in the Transmit Command register description.

At the completion of every transmission or retransmission, new status information is loaded into the Transmit Status Register. Dependent upon the bits enabled in the Transmit Command Register, an interrupt will be generated for the just completed transmission. In both collision and underflow the TxRET signal is activated.

### Receiving

The EDLC chip is continuously monitoring the network. When activity is recognized via the Carrier Sense (CSN) line going active, the EDLC chip synchronizes itself to the incoming data stream during the Preamble, and then examines the destination address field of the frame. Depending on the Address Match Mode specified, the EDLC chip will either recognize the frame as being addressed to itself in a general or specific fashion or abort the frame reception. The 80C03 also allows counting of all collisions seen on the network.

### Preamble Processing

The EDLC chip recognizes activity on the Ethernet via the Carrier Sense line. The Preamble is normally 64 bits (8 bytes) long. The Preamble consists of a sequence of 62 alternating "1"s and "0"s followed by "11", with the frame information fields immediately following. In order for the decoder phase-lock to occur, the EDLC chip waits 16 bit times before looking for the "11" end of preamble indicator. If the EDLC chip receives a "00" before receiving the "11" in the Preamble, an error condition has occurred. The frame is not received, and the EDLC chip begins monitoring the network for a carrier again.

### Figure 5. Typical Ethernet Node Configuration

### Address Matching

Ethernet addresses consist of two 6-byte fields. The first bit of the address signifies whether it is a Station Address or a Multicast/Broadcast Address.

| First Bit | Address                                  |

|-----------|------------------------------------------|

| 0         | Station Address (Physical)               |

| 1         | Multicast/Broadcast Address<br>(logical) |

Address matching occurs as follows:

**Station Address:** All destination address bytes must match the corresponding bytes found in the Station Address Register. If Group Address mode is enabled, the last 4 bits of the station address are masked out during address matching.

After computing the FCS on the first six bytes of the address field (Destination address), the 80C03 uses bits 0 thru 5 as an address to the Multi-cast address filter register. Bit 0 of the FCS is assumed to be where receive data enters the FCS generation circuitry. If the corresponding bit addressed in the Multicast address filter register is a '1' the 80C03 will receive the frame, otherwise it will discard the frame. Addressing of the Multicast address filter register s filter register occurs using bits 0 thru 2 to deter-

mine which byte is selected and bits 3 thru 5 to determine which bit according to the following tables:

| FCS               |             | Byte Selected  |

|-------------------|-------------|----------------|

| 0.0               |             | Buto O         |

| 0 0               | 0           | Byte 0         |

| 00                |             | Byte 1         |

| 0 1               | 0           | Byte 2         |

| 0 1               | 1           | Byte 3         |

| 1 1               | 1           | Byte 7         |

| FCS               | Bits        | Bit Selected   |

| 4 5               | 6           |                |

| 4 5               | 0           |                |

| 4 J<br>0 0        | 0           | Bit 0          |

|                   | 0           | Bit 0<br>Bit 1 |

| 0 0               | 0<br>1      | 2.1.0          |

| 0 0 0             | 0<br>1<br>0 | Bit 1          |

| 0 0<br>0 0<br>0 1 | 0<br>1<br>0 | Bit 1<br>Bit 2 |

**Multicast Address:** If the first bit of the incoming address is a 1 and the EDLC chip is programmed to accept Multicast Addresses without using Hash filtering, the frame is received. The 80C03 also can be programmed to use hash filter for determining acceptance of multicast addresses.

**Broadcast Address:** The six incoming destination address bytes must all be FF hex. If the EDLC chip is programmed to accept broadcast or Multicast Addresses the frame will be received.

If the incoming frame is addressed to the EDLC chip specifically (Destination Address matches the contents of the Station Address Register), or is of general or group interest (Broadcast or Multicast Address), the EDLC chip will pass the frame exclusive of Preamble and FCS to the CPU buffer and indicate any error conditions at the end of the frame. If, however, the address does not match, as soon as the mismatch is recognized the EDLC chip will terminate reception and issue an RxDC.

The EDLC chip may be programmed via the Match Mode bits of the Receive Command Register to ignore all frames (Disable Receiver), accept all frames (Promiscuous mode), accept frames with the proper Station Address or the Broadcast Address (Station/Broadcast), or accept all frames with the proper Station Address, the Broadcast Address, or all Multicast Addresses (Station/Broadcast/ Multicast).

### Terminating Reception

Reception is terminated when either of the following conditions occur:

*Carrier Sense Inactive:* Indicates that traffic is no longer present on the Ethernet cable.

**Overflow:** The host node for some reason is not able to empty the Receive FIFO as rapidly as it is filled, and an error occurs as frame data is lost. On average the Receive FIFO must be serviced every 800 ns to avoid this condition.

### Frame Reception Conditions

Upon terminating reception, the EDLC chip will determine the status of the received frame and conditionally load it into the Receive Status Register. An interrupt will be issued if the appropriate conditions as specified in the Receive Command Register are present. The EDLC chip may report the following conditions at the end of frame reception:

**Overflow:** The EDLC internal Receive FIFO overflows.

**Dribble Error:** Carrier Sense did not go inactive on a receive data byte boundary.

**CRC Error:** The 32-bit CRC transmitted with the frame does not match that calculated upon reception.

**Short Frame:** A frame containing less than 64 bytes of information was received (including FCS).

**Good Frame:** A frame is received that does not have a CRC error, Shortframe or Overflow Condition.

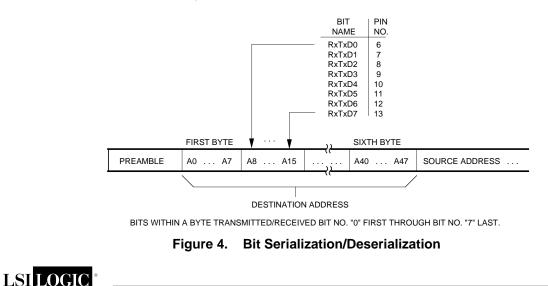

#### System Interface

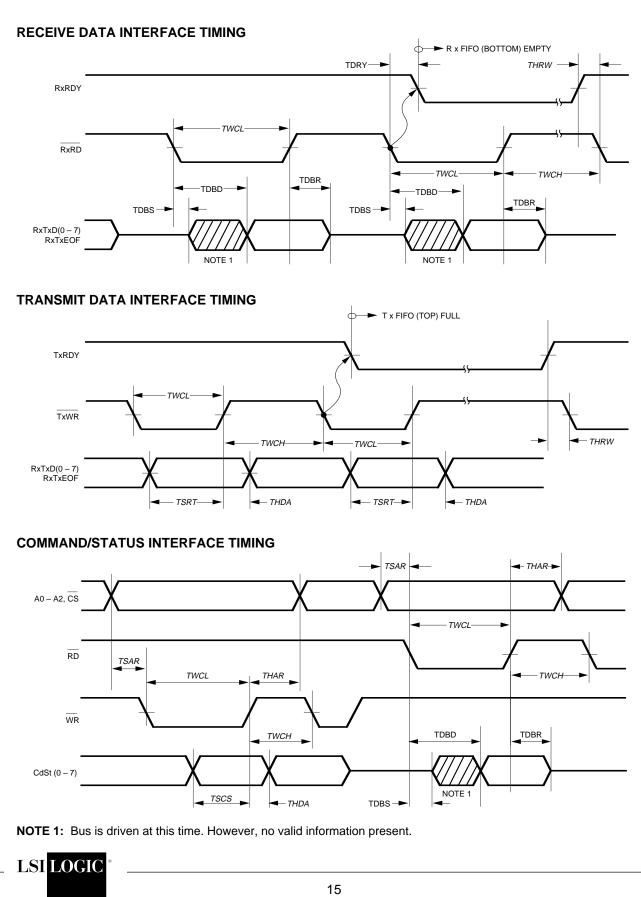

The EDLC chip system interface consists of two independent busses and respective control signals. Data is read and written over the Receive/Transmit Data Bus RxTxD (0-7). These transfers are controlled by the TxRDY and TxWR signals for transmitted data and RxRDY and RxRD for received data. All Commands and Station Addresses are written, and all status read over a separate Command/ Status Bus CdSt (0-7). These transfers are controlled by the  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$  and A0-A2 signals. The EDLC chip's command and status registers may be accessed at any time. However, it is recommended that writing to the command register be done only during interframe gaps.

With the exception of the two Match Mode bits in the Receive Command Register, all bits in both command registers are interrupt enable bits. Changing the interrupt enable bits during frame transmission does not affect the frame integrity. Asynchronous error events, however, e.g., overflow, underflow, etc., may cause chip operation to vary, if their corresponding enable bits are being altered at the same time.

Reading the status registers may also occur at any time during transmission or reception.

#### Internal Register Addressing (8003 mode)

|   | Register<br>Address |    |    | Register Description |                |  |

|---|---------------------|----|----|----------------------|----------------|--|

|   | A2                  | A1 | A0 | Read Write           |                |  |

| 0 | 0                   | 0  | 0  |                      | Station Addr 0 |  |

| 1 | 0                   | 0  | 1  | _                    | Station Addr 1 |  |

| 2 | 0                   | 1  | 0  |                      | Station Addr 2 |  |

| 3 | 0                   | 1  | 1  |                      | Station Addr 3 |  |

| 4 | 1                   | 0  | 0  |                      | Station Addr 4 |  |

| 5 | 1                   | 0  | 1  |                      | Station Addr 5 |  |

| 6 | 1                   | 1  | 0  | Rx Status            | Rx Command     |  |

| 7 | 1                   | 1  | 1  | Tx Status            | Tx Command     |  |

Status Registers are read only registers. Command and Station Address registers are write only registers. Access to these registers is via the CPU interface: Control signals  $\overline{CS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , and the Command/Status Data Bus CdSt (0-7).

#### Station Address Register

The Station Address Register is 6 bytes in length. The contents may be written in any order, with bit "0" of byte "0" corresponding to the first bit received in the data stream, and indicating whether the address is physical or logical. Bit 7 of station address byte 5 is compared to the last bit of

the received destination address. The Station Address should be programmed prior to enabling the receiver.

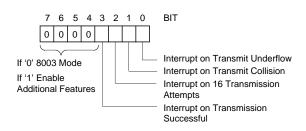

### Transmit Command Register

The Transmit Command Register is an interrupt mask register, which provides for control of the conditions allowed to generate transmit interrupts. Each of the four least significant bits of the register may be individually set or cleared. When set, the occurrence of the associated condition will cause an interrupt to be generated. The four specific conditions for which interrupts may be generated are:

- Underflow

- Collision

- 16 Collisions

- Transmission Successful

The interrupt signal INT will be set when one or more of the specified transmission termination conditions occurs and the associated command bit has been set. The interrupt signal INT will be cleared when the Transmit Status Register is read.

All bits of the Transmit Command Register are cleared upon chip reset.

### Transmit Command Register Format

Transmission Successful is set only on the successful transmission or retransmission of a frame.

80C03 provides additional new features which are enabled depending on writing '1's to bits 7,6,5,4 of the transmit command register. If these four bits are always '0' then the 80C03 will be exactly compatible to SEEQ 8003 EDLC.

The bits 6,5 of transmit command register are used to address new registers on 80C03 together with the A2, A1, A0,  $\overline{RD}$   $\overline{WR}$ ,  $\overline{CS}$  pins. (see table Page 9)

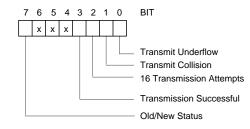

### Transmit Status Register

The Transmit Status Register is loaded at the conclusion of each frame transmission or retransmission attempt. It provides for the reporting of both the normal and error termination conditions of each transmission. The OLD/NEW status bit is set each time the Transmit Status Register is read, and reset each time new status is loaded into the Transmit Status Register. The OLD/NEW status bit is SET, and all other bits CLEARED upon chip reset.

### Transmit Status Register Format

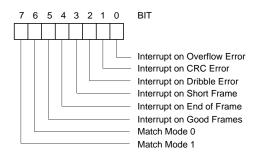

### Receive Command Register

The Receive Command Register has two primary functions, it specifies the Address Match Mode, and it specifies Frames-of Interest. i.e. frames whose arrival must be communicated to the CPU via interrupts and status register updates. Frames-of-Interest are frames whose status must be saved for inspection, even at the expense of losing subsequent frames.

### **Receive Command Register Format**

*Bits 0-5 specify Interrupt and Frame-of-Interest when set. Bit 4, End of Frame, specifies any type of frame except overflow.*

|   | Match<br>Mode<br>1 | Match<br>Mode<br>0 | Function                                       |

|---|--------------------|--------------------|------------------------------------------------|

| 0 | 0                  | 0                  | Receiver Disable                               |

| 1 | 0                  | 1                  | Receive All Frames                             |

| 2 | 1                  | 0                  | Receive Station or Broadcast<br>Frames         |

| 3 | 1                  | 1                  | Receive Station,<br>Broadcast/Multicast Frames |

### Match Mode Definition

Changing the receive Match Mode bits during frame reception may change chip operation and give unpredictable results.

#### Interrupt Enable and Frames-of-Interest

Bits 0-5 when set specify interrupt generation on occurrence of the corresponding frame reception condition. They also specify the corresponding types of frames to be Frames-of-Interest for use by the Receive Status Register to control status loading.

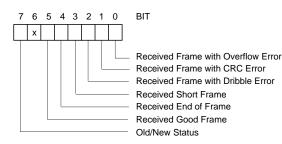

#### **Receive Status Register**

The Receive Status Register is normally loaded with the status of each received frame when the frame has been received or frame reception has been terminated due to an error condition. In addition, this register contains the Old/ New Status bit which is set when the Receive Status Register is read or the chip is reset, and cleared only when status is loaded for a Frame-of-Interest (as defined by bits 0-5 of the Receive Command Register). All other bits are cleared upon chip reset.

### **Receive Status Register Format**

The Old/New Status bit write-protects the Receive Status Register while it contains unread status for a Frame-of-Interest. When this bit is zero, the register is writeprotected. The Old/New Status bit is cleared whenever the status of a new Frame-of-Interest is loaded into the Receive Status Register and is set after that status is read. When zero, it indicates "new status for a Frame-of-Interest".

Thus the status of any frame received following the reception of a Frame-of-Interest will not be loaded into the Receive Status Register unless the previous status has been read. If any following frame is received before the status of the previous Frame-of-Interest has been read, the new status will not be loaded, the Receive Discard (RxDC) signal will be issued and the Receive FIFO will be cleared.

With this one exception caused by a write-protect condition, the status of each frame is always loaded into the Receive Status Register on completion of reception.

Any frame received will cause an interrupt to be generated if the corresponding Interrupt Enable bit is set. This interrupt is reset upon reading the Receive Status Register.

These conditions ensure that a maximum number of good frames are received and retained.

|   | Trans<br>Comr<br>Regi<br>Bit | nand<br>ster |    | egis<br>Idre |    | Register Description                              |                                 |

|---|------------------------------|--------------|----|--------------|----|---------------------------------------------------|---------------------------------|

|   | 6                            | 5            | A2 | A1           | A0 | Read                                              | Write                           |

| 0 | 0                            | 0            | 0  | 0            | 0  | Transmit Collision Counter LSB                    | Station Addr 0                  |

| 1 | 0                            | 0            | 0  | 0            | 1  | Transmit Collision Counter MSB                    | Station Addr 1                  |

| 2 | 0                            | 0            | 0  | 1            | 0  | Total Collision Counter LSB                       | Station Addr 2                  |

| 3 | 0                            | 0            | 0  | 1            | 1  | Total Collision Counter MSB                       | Station Addr 3                  |

| 4 | 0                            | 0            | 1  | 0            | 0  | "For Test Only" Do Not Use                        | Station Addr 4                  |

| 5 | 0                            | 0            | 1  | 0            | 1  | Bit 0 — SQE Flag<br>Bit 1 — txen_no_ carrier flag | Station Addr 5                  |

| 6 | 0                            | 0            | 1  | 1            | 0  | Rx Status                                         | Rx Command                      |

| 7 | 0                            | 0            | 1  | 1            | 1  | Tx Status                                         | Tx Command                      |

| 0 | 0                            | 1            | 0  | 0            | 0  | _                                                 | Multicast Filter LSB Register 0 |

| 1 | 0                            | 1            | 0  | 0            | 1  | —                                                 | Multicast Filter Register 1     |

| 2 | 0                            | 1            | 0  | 1            | 0  | —                                                 | Multicast Filter Register 2     |

| 3 | 0                            | 1            | 0  | 1            | 1  | —                                                 | Multicast Filter Register 3     |

| 4 | 0                            | 1            | 1  | 0            | 0  | —                                                 | Multicast Filter Register 4     |

| 5 | 0                            | 1            | 1  | 0            | 1  | —                                                 | Multicast Filter Register 5     |

| 0 | 1                            | 0            | 0  | 0            | 0  | _                                                 | Multicast Filter Register 6     |

| 1 | 1                            | 0            | 0  | 0            | 1  | —                                                 | Multicast Filter MSB Register 7 |

| 2 | 1                            | 0            | 0  | 1            | 0  | —                                                 | Reserved. Set to All '0'        |

| 3 | 1                            | 0            | 0  | 1            | 1  | —                                                 | Tx Control Register             |

| 4 | 1                            | 0            | 1  | 0            | 0  | —                                                 | TX-RX Config. Register          |

| 5 | 1                            | 0            | 1  | 0            | 1  | —                                                 | Reserved                        |

| 6 | 1                            | 0            | 1  | 1            | 0  | —                                                 | Reserved                        |

| 7 | 1                            | 0            | 1  | 1            | 1  | —                                                 | Reserved                        |

### Internal Register Addressing (80C03 mode)

**Note:** For register reads, the transmit command register bits 5 & 6 are a don't care.

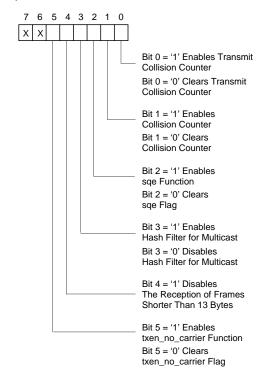

### Transmit Control Register

Available in 80C03 mode only. Allows for control of transmit Collision Counter, total Collision Counter, SQE function, carrier loss on transmit reporting, Multi-cast hash filter reception of runt frames. Set to all '0's after reset.

### Multicast Mode

There is a 64 bit multicast address filter register on 80C03 which can accessed as shown in table (page 9). When the SEEQ 80C03 is programmed to receive multicast frames (match mode 3), after computing the CRC on the address field of the receiving frame (first 6 bytes), it will index to the multicast address filter register depending on bits 0 to 5 of the CRC. If the corresponding bit is a '1' it will receive the frame, otherwise it will discard the frame.

### SQE Status Bit

After transmitting a frame if 80C03 does not receive a collision with in a  $4.0 \,\mu s$  period this bit will be set. Once set this will stay set until cleared. This can read and cleared as explained in the register section.

### **Collision Count Registers**

There are two 16 bit read only collision count registers which are cleared on reset. One counts the collisions on transmission and the other counts all the collisions except the ones in the SQE\_WINDOW. The transmit collision counter is eleven bits wide. Bits 15 to 11 of this register indicates the attempt counter used in SEEQ for collision back off. These can be read and cleared as described in register section.

### TxEN\_no\_carrier

When txen goes from 1 to 0, if there is no carrier this bit is set. Once set this will stay set until cleared. These can be read and cleared as described in register section.

### Test Mode

Bits 7 and 4 of the Transmit command register are used for testing purposes only. For normal operation these bits should be set to '0'.

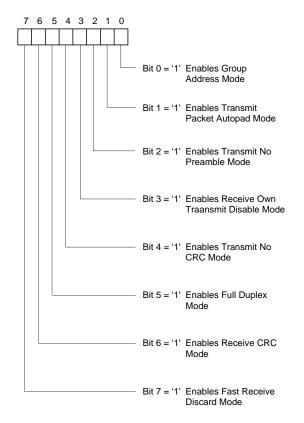

### Tx-Rx Configuration Register

Available in 80C03 mode only. Allows for control of various transmit and receive features. Set to all 0's after reset.

### Group Address Mode

In this mode the last 4 bits of the serial receive data stream for the destination address are masked out in address comparison. This means that when the destination address is compared against the value programmed in the station address register that the packet will not be rejected due to incorrect address even its last 4 bits did not match.

### Transmit Packet Autopad Mode

This feature automatically pads packets to be transmitted with less than 60 bytes of data out to a minimum IEEE 802.3 standard packet length of 60 bytes excluding FCS. Padding is done with bytes of 00 hex.

### Transmit No Preamble Mode

This mode prevents the transmitter from adding a preamble pattern at the beginning of data to be transmitted.

### Receive Own Transmit Disable Mode

This mode prevents the 80C03 from receiving a packet if it is also transmitting a packet.

### Transmit No CRC Mode

This mode prevents the transmitter from appending transmit data with an FCS.

### AutoDUPLEX Mode

In this mode the transmitter will ignore carrier sense and will not defer to it if it is ready to transmit a packet.

### **Receive CRC Mode**

In this mode the receiver loads the 4 bytes of FCS into the receive FIFO along with the data allowing the FCS value to be read out.

### Fast Receive Discard Mode

In this mode the receive discard signal RxDC occurs a maximum of 400 ns after carrier sense goes low.

### **Pin Description**

The EDLC chip has four groups of interface signals:

- Power Supply

Encoder/Decoder

Command/Status

- ....

### **Power Supply**

| $V_{cc}$ |    | .+5V |

|----------|----|------|

| $V_{ss}$ | Gr | ound |

### Encoder/Decoder Interface

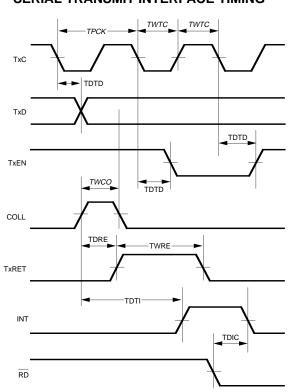

**TxC** Transmit Clock (Input): 10 MHz, 50% duty cycle transmit clock used to synchronize the transmit data from the EDLC chip to the encoder. This clock runs continuously, and is asynchronous to RxC.

**TxD Transmit Data (Output):** Serial Data output to the encoder. Active HIGH.

**TxEN Transmit Enable (Output):** This signal is used to activate the encoder. It becomes active when the first bit of the Preamble is transmitted and inactive when the last bit of the frame is transmitted. Active HIGH and cleared by Reset.

**RxC Receive Data (Input):** 10 MHz, 50% duty cycle nominal. The receive clock is used to synchronize incoming data to the EDLC chip from the decoder. This clock runs continuously, and is asynchronous to TxC.

**RxD Receive Data (Input):** Serial input data to the EDLC chip from the decoder. Active HIGH.

**CSN Carrier Sense (Input):** Indicates traffic on the coaxial cable to the EDLC chip. Becomes active with the first bit of the Preamble received, and inactive one bit time after the last bit of the frame is received. Active HIGH.

**COLL Collision (Input):** Indicates transmission contention of the Ethernet cable. the Collision input is latched internally. Sampled during transmission, Collision is set by an active high pulse on the COLL input and automatically reset at the end of transmission of the JAM sequence.

### Data Buffer Interface

**RxTxD (0-7) Receive/Transmit Data Bus (I/O):** Carries Receive/Transmit data byte from/to the EDLC chip Receive/Transmit FIFOs.

**RxTxEOF Receive/Transmit End of Frame (I/O):** Indicates last byte of data on the Receive/Transmit Data Bus. Effectively a ninth bit in the FIFOs with identical timing to RxTxD (0-7). Active HIGH.

**RxRDY Receive Ready (Output):** Indicates that at least one byte of received data is available in the Receive FIFO. This signal will remain active high as long as one byte of data remains in the Receive FIFO. When this condition no longer exists, RxRDY will be deasserted with respect to the leading edge of the RxRD strobe that removes the last byte of data from the Receive FIFO. RxRD should not be activated if RxRDY is low. Active HIGH and cleared by Reset.

**RxRD Receive Read Strobe (Input):** Enables transfer of received data from the EDLC Receive FIFO to the RxTxD Bus. Data is valid from the EDLC Receive FIFO at the RxTxD pins on the rising edge of this signal. This signal should not be activated unless RxRdy is high. Active LOW.

**RxDC Receive Discard (Output):** Asserted when one of the following conditions occurs, and the associated Interrupt Enable bit in the Receive Command Register is reset. (1) Receive FIFO overflow. (2) CRC Error. (3) Short Frame Error. (4) Receive frame address nonmatch or (5) current frame status lost because previous status was not read.

RxDC does not activate on errors when the associated Interrupt Enable bit is set. In this case, EOF will be generated instead when the Receive FIFO is read out. This allows reception of frames with errors. RxDC acts internally to clear the Receive FIFO.

**TxRDY Transmit Ready (Output):** Indicates that the Transmit FIFO has space available for at least one data byte. This signal will remain active high as long as one byte of space exists for transmitted data to be written into. When this condition no longer exists, TxRDY will be deasserted with respect to the leading edge of the TxWR strobe that fills the Transmit FIFO. TxRDY is forced inactive during Reset, and when TxRET is active. Active HIGH. Goes high after Reset.

**TxWR Transmit Write (Input):** Synchronizes data transfer from the RxTxD Bus to the Transmit FIFO. Data is written to the FIFO on the rising edge of this signal. This signal should not be active unless TxRDY is high. Active LOW.

**TxRet Transmit Retransmit (Output):** Asserted whenever either transmit underflow or transmit collision conditions occur. It is nominally 800 ns in width. Active HIGH. Asserted by Reset. TxRET clears the internal Transmit FIFO.

**ADUPLX\* - Input (PLCC Package Only):** Active low input used to set 80C03 in AutoDUPLEX Mode. In this mode the transmitter will not defer to active carrier sense signal.

### Command/Status Interface

CdSt (0-7) Command/Status Data Bus (I/O): These lines carry commands and status as well as station address

initialization information between the EDLC chip and CPU. These lines are nominally high impedance until activated by  $\overline{CS}$  and  $\overline{RD}$  being simultaneously active.

**A0-A2 Address (0-2) (Input):** Address lines to select the proper EDLC internal registers for reading or writing.

**CS Chip Select (Input):** Chip Select input, must be active in conjunction with RD or WR to successfully access the EDLC internal registers. Active LOW.

**RD Read (Input):** Enables reading of the EDLC internal registers in conjunction with  $\overline{CS}$ . Data from the internal registers is enabled via the falling edge of  $\overline{RD}$  and is valid on the rising edge of the signal. Active LOW.

**WR Write (Input):** Enables writing of the EDLC internal registers in conjunction with  $\overline{CS}$ . Write data on the Cdst (0-7) data lines must be set up relative to the rising edge of the signal. Active LOW.

**INT Interrupt (Output):** Enabled as outlined above by a variety of transmit and receive conditions. Remains active until the status register containing the reason for the interrupt is read. Active HIGH.

**RESET (Input):** Initializes control logic, clears command registers, clears the Transmit Status Register, clears bits 0-5 of the Receive Status Register, sets the Old/New Status bit (bit 7 of the Receive Status Register), asserts RxDC and TxRET and clears the Receive and Transmit FIFOs. In addition, TxRDY is forced low during a reset. TxRDY goes high when RESET goes high, indicating the EDLC chip is ready to transmit. RESET is active LOW.

## Absolute Maximum Ratings

## **Operating Conditions**

| Ambient Temperature Range    | 0°C to 70°C      |

|------------------------------|------------------|

| V <sub>cc</sub> Power Supply | 4.50 V to 5.50 V |

| ADSOIULE MAXIMUM RAIMYS                           |

|---------------------------------------------------|

| Ambient Temperature                               |

| <i>Under Bias</i> −10° <i>C to</i> + 80° <i>C</i> |

| Storage Temperature –65°C to +150°C               |

| All Input or Output Voltages                      |

| with Respect to Ground                            |

| Package Maximum Power Dissipation 1.5 Watts       |

## **DC Characteristics** $T_A = 0^\circ C$ to $70^\circ C$ , $V_{cc} = 5 V$ to 5%

|                  |                          |      | Limits <sup>[1]</sup> |      |       |                                               |

|------------------|--------------------------|------|-----------------------|------|-------|-----------------------------------------------|

| Symbol           | Parameter                | Min. | Тур.                  | Max. | Units | Condition                                     |

| I <sub>IN</sub>  | Input Leakage Current    |      |                       | 10   | μA    | V <sub>IN</sub> = 0.45 V to 5.25 V            |

| I <sub>o</sub>   | Output Leakage Current   |      |                       | 10   | μA    | $V_{OUT} = 0.45 \text{ V to } 5.25 \text{ V}$ |

| I <sub>cc</sub>  | V <sub>cc</sub> Current  |      | 30                    | 40   | mA    |                                               |

| V <sub>CH</sub>  | Clock Input High Voltage | 3.5  |                       | 6    | V     |                                               |

| V <sub>CL</sub>  | Clock Input Low Voltage  |      |                       | 0.8  | V     |                                               |

| V <sub>IL</sub>  | Input Low Voltage        |      |                       | 0.8  | V     |                                               |

| V <sub>IH1</sub> | Input High Voltage       | 2.0  |                       | 6    | V     | Except TxWR and RxRD                          |

| $V_{IH_2}$       | Input High Voltage       | 3.0  |                       | 6    | V     | TxWR and RxRD                                 |

| V <sub>ol</sub>  | Output Low Voltage       |      |                       | 0.4  | V     | I <sub>oL</sub> = 2.1 mA                      |

| V <sub>OH</sub>  | Output High Voltage      | 2.4  |                       |      | V     | I <sub>OH</sub> = -400 μA                     |

### NOTE:

1. Typical values are for  $\rm T_{\rm A}$  = 25°C and nominal supply voltages.

### AC Test Conditions

Output Load: 1 Schottky TTL Gate + CL = 100 pF (All pins except TxEN, TxD) TxEN, TxD Load: 1 Schottky TTL Gate + CL = 35 pF Input Pulse Level:0.4 V to 2.4 V Timing Reference Level:1.5 V

### **Capacitance**<sup>[6]</sup> $T_A = 25^{\circ}C, F_C = 1 \text{ MHz}$

| Symbol          | Parameter         | Maximum | Condition       |

|-----------------|-------------------|---------|-----------------|

| C <sub>IN</sub> | Input Capacitance | 15 pF   | $V_{IN} = 0 V$  |

| C               | I/O Capacitance   | 15 pF   | $V_{I/O} = 0 V$ |

### **AC Characteristics** $T_A = 0^\circ C$ to $70^\circ C$ , $V_{cc} = 5 V \pm 5\%$

|                       |                               |        | Limits | Units  |      |            |

|-----------------------|-------------------------------|--------|--------|--------|------|------------|

| Symbol <sup>[5]</sup> | Parameter                     | Min.   | Тур.   | Max.   | (ns) | Condition  |

| DATA AND              | COMMAND/STATUS INTERFACE TI   | MING   |        |        |      |            |

| TDBD                  | RxTx/CdSt Bus Data Delay      |        |        | 40     | ns   |            |

| TDBR                  | RxTx/CdSt Bus Release Delay   | 10     |        |        | ns   |            |

| TDBS                  | RxTx/CdSt Bus Siezure Delay   | 10     |        | 20     | ns   |            |

| TDRY                  | RxRDY/TxRDY Clear Delay       |        |        | 40     | ns   |            |

| THAR                  | A <sub>0-2</sub> /CS Hold     | 10     |        |        | ns   |            |

| THDA                  | RxTx/CdSt Bus Hold            | 0      |        |        | ns   |            |

| THRW                  | RxRD/TxWR Hold                | 0      |        |        | ns   |            |

| TSAR                  | A <sub>0-2</sub> /CS Setup    | 0      |        |        | ns   |            |

| TSCS                  | CdSt Bus Setup                | 20     |        |        | ns   |            |

| TSRT                  | RxTx Bus Setup                | 20     |        |        | ns   |            |

| TWCH                  | RxRD/TxWR/RD/WR High Width    | 50     |        |        | ns   |            |

| TWCL                  | RxRD/TWR/RD/WR Low Width      | 50     |        | 10,000 | ns   |            |

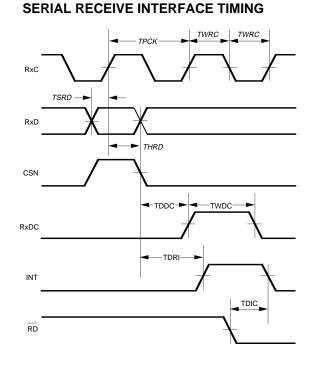

| SERIAL TR             | ANSMIT AND RECEIVE INTEFACE T | IMING  |        |        |      |            |

| TDDC                  | RxDC Set Delay                | 950    |        | 1650   | ns   | NOTE 1     |

| TDIC                  | INT Clear Delay               |        |        | 45     | ns   |            |

| TDRE                  | TxRET Set Delay               | 2400   |        | 3400   | ns   | NOTE 3     |

| TDRI                  | Receive INT Delay             | 1150   |        | 1850   | ns   | NOTE 2     |

| TDTD                  | TxD/TxEN Delay                | 20     |        | 60     | ns   | CI = 35 pF |

| TDTI                  | Transmit INT Delay            | 2600   |        | 3600   | ns   | NOTE 4     |

| THRD                  | RxD Hold                      | 20     |        |        | ns   |            |

| ТРСК                  | RxC/TxC Clock Period          | 95     |        | 1000   | ns   |            |

| TSRD                  | RxD Setup                     | 30     |        |        | ns   |            |

| TWDC                  | RxDC High Width               | 800    |        |        | ns   |            |

| TWRC                  | RxC High/Low Width            | 45     |        |        | ns   |            |

| TWRE                  | TxRET High Width              | 800    |        |        | ns   |            |

| TWRS                  | RESET Low Width               | 10,000 |        |        | ns   |            |

| TWTC                  | TxC High/Low Width            | 45     |        |        | ns   |            |

| TWCO                  | COLL Width                    | 200    |        |        | ns   |            |

NOTES:

For frame reception with Shortframe or CRC Error. If frame reception is terminated due to Overflow, RxDC will be issued within 1.2 μs of Overflow. If frame reception is terminated due to non-match of address, RxDC will be issued within 2.4 μs of the receipt of the last address bit. If Fast Receive Discard Mode is enabled, the maximum delay of RXDC is 400 ns.

2. Normal frame reception without Overflow. If frame reception is terminated due to Overflow, INT will be issued within 1.2µ of Overflow.

For TxRET caused by Collision or 16 Collision condition. If transmission is terminated due to UnderflowTxRET will be issued within 1.2 µs of the Underflow.

For INT caused by Collision or 16 Collision condition. If caused by Underflow, INT will be issued within 1.1 µs. If caused by normal termination, INT will be issued within 200 ns of TxEN going LOW.

5. Italics indicate input requirement, non-italics indicate output timing.

6 Characterized. Not tested.

### SERIAL TRANSMIT INTERFACE TIMING

### **Revision History**

9/9/96

- Pages 18, 19, Dimension diagrams have been added to this data sheet.