# Si55x VCXO TEMPERATURE STABILITY DEFINITION

#### 1. Introduction

The Si55x VCXO utilizes a unique architecture to provide VCXO functionality and performance in an industry standard 5x7 mm CLCC package. This unique architecture provides nearly any clock frequency from 10 MHz to 1.4 GHz and voltage control for closed-loop applications (phase-locked loops).

The basis for frequency synthesis is a single-frequency bulk-acoustic wave (BAW) AT-cut crystal resonator that offers tight frequency stability over temperature and well understood aging behavior. A CMOS IC based on Silicon Labs' proprietary DSPLL™ technology provides the frequency translation from the crystal to the desired output frequency.

Voltage control is achieved via a ground-referenced analog-to-digital converter (VCADC) that dynamically adjusts the frequency synthesis.

# 2. Temperature Effects

Both traditional VCXOs and Si55x VCXOs have specifications that are dependent on temperature. Temperature affects two areas of VCXOs: the crystal's absolute frequency across temperature and the control voltage circuitry's response to temperature.

#### 2.1. Crystal Temperature Behavior

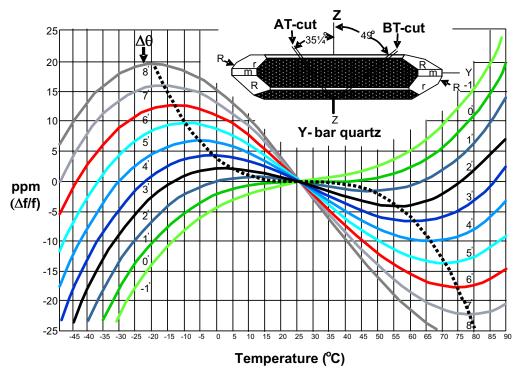

BAW AT-cut crystals have absolute frequency that is dependent on the cut angle and the temperature as shown in Figure 1.

SAW oscillators have a different behavior. The Si55x VCXO data sheet specifies this parameter as "temperature stability" indicating the base oscillator's frequency stability across temperature. The specification is given as a symmetric minimum and maximum.

Figure 1. Relative Frequency Across Temperature for AT-Cut Bulk-Acoustic-Wave Crystal

### 2.2. Control Voltage Temperature Behavior

The control voltage of the Si55x is converted by the VCADC and applied to the internal synthesizer in real-time. The Si55x does not pull the crystal to achieve frequency tuning, so, in this way, differs from traditional VCXOs. The key advantage of this digital approach is to provide customer orderable tuning slopes (Kv). Lower Kv's can be advantageous when designing a PLL, but this topic is beyond the scope of this application note. (See AN255 for additional detail).

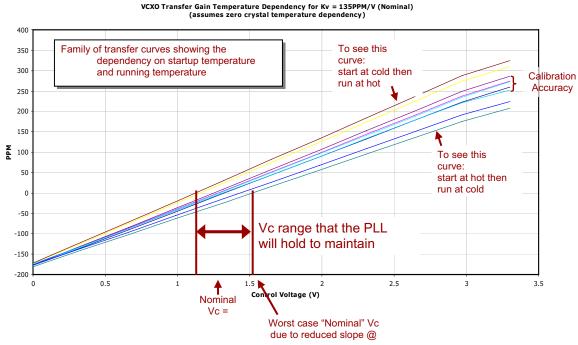

The VCADC relies on an internal voltage reference to define the full-scale voltage (conversion range). The internal voltage reference changes with temperature causing the Kv to vary at a rate of  $\sim 0.1\%/C^{\circ}$  (e.g., 0.045 PPM/V per C° for Kv = 45 PPM/V). The VCADC is ground referenced and therefore provides no frequency adjustment for V<sub>C</sub> = 0.0 V.

The full-scale reference is also reset after each powerup. The reset attempts to calibrate the Kv back to its nominal value. Together, the variation and reset bound the allowed Kv range. The range of Kv is specified in the data sheet as a minimum and maximum percent change from the nominal value.

The resulting frequency for a given  $V_C$  voltage for various start-up and operating temperature conditions is shown in Figure 2.

Figure 2. VCXO Transfer Gain Temperature Dependency

#### 2.3. Measuring the Crystal's Temperature Stability

Because of the secondary effect of Kv variation, measurement of the crystal temperature stability must be made under a specific condition. Because the VCADC is ground referenced, applying 0.0 V to the  $V_C$  input effectively disables the output frequency tuning. Once inactive, the VCADC temperature dependency (and Kv variation) is removed, and the crystal's temperature stability can be observed.

2 Rev. 0.1

## 3. Absolute Pull Range

Correct understanding the temperature dependencies of the Si55x VCXO allow calculation of the absolute pull range (APR). AN266 describes this calculation in full detail when taking the total pull-range from the minimum guaranteed Kv; the minimum APR is calculated by taking the minimum pull-range (minimum  $V_C$  range times the minimum Kv) and subtracting the crystal's temperature stability and aging stability.

## 4. Conclusion

Silicon Labs' Si55x VCXOs have two temperature dependencies that are specified independently within the data sheets. The first dependency is due to the crystal behavior and is specified as temperature stability. The second dependency is due to the  $V_C$  analog-to-digital converter and is specified as Kv range. Measurement of the crystal behavior can only be observed if the VCADC is made inactive (i.e.,  $V_C$  = 0.0 V). The resulting APR can be calculated by taking the minimum Kv and subtracting the crystal's temperature stability and the crystal's aging stability.

## **AN303**

## **CONTACT INFORMATION**

Silicon Laboratories Inc.

4635 Boston Lane Austin, Texas 78735 Tel:1+ (512) 416-8500 Fax:1+ (512) 416-9669 Toll Free:1+ (877) 444-3032

Email: VCXOinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.

4 Rev. 0.1