# NT6881

# **USB Keyboard Micro-Controller**

#### **Features**

- Built-in 6502 8-bit CPU

- 3 MHz CPU operation frequency when oscillator is running at 6 MHz

- 6K bytes of ROM

- 256 bytes of SRAM

- One 8-bit programmable base timer with pre-divider circuit

- 29 programmable bi-directional I/O pins including two external interrupts

- 3 LED direct sink pins with internal serial resistors

- On-chip oscillator (Crystal or Ceramic Resonator)

- Watch-dog timer reset

- Built-in power on reset

- USB interface

- 3 Endpoints provided

- Remote Wakeup provided

- CMOS technology for low power consumption

- 40-pin DIP package, 42-pad Chip Form and COB

#### **General Description**

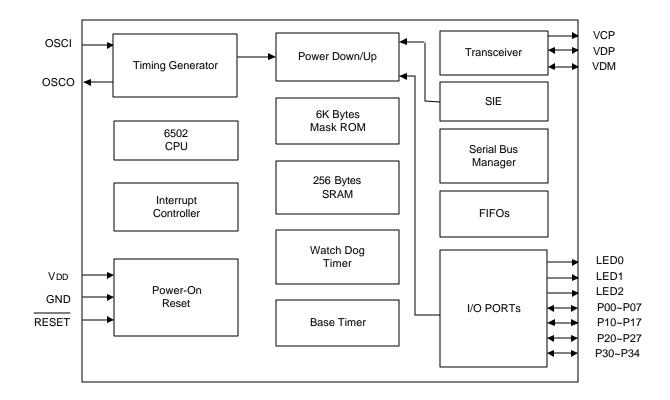

The NT6881 is a single chip micro-controller for USB keyboard applications. It incorporates a 6502 8-bit CPU core, 6K bytes of mask ROM, and 256 bytes of RAM used as working RAM and stack area. It also includes 29 programmable bi-directional I/O pins with built-in resistors, and one 8-bit pre-loadable base timer.

Additionally, it includes a built-in power-on reset, a built-in low voltage reset, an oscillator that requires crystal or ceramic resonator applied, and a watch-dog timer that prevents system standstill.

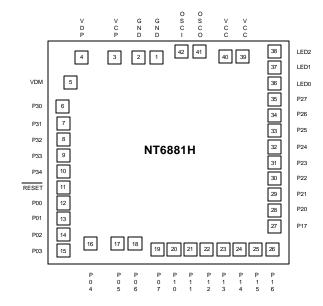

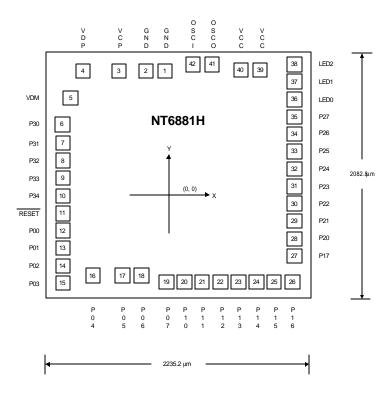

#### **Pin Configuration**

#### **Pad Configuration**

V2.6

## **Block Diagram**

## **Pin and Pad Descriptions**

| Pin No. | Pad No. | Designation | I/O | Description                         |

|---------|---------|-------------|-----|-------------------------------------|

| 1       | 1,2     | GND         | Р   | Ground                              |

| 2       | 3       | VCP         | 0   | USB 3.3V driver                     |

| 3       | 4       | VDP         | I/O | USB data plus                       |

| 4       | 5       | VDM         | I/O | USB data minus                      |

| 5       | 6       | P30         | I/O | Bi-directional I/O                  |

|         |         |             |     | Program output enable               |

| 6       | 7       | P31         | I/O | Bi-directional I/O                  |

|         |         |             |     | Program control                     |

| 7       | 8       | P32/INT0    | I/O | Bi-directional I/O shared with INT0 |

| 8       | 9       | P33/INT1    | I/O | Bi-directional I/O shared with INT1 |

| 9       | 10      | P34         | I/O | Bi-directional I/O                  |

| 10      | 11      | RESET       | ı   | Internally pulled down resistor     |

|         |         |             |     | Program supply voltage              |

| 11 ~ 18 | 12~19   | P00 ~ P07   | I/O | Bi-directional I/O                  |

|         |         |             |     | Program address buffer              |

| 19 ~ 23 | 20~24   | P10 ~ P14   | I/O | Bi-directional I/O                  |

|         |         |             |     | Program address buffer              |

| 24      | 25      | P15         | I/O | Bi-directional I/O                  |

|         |         |             |     | Program chip enable                 |

| 25 ~ 26 | 26~27   | P16 ~ P17   | I/O | Bi-directional I/O                  |

| 27 ~ 34 | 28~35   | P20 ~ P27   | I/O | Bi-directional I/O                  |

|         |         |             |     | Program data buffer                 |

| 35      | 36      | LED0        | 0   | LED direct sink                     |

|         |         |             |     | Mode selection                      |

| 36      | 37      | LED1        | 0   | LED direct sink                     |

|         |         |             |     | Mode selection                      |

| 37      | 38      | LED2        | 0   | LED direct sink                     |

|         |         |             |     | Mode selection                      |

| 38      | 39,40   | VDD         | Р   | Power supply (+5V)                  |

| 39      | 41      | OSCO        | 0   | Crystal oscillator output           |

| 40      | 42      | OSCI        | I   | Crystal oscillator input            |

#### **Functional Description**

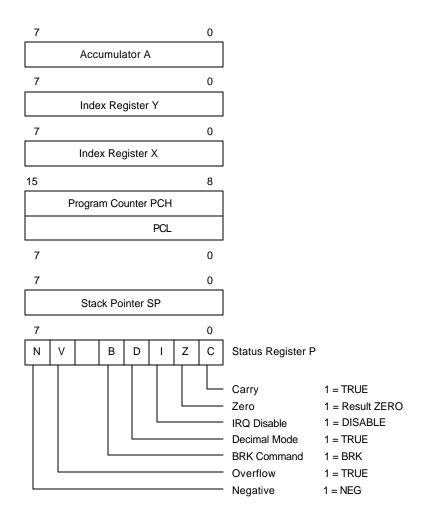

#### 1. 6502 CPU

The 6502 is an 8-bit CPU that provides 56 instructions, decimal and binary arithmetic, thirteen addressing modes, true indexing capability, programmable stack pointer and variable length stack, a wide selection of addressable memory range, and interrupt input. Other features are also included.

The CPU clock cycle is 3MHz (6MHz system clock divided by 2). Please refer to 6502 data sheet for more detailed information.

Figure 1.1. 6502 CPU Registers and Status Flags

## 2.Instruction Set List

| Instruction Code | Meaning                       | Operation                            |

|------------------|-------------------------------|--------------------------------------|

| ADC              | Add with carry                | A + M + C A , C                      |

| AND              | Logical AND                   | A M A                                |

| ASL              | Shift left one bit            | C M7 M0 0                            |

| BCC              | Branch if carry clear         | Branch on C = 0                      |

| BCS              | Branch if carry set           | Branch on C = 1                      |

| BEQ              | Branch if equal to zero       | Branch on Z= 1                       |

| BIT              | Bit test                      | A M, M7 N, M6 V                      |

| ВМІ              | Branch if minus               | Branch on N = 1                      |

| BNE              | Branch if not equal to zero   | Branch on Z= 0                       |

| BPL              | Branch if plus                | Branch on N = 0                      |

| BRK              | Break                         | Forced interrupt PC + 2 PC           |

| BVC              | Branch if overflow clear      | Branch on V = 0                      |

| BVS              | Branch if overflow set        | Branch on V = 1                      |

| CLC              | Clear carry                   | 0 C                                  |

| CLD              | Clear decimal mode            | 0 D                                  |

| CLI              | Clear interrupt disable bit   | 0 I                                  |

| CLV              | Clear overflow                | 0 V                                  |

| СМР              | Compare accumulator to memory | A - M                                |

| CPX              | Compare with index register X | X - M                                |

| CPY              | Compare with index register Y | Y - M                                |

| DEC              | Decrement memory by one       | M - 1 M                              |

| DEX              | Decrement index X by one      | X - 1 X                              |

| DEY              | Decrement index Y by one      | Y - 1 Y                              |

| EOR              | Logical exclusive-OR          | A M A                                |

| INC              | Increment memory by one       | M + 1 M                              |

| INX              | Increment index X by one      | X+1 X                                |

| INY              | Increment index Y by one      | Y+1 Y                                |

| JMP              | Jump to new location          | (PC + 1) PCL , (PC + 2) PCH          |

| JSR              | Jump to subroutine            | PC + 2 , (PC + 1) PCL , (PC + 2) PCH |

# **Instruction Set List (contiuned)**

| Instruction Code | Meaning                           | Operation               |

|------------------|-----------------------------------|-------------------------|

| LDA              | Load accumulator with memory      | M A                     |

| LDX              | Load index register X with memory | M X                     |

| LDY              | Load index register Y with memory | M Y                     |

| LSR              | Shift right one bit               | 0 M7 M0 C               |

| NOP              | No operation                      | No operation (2 cycles) |

| ORA              | Logical OR                        | A + M A                 |

| PHA              | Push accumulator on stack         | A                       |

| PHP              | Push status register on stack     | Р                       |

| PLA              | Pull accumulator from stack       | A                       |

| PLP              | Pull status register from stack   | Р                       |

| ROL              | Rotate left through carry         | C M7 M0 C               |

| ROR              | Rotate right through carry        | C M7 M0 C               |

| RTI              | Return from interrupt             | P , PC                  |

| RTS              | Return from subroutine            | PC , PC+1 PC            |

| SBC              | Subtract with borrow              | A - M - C A, C          |

| SEC              | Set carry                         | 1 C                     |

| SED              | Set decimal mode                  | 1 D                     |

| SEI              | Set interrupt disable status      | 1 I                     |

| STA              | Store accumulator in memory       | A M                     |

| STX              | Store index register X in memory  | х м                     |

| STY              | Store index register Y in memory  | Y M                     |

| TAX              | Transfer accumulator to index X   | A X                     |

| TAY              | Transfer accumulator to index Y   | A Y                     |

| TSX              | Transfer stack pointer to index X | S X                     |

| TXA              | Transfer index X to accumulator   | X A                     |

| TXS              | Transfer index X to stack pointer | X S                     |

| TYA              | Transfer index Y to accumulator   | Y A                     |

<sup>\*</sup> For more detailed specifications, please refer to 6502 programming data book.

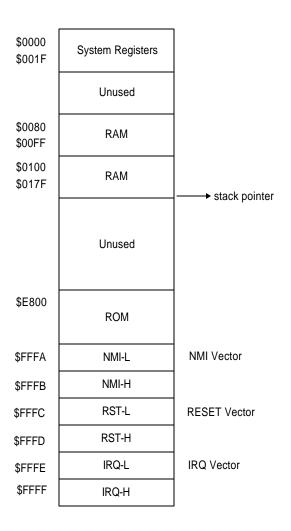

#### 3. Mask ROM: 6K X 8 bits

The built-in mask ROM program code, executed by the 6502 CPU, has a capacity of 6K X 8-bit and is addressed from E800H to FFFFH.

#### 4. SRAM: 256 X 8 bits

The built-in SRAM is used for general purpose data memory and for stack area. SRAM is addressed from 0080H to 017FH. Because the 6502 default stack pointer is 01FFH, the stack area will map \$01FF-\$0180 to \$00FF-\$0080, thus the programmer can set "S" register to 7FH when starting program, allowing stack point is 017FH.

as; LDX #\$7F TXS

## 5. System Reserved Registers

| Address | Register | Reset | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | R/W |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|

| \$0000  | IRQFUNC  | 00H   | -     | -     | -     | -     | KBD   | INT1  | INT0  | TMR   | R   |

| \$0001  | IRQCLRF  | 00H   | -     | -     | -     |       | CKBD  | CINT1 | CINT0 | CTMR  | W   |

| \$0002  | IE_FUNC  | 00H   | -     | -     | -     |       | EKBD  | EINT1 | EINT0 | ETMR  | R/W |

| \$0003  | IRQUSB   | 00H   | SUSP  | STUP  | -     |       | IN2   | IN1   | OT0   | IN0   | R   |

| \$0004  | IRQCLRU  | 00H   | CSUSP | CSTUP | -     |       | CIN2  | CIN1  | COT0  | CIN0  | W   |

| \$0005  | IE_USB   | 00H   | ESUSP | ESTUP | -     |       | EIN2  | EIN1  | EOT0  | EIN0  | R/W |

| \$0006  | ВТ       | 00H   | BT7   | BT6   | BT5   | BT4   | BT3   | BT2   | BT1   | BT0   | W   |

| \$0007  | TCON     | 01H   | -     | -     | -     | 1     | -     | -     | -     | ENBT  | W   |

| \$0008  | TMOD     | 00H   | -     | -     | -     | -     | -     | TM2   | TM1   | TM0   | R/W |

| \$0009  | PORT0    | FFH   | P07   | P06   | P05   | P04   | P03   | P02   | P01   | P00   | R/W |

| \$000A  | PORT1    | FFH   | P17   | P16   | P15   | P14   | P13   | P12   | P11   | P10   | R/W |

| \$000B  | PORT2    | FFH   | P27   | P26   | P25   | P24   | P23   | P22   | P21   | P20   | R/W |

| \$000C  | PORT3    | 1FH   | -     | -     | ı     | P34   | P33   | P32   | P31   | P30   | R/W |

| \$000D  | LED      | 07H   | -     | -     | ı     | -     | -     | LED2  | LED1  | LED0  | W   |

| \$000E  | CLRWDT   | 00H   | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1     | W   |

| \$000F  | MODE_FG  | 02H   | -     | -     | ı     | -     | ı     | ı     | POF   | SUSF  | R/W |

<sup>- :</sup> no effect

#### 6. Power-on Reset

Built-in power-on reset circuit can generate a minimum of 5ms pulse to reset the entire chip. User also can use an external RESET pin to reset the entire chip.

## 7. Timing Generator

This block generates the system timing and control signals supplied to CPU and on-chip peripherals. The crystal oscillator generates a 6MHz system clock. It only generates 3MHz clock for CPU.

#### 8. Base Timer (BT)

The Base Timer is an 8-bit counter with a programmable clock source selection. The BT can be enabled/disabled by the CPU. After reset, the BT is disabled and cleared. The BT can be preset by writing preset value to BT7 ~ BT0 of the BT register at any time. When the BT is enabled, the BT starts counting from the preset value. When the value reaches FFH, it generates a timer interrupt if the timer interrupt is enabled. When it reaches the maximum value of FFH, the BT will wrap around and begin counting at 00H. The BT can be enabled by writing a "0" to "ENBT" bit in the TCON (Timer Control) register. The ENBT signal is level trigger.

The input clock source of BT is controlled by the TMOD register. The following table shows 8 ranges of BT.

| TM2 | TM1 | TMO | Pre-scalar Ratio             | Min. Count | Max. Count |

|-----|-----|-----|------------------------------|------------|------------|

| 0   | 0   | 0   | System Clock/2³ 1.33 µs      |            | 341.33 μs  |

| 0   | 0   | 1   | System Clock/24              | 2.66 µs    | 682.66 μs  |

| 0   | 1   | 0   | System Clock/25              | 5.32 µs    | 1.36 ms    |

| 0   | 1   | 1   | System Clock/2 <sup>6</sup>  | 10.64 µs   | 2.72 ms    |

| 1   | 0   | 0   | System Clock/27              | 21.28 µs   | 5.44 ms    |

| 1   | 0   | 1   | System Clock/2 <sup>8</sup>  | 42.56 µs   | 10.89 ms   |

| 1   | 1   | 0   | System Clock/29              | 85.12 μs   | 21.79 ms   |

| 1   | 1   | 1   | System Clock/2 <sup>10</sup> | 170.24 µs  | 43.58 ms   |

For counting accuracy, please set the TMOD register first, then preset the BT register, and enable base timer finally. (TM2, TM1, TM0) = (1, 1, 1) is reserved for USB driver use.

## 9. Interrupt Controller

There are 10 interrupt sources: Timer, INT0, INT1, KBD, SUSP, IN0, IN1, IN2, OT0 and STUP.

#### 9.1. Timer Interrupt

When the BASE TIMER overflows, it will set the TMR flag. If the interrupt is enabled by writing "1" to the bit 0 in IE\_FUNC (\$0002H), then it will interrupt 6502 CPU. The TMR flag can be read by software. Once set by an interrupt source, it can read from bit0 in IRQFUNC (\$0000H) and remains high unless cleared by writing "1" to the bit 0 in IRQCLRF (\$0001H). All of register's data are cleared to "0" at initialization by the system reset. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, thus the TMR flag must be cleared by software.

#### 9.2. INTO Interrupt

As soon as INT0 pin detects a falling edge trigger, NT6881 sets the INT0 flag (\$0000H, bit1). After that, the 6502 CPU is interrupted if this interrupt has already been enabled already by writing "1" to EINT0 (\$0002H, bit1). If EINT0 flag is cleared, 6502 CPU can't be INT0 interrupted even if the INT0 flag is set. INT0 flag can only be set by hardware and can not be set or cleared directly by the software except for writing "1" to CINT0 (\$0001H, bit1) flag to clear INT0 flag. When an interrupt occurs, the CPU will jump to \$FFFEH & \$FFFFH to execute the interrupt service routine so the INT0 flag must be cleared by software.

#### 9.3. INT1 Interrupt

As soon as INT1 pin detects a falling edge trigger, NT6881 sets the INT1 flag (\$0000H, bit2). Then the 6502 CPU is interrupted if this interrupt has already been enabled already by writing "1" to EINT0 (\$0002H, bit2). If EINT1 flag is cleared, 6502 CPU can't be INT1 interrupted even if the INT1 flag is set. INT1 flag can only be set by hardware and can not be set or cleared directly by the software except for writing "1" to CINT1 (\$0001H, bit2) flag to clear INT1 flag. When an interrupt occurs, the CPU will jump to \$FFFEH & \$FFFFH to execute the interrupt service routine so the INT1 flag must be cleared by software.

#### 9.4. KBD Interrupt

This interrupt will set the KBD flag (\$0000H, bit3) every 4ms(HID 1.00 version) to indicate that keyboard scan data is ready to send for endpoint1. And then 6502 CPU is interrupted if this interrupt has been enabled already by writing "1" to EKBD (\$0002H, bit3). If the EKBD flag is cleared, 6502 CPU can't be KBD interrupted even if KBD flag is set. The KBD flag can only be set by the hardware and can not be set or cleared directly by firmware except for writing "1" to CKBD (\$0001H, bit 3) flag to clear KBD flag. When an interrupt occurs, CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the KBD flag must be cleared by firmware.

#### 9.5. INO Token Interrupt

When an IN TOKEN for endpoint 0 is done, it will set the IN0 flag. If this interrupt is enabled by writing "1" to EIN0 (\$0005H, bit0), it will interrupt 6502 CPU. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the IN0 flag must be cleared by the software.

#### 9.6. OT0 (OUT 0) Token Interrupt

When an OUT TOKEN for endpoint 0 is done, it will set the OT0 flag. If this interrupt is enabled by writing "1" to EOT0 (\$0005H, bit1), it will interrupt 6502 CPU. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the OT0 flag must be cleared by the software.

#### 9.7. IN1 Token Interrupt

When an IN TOKEN for endpoint 1 is done, it will set the IN1 flag. If this interrupt is enabled by writing "1" to EIN1 (\$0005H, bit2), it will interrupt 6502 CPU. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the IN1 flag must be cleared by software.

#### 9.8. IN2 Token Interrupt

When an IN TOKEN for endpoint 2 is done, it will set the IN2 flag. If this interrupt is enabled by writing "1" to EIN2 (\$0005H, bit3), it will interrupt 6502 CPU. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the IN2 flag must be cleared by the software.

#### 9.9. STUP (SETUP) Token Interrupt

When a SETUP TOKEN for endpoint 0 is done, it will set the STUP flag. If this interrupt is enabled by writing "1" to ESTUP (\$0005H, bit6), it will interrupt 6502 CPU. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the STUP flag must be cleared by the software.

#### 9.10. SUSP Interrupt

When USB SIE detects a suspend signal, it sets the SUSP flag. Then 6502 CPU is interrupted if the interrupt has been enabled already by writing "1" to ESUSP (\$0005H, bit7). If ESUSP flag is cleared, 6502 CPU can't be SUSP interrupted even if SUSP flag is set. SUSP flag can be set by H/W only and can't be set/cleared directly by S/W except for writing "1" to CSUSP (\$0004H, bit 7) flag to clear SUSP flag. When an interrupt occurs, the CPU jumps to \$FFFEH & \$FFFFH to execute the interrupt service routine, the SUSP flag must be cleared by software.

#### 10. I/O PORTs

The NT6881 has 32 pins dedicated to input and output. These pins are grouped into 5 ports, as follows:

#### PORT0 (P00~P07)

PORT0 is an 8-bit bi-directional CMOS I/O port that is internally pulled high by PMOS. Each pin of PORT0 can be bit programmed as an input or output port under software control. When programmed as output, data is latch to the port data register and output to the pin. PORT0 pins with "1" written to them are pulled high by the internal PMOS pull-ups, and can be used as inputs in that state then these input signals can be read. The port will output high after reset.

PORT1 (P10~P17): Functions the same as PORT0.

PORT2 (P20~P27): Functions the same as PORT0.

**PORT3 (P30~P34)**: Functions the same as PORT0. Except for P33/P32 is shared with INT1/INT0 pin. It is also a Schmitt Trigger input with an interrupt source of falling edge sensitive.

**LED:** There are three LED direct sink pins which require no external serial resistors.

The address is mapped to \$000DH.

#### 11. Watch-Dog Timer (WDT)

The NT6881 has a watch-dog timer reset function that protects programs against system standstill. The clock of the WDT is derived from the crystal oscillator. The WDT interval is about 0.15 seconds when operation frequency is 6MHz. The timer must be cleared every 0.15 second during normal operation; otherwise, it will overflow and cause system reset. (This cannot be disabled by software) Before watch-dog reset occurred, the software must clear watch-dog register by writing #55H to CLRWDT (\$000EH) register.

For example:

LDA #\$55H STA \$000E

#### 12. Power Control

The power off flag (POF) in the MODE\_FG register indicates whether a reset is a warm start or a cold start reset. POF is set by hardware when an external power VCC arises to its normal operating level, and must be cleared by software in the cold reset initialization procedure. A warm start reset (POF = 0) occurs at a watch-dog reset or resume reset.

| Address | Register | Reset | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | R/W |

|---------|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|

| \$000FH | MODE_FG  | 02H   | -     | -     | -     | -     | -     | -     | POF   | SUSF  | R/W |

#### 13. Universal Serial Bus Interface

Please refer to UNIVERSAL SERIAL BUS specification Version 1.0 Chapter 7, 8, and 9.

#### 14. Suspend and Resume

## Suspend:

When SIE receives suspend signal, NT6881 generates SUSP interrupt request. In the SUSP interrupt service routine, the software must carry out following steps:

- 1) Clear SUSP IRQ flag,

- 2) Store all the port status,

- 3) Force return lines (PORT2) pull-high,

- 4) Force scan lines (PORT0, PORT1 and P30, P31 or P32) pull-low,

- 5) Turn off LED output,

- 6) Clear watch-dog register.

After the above action has been completed, the software must then set SUSLO (\$1EH) to #55H and SUSHI (\$1FH) to #AAH in order to enter the SUSPEND mode. Finally, oscillator stops in order to save power.

#### Resume:

When NT6881 receives a RESUME signal, the chip will resume and the firmware initializes itself. The initialization process includes, checking the status of the POF bit in the MODE\_FG register, whereas if the POF bit equals "1", the firmware will enter into a cold reset procedure and clears the POF bit. If the POF bit equals "0", the firmware will enter into a warm reset procedure. If indeed a warm reset begins, the firmware checks the SUSF bit in MODE\_FG. Regarding the SUSF bit, if it equals "1", the firmware enters into the RESUME procedure and then clears the SUSF bit, however if SUSF equals "0", then the firmware enters into a Watchdog Reset procedure.

When any keyboard key is struck and the Remote\_Wake\_Up bit equals "1", a RESUME signal will be sent to the host, and the above procedure will repeat themselves.

## 15. Reset Source Summary

These are 5 reset sources in NT6881 as shown below.

| No. | Туре   | Function             | Description                    |

|-----|--------|----------------------|--------------------------------|

| 1   | Cold   | External Pin (RESET) | Applied Externally             |

| 2   | Cold   | Power-on Reset       | Reset after Power-on           |

| 3   | Cold   | USB Reset Signaling  | 10 ms Reset Period             |

| 4   | Warm-1 | Resume Reset         | USB Reset Period               |

| 5   | Warm-2 | Watch-dog Reset      | Reset every 0.15S (OSC = 6MHz) |

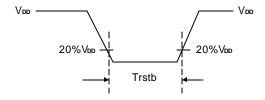

NT6881 can also be reset externally through the RESET pin. A reset is initialed when the signal at the RESET pin is held Low for at least 10 system clocks. When RESET signal goes high, the NT6881 begins to work. The following shows the definition of RESET input low pulse width.

#### 16. PS/2 Mouse Application

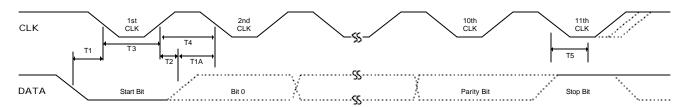

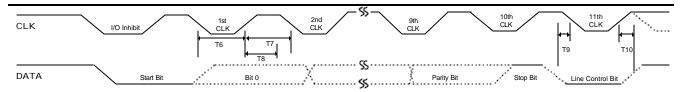

A PS/2 mouse interface is implemented in P32 (CLK), P33 (DATA) and P34 (Power Control). The timing diagrams are described as follows.

Auxiliary Device Sending Data Timings

| Timing | Description                                                                                                        | MIN/MAX           |

|--------|--------------------------------------------------------------------------------------------------------------------|-------------------|

| T1     | Time from DATA transaction to falling edge of CLK 1                                                                | 5/25us            |

| T1A    | Time from DATA transaction to falling edge of CLK 2-11                                                             | 5/25 <i>u</i> s   |

| T2     | Time from rising edge of CLK to DATA transaction                                                                   | 5/T4-5 <i>u</i> s |

| T3     | Duration of CLK inactive (LOW)                                                                                     | 30/50 <i>u</i> s  |

| T4     | Duration of CLK active (HIGH)                                                                                      | 30-50 <i>u</i> s  |

| T5     | Time to Auxiliary Device inhibit after clock 11 to ensure the Auxiliary Device does not start another transmission | >0/50 <i>u</i> s  |

# Auxiliary Device Receiving Data Timings

| Timing | Description                                                                                      | MIN/MAX          |

|--------|--------------------------------------------------------------------------------------------------|------------------|

| T6     | Duration of CLK interface (LOW)                                                                  | 30/50 <i>u</i> s |

| T7     | Duration of CLK active (HIGH)                                                                    | 30/50us          |

| T8     | Time from inactive to active CLK transition, used to time when the Auxiliary Device samples DATA | 5/25 <i>u</i> s  |

| T9     | Time from falling edge of line control bit to falling edge of clock 11 CLK                       | 5 <i>u</i> s/    |

| T10    | Time from rising edge of clock 11 to rising edge of line control bit                             | 5/25 u s         |

#### **Absolute Maximum Rating\***

#

#### \*Comments

Stresses above those listed under "Absolute Maximum Rating" may cause permanent damage to the device. These are stress ratings only. Functional operation of this device at these or any other conditions above those indicated in the operational sections of this specification is not implied and exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC Electrical Characteristics (VDD = 5V, GND = 0V, Ta = 25°C, Fosc = 6MHz, unless otherwise noted)

| Symbol | Parameters                    | Min. | Тур. | Max. | Unit | Conditions   |

|--------|-------------------------------|------|------|------|------|--------------|

| Vdd    | Operating Voltage             | 4.4  | 5    | 5.25 | V    |              |

| ЮР     | Operating Current             |      |      | 20   | mA   | No load      |

| ISP    | Suspend Current               |      |      | 150  | μΑ   | Note 1       |

| Vih    | Input High Voltage            | 2    |      |      | V    |              |

| VIL    | Input Low Voltage             |      |      | 0.8  | V    |              |

| Voн    | Output High Voltage           | 2.4  |      |      | V    | Іон = -100μΑ |

| Vol1   | Output Low Voltage (P0/P1/P2) |      |      | 0.4  | V    | loL1 = 4mA   |

| VOL2   | Output Low Voltage (P3)       |      |      | 0.4  | V    | lol2 = 5mA   |

| lled   | LED Sink Current              | 6    | 10   | 14   | mA   | Vol = 3.2V   |

Note 1: The test condition of Isp is when both of 2 things occur, 1) an oscillation stop and 2) no application circuit is applied. When an application circuit is applied in the keyboard, and the PC is suspended, the suspend current of the keyboard must be less than 500µA.

#### AC Electrical Characteristics (VDD = 5V, GND = 0V, Ta = 25°C, Fosc = 6MHz, unless otherwise noted)

| Symbol            | Parameters                           |      | Тур. | Max. | Unit | Conditions          |

|-------------------|--------------------------------------|------|------|------|------|---------------------|

| Fosc              | Oscillator Frequency                 | 5.97 | 6    | 6.03 | MHz  | OSC within +/- 0.5% |

| T <sub>RSTB</sub> | RESET Input Low Pulse Width          | 1.67 |      |      | μs   | 10 system clocks    |

| T <sub>POR</sub>  | T <sub>POR</sub> Power On Reset Time |      |      | 30   | ms   |                     |

#### **USB DC/AC SPECIFICATIONS**

Please refer to UNIVERSAL SERIAL BUS specification Version 1.0 Chapter 7.

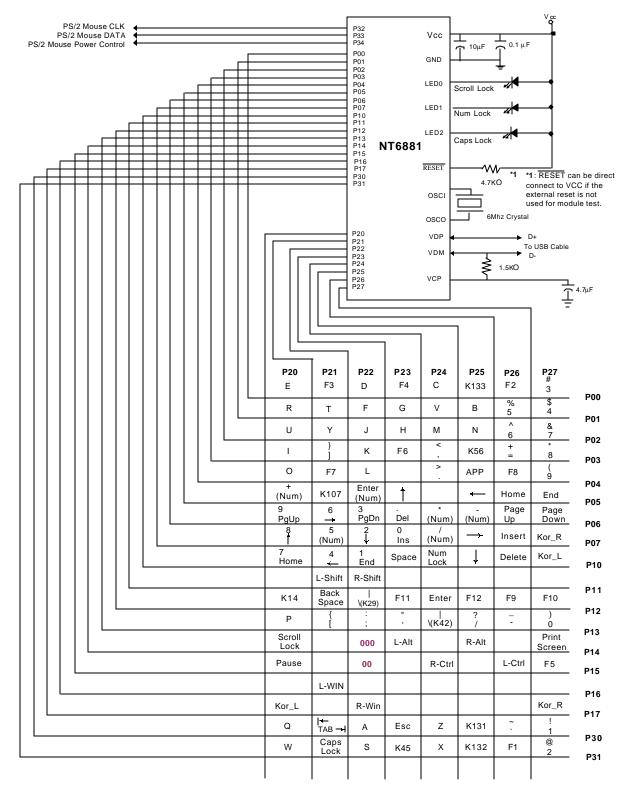

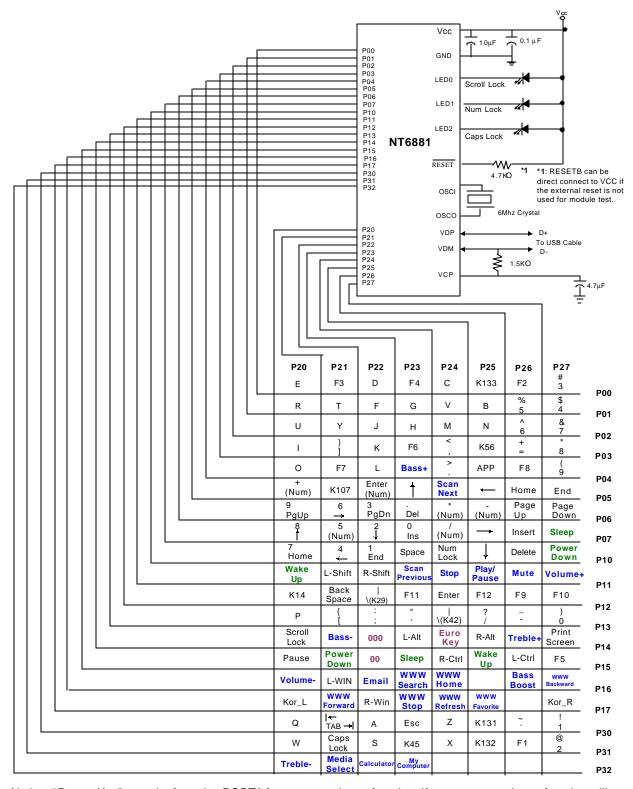

## Application Circuit 1 (Simple Keyboard with PS/2 Mouse)

Notice: "Return Key" must be forced to PORT2 for remote wake up function. If not, remote wake up function will not work.

## **Application Circuit 2 (Windows 2000 Compatible Keyboard)**

Notice: "Return Key" must be forced to PORT2 for remote wake up function. If not, remote wake up function will not work.

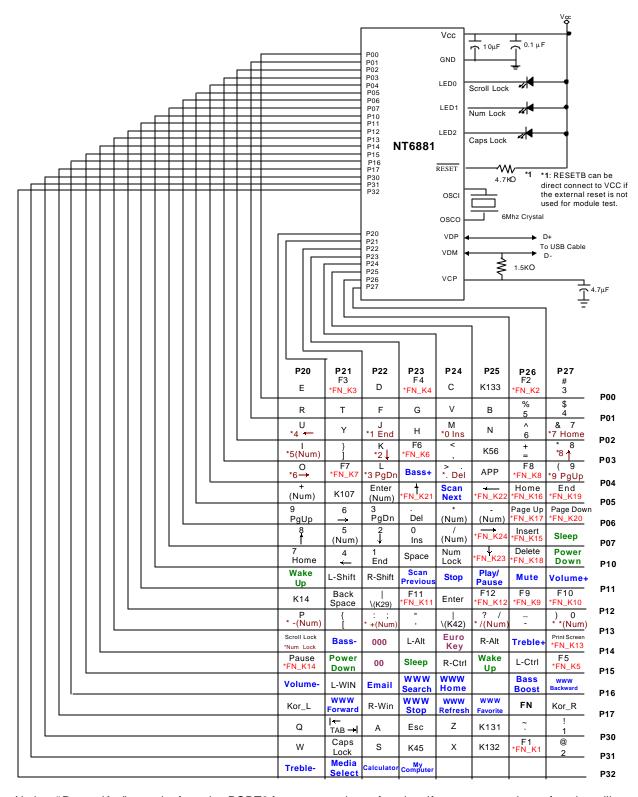

## **Application Circuit 3 (Mini Keyboard)**

Notice: "Return Key" must be forced to PORT2 for remote wake up function. If not, remote wake up function will not work.

<sup>\*:</sup> For FN key model usage

| FN Key Mode       | FN Key Model Usage for Keypad |        |        |          |        |        |        |  |  |  |  |

|-------------------|-------------------------------|--------|--------|----------|--------|--------|--------|--|--|--|--|

| FN+Scroll<br>Lock | Num Lock                      |        |        |          |        |        |        |  |  |  |  |

| FN+& 7            | 7 Home                        | FN+* 8 | 8 ↑    | FN + ( 9 | 9 PgUp | FN+) 0 | *(Num) |  |  |  |  |

| FN+U              | 4 ←                           | FN+I   | 5(Num) | FN+O     | 6 →    | FN+P   | -(Num) |  |  |  |  |

| FN+J              | 1 End                         | FN+K   | 2↓     | FN+L     | 3 PgDn | FN+: ; | +(Num) |  |  |  |  |

| FN+M              | 0 Ins                         |        |        | FN+> .   | . Del  | FN+? / | /(Num) |  |  |  |  |

| FN Key Model Usage for Consumer Keys |                    |              |        |              |                     |

|--------------------------------------|--------------------|--------------|--------|--------------|---------------------|

| FN_K1                                | FN+F1              | WWW Backward | FN_K2  | FN+F2        | WWW Forward         |

| FN_K3                                | FN+F3              | WWW Stop     | FN_K4  | FN+F4        | WWW Refresh         |

| FN_K5                                | FN+F5              | WWW Search   | FN_K6  | FN+F6        | WWW Favorite        |

| FN_K7                                | FN+F7              | WWW Home     | FN_K8  | FN+F8        | Email               |

| FN_K9                                | FN+F9              | My Computer  | FN_K10 | FN+F10       | Calculator          |

| FN_K11                               | FN+F11             | Media Select | FN_K12 | FN+F12       | Mute                |

| FN_K13                               | FN+Print<br>Screen | Bass Boost   | FN_K14 | FN+Pause     | Sleep               |

| FN_K15                               | FN+Insert          | Volume+      | FN_K16 | FN+Home      | Bass+               |

| FN_K17                               | FN+Page Up         | Treble+      | FN_K18 | FN+Delete    | Volume-             |

| FN_K19                               | FN+End             | Bass-        | FN_K20 | FN+Page Down | Treble-             |

| FN_K21                               | FN+↑               | Stop         | FN_K22 | FN+ ←        | Scan Previous Track |

| FN_K23                               | FN+↓               | Play/Pause   | FN_K24 | FN+ →        | Scan Next Track     |

# **Bonding Diagram**

Substrate connect to GND

|         |             |         |         |         |             |        | Unit: μm |

|---------|-------------|---------|---------|---------|-------------|--------|----------|

| Pad No. | Designation | X       | Y       | Pad No. | Designation | X      | Υ        |

| 1       | GND         | -28.90  | 806.90  | 22      | P12         | 442.15 | -901.40  |

| 2       | GND         | -163.90 | 806.95  | 23      | P13         | 572.15 | -901.40  |

| 3       | VCP         | -424.10 | 819.55  | 24      | P14         | 702.15 | -901.40  |

| 4       | VDP         | -841.85 | 828.05  | 25      | P15         | 832.15 | -901.40  |

| 5       | VDM         | -924.35 | 549.95  | 26      | P16         | 962.15 | -901.40  |

| 6       | P30         | -979.05 | 275.10  | 27      | P17         | 980.50 | -561.55  |

| 7       | P31         | -980.35 | 140.70  | 28      | P20         | 980.45 | -426.75  |

| 8       | P32         | -980.40 | 10.65   | 29      | P21         | 980.35 | -292.35  |

| 9       | P33         | -980.40 | -119.30 | 30      | P22         | 980.35 | -162.50  |

| 10      | P34         | -980.50 | -249.30 | 31      | P23         | 980.40 | -32.40   |

| 11      | RESET       | -980.70 | -380.20 | 32      | P24         | 980.15 | 97.60    |

| 12      | P00         | -980.30 | -509.30 | 33      | P25         | 980.45 | 227.65   |

| 13      | P01         | -980.30 | -639.25 | 34      | P26         | 980.40 | 357.55   |

| 14      | P02         | -980.40 | -769.30 | 35      | P27         | 980.35 | 487.75   |

| 15      | P03         | -980.40 | -899.30 | 36      | LED0        | 980.40 | 628.70   |

| 16      | P04         | -601.05 | -859.30 | 37      | LED1        | 980.40 | 754.80   |

| 17      | P05         | -350.25 | -859.30 | 38      | LED2        | 980.40 | 888.75   |

| 18      | P06         | -218.25 | -859.30 | 39      | VCC         | 685.45 | 793.80   |

| 19      | P07         | 52.15   | -901.40 | 40      | VCC         | 512.75 | 793.80   |

| 20      | P10         | 182.15  | -901.40 | 41      | OSCO        | 288.75 | 883.80   |

| 21      | P11         | 312.15  | -901.40 | 42      | OSCI        | 158.75 | 883.80   |

## **Ordering Information**

| Part No. | Packages  |  |

|----------|-----------|--|

| NT6881H  | CHIP FORM |  |

| NT6881   | 40L DIP   |  |

# Standard code functional descriptions

| Code Number   | Name                                | Reference application circuit | Functional Description           |

|---------------|-------------------------------------|-------------------------------|----------------------------------|

| NT6881-D01012 | Simple Keyboard with PS/2 Mouse     | Application circuit 1         | 1. PS/2 mouse port               |

|               |                                     |                               | 2. '000' and '00' keys           |

| NT6881-D01013 | Windows 2000<br>Compatible Keyboard | Application circuit 2         | 1. ACPI keys                     |

|               |                                     |                               | 2. '000', '00' and Euro keys     |

|               |                                     |                               | 3. Consumer keys (Windows 2000)  |

| NT6881-D01014 | Mini Keyboard                       | Application circuit 3         | 1. ACPI keys                     |

|               |                                     |                               | 2. '000', '00' and Euro keys     |

|               |                                     |                               | 3. Consumer keys (Windows 2000)  |

|               |                                     |                               | 4. FN key and 40 Translated keys |

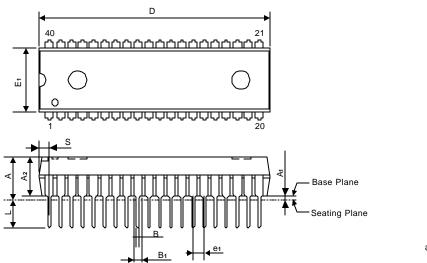

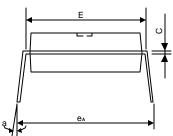

## **Package Information**

## P-DIP 40L Outline Dimensions

| Symbol         | Dimensions in inches    | Dimensions in mm        |  |

|----------------|-------------------------|-------------------------|--|

| Α              | 0.210 Max.              | 5.33 Max.               |  |

| A <sub>1</sub> | 0.010 Min.              | 0.25 Min.               |  |

| A2             | 0.155±0.010             | 3.94±0.25               |  |

| В              | 0.018 +0.004            | 0.46 +0.10              |  |

|                | -0.002                  | -0.05                   |  |

| B <sub>1</sub> | 0.050 +0.004            | 1.27 +0.10              |  |

|                | -0.002                  | -0.05                   |  |

| С              | 0.010 +0.004            | 0.25 +0.10              |  |

|                | -0.002                  | -0.05                   |  |

| D              | 2.055 Typ. (2.075 Max.) | 52.20 Typ. (52.71 Max.) |  |

| Е              | 0.600±0.010             | 15.24±0.25              |  |

| E <sub>1</sub> | 0.550 Typ. (0.562 Max.) | 13.97 Typ. (14.27 Max.) |  |

| <b>e</b> 1     | 0.100±0.010             | 2.54±0.25               |  |

| L              | 0.130±0.010             | 3.30±0.25               |  |

|                | 0°~ 15°                 | 0°~ 15°                 |  |

| еа             | 0.655±0.035             | 16.64±0.89              |  |

| S              | 0.093 Max.              | 2.36 Max.               |  |

#### Note:

- 1. The maximum value of dimension D includes end flash.

- 2. Dimension E<sub>1</sub> does not include resin fins.

- 3. Dimension S includes end flash.

**Product Spec. Change Notice**

| NT6881 Specification Revision History |                                                                                                                                                                                                                                     |           |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|

| Version                               | Content                                                                                                                                                                                                                             | Data      |  |  |

| 2.7                                   | FN Key Model Usage for Consumer Keys modified - FN_K22 and FN_K24 (Page 19)                                                                                                                                                         | Oct. 2002 |  |  |

| 2.6                                   | Volume Knob Application deleted (Page 13) PS/2 Mouse Application added (Page 13 and 14) Application circuit 2 and 3 modified (Page 17 and 18) FN key usage added (Page 19) Standard code functional descriptions modified (Page 21) | Sep. 2002 |  |  |

| 2.5                                   | Application circuits modified (Page 15, 16 and 17) Standard code functional description added (Page19)                                                                                                                              | July 2002 |  |  |

| 1.0                                   | Original                                                                                                                                                                                                                            | Nov. 1998 |  |  |