- 8-Bit Serial-In Parallel-Out Driver

- 1-A Output Current Capability Per Channel or 8-A Total Current

- Overcurrent Limiting and Out-of-Saturation Voltage Protection on Driver Outputs

- Contains Eight Open-Collector Saturating Sink Outputs With Low On-State Voltage

- High-Impedance Inputs With Hysteresis Are Compatible With TTL or CMOS Levels

- Very Low Standby Power 20 mW Typical

- Status of Output Drivers May Be Monitored at Serial Output

- 3-State Serial Output Permits Serial Cascading or Wire-AND Device Connections

- 25-V Transient Clamping With Inductive Switching on Outputs, 40-mJ Rating Per **Driver Output**

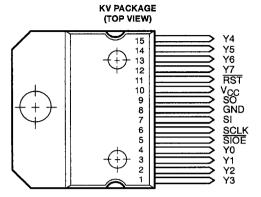

The tab is electrically connected to GND.

### description

The TPIC2801 octal intelligent-power switch is a monolithic BIDFET† integrated circuit designed to sink currents up to 1 A at 30 V simultaneously at each of eight driver outputs under serial input data control. Status of the individual driver outputs is available in serial data format. The driver outputs have overcurrent limiting and out-of-saturation voltage protection features. Applications include driving solenoids, relays, dc motors, lamps, and other medium-current or high-voltage loads.

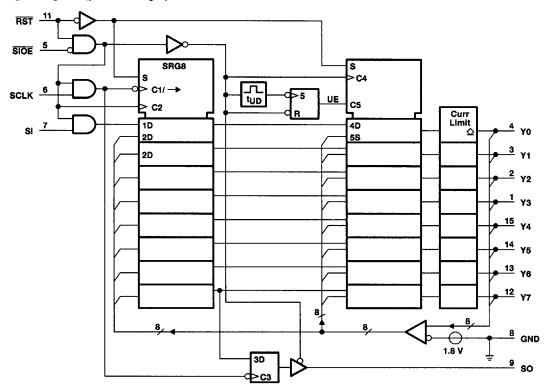

The device contains an 8-bit serial-in, parallel-out shift register that feeds an 8-bit parallel latch, which independently controls each of the eight Y-output drivers.

Data is entered into the device serially via the serial input (SI) and goes directly into the lowest bit (0) of the shift register. Using proper timing signals, the input data is passed to the corresponding output latch and output driver. A logic-high bit at SI turns the corresponding output driver (Yn) off. A logic-low bit at SI turns the corresponding output driver on. Serial data is transferred into SI on the high-to-low transition of serial clock (SCLK) input in 8-bit bytes with data for the Y7 output (most significant bit) first and data for Y0 output (least significant bit) last. Both SI and SCLK are active when serial input-output enable (SIOE) input is low and are disabled when SIOE is high.

Each driver output is monitored by a voltage comparator that compares the Y-output voltage level with an internal out-of-saturation threshold voltage reference level. The logic state of the comparator output is dependent upon whether the Y output is greater or smaller than the reference voltage level. An activated driver output is unlatched and turned off when the output voltage exceeds the out-of-saturation threshold voltage level except when the internal unlatch enable is low and disabled. The high-to-low transition of SIOE transfers the logic state of the comparator output to the shift register.

†BIDFET – Bipolar, double-diffused, N-channel and P-channel MOS transistors on same chip. This is a patented process.

RODUCTION DATA information is current as of publication da roducts conform to specifications per the terms of Texas Instrumer tandard warranty. Production processing does not necessarily inclu

Copyright © 1990, Texas Instruments Incorporated

2-63

8961724 0092136 870

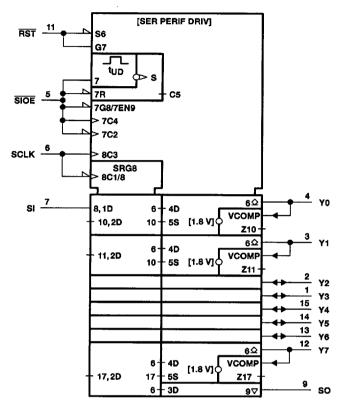

### logic symbol†

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

2-64

■ 8961724 DD92137 7D7 **■**

# logic diagram (positive logic)

2-65

# **TPIC2801 OCTAL INTELLIGENT-POWER SWITCH** WITH SERIAL INPUT SLIS008 - D3282, AUGUST 1989 - REVISED JUNE 1990

### **Terminal Functions**

| PIN                                          |                                    | 1/0 | B-20-15-101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------------------------------------------|------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                         | NO.                                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GND                                          | 8                                  |     | Ground. Common return for entire chip. The current from this terminal is potentially as high as 4 A if all outputs are on. GND is used for both logic and power circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST                                          | 11                                 | Ī   | Reset. An asynchronous reset is provided for the shift register and the parallel latches. This terminal is active when low and has no internal pullup. When active, it causes the power outputs to turn off. A power-on clear can be implemented using an RC network to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                        |

| SCLK                                         | 6                                  | I   | Serial clock. This terminal clocks the shift register. The serial output (SO) changes state on the rising edge of SCLK and serial input (SI) data is accepted on the falling edge.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SI                                           | 7                                  | 1   | Serial input. This terminal is the serial data input. A high on this terminal programs a particular output off, and a low turns it on.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SIOE                                         | 5                                  | I   | Serial input-output enable. Data is transferred from the shift registers to the power outputs on the rising edge of this signal. The falling edge of this signal parallel loads the output voltage sense bits from the power output stages into the shift register. The output driver for SO is enabled when this terminal is low, provided RST is high.                                                                                                                                                                                                                                                  |

| SO                                           | 9                                  | 0   | Serial output. This terminal is the serial 3-state output from the shift register and is in a high-impedance state when $\overline{SIOE}$ is high or $\overline{RST}$ is low. A high for a data bit on this terminal indicates that the corresponding power output $(Y_n)$ is high. This means that the output was programmed to be off the last time a byte was input to the device or that the output faulted and was latched off by the output voltage-sense indicator. A low on this output indicates that the corresponding power output $(Y_n)$ is low (on output stage or open-circuit condition). |

| Vcc                                          | 10                                 |     | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Y0<br>Y1<br>Y2<br>Y3<br>Y4<br>Y5<br>Y6<br>Y7 | 4<br>3<br>2<br>1<br>15<br>14<br>13 | 0   | Power outputs. These outputs are provided with current limiting and voltage sense for fault indication and protection. The nominal load current for these outputs is 500 mA, and the current limiting is set to a minimum of 1.2 A. The active-low outputs also have voltage clamps set at about 35 V for recirculation of inductive load current. Internal $90\text{-}k\Omega$ pulldown resistors are provided at each output. These resistors hold the output low during an open-circuit condition.                                                                                                     |

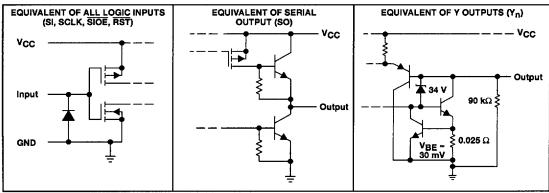

## schematic of inputs and outputs

All resistor and voltage values shown are nominal.

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

2-66

8961724 0092139 58T 🖿

# absolute maximum ratings over operating temperature range (unless otherwise noted)

| Supply voltage range, V <sub>CC</sub> (see Note 1)                             |                    |

|--------------------------------------------------------------------------------|--------------------|

| Output voltage range, V <sub>O</sub>                                           | 0.3 V to 7 V       |

| Peak output sink current at Y, lo repetitive, tw = 10 ms, duty cycle = 50%,    |                    |

| (see Notes 2 and 3)                                                            | internally limited |

| Continuous output current at Y, I <sub>O</sub> (see Note 3)                    | 1A                 |

| Repetitive, t <sub>w</sub> = 10 ms, duty cycle = 50%                           | 6A                 |

| Continuous current through GND                                                 | 4.5 A              |

| Output clamp energy, $E_{OK}$ (after turning off $I_{O}(on) = 0.5 \text{ A}$ ) | 40 mJ              |

| Continuous dissipation at (or below) $T_A = 25^{\circ}$ C (see Note 4)         | 3.575 W            |

| Continuous dissipation at (or below) T <sub>C</sub> = 75°C (see Note 4)        | 25 W               |

| Operating case or virtual junction temperature range                           | 55°C to 150°C      |

| Storage temperature range                                                      | 65°C to 150°C      |

| Lead temperature 1, 6 mm (1/16 inch) from case for 10 seconds                  | 260°C              |

NOTES: 1. All voltage values are with respect to network GND.

- 2. Each Y output is individually current limited with a typical overcurrent limit of about 1.4 A.

- Multiple Y outputs of this device can conduct rated current simultaneously; however, power dissipation (average) over a short time interval must fall within the continuous dissipation range and the GND current must fall within the GND-terminal current range.

- 4. For operation above 25°C free-air temperature, derate linearly at the rate of 28.6 mW/°C. For operation above 75°C case temperature, derate linearly at the rate of 333 mW/°C. To avoid exceeding the maximum virtual junction temperature, these ratings must not be exceeded.

### recommended operating conditions

|                                            | MIN N               | OM M | ΙΑΧ  | UNIT |

|--------------------------------------------|---------------------|------|------|------|

| Supply voltage, V <sub>CC</sub>            | 4.75                | 5 5  | .25  | V    |

| High-level input voltage, VIH              | 0.7 V <sub>CC</sub> | 5    | 5.25 | ٧    |

| Low-level input voltage, V <sub>IL</sub>   | -0.3                | 0.2  | Vcc  | V    |

| Output voltage, VO(off)                    |                     |      | 30   | V    |

| Continuous output current, IO(on)          |                     |      | 1    | Α    |

| Operating case temperature, T <sub>C</sub> | -40                 | 25   | 105  | °C   |

2-67

8961724 0092140 211 🖿

# electrical characteristics over recommended ranges of supply voltage and operating case temperature (unless otherwise noted)

### driver array outputs (Y0 to Y7)

| PARAMETER          |                                     | TEST CONDITIONS                                              |                                                              |      | TYPT | MAX | UNIT |

|--------------------|-------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------|------|------|-----|------|

| Voк                | Output clamp voltage                | IO = 0.5 A, Output programmed off and current shunted to GND |                                                              |      | 36   | 40  | ٧    |

| V <sub>O(on)</sub> |                                     |                                                              | I <sub>OL</sub> = 0.5 A                                      |      | 0.4  | 0.5 | ٧    |

|                    | On-state output voltage             | With output programmed on                                    | I <sub>OL</sub> = 0.75 A                                     |      | 0.6  | 1   | V    |

| <b>(</b> (0)       |                                     |                                                              | IOL = 1 A, During unlatch disable                            |      | 0.8  | 1.5 | V    |

| VTOS               | Out-of-saturation threshold voltage | With output progra                                           | With output programmed on and an overcurrent fault condition |      | 1.8  | 2   | >    |

| IO(off)            | Off-state output current            | V <sub>O</sub> = 24 V with output programmed off             |                                                              |      |      | 1   | mA   |

| lO(cl)             | Output current limit                | VO = 3 V with out                                            | put programmed on                                            | 1.05 | 1.4  |     | Α    |

# shift register (inputs SI, SIOE, SCLK, and RST)

|                  | PARAMETER                        | TEST CONDITIONS                        | MIN                 | MAX                 | UNIT |

|------------------|----------------------------------|----------------------------------------|---------------------|---------------------|------|

| VT+              | Positive-going threshold voltage |                                        |                     | 0.7 V <sub>CC</sub> | ٧    |

| VT-              | Negative-going threshold voltage |                                        | 0.2 V <sub>CC</sub> |                     | >    |

| V <sub>hys</sub> | Hysteresis voltage (VT+ - VT-)   |                                        | 0.85                | 2.25                | >    |

| l <sub>l</sub>   | Input current                    | VI = 0 to VCC                          |                     | ±10                 | μА   |

| Ci               | Input capacitance                | V <sub>I</sub> = 0 to V <sub>C</sub> C |                     | 20                  | pF   |

## shift register (output SO)

|     | PARAMETER                 | TEST COND                                 | ITIONS                 | MIN                  | TYP | MAX | UNIT |

|-----|---------------------------|-------------------------------------------|------------------------|----------------------|-----|-----|------|

| VOL | Low-level output voltage  | I <sub>O</sub> = 1.6 mA                   |                        |                      | 0.2 | 0.4 | ٧    |

| VOH | High-level output voltage | I <sub>O</sub> = - 0.8 mA                 |                        | V <sub>CC</sub> -1.3 |     |     | ٧    |

| 10  | Output current            | VO = 0 to VCC,                            | SIOE input high        |                      |     | ±10 | μА   |

|     |                           |                                           | T <sub>J</sub> = 105°C |                      |     | 150 |      |

|     |                           | All outputs on, IO = 0.5 A at all outputs | T <sub>J</sub> = 25°C  |                      |     | 200 | mA   |

| lcc | Supply current            |                                           | T <sub>J</sub> = -40°C |                      |     | 250 | IIIA |

|     |                           | All outputs off                           | Tj = 25°C              |                      | 4   | 10  |      |

| Со  | Output capacitance        | $V_O = 0$ to $V_{CC}$ ,                   | SIOE input high        |                      |     | 20  | pF   |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>J</sub> = 25°C.

POST OFFICE BOX 655303 ● DALLAS, TEXAS 75265

# TPIC2801 OCTAL INTELLIGENT-POWER SWITCH WITH SERIAL INPUT

SLIS008 - D3282, AUGUST 1989 - REVISED JUNE 1990

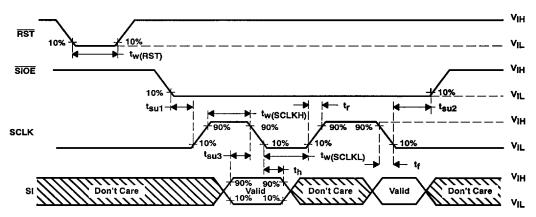

# timing requirements over receommended ranges of supply voltage and operating case temperature (see Figure 1)

|                  |                                  |            | M  | IIN | MAX | UNIT |

|------------------|----------------------------------|------------|----|-----|-----|------|

| fclock           | Clock frequency, SCLK            |            |    | 0   | 500 | kHz  |

| tw(SCLKH)        | Pulse duration, SCLK high        | See Note 5 | 8  | 40  |     | ns   |

| tw(SCLKL)        | Pulse duration, SCLK low         |            | 8  | 40  |     | ns   |

| tw(RST)          | Pulse duration, RST low          |            | 10 | 00  | ï   | กร   |

| t <sub>su1</sub> | Setup time, SIOE↓ before SCLK↑   |            | 10 | 00  |     | ns   |

| t <sub>su2</sub> | Setup time, SCLK↓ before SIOE↑   |            | 10 | 00  |     | ns   |

| t <sub>su3</sub> | Setup time, SI high before SCLK↓ |            | 5  | 00  |     | ns   |

| t <sub>h1</sub>  | Hold time, SI low after SCLK↓    |            | 5  | 00  |     | ns   |

| tr               | Rise time (SCLK, SI, SIOE)       |            |    |     | 2   | μs   |

| tf               | Fall time (SCLK, SI, SIOE)       |            |    |     | 2   | μS   |

NOTE 5: For cascaded operation, the clock pulse durations [tw (SCLKL) and tw (SCLKH)] must be a minimum of 700 ns (giving a maximum clock frequency of 632 kHz).

### thermal characteristics

|                   |                                                     |  |    | UNIT |

|-------------------|-----------------------------------------------------|--|----|------|

| ReJC              | Thermal resistance, junction-to-case temperature    |  | 3  | °C/W |

| R <sub>0</sub> JA | Thermal resistance, junction-to-ambient temperature |  | 35 | °C/W |

# switching characteristics over recommended ranges of supply voltage and operating case temperature

|                     | PARAMETER                                                | FROM<br>(INPUT) | TO<br>(OUTPUT) | TEST CONDITIONS                                                                      | MIN | MAX  | UNIT |

|---------------------|----------------------------------------------------------|-----------------|----------------|--------------------------------------------------------------------------------------|-----|------|------|

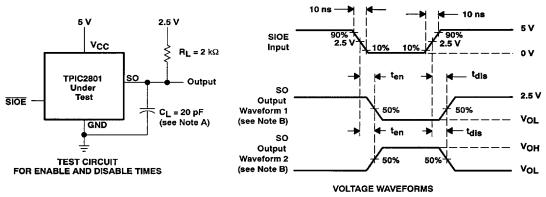

| t <sub>en</sub>     | Enable time                                              | SIOE↓           | SO             | $C_L = 20 \text{ pF},  R_L = 2 \text{ k}\Omega,  \text{See Figure 2}$                |     | 1000 | ns   |

| <sup>t</sup> dis    | Disable time                                             | SIOE↑           | SO             | $C_L = 20 \text{ pF},  R_L = 2 \text{ k}\Omega,  \text{See Figure 2}$                |     | 1000 | ns   |

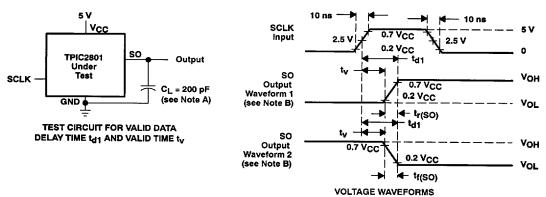

| <sup>t</sup> d1     | Delay time, valid data                                   | SCLK↑           | SO             | C <sub>L</sub> = 200 pF, See Figure 3                                                |     | 740  | ns   |

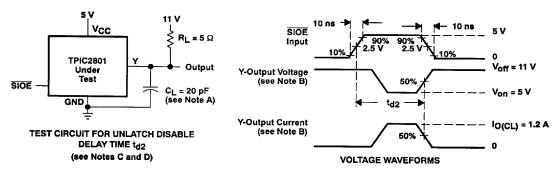

| <sup>t</sup> d2     | Delay time, unlatch disable                              | SIOE↑           | Yn             | $C_L = 20  pF$ , $R_L = 5  \Omega$ , See Figure 4                                    | 75  | 250  | μ\$  |

| tr(SO)              | Rise time, SO                                            |                 |                | C <sub>L</sub> = 200 pF, See Figure 3                                                |     | 150  | กร   |

| tf(SO)              | Fall time, SO                                            |                 |                | C <sub>L</sub> = 200 pF, See Figure 3                                                |     | 150  | ns   |

| <sup>t</sup> d(on)  | Delay time, turn on                                      | SIOE↑           | Yn             | $C_L = 20 \text{ pF}$ , $R_L = 28 \Omega$ , $I_{OL} = 500 \text{ mA}$ , See Figure 5 |     | 10   | μ8   |

| <sup>t</sup> d(off) | Delay time, turn off                                     | <u>SIOE</u> ↑   | Yn             | $C_L$ = 20 pF, $R_L$ = 28 $\Omega$ , $I_{OL}$ = 500 mA, See Figure 5                 |     | 10   | μS   |

| t <sub>V</sub>      | Valid time, SO output data remains valid after SCLK high | SCLK1           | so             | C <sub>L</sub> = 200 pF, See Figure 3                                                | 0   |      | ns   |

2-69

8961724 0092142 074

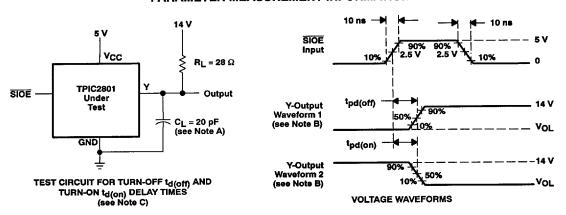

### PARAMETER MEASUREMENT INFORMATION

Figure 1. Input Timing Waveforms

NOTES: A. C<sub>L</sub> includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control when SIOE is high. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control when SIOE is high.

Figure 2. Test Circuit and Voltage Waveforms for Enable and Disable Times

2-70

FOST OF FICE BOX 000000 BALLAG, FEXAS

■ 8961554 0045143 £00 ■

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. CL includes probe and jig capacitance.

B. Waveform 1 is for an output with internal conditions such that the low-to-high transition of SCLK causes the SO output to switch from low to high. Waveform 2 is for an output with internal conditions such that the low-to-high transition of SCLK causes the SO output to switch from high to low.

Figure 3. Test Circuit and Voltage Waveforms for Delay Times

NOTES: A. CL includes probe and jig capacitance.

- B. Output voltage and current waveforms are for an output with internal conditions such that the low-to-high transition of SIOE causes the output to switch from being off to being on.

- C. td2 = delay until Y-output current goes off under fault condition.

- D. Load voltage V<sub>S</sub> and load resistance R<sub>L</sub> are selected such that on-state voltage at the Y output under test, V<sub>on</sub> is greater than the maximum out-of-saturation hold voltage, V<sub>TOS</sub>. Thus V<sub>OL</sub> = V<sub>on</sub> > V<sub>TOS</sub>(max) = 1.98 V.

Figure 4. Test Circuit and Voltage and Current Waveforms for Unlatch Disable Delay

2-71

### PARAMETER MEASUREMENT INFORMATION

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the low-to-high transition of SIOE causes the output to switch from on to off. Waveform 2 is for an output with internal conditions such that the low-to-high transition of SIOE causes the output to switch from off to on.

- C. td(off) = tPLH, td(on) = tPHL.

Figure 5. Test Circuit and Voltage Waveforms for Turn-Off and Turn-On Delay Times

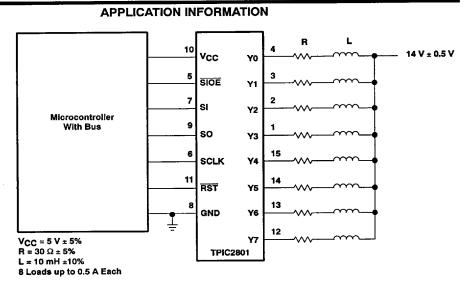

Figure 6. Microcontroller Driving Eight Loads Using a TPIC2801 for Load Interface

2-72

**3961724 0092145 883**

## PRINCIPLES OF OPERATION

# timing data transfer

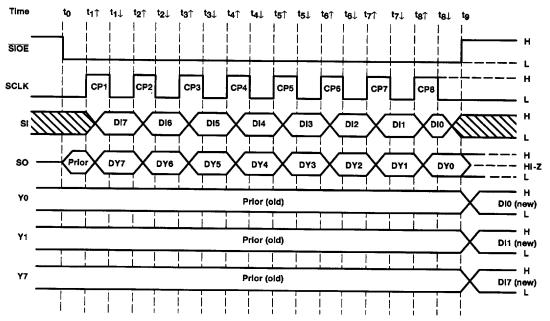

Figure 7 shows the overall 8-bit data-byte transfer to and from the TPIC2801 interface bus. The logic state of the eight output drivers, Y0 through Y7, is latched into the shift register at time  $t_0$  on the high-to-low transition of  $\overline{\text{SIOE}}$ . Therefore, the SO output data (DY0, DY1 . . . ) represent the conditions at the Y-driver outputs at time  $t_0$ . The data at the SO output is updated on the low-to-high transition of SCLK.

Input data present at the SI input is clocked into the shift register on the high-to-low transition of SCLK. As shown in Figure 6 on the SI input, input data DI7 is clocked at time  $t_1$ , DI6 is clocked at time  $t_2$ , etc. Eight SCLK pulses are used to serially load the eight bits of new data into the device. After all the new data is serially loaded, the low-to-high transition of  $\overline{\text{SIOE}}$  parallel loads the new data to the eight driver output latches, which in turn directly control the eight Y-driver outputs.

An unlimited amount of data can be shifted through the shift register (into the SI and out the SO), and this allows other devices to be cascaded in a daisy chain with the TPIC2801. Once the last data bit is shifted into the TPIC2801, the SIOE input is pulled high. The clock (SCLK) input is low at both transitions of the SIOE input to avoid any false clocking of the shift register. The SCLK input is gated by the SIOE input, so the SCLK input is ignored whenever SIOE is high. At the rising edge of SIOE, the shift register data is latched into the parallel latch and the output stages are actuated by the new data. An internal 100-µs delay timer is also started on this rising edge. During the time delay, the outputs are protected only by the analog current-limiting circuits, since the resetting of the parallel latches by fault conditions are inhibited during this time period. This allows the device to overcome any high switching currents that can flow during turn on. Once the delay ends, the output voltages are sensed by the comparators and any output voltages higher than nominally 1.8 V are latched off.

Figure 7. Data-Byte Transfer Timing

2-73

8961724 0092146 717

# TPIC2801 OCTAL INTELLIGENT-POWER SWITCH WITH SERIAL INPUT

SLIS008 - D3282, AUGUST 1989 - REVISED JUNE 1990

### PRINCIPLES OF OPERATION

### fault-conditions check

Open-circuit conditions on any output can be monitored or checked by programming that output off. After a short delay (microseconds), another control byte can be clocked into the device. If the diagnostic bit for that output comes back as a low, it indicates that the output is low and open circuited. A current overload condition can be detected by programming an output on. After waiting an appropriate length of time, another byte is clocked into the TPIC2801. The diagnostic bit clocked back from the TPIC2801 in the subsequent data transfer indicates a low output. If a high returns, a current overload is indicated. A quick overall check is done by clocking in a test control byte. After a sufficient time delay, clock in another control byte (same byte is used). The diagnostic data is exclusive ORed with the original control byte. If a fault condition exists, a high results from the subsequent exclusive OR.

2-74

**8961724 0092147 656**