3684

003684

0KVG -

PRELIMINARY

December 1985

NSC 184-1

# TP3110/TP3112/TP3120/TP3122 Digital Line Interface Controllers (DLIC)

## **General Description**

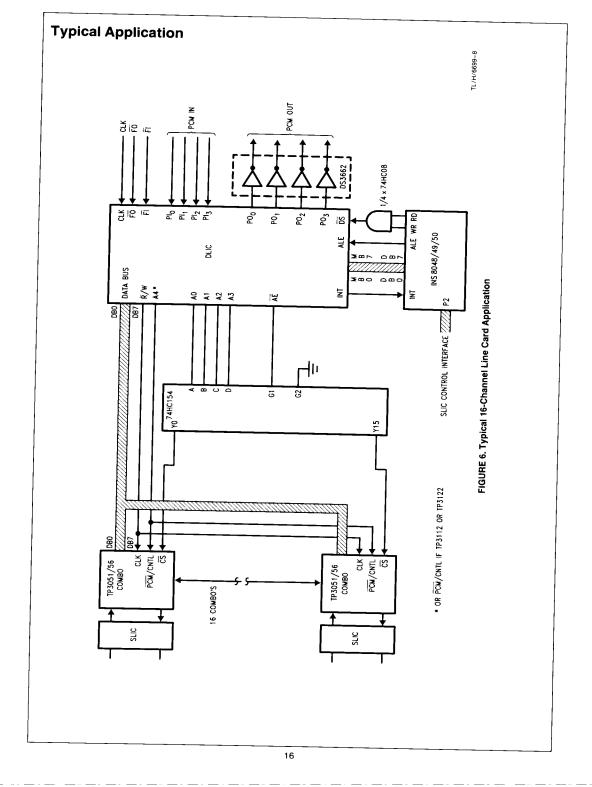

The TP3110, TP3120, TP3112, TP3122 Digital Line Interface Controllers (DLIC) are general purpose switching components primarily intended to serve as controllers of subscriber line, service and trunk circuit cards of a digital switching system. They are also useful as general purpose data controllers for data switching and multiplexing applications.

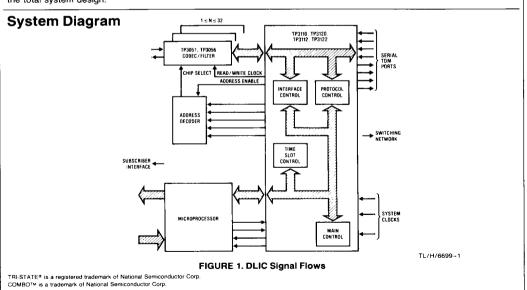

The DLIC performs a three-way control function when used for digital switching applications. The block diagram (Figure 1) displays this tri-port arrangement. First, the DLIC controls the space and time switching function between subscriber line PCM CODECs/filters (COMBOTM) and the switching system time division multiplex (TDM) highways. Second, the DLIC controls the flow of information between the per line circuit devices and the line card's local processor. Last, it performs all protocol control functions, using the HDLC protocol format, for information passing between the local line card processor and the main switching system processor (or any other system processor).

The DLIC is configured with a parallel interface for the per line and local processor circuits and with full duplex multiple port serial highways for the system interface. All system related communications with the DLIC controlled circuit card are handled via channel assignments on the serial TDM interface. In this way, all system data communications, subscriber PCM, data, signaling and system control information are transported and switched with a single network. This approach improves the overall flexibility and modularity of the total system design.

The DLIC contains a time-slot memory map for up to 128 duplex TDM channels, four high speed serial port transceivers, interface logic to allow the local processor to communicate with the per line circuit devices (COMBO circuits and the SLIC), a complete HDLC protocol controller for system control messages, a vectored interrupt controller for the HDLC protocol, signaling and timing control and finally, a buffer memory for per line signaling data.

#### **Features**

- A complete interface controller for up to 32 subscribers of a digital switching system

- Performs all time division multiplex (TDM) channel assignments for the circuit card it controls

- 2 Tx and Rx TDM ports (TP3110, TP3112)

- 4 Tx and Rx TDM ports (TP3120, TP3122)

- Interfaces TP3051/6 parallel CODEC/Filter COMBO

- Only 1 Time Slot delay

- System control uses the HDLC protocol with all zero insertion/deletion, checksum and flag control functions performed by the DLIC

- Assignable addressing plus a "broadcast" address allows up to 255 controllers per subsystem control group without address field overlap

- Master mode allows DLIC to function as the group controller

- Single 5V power supply operation

© 1985 National Semiconductor Corporation

TL/H/669

RRD-B20M125/Printed in U. S. A

## **Absolute Maximum Ratings**

Specifications for Military/Aerospace products are not contained in this datasheet. Refer to the associated reliability electrical test specifications document.

V<sub>DD</sub> Relative to V<sub>SS</sub> 7.0V

Voltage at Any Input or Output  $V_{SS} = 0.3V$  to  $V_{DD} + 0.3V$

Operating Temperature

Range (Ambient) -25°C to +70°C

Storage Temperature Range (Ambient) -65°C to +150°C

Maximum Lead Temp. (Soldering, 10 seconds)

300°C

## **DC Electrical Characteristics**

Unless otherwise noted limits printed in **BOLD** characters are guaranteed for  $V_{DD}=+5V\pm5\%$ ,  $V_{SS}=GNDD$  (digital ground)  $V_{A}=0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $V_{A}=+25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization.

| Parameter                                                                           | Conditions                                                                                    | Min        | Тур | Max            | Units            |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------|-----|----------------|------------------|

| Input Voltage Levels<br>V <sub>IH</sub> , Logic High<br>V <sub>IL</sub> , Logic Iow |                                                                                               | 2.0        |     | 0.7            | <b>&gt; &gt;</b> |

| Output Voltage Levels $V_{OH}$ , Logic High $V_{OL}$ , Logic low                    | $I_{OUT} = 10 \mu A \text{ (Note 1)}$<br>$I_{OUT} = 100 \mu A$<br>$I_{OUT} = -2.0 \text{ mA}$ | 4.0<br>2.4 |     | 0.4            | >>>              |

| TRI-STATE® Leakages<br>μP Bus<br>Data Bus                                           | $V = V_{DD}$ $V = GNDD$ $V = V_{DD}$                                                          | -10<br>-10 |     | 500            | μΑ<br>μΑ<br>μΑ   |

| Input Currents All Non-TRI-STATE Inputs                                             | $V = GNDD$ $0 < V_{IN} < V_{DD}$                                                              | - 10       |     | 500<br>10      | μA<br>μA         |

| Pin Capacitances<br>Inputs<br>Outputs<br>TRI-STATE Busses                           |                                                                                               |            |     | 10<br>15<br>15 | pF<br>pF<br>pF   |

| Power Dissipation                                                                   | Temperature = 25°C V <sub>DD</sub> = 5.0V Master Clock = 2 MHz No Outputs Loaded              |            | 250 | 330            | mW               |

Note 1: Tested at 5.0V ± 0V.

## **AC Electrical Characteristics**

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{DD} = +5V \pm 5\%$ ,  $V_{SS} = GNDD$  (digital ground),  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = +25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization.

| Parameter                                                                                                                                                                                                                                                                                            | Conditions | Min            | Тур | Max                                | Units                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|-----|------------------------------------|----------------------------------|

| Clock Inputs Master Clock Frequency Master Clock High Master Clock Low Frame Clock Frequency Frame Clock Duty Cycle Clock Rise/Fall Times                                                                                                                                                            | (Note 2)   | 185<br>185     | 8   | <b>2.2</b><br>20                   | MHz<br>ns<br>ns<br>kHz           |

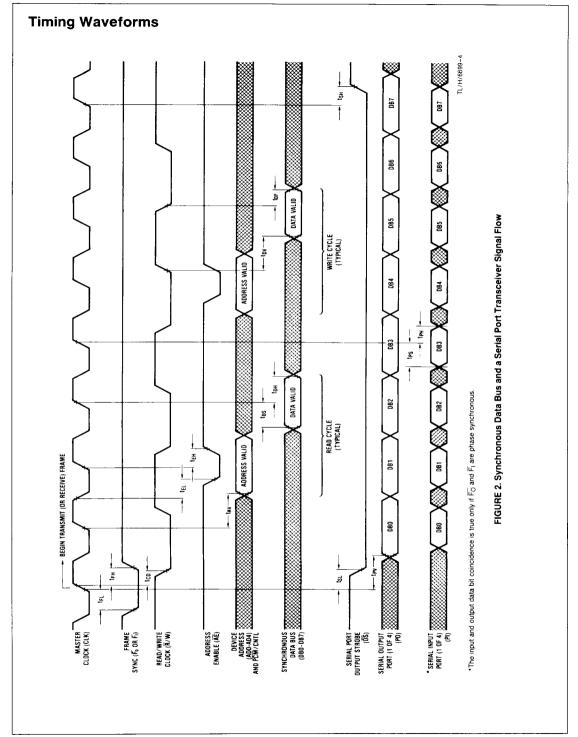

| Data Bus Timing t <sub>CD</sub> , Clock Delay t <sub>EL</sub> , Address Enable Low t <sub>EH</sub> , Address Enable High t <sub>AV</sub> , Address Output Valid t <sub>DV</sub> , Data Output Valid t <sub>DF</sub> , Data Bus Float t <sub>DS</sub> , Data In Set-Up t <sub>DH</sub> , Data In Hold | (Figure 2) | 20<br>50<br>20 |     | 70<br>70<br>70<br>150<br>330<br>80 | ns<br>ns<br>ns<br>ns<br>ns<br>ns |

Note 2: Frame clocks  $\overline{F_0}$  and  $\overline{F_i}$  are low during only one clock cycle of a transmit or receive frame, respectively. Each must go low shortly before the rising edge of the first clock cycle of a frame and return high shortly after the same clock edge, i.e., both edges of the frame clocks must be nominally aligned with falling edges of Master Clock.

## **AC Electrical Characteristics** (Continued)

Unless otherwise noted, limits printed in **BOLD** characters are guaranteed for  $V_{DD} = +5V \pm 5\%$ ,  $V_{SS} = GNDD$  (digital ground),  $T_A = 0^{\circ}C$  to  $+70^{\circ}C$  by correlation with 100% electrical testing at  $T_A = +25^{\circ}C$ . All other limits are assured by correlation with other production tests and/or product design and characterization.

| Symbols          | Parameter                                  | Conditions                                                                                 | Min | Max                                                                | Units                                                             |

|------------------|--------------------------------------------|--------------------------------------------------------------------------------------------|-----|--------------------------------------------------------------------|-------------------------------------------------------------------|

| t <sub>FL</sub>  | Serial Port Timing<br>Frame Clock Low      | (Figure 2)                                                                                 | 150 |                                                                    | ns                                                                |

| t <sub>FH</sub>  | Frame Clock High                           |                                                                                            | 150 |                                                                    | ns                                                                |

| tpV              | Port Output Valid                          |                                                                                            | 80  | 200                                                                | ns                                                                |

| t <sub>PVH</sub> | Port Output Hold                           |                                                                                            | 35  |                                                                    | ns                                                                |

| tps              | Port Input Set-Up                          |                                                                                            | 65  |                                                                    | ns                                                                |

| t <sub>PH</sub>  | Port Input Hold                            |                                                                                            | 30  |                                                                    | ns                                                                |

| t <sub>SL</sub>  | Output Strobe Low                          |                                                                                            |     | 150                                                                | ns                                                                |

| tsH              | Output Strobe High                         |                                                                                            |     | 150                                                                | ns                                                                |

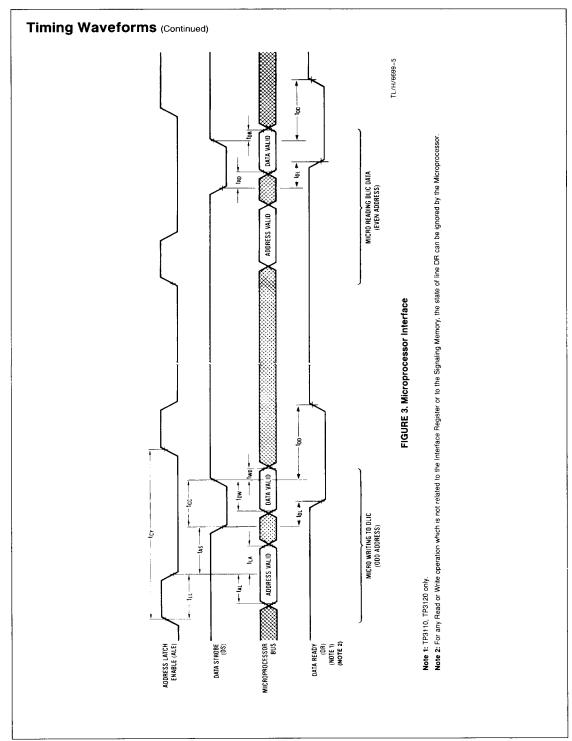

| t <sub>CY</sub>  | Microprocessor Interface Timing Cycle Time | (Figure 3)                                                                                 | 1.0 |                                                                    | μs                                                                |

| t <sub>LL</sub>  | ALE Pulse Width                            |                                                                                            | 125 |                                                                    | ns                                                                |

| tas              | ALE to DS Output                           |                                                                                            | 130 |                                                                    | ns                                                                |

| tcc              | DS Pulse Width                             |                                                                                            | 300 |                                                                    | ns                                                                |

| t <sub>AL</sub>  | Address Set-Up to ALE                      |                                                                                            | 70  |                                                                    | ns                                                                |

| t <sub>LA</sub>  | Address Hold from ALE                      |                                                                                            | 50  |                                                                    | ns                                                                |

| t <sub>DW</sub>  | Data Set-Up to DS                          |                                                                                            | 250 |                                                                    | ns                                                                |

| t <sub>WD</sub>  | Data Hold from DS                          |                                                                                            | 15  |                                                                    | ns                                                                |

| t <sub>RD</sub>  | Data Out Delay                             |                                                                                            |     | 270                                                                | ns                                                                |

| t <sub>DR</sub>  | Data Out Hold                              |                                                                                            |     | 85                                                                 | ns                                                                |

| t <sub>DL</sub>  | Data Ready Low                             |                                                                                            |     | 500                                                                | ns                                                                |

| t <sub>DD</sub>  | Data Ready Delay<br>TP3110, TP3120<br>only | Any register Read/<br>Write operation<br>except Interface<br>Register in one-<br>shot mode |     | 700                                                                | ns                                                                |

| t <sub>DD</sub>  | Data Ready Delay<br>TP3110, TP3120<br>only | Signaling Memory<br>Read/Write<br>operation                                                |     | 700+<br>6 x T <sub>master clock</sub>                              | ns                                                                |

| t <sub>DD</sub>  | Data Ready Delay<br>TP3110, TP3120<br>only | Interface Register<br>one-shot Read/<br>Write operation                                    |     | Depends on the con-<br>tent of the Time-Slot<br>Map (See Table II) | Depends on the con<br>tent of the Time-Slot<br>Map (See Table II) |

Note 3: AC characteristics measured at  $V_{OH} = 2.0V$  and  $V_{OL} = 0.7V$ . Load conditions are:

(a) Data Bus, PCM/CNTL, R/W Output, and Address Outputs

C<sub>LOAD</sub> = 200 pF

(b) Serial Output Ports, Output Strobes and AE Output

$C_{LOAD} = 50 pF$

(c) Microprocessor Bus TRI-STATE lines

$R_{LOAD} = 2 k\Omega \text{ to } V_{DD}$

(d) Interrupt Request and Data Ready Outputs

$C_{LOAD} = 150 pF$

C<sub>LOAD</sub> = 80 pF

a

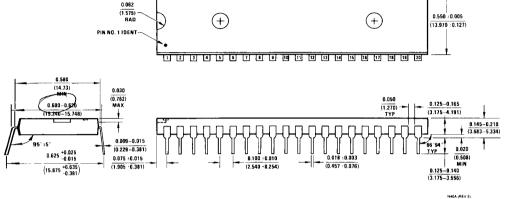

# **Connection Diagrams**

TL/H/6699-3

Note 1: Pin 22 = DR on TP3110, TP3120 Pin 22 =  $\overline{PCM}/CNTL$  on TP3112, TP3122

# **Pin Descriptions**

| 0V0TEM |         |         |

|--------|---------|---------|

| SYSTEM | INTERFA | CE PINS |

| Symbol                            | Description                                                                                                                                                                           | Symbol          | Description                                                                                                                                                                                                 |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK                               | Master Clock Input. This clock determines the serial port data rates and is also used to control the data flow over the line circuit Data Bus.                                        | <u> </u>        | Output Strobes. These active-<br>low outputs indicate when PO <sub>0</sub><br>and PO <sub>1</sub> respectively are trans-<br>mitting valid data. These outputs<br>are not present on the TP3120,<br>TP3122. |

| PO <sub>0</sub> – PO <sub>3</sub> | Serial Port Outputs. These out-<br>puts are the main TDM transmis-<br>sion ports for the DLIC. The sig-<br>nal transmitted over these out-<br>puts must be inverted once be-          | F <sub>o</sub>  | Master Transmit Frame Sync. All Serial Port Output transmissions are synchronized by this signal.                                                                                                           |

|                                   | fore it is applied to a DLIC Serial Port Input $(Pl_0 - Pl_3)$ . $PO_2$ and $PO_3$ are available only on the TP3120 in lieu of $OS_0$ and $OS_1$ .                                    | F <sub>i</sub>  | Master Receive Frame Sync. All<br>Serial Port Input receptions are<br>synchronized by this signal.                                                                                                          |

| Di Di                             | · ·                                                                                                                                                                                   | $V_{DD}$        | 5 V <sub>DC</sub> power input pin.                                                                                                                                                                          |

| Pl <sub>0</sub> – Pl <sub>3</sub> | Serial Port Inputs. These inputs are the main TDM receive ports for the DLIC. Pl <sub>2</sub> and Pl <sub>3</sub> are available only on the TP3120 and TP3122 in lieu of DB8 and DB9. | V <sub>SS</sub> | Digital Ground Power Input Pin (GNDD). All DLIC signal levels are referenced to the voltage level at this pin.                                                                                              |

# Pin Descriptions (Continued)

| SUBSCRIBER CIRC | CUIT INTERFACE PINS                                                                                                                                                                                                                             |                                                                                | MICROPROCES | SSOR INTERFACE PINS                                                                                                                                                                                                                                                                  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Description                                                                                                                                                                                                                                     | 1                                                                              | Symbol      | Description                                                                                                                                                                                                                                                                          |

| DB0-DB7         | 7 Bidirectional eight-bit subscriber circuit interface bus. This bus normally handles the per line PCM COMBO data flowing to or from a TP3051/TP3056 parallel I/O COMBO circuit.                                                                |                                                                                | мво-мв7     | A bidirectional interface bused by a local processor to control all DLIC operations. Address, control and information data flow between DLIC and it associated microprocessor with pass over this bus. MB7 is the                                                                    |

| Data Type       | DB0                                                                                                                                                                                                                                             | DB7                                                                            |             | MSB.                                                                                                                                                                                                                                                                                 |

| PCM             | Sign Bit                                                                                                                                                                                                                                        | LSB                                                                            | ALE         | Address Latch Enable input pir<br>It is used by the DLIC to deter                                                                                                                                                                                                                    |

| Control Data    | C0                                                                                                                                                                                                                                              | C7                                                                             |             | mine when address data is                                                                                                                                                                                                                                                            |

| DB8-DB9         | Additional Data Bus I/                                                                                                                                                                                                                          |                                                                                |             | crossing the MB0-MB7 Micro<br>processor Bus.                                                                                                                                                                                                                                         |

|                 | the 80 kHz channel op<br>DLIC. These two fun<br>not available on the<br>(see PO <sub>2</sub> , PO <sub>3</sub> , PI <sub>2</sub><br>DB9 becomes the I                                                                                           | ctions are<br>e TP3120<br>and Pl <sub>3</sub> ).<br>ast bit of                 | DS          | Data Strobe input pin. A low true input signal pin to indicate when data is crossing the MB0-MB Microprocessor Bus.                                                                                                                                                                  |

| AD0-AD4         | each time slot on e port.  Subscriber circuit adoput pins. These pins a                                                                                                                                                                         | dress out-                                                                     | ĪNTR        | Interrupt control output pin. / low true output that indicate when a DLIC generated interrup is active.                                                                                                                                                                              |

|                 | select one of 32 different sub-<br>scriber or special service circuits<br>associated with the DLIC. AD4 is<br>the MSB.  An active low output that indi-<br>cates a stable and valid sub-<br>scriber circuit address on pins<br>AD0 through AD4. |                                                                                | DR          | Data Ready output pin. This signal goes low on the falling edge of DS when data is written to cread from the DLIC. It goes bac                                                                                                                                                       |

| ĀĒ              |                                                                                                                                                                                                                                                 |                                                                                |             | high again (a) when the write op<br>eration has been executed in<br>side the DLIC or (b) when th<br>previously addressed data i<br>available at the output of th                                                                                                                     |

| R/W             | Data Bus read/write sput and COMBO mar. The R/W output for one-half of the main of frequency. A read op the DLIC Data Bus (rexternal device) occ this clock is low and                                                                          | ster clock. equency is clock input eration on reading an curs while the corre- |             | DLIC.  The primary use of this signal if for Signaling Memory or Interface Register Read operations since for these operations thaddressed data may not be immediately available.                                                                                                    |

|                 | sponding write operat<br>while it is high.                                                                                                                                                                                                      | ion occurs                                                                     | PCM/CNTL    | PCM/control output pin. This signal is normally low and goe high during an interface instruction in NOP mode. Thus the PCM/CNTL inputs of up to 3 TP3051 or TP3056 COMBO devices can be driven by this output, leaving all address output AD0-AD4 available for decodin 32 CS lines. |

## **Functional Description**

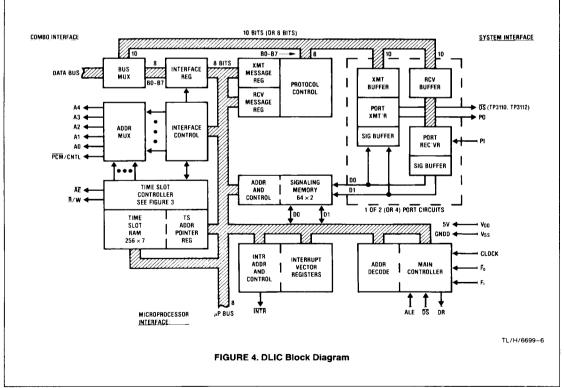

Referring to Figure 4, the primary purpose of the DLIC is to control the flow of data between three I/O interfaces. These interfaces are the System Interface, COMBO (or other subscriber circuit) Interface and the Microprocessor Interface. Data that moves between the COMBO Interface and the System Interface is converted from an eight or ten-bit parallel format to a synchronous serial format. In addition, up to four bidirectional serial transmission interfaces are included in this first data movement group. Data that moves between the Microprocessor Interface and the System Interface is processed by Transmit and Receive High-level Data Link Control (HDLC) protocol controllers. This data is always in an eight-bit format with two "don't care" stuffing bits if necessary for ten-bit compatibility. The third and final type of data movement is between the COMBO Interface and the Microprocessor Interface ports. This movement allows interaction between the synchronous data flow of the COMBO to System Interface bus and the asynchronous flow of the Microprocessor Interface bus. A description of these data movements and their relation to the circuit blocks of Figure 4 is the main purpose of this Functional Description.

The DLIC is available in four configurations. The TP3110 and TP3112 are arranged with a ten-bit wide COMBO interface and only two System Interface port circuits. These two port circuits include separate serial input and output highways and individual output strobes  $(\overline{OS}_0$  and  $\overline{OS}_1)$  to indicate when the PO $_0$  and PO $_1$  signals are valid. The TP3120 and TP3122 DLIC eliminate two bits of the ten-bit COMBO Interface and the output strobes to provide a four-port

System Interface. In this case, the serial output ports must be used with open-collector or open drain line drivers because the output strobes are not available for TRI-STATE output control. Otherwise, all aspects of these parts are identical.

| Summarizing,                                                                                             |                   |                   |

|----------------------------------------------------------------------------------------------------------|-------------------|-------------------|

| Feature                                                                                                  | TP3110,<br>TP3112 | TP3120,<br>TP3122 |

| ■ 10-bit COMBO                                                                                           | yes               | no                |

| Interface bus                                                                                            |                   |                   |

| <ul> <li>Output strobes for<br/>PO<sub>0</sub> and PO<sub>1</sub></li> </ul>                             | yes               | no                |

| <ul> <li>I/O ports Pl<sub>2</sub>, Pl<sub>3</sub></li> <li>and PO<sub>2</sub>, PO<sub>3</sub></li> </ul> | no                | yes               |

The DLIC is composed of seven major circuit blocks as listed below. The interaction between these circuit functions and the three interface ports will be described separately.

The DLIC circuit blocks are:

- 1. Time Slot Map

- 2. Serial Port Transceivers

- 3. HDLC Protocol Logic

- 4. Interface Register and Controller

- 5. Vectored Interrupt Control Logic

- 6. Signaling Memory

- 7. Main Controller

#### TIME SLOT MAP

The Time Slot Map and its associated circuitry control all of the synchronous data movements in the DLIC. The Map is organized as 256 seven-bit registers, each register directly corresponding to one clock cycle of the master input clock when in the eight-bit per channel format. For channels programmed to operate at ten bits per channel (as will be described later), the first eight clock cycles of each channel correspond to eight Map instructions and the last two cycles are skipped by the Time Slot Map. Each Map register can hold an instruction which will cause one of four basic operations. See Table VII for a listing of the Time Slot Map instruction set.

The data entered into the Map is arranged as a two-bit instruction code and a five-bit external device address code (i.e., COMBO, or SLIC select address). An eighth bit, not actually stored in the Map, is derived from an internal read/write clock that alternates data bus operations from read to write. This internal clock is exactly one-half the main clock frequency and it forces adjacent instructions from the Map to be read and write instructions.

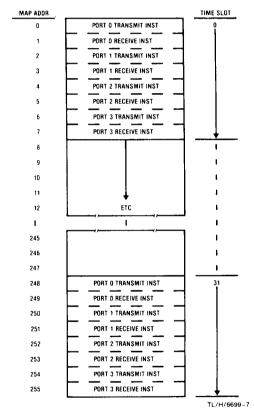

Map addressing determines the actual time or space division switching function to be performed by the DLIC. As shown in *Figure 5*, the Map addresses are arranged so the LSB determines serial transmission direction. The next two bits are decoded as the system interface port transceiver address and the top five address bits select one of 32 time slots in the frame. By loading a Time Slot Map register, the position of the instruction within the Map will determine the channel, port and direction of the data flow over the System Interface, while the contents of the Map register will determine the source or destination of the data.

Time Slot Map instructions are executed sequentially and in complete synchronism with the master clock. The Map control logic, however, does allow the instruction sequence for transmit and receive operations to be skewed in time. Clock inputs  $\overline{F_0}$  and  $\overline{F_1}$  provide the DLIC Map with the timing relationship between the transmit and receive frames, respectively. This arrangement requires bit synchronization between the System Interface serial transmit and receive ports, but does not require frame or channel (time slot) synchronization.

To accommodate frames of less than 256 clock cycles, a maximum clock count register is loaded with a binary number for the maximum number of clock cycles per frame. This number is always a multiple of eight minus one (i.e., 7, 15, 31...255).

An associated microprocessor accesses the Time Slot Map through the DLIC Microprocessor Interface port. The access is a two step process to allow the synchronization of data that must be written to or read from the Map. First, the microprocessor must write a Map address into the Address Pointer Register (address 01 hex), see Table I. Next, the microprocessor can execute a Map read (address 40 hex) or write (address 41 hex) command to move data to or from the Map. A read command must be executed a minimum of 125 µs after an address load to allow the desired Map data to be "down-loaded" into the access holding register. A

write command can be executed immediately after an address load, but further Map read or write operations must be suspended for at least 125  $\mu s$  or one frame period. This pause allows the written data to be loaded into the proper Map location during the next complete Map scan. To facilitate a Map reset operation, the Address Pointer Register will automatically increment to the next address count at the end of each Map write command cycle (again, address 41 hex). This feature allows the microprocessor to write 256 NOP instructions into the Map, one instruction load per frame period, using only a single microprocessor write operation per cycle.

#### **SERIAL PORT TRANSCEIVERS**

Two or four serial port transceivers are provided for the DLIC System Interface. Under control of the Time Slot Map, data is either parallel loaded for serial transmission or parallel read after serial reception. The exact timing for all operations is dependent upon the instructions in the Map and the beginning of each TDM channel relative to the start of the

FIGURE 5. Time Slot Map Organization

frame. While all serial exchanges begin and end in alignment with the TDM channels, parallel exchanges are only synchronized to master clock cycles. Incidentally, for normal DLIC operation a channel is eight clock cycles long and the first channel begins with the positive master clock edge while the appropriate frame clock is low.

The idle state for any Serial Output Port is logic low. This signal must be externally inverted to logic high before it can be applied to a Serial Input Port on any DLIC. The inverted signal corresponds to the idle channel code of a PCM COMBO and the idle or abort sequence of the HDLC protocol. The normal hardware arrangement would use an inverting bus driver between the DLIC Serial Output Ports and the system backplane highways, and no inverter between the backplane and the DLIC Serial Input Ports.

In the ten-bit operating mode, the beginning of channel one is still the rising clock edge while the appropriate frame clock is low. The length of each channel, however, is ten bits or clock cycles and for a full 32-channel frame, 320 clock cycles are required. The transceivers will serially shift the extra two bits per channel after the normal eight-bit sequence is complete.

Transmission order for the serial System Interface is always LSB first, for data and sign bit first for PCM. This is compatible with the normal protocol of PCM transmission. The ordering of the data from the parallel interface of the TP3051 or TP3056 PCM COMBOs is thus reversed from the normal arrangement, and is shown below:

| Serial Transmission Order    | Data Bus Orde |

|------------------------------|---------------|

| First bit in or out          | DB0           |

| Second bit                   | DB1           |

| Third bit                    | DB2           |

| Fourth bit                   | DB3           |

| Fifth bit                    | DB4           |

| Sixth bit                    | DB5           |

| Seventh bit                  | DB6           |

| Eighth bit                   | DB7           |

| Ninth bit (10-bit mode only) | DB8           |

| Tenth bit (10-bit mode only) | DB9           |

Whenever the ninth and tenth serial bits are delivered to or from the signaling memory circuit block (a programmable option), the ninth bit internally passes through the DLIC as bit D0 while the tenth bit passes as D1 (*Figure 4*). Over the Microprocessor Interface bus, these bits correspond to MB0 and MB1 respectively.

### PROTOCOL LOGIC

System control messages are transmitted between the main processor and the DLIC local processor by way of System Interface TDM channels. This data passes through the DLIC under direct control of the Time Slot Map. Because the integrity of this control information is very important to the total system operation, the DLIC includes High-level Data Link Control (HDLC) protocol circuits to process these control messages. These are independent Transmit and Receive HDLC circuits that allow simultaneous both-way control messages if required.

The HDLC format used in the DLIC follows the CCITT X.25, Section 2.1 and 2.2 recommendation. This recommendation calls for an opening flag sequence of 011111110 followed by the device address, control, data, checksum and closing flag fields. The closing flag of one message can be used as the opening flag to the next message. To avoid the unintentional simulation of a flag sequence, the DLIC will insert a zero after any string of five ones except where a flag or abort code is desired. Again, this is in conformance with the CCITT recommendation.

Before starting a transmit message the microprocessor must first load the DLIC Address Register with the unique address for that subscriber line card; write the Time Slot(s) for the message channel in the Time Slot Map; and enable the necessary interrupts (see Table V). Then the first data byte must be loaded in the Transmit Message Register. The message channel is activated by setting Control Register bit 5 high (see Table III). An opening flag is transmitted in the selected channel, then the DLIC address and then the first data byte, with zeroes inserted according to the HDLC protocol. Each time the Transmit Message Register is emptied. the DLIC automatically generates a "register empty" interrupt to force the microprocessor into loading the next data byte of the message. If the microprocessor responds to this interrupt by turning the HDLC transmit logic off, the DLIC will close out the current message with the CRC checksum and a closing flag. Failure to service this interrupt before the next message Time Slot arrives will result in the abort sequence of all 1's being transmitted.

For receive messages the microprocessor must first load the associated DLIC registers as described for the transmit section. The DLIC monitors the message channel until an opening flag is detected, then compares the address field with the contents of the DLIC Address Register. If there is a match, or if the address field contains the broadcast address, Hex FF, the message is accepted. (Inserted zeroes are automatically deleted.) As each message data byte is received it is stored in the Receive Message register and an interrupt generated to summon the microprocessor. When the register is read, the interrupt signal is reset to await the next data byte. If the interrupt is not serviced before the next data byte arrives, or if an abort sequence is received, the receive CRC checksum will be corrupted to indicate that the message is not valid. The receive protocol logic automatically computes the CRC checksum on the incoming message and compares it with the CRC field (which is not known until the closing flag is detected) to determine the final interrupt for this message, i.e., Checksum Correct or Checksum Incorrect.

It should be noted that the DLIC can receive only a single control message at a time (i.e., the receive message channel must be one channel of one serial highway). It can, however, transmit a control message over one, two, three or four ports simultaneously, although the same channel must be used for each of the ports. This is a useful feature that simplifies overall system design.

#### MASTER MODE

This mode allows the DLIC to be used as the master controller for a group of line cards connected to a common backplane. It forces the receive protocol logic to ignore the contents of the address field on an incoming message so that it will accept a message from any source. Internally the address comparison is inhibited and the address byte is

forwarded to the microprocessor in the same manner as a data byte.

The transmit HDLC logic operation is not changed in this mode. Before transmitting a new message the microprocessor must load the DLIC Address Register with the destination address. Alternatively, a message can be "broadcasted" to all DLIC's in a control group by setting the address field to hex FF. Master Mode is selected by setting Control Register bit 4 high.

#### INTERFACE REGISTER AND CONTROLLER

This circuit block provides a direct data access path between the DLIC associated microprocessor and any of the circuit devices connected to the COMBO Interface bus. This allows the two internal data busses, which are operating in asynchronism with each other, to communicate control and signaling information through the DLIC. This need for additional access ports on the per channel circuits is eliminated with this communications scheme.

The Interface Register operates in one of two control modes and handles the flow of data in only one direction at a time. Data written into the register from the Microprocessor Interface bus can be moved onto the COMBO Interface bus during either the next available Time Slot Map NOP (direct mode) or when a particular Map instruction is executed (frame mode). In a similar fashion, data can be moved in from the COMBO Interface bus to be written onto the Microprocessor Interface bus in either the direct or frame mode fashion. Control of the Interface Register is handled by matching instructions in the Time Slot Map and Interface Register Controller. See Table II for additional details.

Control data is written to DLIC address 03 hex. The microprocessor can read the Interface Register with hex address 42 and it can write to the Register with hex address 43. Reading the Register from either the Microprocessor or COMBO Interface busses does not alter its contents. Any operation which takes place during a Time Slot Map NOP will occur only once. The Register Controller will reset to a NOP control condition after the "one-shot" execution. The data READY output (TP3120 and TP3110) indicates the pending nature of this control cycle by remaining low from the time the instruction is loaded until execution is complete. On the TP3122 and TP3112 only, the PCM/CNTL output goes high when a "one-shot" control instruction is being executed. Operations which occur as the result of a match between a Time Slot Map instruction and the control byte loaded into the Interface Register Controller will occur every frame and must be halted by direct command from the microprocessor. This latter operating mode is interrupt driven and is useful in generating PCM test signals with the local microprocessor.

#### INTERRUPT LOGIC

The DLIC contains an on-board Vectored Interrupt Controller. This Controller will process the seven built-in interrupts of the DLIC. In addition, these interrupts are prioritized so that important operations are never missed. See Table V for more information.

The DLIC microprocessor can directly read or write the seven DLIC interrupt registers. This allows a specific program address to be loaded into the DLIC interrupt control logic so that the occurrence of the interrupt can cause a program

vector to be read from the DLIC by the microprocessor. The DLIC read address for a pending interrupt is 00 hex. The information read with the 00 address is then directly used by the microprocessor to compute an address jump to the appropriate software routine to service this interrupt. The address 00 read operation will automatically reset and clear the interrupt request and its output signal on the INTR line. Interrupts that require simultaneous service are handled in the priority order given in Table V. Additional features of this logic section include a single DLIC Command Register control bit to activate and deactivate the interrupt logic output signal and a control register within the interrupt logic block for selective masking of individual interrupts. It should be noted that turning all interrupts off with the single control bit does not disable the generation of the interrupts inside the DLIC. When the control bit reactivates the interrupt output line, any interrupts that have occurred during the idle state will immediately request service in the proper priority order. However, masking an interrupt off by storing a zero in the proper place within the interrupt control register (address 3F hex) will totally disable the interrupt. Internal circuitry will not recognize the activity that normally causes the interrupt request and the interrupt, when enabled, starts from a reset condition.

#### SIGNALING MEMORY

This memory block operates as either a buffer store for the two bits of the ten-bit 80 kHz channel or as a general purpose RAM. DLIC control bit D3 of Table III will determine the operating state. In either state, the Signaling Memory is arranged as 64 two-bit cells that interface the microprocessor bus through the two least significant bits MB0 and MB1. Internal to the DLIC, these two bits are called D0 and D1.

When the Signaling Memory is used for general storage, the DLIC control bit D3 is set to zero. Each two-bit cell of the memory is accessed with one of 64 read or write addresses as shown in Table VIII. The interface between the Signaling Memory function and the System Interface transceivers is totally disabled while in this operating state.

While using the Signaling Memory RAM for general storage, the extra two bits of the ten-bit serial channel System Interface format can only be accessed through the DB8 and DB9 lines of the COMBO Interface bus. This means that only the TP3110 and TP3112 can simultaneously operate with ten-bit serial channels and the Signaling Memory in the general storage operating state.

When DLIC control bit D3 is high, the Signaling Memory RAM is switched to an operational state known as Extended Channel Signaling (ECS). In this operating mode, the data for bits 9 and 10 of a ten-bit serial channel are buffered by the Signaling Memory. This data is not accessible through the COMBO Interface bus pins DB8 and DB9 when ECS is enabled. The extra two bits of data are accessible only through the 32 transmit and 32 receive cells in the Signaling Memory RAM. Each of the cells corresponds to an address of the COMBO Interface bus. This allows any device connected to this bus to utilize the Signaling Memory RAM, loaded and unloaded through the DLIC microprocessor, for end-to-end system data communications at speeds of up to 16 kHz

#### MAIN CONTROLLER

While most of the DLIC features and functions are controlled by the various circuit blocks already described, some master control functions still remain to be explained. These include the setting of overall frame timing and length, power on reset conditions, and the initialization of Time Slot Map, Signaling Memory and HDLC protocol control power-up states. Also available through the DLIC main control are status flags for the HDLC protocol logic and the interface register.

Because of the pipelined architecture of the DLIC, the Time Slot Map is actually operated in a "look ahead" fashion. This structure requires a maximum TDM frame length register on the DLIC. It is microprocessor loaded during initial-

ization and it provides the DLIC with address counter "wrap" information during less than full length TDM frames. The DLIC maximum count is determined on a eight-bit per channel basis. If the DLIC is set for ten-bit operation, the maximum count is still related to eight bits per channel. This is because the Time Slot Map will skip two clock cycles out of every ten during this latter operating mode. The maximum count register is set to the number of channels in a frame (on one of the highways) times eight. As an example, a 24-channel system would require a maximum count frame length of 192 (24 x 8) and the DLIC maximum count register would be set to hex BF which corresponds to the decimal 192 clock cycles per frame.

TABLE I. Microprocessor Interface

| Hex<br>Address | Description of Interface Data Flow                                                                                                                        |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0            | Microprocessor READ of current interrupt vector after detecting a logic low condition on DLIC output INTR.                                                |

| 0 1            | Microprocessor WRITE cycle to the address pointer register of the Time Slot Map controller.                                                               |

| 0 2            | Not used.                                                                                                                                                 |

| 0 3            | Microprocessor WRITE cycle to the control logic of the Interface Register. See Table II.                                                                  |

| 0 4            | Not used.                                                                                                                                                 |

| 0 5            | The WRITE cycle used by the microprocessor to load the DLIC Address Register.                                                                             |

| 0 6            | Not used.                                                                                                                                                 |

| 0 7            | The WRITE cycle used by the microprocessor to set the maximum number of clock cycle                                                                       |

|                | per frame.                                                                                                                                                |

| 0 8            | Microprocessor READ of current DLIC status conditions.                                                                                                    |

| 0 9            | Microprocessor WRITE cycle to set the DLIC Control Register. For addresses 08 and 09, see Table III.                                                      |

| 0 A            |                                                                                                                                                           |

| $\downarrow$   | Not used.                                                                                                                                                 |

| 1 F            |                                                                                                                                                           |

| 2 0<br>1       | READ and WRITE operations to the Interrupt Vector Registers of the DLIC. See Table V.                                                                     |

| 3 F            |                                                                                                                                                           |

| 4 0            | A microprocessor READ cycle of Time Slot Map data. The Map address must be preset                                                                         |

| 4 0            | using hex address 01.                                                                                                                                     |

| 4 1            | The complementary WRITE operation for hex address 40. See Table VII.                                                                                      |

| 4 2            | The microprocessor READ cycle of the Interface Register. Control conditions must be                                                                       |

| 4 2            | preset with hex address 03.                                                                                                                               |

| 4 3            |                                                                                                                                                           |

| 4 3            | The complementary WRITE operation for hex address 42. Control conditions are normally set after this WRITE cycle.                                         |

| 4 4            |                                                                                                                                                           |

| 1              | Not used.                                                                                                                                                 |

| 4 F            |                                                                                                                                                           |

| 5 0            | A microprocessor READ operation to retrieve data from the Receive Message Register after the appropriate interrupt has been received.                     |

| 5 1            | A microprocessor WRITE operation to the Transmit Message Register. Again, the appropriate interrupt will normally initiate this microprocessor operation. |

| 5 2            | p/op/and money                                                                                                                                            |

| 1              | Not used.                                                                                                                                                 |

| 7 F            |                                                                                                                                                           |

| 8 0            | Microprocessor access to the DLIC Signaling Memory. Even addresses correspond to                                                                          |

| 1              | READ cycles for the 64 two-bit memory cells while odd addresses correspond to comple-                                                                     |

| F F            | mentary WRITE cycles. See Table VIII.                                                                                                                     |

#### POWER-UP INITIALIZATION

During power-up initialization, the DLIC will automatically clear its control register. This action will disable the Time Slot Map and System Interface output ports, set the INTR output high, deactivate the HDLC transmit protocol logic and place the DLIC in the eight-bit per channel operating mode. No other reset functions will occur. As described ear-

lier, the DLIC associated microprocessor is responsible for clearing the Time Slot Map, setting the interrupt vectors, loading the DLIC Address Register, and in general, establishing all of the DLIC control and operating states. Through the Control Register, the microprocessor can quickly activate and deactivate the major functions of the DLIC with a single write operation to hex address 09.

**TABLE II. Interface Register Control**

|    |    |    | Data | a Byte                            |              |    |    | Description of Interface Register Control Operation                                                                                                                                                                                               |

|----|----|----|------|-----------------------------------|--------------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 | D6 | D5 | D4   | D3                                | D2           | D1 | D0 | Description of interface negister control Operation                                                                                                                                                                                               |

| 0  | 0  |    |      |                                   |              |    | 0  | A control instruction to move data from an external device into the DLIC Interface Register during the next Time Slot Map NOP while the R/W line is low. This cycle will automatically reset to a no operate state after execution.               |

| 0  | 0  | į  |      | Address                           |              |    | 1  | The complementary operation to the above with the data movement from the preloaded Interface Register into an external device. Again, this is a one-shot operation.                                                                               |

| 0  | 1  |    |      | devices connected to the data bus | _            |    | 0  | A control instruction to move data from an external device into the DLIC Interface Register whenever this control byte matches a Time Slot Map instruction byte. This instruction remains in effect until manually cleared by the microprocessor. |

| 0  | 1  |    |      |                                   |              |    | 1  | The complementary operation to the above with the data movement from the Interface Register into an external device any time this control byte matches a Time Slot Map instruction byte.                                                          |

| 1  | 0  |    |      | D 14                              | _            |    | 0  | Reserved.                                                                                                                                                                                                                                         |

| 1  | 0  |    | _    | Don't care                        | <del>.</del> |    | 1  | Reserved.                                                                                                                                                                                                                                         |

| 1  | 1  |    |      | Don't care                        | е            |    | 0  | No operation.                                                                                                                                                                                                                                     |

| 1  | 1  |    |      | $\downarrow$                      |              |    | 1  | No operation.                                                                                                                                                                                                                                     |

#### **TABLE III. DLIC Status and Control Data**

| Data<br>Bit | DLIC Status Register<br>READ Cycle; Address 08 | DLIC Control Register WRITE Cycle;<br>Address 09           |

|-------------|------------------------------------------------|------------------------------------------------------------|

| D0          | Transmit Message Register empty.               | Enable Time Slot Map controller.                           |

| D1          | Receive Message Register full.                 | Enable INTR (interrupt) request output.                    |

| D2          | An Interface Register command is in effect.    | Enable the 10-bit/channel operating mode.                  |

| D3          | HDLC opening receive flag detected.            | Enable Signaling Memory for Extended<br>Channel Signaling. |

| D4          | CRC error detected on incoming message.        | Enable Master Mode.                                        |

| D5          | HDLC receive logic in idle state.              | Enable HDLC Transmit Message Logic.                        |

| D6          | HDLC transmit logic in the active state.       | Not used.                                                  |

| D7          | HDLC transmit channel in the idle state.       | Should always be zero.                                     |

**TABLE IV. DLIC Control States**

| Function | Cor<br>D7 | trol Regi<br>D3 | ster<br>D2 | TP3110, 3112<br>Option | TP3120, 3122<br>Option | Description                                                                         |

|----------|-----------|-----------------|------------|------------------------|------------------------|-------------------------------------------------------------------------------------|

| Normal   | 0         | 0               | 0          | yes                    | yes                    | Up to 32 eight-bit channels per frame on each serial highway. No other options.     |

| Ten-Bit  | 0         | 0               | 1          | yes                    | no                     | 32 ten-bit channels/frame with bits 9 and 10 accessed through 10-bit data bus.      |

| ECS      | 0         | 1               | 1          | yes                    | yes                    | 32 ten-bit channels/frame with bits 9 and 10 accessed through the Signaling Memory. |

**TABLE V. Interrupt Vector Registers**

|                           |   | TABLE TIMESTOP TOOLOT HEGISTERS                                                                                                        |  |  |

|---------------------------|---|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Hex Priorty Address Level |   | Description of Register READ and WRITE Operations                                                                                      |  |  |

| 2 0<br>2 1                | 5 | Direct READ of vector register for Interface Register instruction executed interrupt. WRITE operation for the same interrupt register. |  |  |

| 2 2<br>2 3                | 4 | Direct READ of vector register for Transmit Message Register empty interrupt. WRITE operation for the same interrupt register.         |  |  |

| 2 4<br>2 5                | 1 | Direct READ of vector register for Receive Message Register full interrupt. WRITE operation for the same interrupt register.           |  |  |

| 2 6<br>2 7                | 2 | Direct READ of vector register for Receive Message Checksum Correct interrup WRITE operation for the same interrupt register.          |  |  |

| 2 8<br>2 9                | 3 | Direct READ of vector register for Receive Message Checksum Incorrect interrupt. WRITE operation for the same interrupt register.      |  |  |

| 2 A<br>2 B                | 6 | Direct READ of vector register for End of Transmit Frame interrupt. WRITE operation for the same interrupt register.                   |  |  |

| 2 C<br>2 D                | 7 | Direct READ of vector register for End of Receive Frame interrupt. WRITE operation for the same interrupt register.                    |  |  |

| 2 E<br>↓<br>3 D           | × | Not used.                                                                                                                              |  |  |

| 3 E<br>3 F                | × | READ operation for Interrupt Masking Register. WRITE operation for Interrupt Masking Register. (See Table VI for details).             |  |  |

Note: Interrupt priority levels are associated with the service order if simultaneous interrupts request attention via the microprocessor 00 hex address READ cycle. All interrupts automatically reset only after the appropriate vector is read through this same 00 hex address.

**TABLE VI. Interrupt Masking**

| Data<br>Bit | Description of Masking Control with Interrupt Mask Register       |  |  |  |  |

|-------------|-------------------------------------------------------------------|--|--|--|--|

| D0          | If high, Receive Message Register full interrupt is on.           |  |  |  |  |

| D1          | If high, Receive Message Checksum Correct interrupt is on.        |  |  |  |  |

| D2          | If high, Receive Message Checksum Incorrect interrupt is on.      |  |  |  |  |

| D3          | If high, Transmit Message Register empty interrupt is on.         |  |  |  |  |

| D4          | If high, Interface Register instruction executed interrupt is on. |  |  |  |  |

| D5          | If high, End of Transmit Frame interrupt is on.                   |  |  |  |  |

| D6          | If high, End of Receive Frame interrupt is on.                    |  |  |  |  |

| D7          | Not used.                                                         |  |  |  |  |

**TABLE VII. Time Slot Map Instructions**

|    |    | Data                           | a Byte                |        |    |    | Description of Time Clat Man Instruction On de                                                                                                                                                                            |

|----|----|--------------------------------|-----------------------|--------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 | D6 | D5 D4                          | D3                    | Đ2     | D1 | D0 | Description of Time Slot Map Instruction Code                                                                                                                                                                             |

| 0  | 0  |                                | 1                     |        |    | 0  | Move data from an external device (e.g., parallel COMBO) to a serial port transmitter. The Map address identifies the proper transmitter.                                                                                 |

| 0  | 0  |                                | Address<br>field for  |        |    | 1  | Move data from a serial port receiver to an external device. The Map address identifies the proper receiver.                                                                                                              |

| 0  | 1  | devices<br>connected<br>to the |                       |        |    | 0  | Move data from an external device to the Interface Register whenever a match occurs between this data byte                                                                                                                |

| 0  | 1  |                                | data bus              |        |    | 1  | and the contents of the Interface Register Controller.  Move data from the Interface Register to an external device whenever a match occurs between this data byte and the contents of the Interface Register Controller. |

| 1  | 0  |                                |                       |        |    | 0  | Move data from the Transmit Message Register, through the protocol logic section to a serial port transmitter. The Map address identifies the proper transmitter.                                                         |

| 1  | 0  | Don                            | T<br>'t care (No<br>↓ | ote 1) |    | 1  | Move data from a serial port receiver, through the protocol logic section to the Receive Message Register. The Map address identifies the proper receiver.                                                                |

| 1  | 1  |                                |                       |        |    | 0  | No operation.                                                                                                                                                                                                             |

| 1  | 1  |                                |                       |        |    | 1  | No operation.                                                                                                                                                                                                             |

Note 1: To minimize bus and system noise it is recommended that this field be set to all '1's.

**TABLE VIII. Signaling Memory Addressing**

| Hex<br>Address | Description of Memory Access with ECS Disabled | Description of Memory Access with ECS Enabled READ signaling data received for external |  |  |

|----------------|------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|

| 8 0            | READ bits D0 and D1 of cell                    |                                                                                         |  |  |

|                | number 0.                                      | device 0.                                                                               |  |  |

| 8 1            | WRITE bits D0 and D1 of cell                   | Not used.                                                                               |  |  |

|                | number 0.                                      |                                                                                         |  |  |

| 8 2            | READ bits D0 and D1 of cell                    | READ signaling data received for external device 1.                                     |  |  |

|                | number 1.                                      |                                                                                         |  |  |

| 8 3            | WRITE bits D0 and D1 of cell                   | Not used.                                                                               |  |  |

|                | number 1.                                      |                                                                                         |  |  |

| •              | •                                              | •                                                                                       |  |  |

| •              | •                                              | •                                                                                       |  |  |

| •              | •                                              | •                                                                                       |  |  |

| ВЕ             | READ bits D0 and D1 of cell                    | READ signaling data received for external                                               |  |  |

|                | number 31.                                     | device 31.                                                                              |  |  |

| B F            | WRITE bits D0 and D1 of cell                   | Not used.                                                                               |  |  |

|                | number 31.                                     |                                                                                         |  |  |

| C 0            | READ bits D0 and D1 of cell                    | Not used.                                                                               |  |  |

|                | number 32.                                     |                                                                                         |  |  |

| C 1            | WRITE bits D0 and D1 of cell                   | WRITE into memory, external device 0                                                    |  |  |

|                | number 32.                                     | transmit signal data.                                                                   |  |  |

| C 2            | READ bits D0 and D1 of cell                    | Not used.                                                                               |  |  |

|                | number 33.                                     |                                                                                         |  |  |

| C 3            | WRITE bits D0 and D1 of cell                   | WRITE into memory, external device 1                                                    |  |  |

|                | number 33.                                     | transmit signal data.                                                                   |  |  |

| •              | •                                              | •                                                                                       |  |  |

| •              | •                                              | •                                                                                       |  |  |

| •              | •                                              | •                                                                                       |  |  |

| FE             | READ bits D0 and D1 of cell                    | Not used.                                                                               |  |  |

|                | number 63.                                     |                                                                                         |  |  |

| FF             | WRITE bits D0 ad D1 of cell                    | WRITE into memory, external device 31                                                   |  |  |

|                | number 63.                                     | transmit signal data.                                                                   |  |  |

Lit. # 113980

2.043-2.070 (51.89-52.58) 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

Molded Dual-In-Package (N) Order Number TP3120J or TP3122J or TP3110J or TP3112J NS Package N40A

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation

Corporation 2900 Semiconductor Drive P.O. Box 58090 Santa Clara, CA 95052-8090 Tel: (408) 721-5000 TWX: (910) 339-9240

National Semiconductor GmbH Westendstrasse 193-195 D-8000 Munchen 21 West Germany Tel: (089) 5 70 95 01 Telex: 522772

NS Japan Ltd. 4-403 Ikebukuro, Toshima-ku, Tokyo 171, Japan Tel: (03) 988-2131 FAX: 011-81-3-988-1700

National Semiconductor Hong Kong Ltd.

Southeast Asia Marketing

Austin Tower, 4th Floor

22-26A Austin Avenue

Tsimshatsui, Kowloon, H.K. Tel: 3-7231290, 3-7243645

National Semicondutores Do Brasil Ltda. Av. Brig. Faria Lima, 830 Av. Brig. Faria Lima, 830 8 Andar 01452 Sao Paulo, SP. Brasil Tel: (55/11) 212-5066 Telex: 391-1131931 NSBR BR