# ANALOG DEVICES

# 16 V Rail-to-Rail Buffer Amplifier

AD8560

### FEATURES

Single-Supply Operation: 4.5 V to 16 V Dual-Supply Capability from ±2.25 V to ±8 V Input Capability Beyond the Rails Rail-to-Rail Output Swing Continuous Output Current: 35 mA Peak Output Current: 250 mA Offset Voltage: 10 mV Max Slew Rate: 8 V/µs Stable with 1 µF Loads Supply Current

APPLICATIONS LCD Reference Drivers Portable Electronics Communications Equipment

### **GENERAL DESCRIPTION**

The AD8560 is a low cost, five-channel, single-supply buffer amplifier with rail-to-rail input and output capability. The AD8560 is optimized for LCD monitor applications.

These LCD buffers have high slew rates, a 35 mA continuous output drive, and high capacitive load drive capability. They have wide supply range and offset voltages below 10 mV.

The AD8560 is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range. They are available on tape and reel in a 16-lead LFCSP.

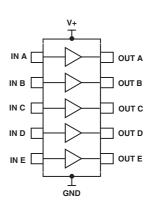

### **BLOCK DIAGRAM**

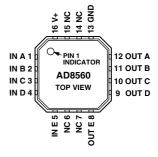

16-Lead LFCSP (CP Suffix)

NC = NO CONNECT

REV.0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2002

# AD8560-SPECIFICATIONS

### **ELECTRICAL CHARACTERISTICS** (4.5 V $\le$ V<sub>S</sub> $\le$ 16 V, V<sub>CM</sub> = V<sub>S</sub>/2, T<sub>A</sub> = 25°C, unless otherwise noted.)

| Parameter                                                                                                                       | Symbol                                                    | Conditions                                                                                                                                                                                                                                        | Min                          | Тур                                          | Max                               | Unit                               |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------|-----------------------------------|------------------------------------|

| INPUT CHARACTERISTICS<br>Offset Voltage<br>Offset Voltage Drift<br>Input Bias Current<br>Input Voltage Range<br>Input Impedance | $V_{OS}$<br>$\Delta V_{OS}/\Delta T$<br>$I_B$<br>$Z_{IN}$ | $-40^{\circ}C \le T_A \le +85^{\circ}C$ $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                                                                                                                                   | -0.5                         | 2<br>5<br>80<br>400                          | 10<br>600<br>800<br>$V_{S} + 0.5$ | mV<br>μV/°C<br>nA<br>nA<br>V<br>kΩ |

| Input Capacitance                                                                                                               | C <sub>IN</sub>                                           |                                                                                                                                                                                                                                                   |                              | 1                                            |                                   | pF                                 |

| OUTPUT CHARACTERISTICS<br>Output Voltage High<br>Output Voltage Low                                                             | V <sub>OH</sub>                                           | $\begin{split} I_L &= 100 \; \mu A \\ V_S &= 16 \; V, \; I_L = 5 \; m A \\ -40^\circ C &\leq T_A \; \leq \; +85^\circ C \\ V_S &= 4.5 \; V, \; I_L = 5 \; m A \\ -40^\circ C &\leq T_A \; \leq \; +85^\circ C \\ I_L &= 100 \; \mu A \end{split}$ | 15.85<br>15.75<br>4.2<br>4.1 | V <sub>s</sub> - 0.005<br>15.95<br>4.38<br>5 |                                   | V<br>V<br>V<br>V<br>V<br>mV        |

| Continuous Output Current                                                                                                       | I <sub>OUT</sub>                                          |                                                                                                                                                                                                                                                   |                              | 42<br>95<br>35                               | 150<br>250<br>300<br>400          | mV<br>mV<br>mV<br>mV<br>mA         |

| Peak Output Current                                                                                                             | $I_{PK}$                                                  | $V_s = 16 V$                                                                                                                                                                                                                                      |                              | 250                                          |                                   | mA                                 |

| TRANSFER CHARACTERISTICS<br>Gain                                                                                                | A <sub>VCL</sub>                                          | $R_{L} = 2 k\Omega$ $-40^{\circ}C \le T_{A} \le +85^{\circ}C$                                                                                                                                                                                     | 0.995<br>0.995               | 0.9985<br>0.9980                             | 1.005<br>1.005                    | V/V<br>V/V                         |

| Gain Linearity                                                                                                                  | NL                                                        | $R_{\rm L} = 2 \ \text{k}\Omega, \ V_{\rm O} = 0.5 \ \text{to} \ (V_{\rm S} - 0.5 \ \text{V})$                                                                                                                                                    |                              | 0.01                                         |                                   | %                                  |

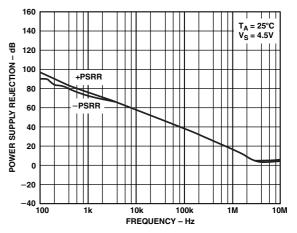

| POWER SUPPLY<br>Supply Voltage<br>Power Supply Rejection Ratio                                                                  | V <sub>S</sub><br>PSRR                                    | $V_S = 4 V \text{ to } 17 V$<br>-40°C ≤ $T_A \le +85°C$                                                                                                                                                                                           | 4.5<br>70                    | 90                                           | 16                                | V<br>dB                            |

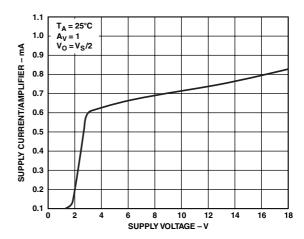

| Supply Current/Amplifier                                                                                                        | I <sub>SY</sub>                                           | $V_0 = V_s/2$ , No Load<br>-40°C $\leq T_A \leq +85$ °C                                                                                                                                                                                           |                              | 780                                          | 1,000<br>1,200                    | μΑ<br>μΑ                           |

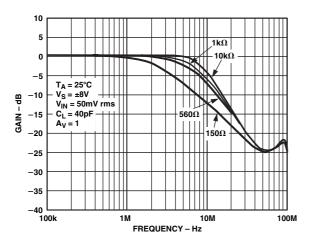

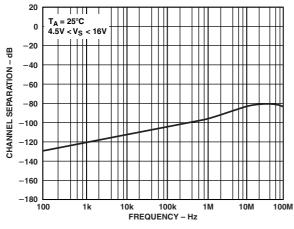

| DYNAMIC PERFORMANCE<br>Slew Rate<br>Bandwidth<br>Phase Margin<br>Channel Separation                                             | SR<br>BW<br>Øo                                            | $ \begin{array}{l} R_{L} = 10 \ \text{k}\Omega, \ C_{L} = 200 \ \text{pF} \\ -3 \ \text{dB}, \ R_{L} = 10 \ \text{k}\Omega, \ C_{L} = 10 \ \text{pF} \\ R_{L} = 10 \ \text{k}\Omega, \ C_{L} = 10 \ \text{pF} \end{array} $                       | 4.5                          | 8<br>8<br>65<br>75                           |                                   | V/µs<br>MHz<br>Degrees<br>dB       |

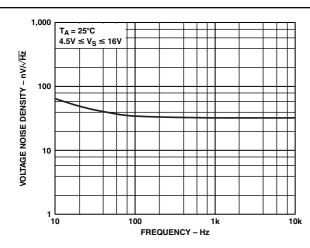

| NOISE PERFORMANCE<br>Voltage Noise Density<br>Current Noise Density                                                             | e <sub>n</sub><br>e <sub>n</sub><br>i <sub>n</sub>        | f = 1  kHz<br>f = 10 kHz<br>f = 10 kHz                                                                                                                                                                                                            |                              | 27<br>25<br>0.8                              |                                   | nV/√Hz<br>nV/√Hz<br>pA/√Hz         |

Specifications subject to change without notice.

-2-

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage (V <sub>S</sub> ) 18 V            |

|--------------------------------------------------|

| Input Voltage                                    |

| Differential Input VoltageVs                     |

| Storage Temperature Range65°C to +150°C          |

| Operating Temperature Range40°C to +85°C         |

| Junction Temperature Range                       |

| Lead Temperature Range (Soldering, 60 sec) 300°C |

| ESD Tolerance (HBM)1.5 kV                        |

| ESD Tolerance (CDM) 1 kV                         |

|                                                  |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Package Type       | $\theta_{JA}{}^1$ | θ <sub>JC</sub> | $\Psi_{JB}^{2}$ | Unit |

|--------------------|-------------------|-----------------|-----------------|------|

| 16-Lead LFCSP (CP) | 35                |                 | 13              | °C/W |

NOTES

${}^1\theta_{JA} \mbox{ is specified for worst-case conditions, i.e., } \theta_{JA} \mbox{ is specified for device soldered onto a circuit board for surface-mount packages.}$

$^2\Psi_{JB}$  is applied for calculating the junction temperature by reference to the board temperature.

#### **ORDERING GUIDE**

| Model     | Temperature    | Package       | Package |  |

|-----------|----------------|---------------|---------|--|

|           | Range          | Description   | Option  |  |

| AD8560ACP | –40°C to +85°C | 16-Lead LFCSP | CP-16   |  |

Available in reels only.

#### CAUTION-

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD8560 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### **AD8560–Typical Performance Characteristics**

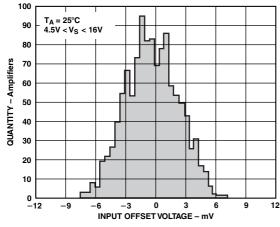

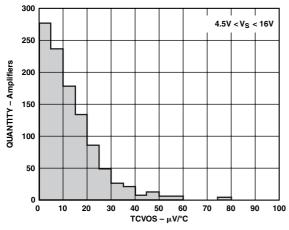

TPC 1. Input Offset Voltage Distribution

TPC 2. Input Offset Voltage Drift Distribution

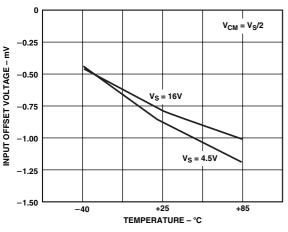

TPC 3. Input Offset Voltage vs. Temperature

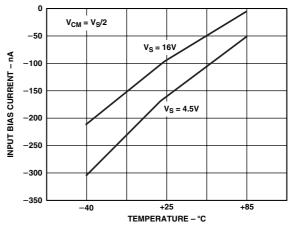

TPC 4. Input Bias Current vs. Temperature

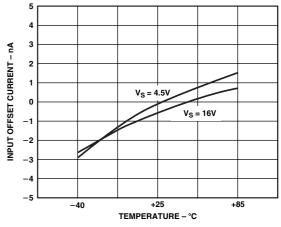

TPC 5. Input Offset Current vs. Temperature

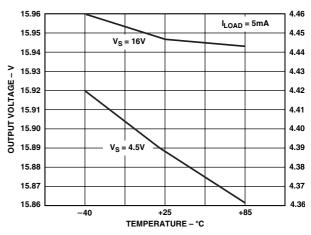

TPC 6. Output Voltage Swing vs. Temperature

TPC 7. Output Voltage Swing vs. Temperature

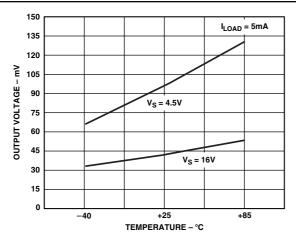

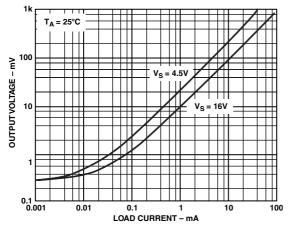

TPC 8. Voltage Gain vs. Temperature

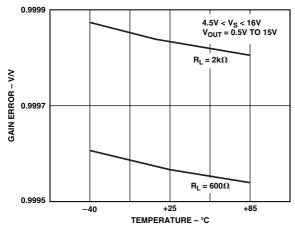

TPC 9. Output Voltage to Supply Rail vs. Load Current

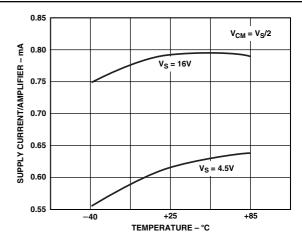

TPC 10. Supply Current/Amplifier vs. Temperature

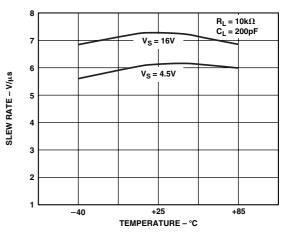

TPC 11. Slew Rate vs. Temperature

TPC 12. Supply Current/Amplifier vs. Supply Voltage

TPC 13. Frequency Response vs. Resistive Loading

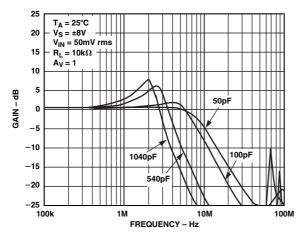

TPC 14. Frequency Response vs. Capacitive Loading

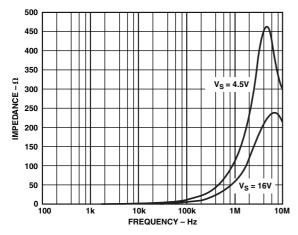

TPC 15. Closed-Loop Output Impedance vs. Frequency

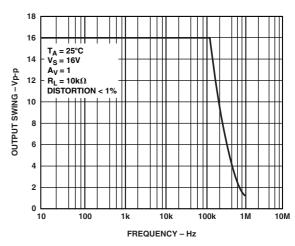

TPC 16. Closed-Loop Output Swing vs. Frequency

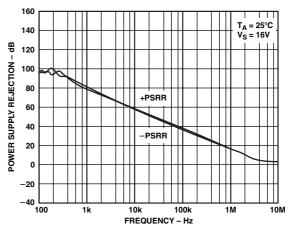

TPC 17. Power Supply Rejection Ratio vs. Frequency

TPC 18. Power Supply Rejection Ratio vs. Frequency

-6-

TPC 19. Voltage Noise Density vs. Frequency

TPC 20. Channel Separation vs. Frequency

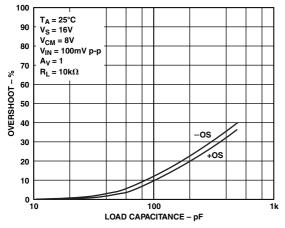

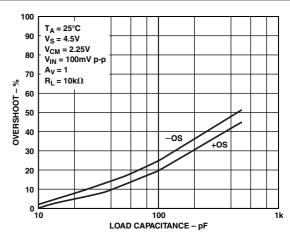

TPC 21. Small Signal Overshoot vs. Load Capacitance

TPC 22. Small Signal Overshoot vs. Load Capacitance

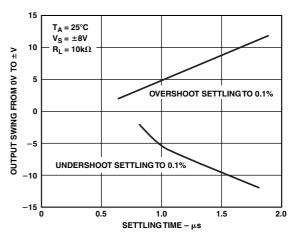

TPC 23. Settling Time vs. Step Size

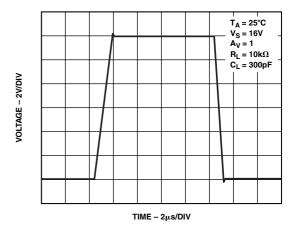

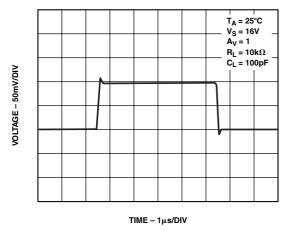

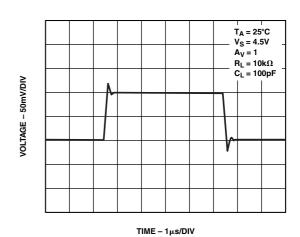

TPC 24. Large Signal Transient Response

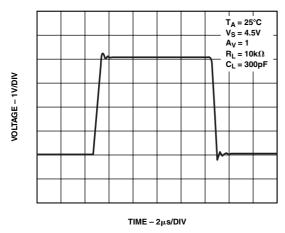

TPC 25. Large Signal Transient Response

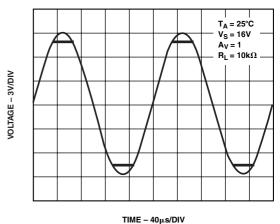

TPC 26. Small Signal Transient Response

TPC 27. Small Signal Transient Response

TPC 28. No Phase Reversal

### APPLICATIONS

### **Theory of Operation**

These buffers are designed to drive large capacitive loads in LCD applications. Each has a high output current drive and rail-to-rail input/output operation and can be powered from a single 16 V supply. They are also intended for other applications where low distortion and high output current drive are needed.

#### Input Overvoltage Protection

As with any semiconductor device, whenever the input exceeds either supply voltage, attention needs to be paid to the input overvoltage characteristics. As an overvoltage occurs, the amplifier could be damaged depending on the voltage level and the magnitude of the fault current. When the input voltage exceeds either supply by more than 0.6 V, internal pin junctions will allow current to flow from the input to the supplies.

This input current is not inherently damaging to the device as long as it is limited to 5 mA or less. If a condition exists using the buffers where the input exceeds the supply by more than 0.6 V, a series external resistor should be added. The size of the resistor can be calculated by using the maximum overvoltage divided by 5 mA. This resistance should be placed in series with the input exposed to an overvoltage.

#### **Output Phase Reversal**

The buffer family is immune to phase reversal. Although the device's output will not change phase, large currents due to input overvoltage could damage the device. In applications where the possibility exists of an input voltage exceeding the supply voltage, overvoltage protection should be used as described in the previous section.

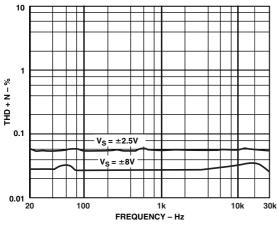

#### Total Harmonic Distortion (THD+N)

The buffer family features low total harmonic distortion. The total harmonic distortion plus noise for the buffer over the entire supply range is below 0.08%. When the device is powered from a 16 V supply, the THD + N stays below 0.03%. Figure 1 shows the AD8560's THD + N versus the frequency performance.

Figure 1. THD + N vs. Frequency

#### **Short Circuit Output Conditions**

The buffer family does not have internal short circuit protection circuitry. As a precautionary measure, do not short the output directly to the positive power supply or to the ground.

It is not recommended to operate the AD8560 with more than 35 mA of continuous output current. The output current can be limited by placing a series resistor at the output of the amplifier whose value can be derived using the following equation:

$$R_X \ge \frac{V_S}{35 \, mA}$$

For a 5 V single-supply operation,  $R_X$  should have a minimum value of 143  $\Omega$ .

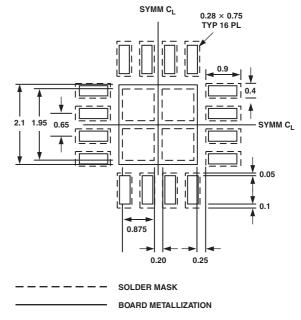

#### Recommended Land Pattern for the AD8560

Figure 2 is a recommended land pattern for the AD8560 PCB design. The recommended thermal pad size for the PCB design matches the dimensions of the exposed pad on the bottom of the package. The solder mask design for improved thermal pad contact to the exposed pad and reliability uses a stencil pattern for approximately 85% solder coverage. A minimum clearance of 0.25 mm is maintained on the PCB between the outer edges of the thermal pad and the inner edges of the pattern for the land to avoid shorting. For better thermal performance, thermal vias should also be used. Since the AD8560 is relatively a low power part, just soldering the exposed package pad to the PCB thermal pad should provide sufficient electrical performance.

Figure 2. 16-Lead 4 x 4 Land Pattern

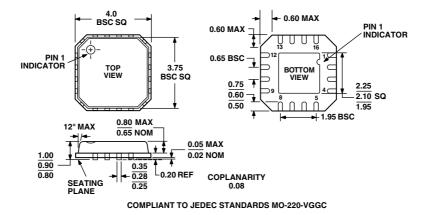

### **OUTLINE DIMENSIONS**

#### 16-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body (CP-16)

Dimensions shown in millimeters