## 1 Megabyte Sync/Sync Burst, Small Outline DIMM

### FEATURES

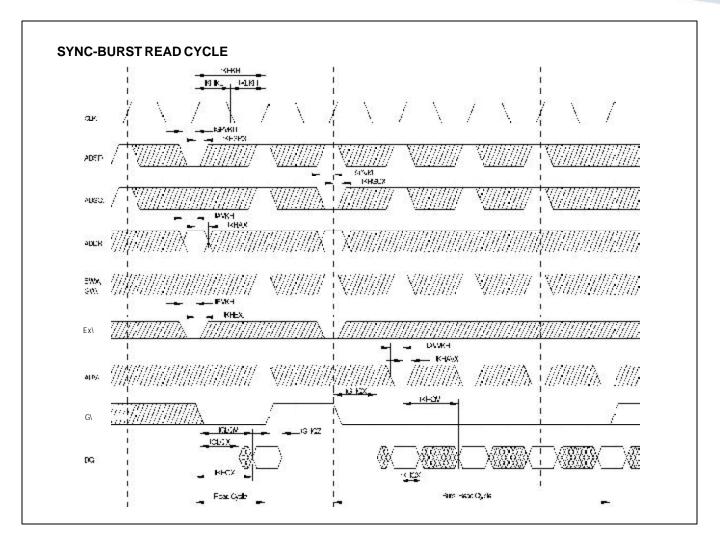

- 2x64kx72 Synchronous, Synchronous Burst

- Flow-Through Architecture

- Sequential Burst MODE

- Clock Controlled Registered Bank Enables (E1\, E2)

- Clock Controlled Byte Write Mode Enable (BWE\)

- Clock Controlled Byte Write Enables (BW1\ BW8\)

- Clock Controlled Registered Address

- Clock Controlled Registered Global Write (GW)

- Aysnchronous Output Enable (G\)

- Internally self-timed Write

- Gold Lead Finish

- 3.3V +10% Operation

- Access Speed(s): TKHQV=8.5, 9, 10, 12ns

- Common Data I/O

- High Capacitance (30pf) drive, at rated Access

Speed

- Single total array Clock

- Multiple Vcc and Gnd

The EDI2AG27265VxxD1 is a Synchronous/Synchronous Burst SRAM, 72 position 30 DIMM(144 contacts) Module, organized as 2x64Kx72. The Module contains four (4) Synchronous Burst Ram Devices, packaged in the industry standard JEDEC 14mmx20mm TQFP placed on a Multilayer FR4 Substrate. The module architecture is defined as a Sync/Sync Burst, Flow-Through, with support for either linear or sequential burst. This module provides High Performance, 2-1-1-1 accesses when used in Burst Mode, and used as a Synchronous Only Mode, provides a high performance cost advantage over BiCMOS aysnchronous device architectures.

Synchronous Only operations are performed via strapping ADSC\ Low, and ADSP\ / ADV\ High, which provides for Ultra Fast Accesses in Read Mode while providing for internally self-timed Early Writes.

Synchronous/Synchronous Burst operations are in relation to an externally supplied clock, Registered Address, Registered Global Write, Registered Enables as well as an Asynchronous Output enable. This Module has been defined with full flexibility, which allows individual control of each of the eight bytes, as well as Quad Words in both Read and Write Operations.

| PIN NAMES |           |                                 |

|-----------|-----------|---------------------------------|

|           | DQ0-DQ63  | Input/Output Bus                |

|           | DQP0-DQP7 | Parity Bits                     |

|           | A0-A15    | Address Bus                     |

|           | E1 E2     | Synchronous Bank Enables        |

|           | BWE\      | Byte Write Mode Enable          |

|           | BW1\-BW8\ | Byte Write Enables              |

|           | Clk       | Array Clock                     |

|           | GW        | Synchronous Global write Enable |

|           | G\        | Asynchronous Output Enable      |

|           | Vcc       | 3.3V Power Supply               |

|           | Vss       | Gnd                             |

### **PIN CONFIGURATION**

| MN         | FUNCION     | FIN | FUNCTION      | FIN RUNCTION |       | FN   | FUNCTION |

|------------|-------------|-----|---------------|--------------|-------|------|----------|

| 1          | VSS         | 37  | DCC           | 73           | VSS   | 103  | DQ41     |

| 2          | 1/93        | 30  | DC7           | 74           | 195   | 110  | DQ46     |

| 3          | 20          | 30  | DC1           | 75           | E%4   | 111  | DG42     |

| 2          | RFU         | 40  | .:20          | 76           | DCFS  | 112  | DQ45     |

| 5          | RŲ          | 4-  | DC2           | 77           | VCC   | 113  | DC43     |

| 6          | A1          | 42  | 0 <b>6</b> 8  | 78           | %œ    | 4    | DQ44     |

| 7          | 20          | 42  | DC3           | 78           | DC24  | ···s | VSS      |

| 8          | <i>∳</i> -5 | 41  | DC4           | 80           | DQ31  | 115  | VSS      |

| 5          | A14         | 45  | V\$6          | 81           | DQ25  | 117  | EW/7     |

| 10         | 43          | 45  | VSS           | 62           | CC.30 | 118  | DOPE     |

| 11         | <u>14</u>   | 47  | BV/2          | 83           | 3028  | 119  | 100      |

| 12         | A10         | 48  | DCF1          | ধ্য          | CC2D  | -20  | VCC      |

| 13         | A*2         | 49  | VCC           | Æ            | X.227 | 191  | 3048     |

| 14         | A5          | 30  | VCC           | 35           | 55CC  | 122  | 0056     |

| <b>'</b> 5 | K           | 5   | DCS           | 87           | V92   | 123  | DX248    |

| 16         | A11         | 52  | 2015          | 86           | VSS   | 124  | DQ54     |

| •7         | A10         | 53  | DCG           | 89           | BNS.  | -25  | D050     |

| °U         | <i>4</i> 7  | 54  | DC <b>1</b> 4 | 9)           | DC-4  | 196  | DQ53     |

| -D         | A8          | 55  | DQ10          | 31           | VCC   | -27  | DQ:1     |

| 20         | .49         | 56  | DOTIB         | 92           | VCC   | 128  | DO2      |

| 21         | ACC .       | 57  | 3C**          | \$3          | DC22  | *29  | Ves      |

| 22         | VOC         | 58  | DG12          | \$4          | GGSƏ  | 130  | VSS      |

| 23         | G.          | 53  | Veg           | 95           | DC38  | 131  | EMS/     |

| 24         | ₽RU         | æ   | VSS           | 96           | LC38  | 132  | DCP7     |

| 25         | GW.         | F.  | EA3           | 97           | DC34  | 103  | VCC      |

| 26         | AD?A        | ٤2  | DCF2          | 38           | DG3/  | 134  | VOC      |

| 27         | ADSEN       | 83  | V00           | 66           | DC35  | 135  | DQ35     |

| 2B         | ADGC)       | F4  | VCO.          | 100          | DC35  | 196  | DC)33    |

| 29         | E1:         | 65  | DC16          | 101          | VSS   | 137  | DO57     |

| <u>;</u> 9 | CK          | 66  | CC29          | 102          | VES   | 132  | DQ52     |

| ŝ.         | E2.         | 67  | DC17          | 103          | EW\$  | 139  | DC58     |

| 32         | BWB         | 63  | DQ22          | 124          | DCF5  | 140  | DOEI     |

| 23         | BMA :       | C9  | DC-8          | 105          | vce   | 141  | DG29     |

| 84         | DCP0        | 70  | D021          | 106          | VCC   | 1/12 | DQ60     |

| 35         | 702         | 7-  | DC-9          | 107          | CC40  | -43  | V93      |

| æ          | 200         | 72  | DC20          | 108          | DC47  | 144  | VSS      |

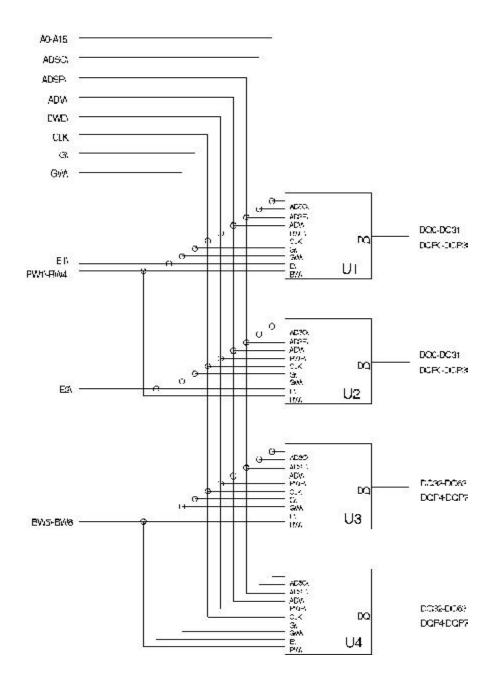

#### FUNCTIONAL BLOCK DIAGRAM

## WHITE ELECTRONIC DESIGNS

#### **PIN DESCRIPTIONS**

| DIMM Pins<br>3, 6, 7, 10, 11 | Symbol<br>A0-A17 | Type         | Description<br>Addresses: These inputs are registered and must meet the setup and hold |

|------------------------------|------------------|--------------|----------------------------------------------------------------------------------------|

|                              |                  | Input        |                                                                                        |

| 14, 15, 18, 19,              |                  | Synchronous  | times around the rising edge of CLK. The burst counter generates internal              |

| 17, 16, 13, 12, 9            |                  | lan, et      | addresses associated with A0 and A1, during burst and wait cycle.                      |

| 33, 47, 61                   | BW1 BW2          | Input        | Byte Write: A byte write is LOW for a WRITE cycle and HIGH for a READ                  |

| 75, 89, 103                  | BW3 BW4          | Synchronous  | cycle. BW0/ controls DQ0-7 and DQP0, BW1\ controls DQ8-15 and DQP1.                    |

| 117,13                       | BW5 BW6          |              | BW2\controls DQ16-23 and DQP2. BW3\controls DQ24-31 and DQP3.                          |

|                              | BW7 BW8\         |              | BW4\controls DQ32-39 and DQP4. BW5\controls DQ40-47 and DQP5.                          |

|                              |                  | have at      | BW6\controls DQ48-55 and DQP6. BW7\controls DQ56-64 and DQP7.                          |

| 32                           | BWE\             | Input        | Write Enable: This active LOW input gates byte write operations and must               |

| 05                           | 0111             | Synchronous  | meet the setup and hold times around the rising edge of CLK.                           |

| 25                           | GW               | Input        | Global Write: This active LOW input allows a full 72-bit WRITE to occur                |

|                              |                  | Synchronous  | independent of the BWE\ and BWx\ lines and must meet the setup and hold                |

|                              |                  |              | times around the rising edge of CLK.                                                   |

| 30                           | CLK              | Input        | Clock: This signal registers the addresses, data, chip enables, write control          |

|                              |                  | Synchronous  | and burst control inputs on its rising edge. All synchronous inputs must               |

|                              |                  |              | meet setup and hold times around the clock's rising edge.                              |

| 29, 31,                      | E1 E2\           | Input        | Bank Enables: These active LOW inputs are used to enable each                          |

|                              | E3 E4\           | Synchronous  | individual bank and to gate ADSP\.                                                     |

| 23                           | G/               | Input        | Output Enable: This active LOW asynchronous input enables the data output              |

|                              |                  |              | drivers.                                                                               |

| 26                           | ADV              | Input        | Address Status Processor: This active LOW input is used to control the                 |

|                              |                  | Synchronous  | internal burst counter. A HIGH on this pin generates wait cycle (no address            |

|                              |                  |              | advance).                                                                              |

| 27                           | ADSP\            | Input        | Address Status Processor: This active LOW input, along with EL\ and EH\                |

|                              | Synchronous      |              | being LOW, causes a new external address to be registered and a READ                   |

|                              |                  |              | cycle is initiated using the new address.                                              |

| 28                           | ADSC\            | Input        | Address Status Controller: This active LOW input causes device to be de-               |

|                              | Synchronous      |              | selected or selected along with new external address to be registered. A               |

|                              |                  |              | READ or WRITE cycle is initiated depending upon write control inputs.                  |

| Various                      | DQ0-63           | Input/Output | Data Inputs/Outputs: First byte is DQ0-7, second byte is DQ8-15, third byte is         |

|                              |                  |              | DQ16-23, fourth byte is DQ24-31, fifth byte is DQ32-39, sixth byte is                  |

|                              |                  |              | DQ40-47, seventh byte is DQ48-55 and the eight byte is DQ56-64.                        |

| 38, 48, 62                   | DQP0-7           | Input/Output | Parity Inputs/Outputs: DQP0 is parity bit for DQ0-7. DQP1 is parity bit for DQ8-15     |

| 76, 90, 104                  |                  |              | DQP2 is parity bit for DQ16-23. DQP3 is parity bit for DQ24-31. DQP4\ is parity        |

| 118,132                      |                  |              | bit for DQ32-39. DQP5 is parity bit for DQ40-47. DQP6\ is parity bit for DQ48-55       |

|                              |                  |              | DQP7 is parity bit for DQ56-64 and DQP7. In order to use the device Configured         |

|                              |                  |              | as a128K x 64, the parity bits need to be tied to Vss through a 10K ohm resistor       |

| Various                      | Vcc              | Supply       | Core power supply: +3.3V -5%/+10%                                                      |

| Various                      | Vss              | Ground       | Ground                                                                                 |

4

#### SYNCHRONOUS BURST - TRUTH TABLE

| Operation                           | E1\ | E2\ | ADSP\ | ADSC\ | ADV\ | GW\ | G\ | CLK | DQ     | Addr. Used |

|-------------------------------------|-----|-----|-------|-------|------|-----|----|-----|--------|------------|

| Deselected Cycle, Power Down; Ban   | k1H | Х   | Х     | L     | Х    | Х   | Х  | L-H | High-Z | None       |

| Deselected Cycle, Power Down; Ban   | k2X | Н   | Х     | L     | Х    | Х   | Х  | L-H | High-Z | None       |

| Read Cycle, Begin Burst; Bank 1     | L   | Н   | L     | Х     | Х    | Х   | L  | L-H | Q      | External   |

| Read Cycle, Begin Burst; Bank 1     | L   | Н   | L     | Х     | Х    | Х   | Н  | L-H | High-Z | External   |

| Read Cycle, Begin Burst; Bank 2     | Н   | L   | L     | Х     | Х    | Х   | L  | L-H | Q      | External   |

| Read Cycle, Begin Burst; Bank 2     | Н   | L   | L     | Х     | Х    | Х   | Н  | L-H | High-Z | External   |

| Write Cycle, Begin Burst; Bank 1    | L   | Н   | Н     | L     | Х    | L   | Х  | L-H | D      | External   |

| Write Cycle, Begin Burst; Bank 2    | Н   | L   | Н     | L     | Х    | L   | Х  | L-H | D      | External   |

| Read Cycle, Begin Burst; Bank 1     | L   | Н   | Η     | L     | Х    | Н   | L  | L-H | Q      | External   |

| Read Cycle, Begin Burst; Bank 1     | L   | Н   | Η     | L     | Х    | Н   | Н  | L-H | High-Z | External   |

| Read Cycle, Begin Burst; Bank 2     | Н   | L   | Η     | L     | Х    | Н   | L  | L-H | Q      | External   |

| Read Cycle, Begin Burst; Bank 2     | Н   | L   | Η     | L     | Х    | Н   | Н  | L-H | High-Z | External   |

| Read Cycle, Continue Burst; Bank 1  | Х   | Н   | Х     | Н     | L    | Н   | L  | L-H | Q      | Next       |

| Read Cycle, Continue Burst; Bank 1  | Х   | Н   | Х     | Н     | L    | Н   | Н  | L-H | High-Z | Next       |

| Read Cycle, Continue Burst; Bank 2  | Н   | Х   | Х     | Н     | L    | Н   | L  | L-H | Q      | Next       |

| Read Cycle, Continue Burst; Bank 2  | Н   | Х   | Х     | Н     | L    | Н   | Н  | L-H | High-Z | Next       |

| Read Cycle, Continue Burst; Bank 1  | Н   | Н   | Х     | Н     | L    | Н   | L  | L-H | Q      | Next       |

| Read Cycle, Continue Burst; Bank 1  | Н   | Н   | Х     | Н     | L    | Н   | Н  | L-H | High-Z | Next       |

| Read Cycle, Continue Burst; Bank 2  | Н   | Н   | Х     | Н     | L    | Н   | L  | L-H | Q      | Next       |

| Read Cycle, Continue Burst; Bank 2  | Н   | Н   | Х     | Н     | L    | Н   | Н  | L-H | High-Z | Next       |

| Write Cycle, Continue Burst; Bank 1 | Х   | Н   | Н     | Н     | L    | L   | Х  | L-H | D      | Next       |

| Write Cycle, Continue Burst; Bank 1 | Н   | Н   | Х     | Н     | L    | L   | Х  | L-H | D      | Next       |

| Write Cycle, Continue Burst; Bank 2 | Н   | Х   | Н     | Н     | L    | L   | Х  | L-H | D      | Next       |

| Write Cycle, Continue Burst; Bank 2 | Н   | Н   | Х     | Н     | L    | L   | Х  | L-H | D      | Next       |

| Read Cycle, Suspend Burst; Bank 1   | Х   | Н   | Η     | Н     | Н    | Н   | L  | L-H | Q      | Current    |

| Read Cycle, Suspend Burst; Bank 1   | Х   | Н   | Η     | Н     | Н    | Н   | Н  | L-H | High-Z | Current    |

| Read Cycle, Suspend Burst; Bank 2   | Н   | Х   | Н     | Н     | H    | Н   | L  | L-H | Q      | Current    |

| Read Cycle, Suspend Burst; Bank 2   | Н   | Х   | Н     | Н     | Н    | Н   | Н  | L-H | High-Z | Current    |

| Read Cycle, Suspend Burst; Bank 1   | Н   | Н   | Х     | Н     | Н    | Н   | L  | L-H | Q      | Current    |

| Read Cycle, Suspend Burst; Bank 1   | Н   | Н   | Х     | Н     | Н    | Н   | Н  | L-H | High-Z | Current    |

| Read Cycle, Suspend Burst; Bank 2   | Н   | Н   | Х     | Н     | Н    | Н   | L  | L-H | Q      | Current    |

| Read Cycle, Suspend Burst; Bank 2   | Н   | Н   | Х     | Н     | Н    | Н   | Н  | L-H | High-Z | Current    |

| Write Cycle, Suspend Burst; Bank 1  | Х   | Н   | Н     | Н     | Н    | L   | Х  | L-H | D      | Current    |

| Write Cycle, Suspend Burst; Bank 1  | Н   | Н   | Х     | Н     | Н    | L   | Х  | L-H | D      | Current    |

| Write Cycle, Suspend Burst; Bank 2  | Н   | Х   | Н     | Н     | Н    | L   | Х  | L-H | D      | Current    |

| Write Cycle, Suspend Burst; Bank 2  | Н   | Н   | Х     | Н     | Н    | L   | Х  | L-H | D      | Current    |

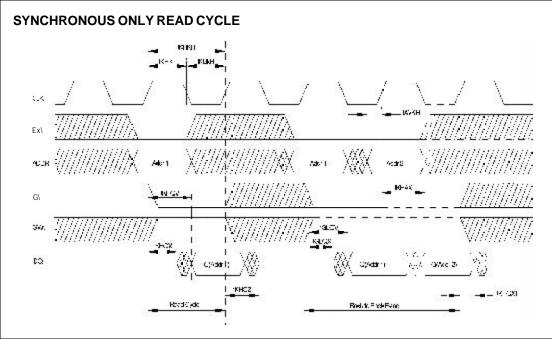

#### SYNCHRONOUS ONLY - TRUTH TABLE

| Operation                | E1\ | E2\ | GW\ | G\ | ZZ | CLK | DQ     |

|--------------------------|-----|-----|-----|----|----|-----|--------|

| Synchronous Write-Bank 1 | L   | Η   | L   | Н  | L  | ٨   | High-Z |

| Synchronous Read-Bank 1  | L   | Η   | Н   | L  | L  | ٨   |        |

| Synchronous Write-Bank 2 | Н   | L   | L   | Н  | L  | ٨   | High-Z |

| Synchronous Read-Bank 2  | H   | Ĺ   | H   | Ĺ  | L  | ٨   |        |

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Vcc Relative to Vss     | -0.5V to +4.6V     |

|------------------------------------|--------------------|

| Vin                                | -0.5V to Vcc +0.5V |

| Storage Temperature                | -55°C to +125°C    |

| Operating Temperature (Commercial) | 0°C to +70°C       |

| Operating Temperature (Industrial) | -40°C to +85°C     |

| Short Circuit Output Current       | 10 mA              |

"Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in operational sections of this specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **RECOMMENDED DC OPERATING CONDITIONS**

| Parameter      | Sym | Min  | Тур | Мах     | Units |

|----------------|-----|------|-----|---------|-------|

| Supply Voltage | VCC | 3.14 | 3.3 | 3.6     | V     |

| Supply Voltage | VSS | 0.0  | 0.0 | 0.0     | V     |

| Input High     | VH  | 1.1  | 3.0 | VCC+0.3 | V     |

| InputLow       | VIL | -0.3 | 0.0 | 0.3     | V     |

| Input Leakage  | ILi | -2   | 1   | 2       | μA    |

| Output Leakage | ILo | -2   | 1   | 2       | μA    |

#### DC ELECTRICAL CHARACTERISTICS - READ CYCLE

|                               |      |      |      |      |      | Max  |       |  |  |  |

|-------------------------------|------|------|------|------|------|------|-------|--|--|--|

| Description                   | SYM  | Тур  | 8.5  | 5    | 10   | 12   | Units |  |  |  |

| Power Supply Current          | lcc1 | 1.35 | 1.2  | 1.1  | 1.1  | 1.0  | А     |  |  |  |

| Power Supply Current          | lcc  | .700 | .550 | .800 | .750 | .700 | А     |  |  |  |

| Device Selected, No Operation |      |      |      |      |      |      |       |  |  |  |

| CMOS Standby                  | Icc3 | 200  | 300  | 300  | 300  | 300  | mA    |  |  |  |

| Clock Running-Deselect        | IccK | 500  | 750  | 750  | 750  | 750  | mA    |  |  |  |

#### BURST ADDRESS TABLE (MODE=NC/VCC)

| I |            |            |            |            |

|---|------------|------------|------------|------------|

|   | First      | Second     | Third      | Fourth     |

|   | Address    | Address    | Address    | Address    |

|   | (external) | (internal) | (internal) | (internal) |

|   | AA00       | AA01       | AA10       | A.A11      |

|   | AA01       | AA00       | AA11       | AA10       |

|   | AA10       | AA11       | AA00       | AA01       |

|   | AA11       | AA10       | AA01       | AA00       |

|   |            |            |            |            |

#### BURST ADDRESS TABLE (MODE=GND)

| First<br>Address<br>external) | Second<br>Address<br>(internal) | Third<br>Address<br>(internal) | Fourth<br>Address<br>(internal) |   |

|-------------------------------|---------------------------------|--------------------------------|---------------------------------|---|

| <br>AA00                      | AA01                            | AA10                           | AA11                            | _ |

| AA01                          | AA10                            | AA11                           | AA00                            |   |

| <br>AA10                      | AA11                            | AA00                           | AA01                            |   |

| <br>AA11                      | AA00                            | AA01                           | AA10                            | _ |

|                               |                                 |                                |                                 |   |

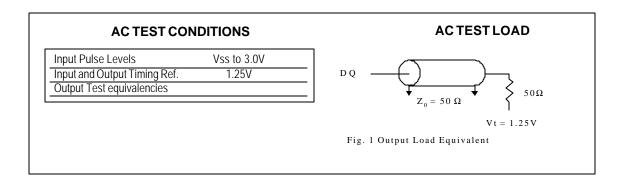

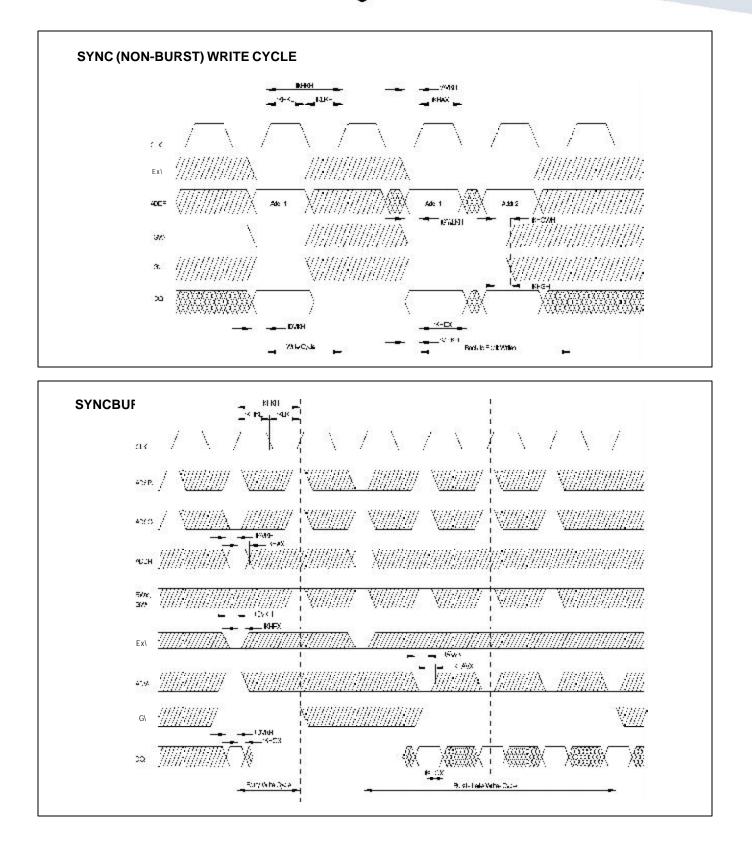

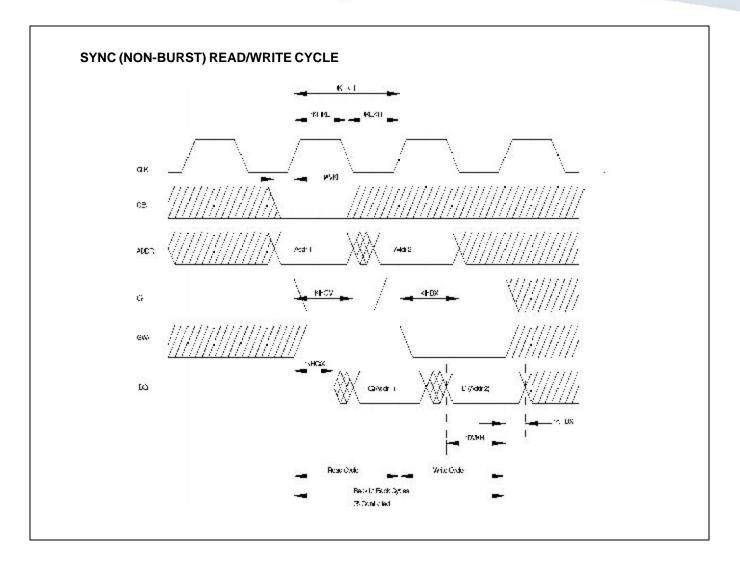

#### **READ CYCLE TIMING PARAMETERS**

|                                |        | 8.5 | ōns | 9   | ns  | 10  | ns  | 12ns |     |       |

|--------------------------------|--------|-----|-----|-----|-----|-----|-----|------|-----|-------|

| Description                    | Sym    | Min | Мах | Min | Мах | Min | Мах | Min  | Мах | Units |

| Clock Cycle Time               | tKhKh  | *   | *   | 10  |     | 10  |     | 15   |     | ns    |

| Clock High Time                | tKHKL  | *   | *   | 4   |     | 5   |     | 5    |     | ns    |

| Clock Low Time                 | tKLKH  | *   | *   | 9   |     | 5   |     | 5    |     | ns    |

| Clock to Output Valid          | tKHQV  | *   | *   |     | 9   |     | 10  |      | 12  | ns    |

| Clock to Output Invalid        | tKHQX1 | *   | *   | 3   |     | 3   |     | 3    |     | ns    |

| Clock to Output Low-Z          | tKHQX  | *   | *   | 2   |     | 2   |     | 2    |     | ns    |

| Output Enable to Output Valid  | tGLQV  | *   | *   |     | 4   |     | 4   |      | 5   | ns    |

| Output Enable to Output Low-Z  | tGLQX  | *   | *   | 0   |     | 0   |     | 0    |     | ns    |

| Output Enable to Output High-Z | tGHQZ  | *   | *   |     | 9   |     | 9   |      | 5   | ns    |

| Address Setup                  | tAVKH  | *   | *   | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Bank Enable Setup              | tEVKH  | *   | *   | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Address Hold                   | tKHAX  | *   | *   | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

| Bank Enable Hold               | tKHEX  | *   | *   | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

\*T\*BBD

## WHITE ELECTRONIC DESIGNS

#### WRITE CYCLE TIMING PARAMETERS

|                           |       | 8.5ns |     | 91  | ıs  | 10  | ns  | 12ns |     |       |

|---------------------------|-------|-------|-----|-----|-----|-----|-----|------|-----|-------|

| Description               | Sym   | Min   | Мах | Min | Мах | Min | Мах | Min  | Мах | Units |

| Clock Cycle Time          | tKHKH |       |     | 10  |     | 12  |     | 15   |     | ns    |

| Clock High Time           | tKHKL |       |     | 4   |     | 5   |     | 5    |     | ns    |

| Clock Low Time            | tKLKH |       |     | 4   |     | 5   |     | 5    |     | ns    |

| Address Setup             | tAVKH |       |     | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Address Hold              | tKHAX |       |     | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

| Bank Enable Setup         | tEVKH |       |     | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Bank Enable Hold          | tKHEX |       |     | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

| Global Write Enable Setup | tWVKH |       |     | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Global Write Enable Hold  | tKHWX |       |     | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

| Data Setup                | tDVKH |       |     | 2.5 |     | 2.5 |     | 2.5  |     | ns    |

| Data Hold                 | tKHDX |       |     | 1.0 |     | 1.0 |     | 1.0  |     | ns    |

# WHITE ELECTRONIC DESIGNS

WHITE ELECTRONIC DESIGNS

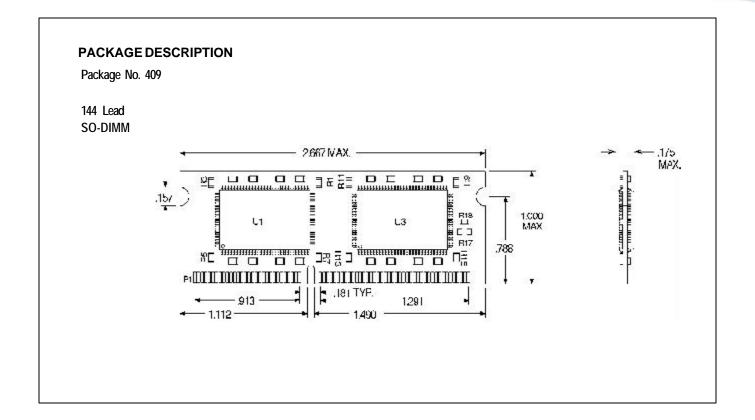

| PartNumber        | Organization | Voltage | Speed (ns) | Package     |

|-------------------|--------------|---------|------------|-------------|

| EDI2AG27265V85D1* | 2x64Kx72     | 3.3     | 8.5        | 144 SO-DIMM |

| EDI2AG27265V9D1*  | 2x64Kx72     | 3.3     | 9          | 144 SO-DIMM |

| EDI2AG27265V10D1  | 2x64Kx72     | 3.3     | 10         | 144 SO-DIMM |

| DI2AG27265V12D1   | 2x64Kx72     | 3.3     | 12         | 144 SO-DIMM |