# CMOS 16-bit Microcontroller

# TMP95FY64F

- 1. TMP95FY64F Basic Specification

- 1.1 Outline and Feature

TMP95FY64 is high-speed advanced 16-bit microcontroller developed for controlling medium to large-scale equipment. TMP95FY64 has 256K-Byte Flash memory which can be rewritten and erased on board.

TMP95FY64 is housed in QFP-100pin package.

Device characteristics are as follows:

- (1) Original High speed 16-bit CPU(900/H CPU)

- TLCS-90/900 instruction mnemonic upward compatible.

- 16M-byte linear address space

- General-purpose registers and register bank system

- 16-bit multiplication/ division and bit transfer/arithmetic instructions

- Micro DMA :4 channels(640ns/2bytes at 25MHz)

- (2) Minimum instruction execution time:160ns at 25MHz

- (3) Internal RAM:8Kbyte

Internal ROM:256Kbyte Flash memory

- (4) External memory expansion

- Can be expanded up to 16M byte (for both programs and data)

- AM8/16pin (select the external data bus width)

- Can mix 8- and 16-bit external data buses. ..... Dynamic data bus sizing

- (5) 8-bit timer:8 channels

- Including event counter function(2 channels)

- (6) 16-bit timer/event counter:2 channels

- (7) Serial interface:3 channels

- (8) 10-bit A/D converter:8 channels

- (9) 8-bit D/A converter:2 channels

- (10) Watchdog timer

- (11) Chip select/wait controller:4 blocks

- (12) Interrupt functions:45-Interrupt sources

- •9-CPU interrupts ····· SWI instruction, and Illegal instruction

- 26-Internal interrupts.....7-level priority can be set.

- 10-External interrupts.....7-level priority can be set.

- (13) I/O ports : Single chip mode 81 pins

Multi chip mode 55 pins(at AM8/16="H")

- (14) Standby function:4 HALT mode(RUN,IDLE2,IDLE1,STOP)

- (15) Operating Voltage : Vcc = 4.5 to 5.5V

- (16) Package:100pin QFP(LFFP100-P-1414-0.50C:Thickness 2.4mm)

#### 970514EBK1

TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfuction or failure of a TOSHIBA product could cause loss of human life,bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

• USP 4,382,279 owned by BULL CP8

- The products described in this document are subject to foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by

- TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.

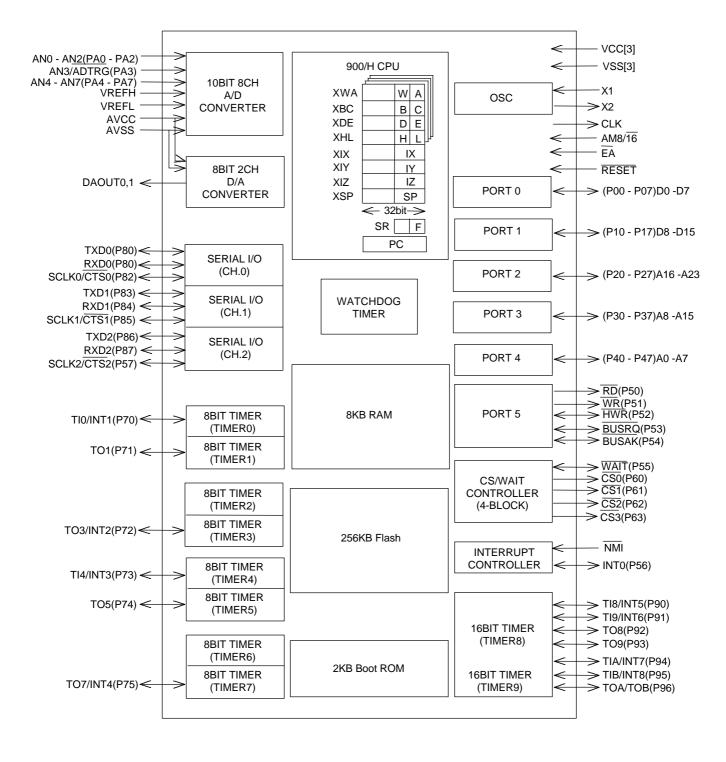

Figure 1 TMP95FY64 Block Diagram

#### 1.2 Pin Assignment and pin functions

#### 1.2.1 Pin Assignment

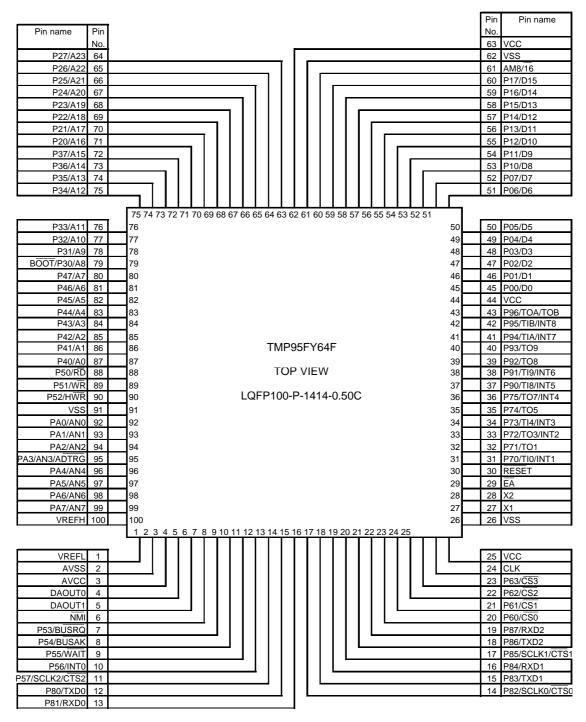

TMP95FY64 Pin Assignment

# 2.2 Pin name and functions

The names of input/output pins and their functions are described below.

Table 2.2 Pin names and functions.

| Pin name    | Number  | I/O    | functions                                                         |

|-------------|---------|--------|-------------------------------------------------------------------|

|             | of pins |        |                                                                   |

| P00 to P07  | 8       | I/O    | Port 0 :I/O ports that allow I/O to be selected on a bit basis.   |

| /D0 to D7   |         | I/O    | Data :0 to 7 for data bus                                         |

| P10 to P17  | 8       | I/O    | Port 1 :I/O ports that allow I/O to be selected on a bit basis.   |

| /D8 to D15  |         | I/O    | Data :8 to 15 for data bus                                        |

| P20 to P27  | 8       | I/O    | Port 1 :I/O ports that allow I/O to be selected on a bit basis.   |

| /A16 to A23 |         | Output | Address :16 to 23 for address bus                                 |

| P30         | 1       | I/O    | Port 30 : I/O port                                                |

| /A8         |         | Output | Address : 8 for address bus                                       |

| /BOOT       |         | Input  | Setting pin for Single BOOT mode. Pull-up with external resister. |

| P31 to P37  | 7       | I/O    | Port 3 :I/O ports that allow I/O to be selected on a bit basis.   |

| /A9 to A15  |         | Output | Address :9 to 15 for address bus                                  |

| P40 to P47  | 8       | I/O    | Port 4 :I/O ports that allow I/O to be selected on a bit basis.   |

| /A0 to A7   |         | Output | Address :0 to 7 for address bus                                   |

| P50         | 1       | Output | Port 50 :Output port                                              |

| /RD         |         | Output | Read :Strobe signal for reading external memory.                  |

|             |         |        | (When P5 <p50>=0, P5FC<p50f>=1,</p50f></p50>                      |

|             |         |        | strobe signal output at all read timing.)                         |

| P51         | 1       | Output | Port 51 :Output port                                              |

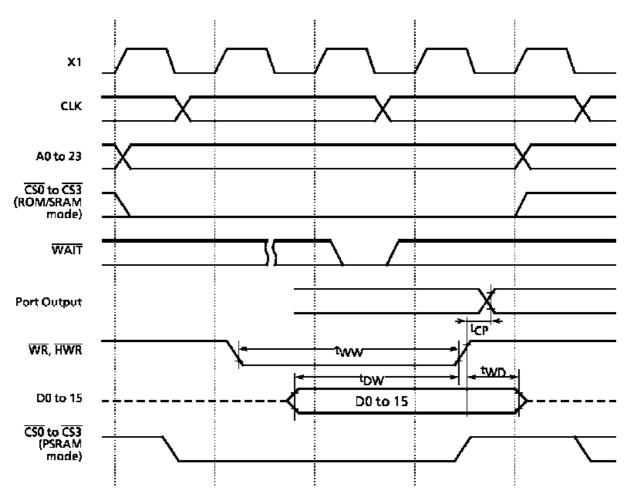

| /WR         |         | Output | Write :Strobe signal for writing data on pins D0 to 7.            |

| P52         | 1       | I/O    | Port 52 :I/O port(with pull-up resistor)                          |

| /HWR        |         | Output | High Write :Strobe signal for writing data on pins D8 to 15.      |

| P53         | 1       | I/O    | Port 53 :I/O port(with pull-up resistor)                          |

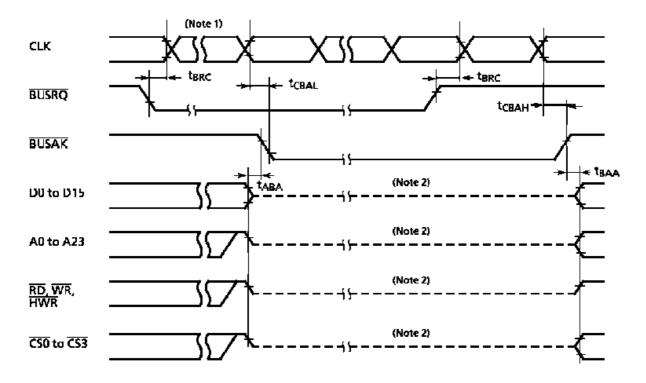

| /BUSRQ      |         | Input  | Bus request :Signal used to request bus release to external bus.  |

| P54         | 1       | I/O    | Port 54 :I/O port(with pull-up resistor)                          |

| /BUSAK      |         | Output | Bus acknowledge :Signal indicating bus release.                   |

| P55         | 1       | I/O    | port 55 : I/O port(with pull-up resistor)                         |

| /WAIT       |         | Input  | Wait :Pin used to request CPU bus wait.                           |

| P56         | 1       | I/O    | Port 56 : I/O port(with pull-up resistor)                         |

| /INT0       |         | Input  | Interrupt request pin 0:Interrupt request pin with                |

|             |         |        | programmable level/rising edge.                                   |

| Pin name     | Number  | I/O    | Table 2.2 Pin names and functions(2/4)         functions         |

|--------------|---------|--------|------------------------------------------------------------------|

| Fill hame    | of pins | 1/0    | Tuncions                                                         |

| P57          | 1       | I/O    | Port 57:I/O port(with pull-up resistor)                          |

| /SCLK2       | 1       | I/O    | Serial Clock I/O 2                                               |

| /CTS2        |         | Input  | Serial data send enable 2(Clear To Send)                         |

| P60          | 1       | Output | Port 60 :Output port                                             |

| / <u>CS0</u> | '       | Output | Chip select 0:Output 0 when address is within specified address. |

| P61          | 1       | Output | Port 61 :Output port                                             |

| /CS1         | I       | Output | Chip select 1:Output 0 when address is within specified address. |

|              | 4       |        |                                                                  |

| P62<br>/CS2  | 1       | Output | Port 62 :Output port                                             |

|              |         | Output | Chip select 2:Output 0 when address is within specified address. |

| P63          | 1       | Output | Port 63 :Output port                                             |

| / <u>CS3</u> |         | Output | Chip select 3:Output 0 when address is within specified address. |

| P70          | 1       | I/O    | Port 70:1/O port                                                 |

| /TI0         |         | Input  | Timer input 0                                                    |

| /INT1        |         | Input  | Interrupt request pin 1:Interrupt request pin with rising edge.  |

| P71          | 1       | I/O    | Port 71:I/O port                                                 |

| /TO1         |         | Output | Timer out 1:Timer 0 or Timer 1 output                            |

| P72          | 1       | I/O    | Port 72:1/O port                                                 |

| /TO3         |         | Output | Timer output 3:Timer 2 or Timer 3 output                         |

| /INT2        |         | Input  | Interrupt request pin 2:Interrupt request pin with rising edge.  |

| P73          | 1       | I/O    | Port 73:I/O port                                                 |

| /TI4         |         | Input  | Timer input 4:Timer 4 input                                      |

| /INT3        |         | Input  | Interrupt request pin 3:Interrupt request pin with rising edge.  |

| P74          | 1       | I/O    | Port 74:I/O port                                                 |

| /TO5         |         | Output | Timer output 5:Timer 4 or Timer 5 output                         |

| P75          | 1       | I/O    | Port 75:I/O port                                                 |

| /TO7         |         | Output | Timer output 7:Timer 6 or Timer 7 output                         |

| /INT4        |         | Input  | Interrupt request pin 4:Interrupt request pin with rising edge.  |

| P80          | 1       | I/O    | Port 80:I/O port(with pull-up resistor)                          |

| /TXD0        |         | Output | Serial send data 0                                               |

| P81          | 1       | I/O    | Port 81:I/O port(with pull-up resistor)                          |

| /RXD0        |         | Input  | Serial receive data 0                                            |

| P82          | 1       | I/O    | Port 82:1/O port(with pull-up resistor)                          |

| /SCLK0       |         | I/O    | Serial Clock I/O 0                                               |

| /CTS0        |         | Input  | Serial data send enable 0(Clear To Send)                         |

| Table 2.2 Pin | names and | functions(2/4) |

|---------------|-----------|----------------|

|---------------|-----------|----------------|

| Table2.2 Pin names and function(3/4) |

|--------------------------------------|

|--------------------------------------|

| Pin name    | Number  | I/O    | function                                                        |

|-------------|---------|--------|-----------------------------------------------------------------|

|             | of pins |        |                                                                 |

| P83         | 1       | I/O    | Port 83:I/O port(with pull-up resistor)                         |

| /TXD1       |         | Output | Serial send data 1                                              |

| P84         | 1       | I/O    | Port 84:I/O port(with pull-up resistor)                         |

| /RXD1       |         | Input  | Serial receive data 1                                           |

| P85         | 1       | I/O    | Port 85:I/O port(with pull-up resistor)                         |

| /SCLK1      |         | I/O    | Serial Clock I/O 1                                              |

| /CTS1       |         | Input  | Serial data send enable 1(Clear To Send)                        |

| P86         | 1       | I/O    | Port 86:I/O port(with pull-up resistor)                         |

| /TXD2       |         | Output | Serial send data 2                                              |

| P87         | 1       | I/O    | Port 87:I/O port(with pull-up resistor)                         |

| /RXD2       |         | Input  | Serial receive data 2                                           |

| P90         | 1       | I/O    | Port 90:I/O port                                                |

| /TI8        |         | Input  | Timer input 8:Timer 8 input                                     |

| /INT5       |         | Input  | Interrupt request pin 5:Interrupt request pin with programmable |

|             |         |        | rising/falling edge.                                            |

| P91         | 1       | I/O    | Port 91:I/O port                                                |

| /TI9        |         | Input  | Timer input 9:Timer 8 input                                     |

| /INT6       |         | Input  | Interrupt request pin 6:Interrupt request pin with rising edge. |

| P92         | 1       | I/O    | Port 92:I/O port                                                |

| /TO8        |         | Output | Timer output 8:Timer 8 output                                   |

| P93         | 1       | I/O    | Port 93:I/O port                                                |

| /TO9        |         | Output | Timer output 9:Timer 8 output                                   |

| P94         | 1       | I/O    | Port 94:I/O port                                                |

| /TIA        |         | Input  | Timer input A :Timer 9 input                                    |

| /INT7       |         | Input  | Interrupt request pin 7:Interrupt request pin with programmable |

|             |         |        | rising/falling edge.                                            |

| P95         | 1       | I/O    | Port 95:I/O port                                                |

| /TIB        |         | Input  | Timer input B :Timer 9 input                                    |

| /INT8       |         | Input  | Interrupt request pin 8:Interrupt request pin with rising edge. |

| P96         | 1       | I/O    | Port 96:I/O port                                                |

| /TOA        |         | Output | Timer output A :Timer 9 output                                  |

| /TOB        |         | Output | Timer output B :Timer 9 output                                  |

| PA0 to PA2  | 3       | Input  | Port A0 to A2:Input port                                        |

| /AN0 to AN2 |         | Input  | Analog input 0 to 2:Input to A/D converter                      |

| PA3         | 1       | Input  | Port A3:Input port                                              |

| /AN3        |         | Input  | Analog input 3:Input to A/D converter                           |

| /ADTRG      |         | Input  | External A/D conversion start trigger input                     |

| Pin name    | Number<br>of pin | I/O          | function                                                                |

|-------------|------------------|--------------|-------------------------------------------------------------------------|

| PA4 to PA7  | 4                | Input        | Port A4 to A7:Input port                                                |

| /AN4 to AN7 |                  | Input        | Analog input 4 to 7:Input to A/D converter                              |

| DAOUT0      | 1                | Output       | D/A output 0:D/A converter 0 analog current output pin                  |

| DAOUT1      | 1                | Output       | D/A output 1:D/A converter 1 analog current output pin                  |

| NMI         | 1                | Input        | Non-maskable interrupt request pin :Interrupt request pin with          |

|             |                  |              | programmable falling/both edge.                                         |

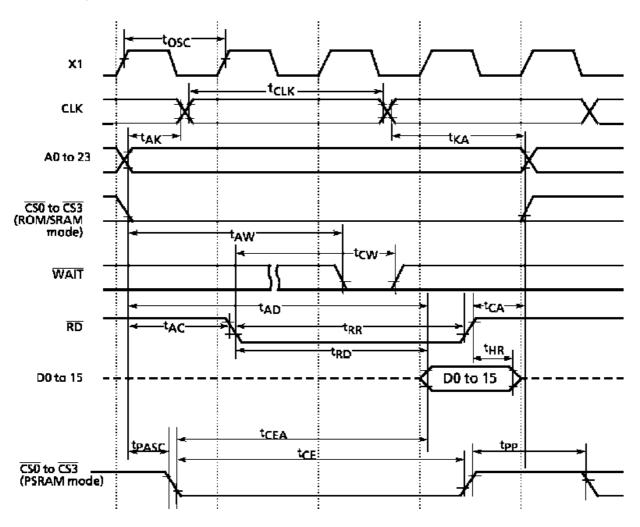

| CLK         | 1                | Output       | Clock output :Outputs external input clock X1 divided by 4.             |

|             |                  |              | Pulled up during reset.                                                 |

| EA          | 1                | Input        | External access :Connect to Vcc when single chip mode.                  |

|             |                  |              | Connect to GND when multi chip mode.                                    |

| AM8/16      | 1                | Input        | Address mode:External data bus width selection pin. Set to 0 when using |

|             |                  |              | fixed 16-bit external bus or dual 8/16-bit external bus.                |

|             |                  |              | Set to 1 with 8-bit external bus fixed.                                 |

| RESET       | 1                | Input        | Reset:Initializes LSI(with pull-up resistor)                            |

| VREFH       | 1                | Input        | Reference voltage input pin for A/D converter (H)                       |

| VREFL       | 1                | Input        | Reference voltage input pin for A/D converter (L)                       |

| AVCC        | 1                |              | A/D and D/A converter power supply pin                                  |

| AVSS        | 1                |              | A/D and D/A converter ground pin (0V)                                   |

| X1 / X2     | 2                | Input/Output | Oscillator connecting pins                                              |

| VCC3        |                  |              | Power supply pin (+5V)                                                  |

| VSS         | 3                |              | Ground pin (0V)                                                         |

| Table 2.2 | Pin | names | and | function | $(\Delta/\Delta)$ |

|-----------|-----|-------|-----|----------|-------------------|

|           |     | names | anu | runction | (                 |

Note 1: Apart from RESET pin, the pull-up resistors can be disconnected by software.

Note 2: Connect all VCC and AVCC pins to power supply and all VSS and AVSS pins to GND.

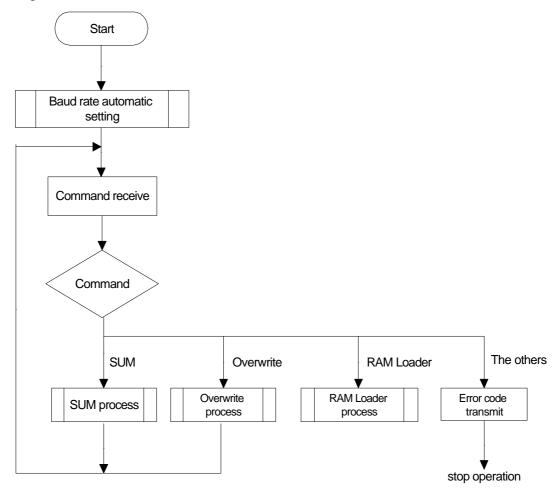

### 3. Operation

The TMP95FY64 is the MCU which includes 256K byte Flash ROM and 8K byte RAM, and has operates as the same way as the TMP95CS64 which includes 64K byte Mask ROM and 2K byte RAM. Please refer to the TMP95CS64 data sheets for the function not described here.

3.1 Operation mode

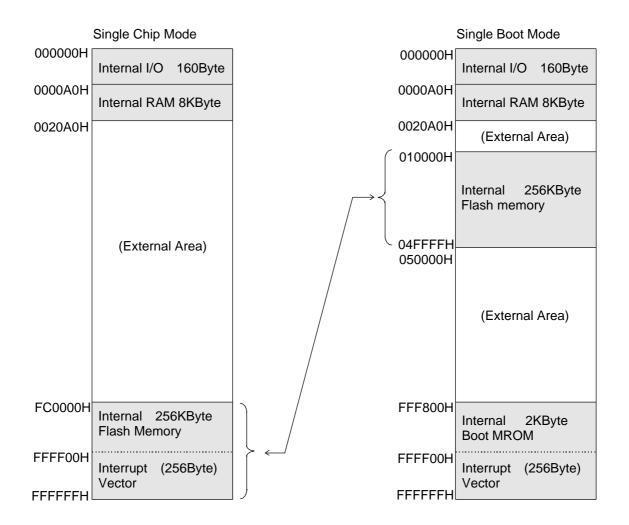

The TMP95FY64 has a single chip mode and a single boot mode. Each mode is set by pin status after reset.

Single Chip Mode: Normal operating mode. The device starts executing program on internal Flash memory after reset.

Single Boot Mode: Internal Flash memory re-programming mode with serial(UART) interface. Internal boot ROM starts and on-board re-write program is executed after reset.

| Operation Mode | mode setting input pin |                |      |    |  |  |  |  |  |

|----------------|------------------------|----------------|------|----|--|--|--|--|--|

|                | RESET                  | CLK            | BOOT | ĒĀ |  |  |  |  |  |

| Single Chip    |                        | Open(Pulled-up | н    |    |  |  |  |  |  |

| Single Boot    |                        | during reset)  | L    | н  |  |  |  |  |  |

#### Table 3.1(1) Operation mode setting table

#### 3.2 Memory Map

The memory map and capacity of built in Flash ROM and RAM are different from TMP95CS64.

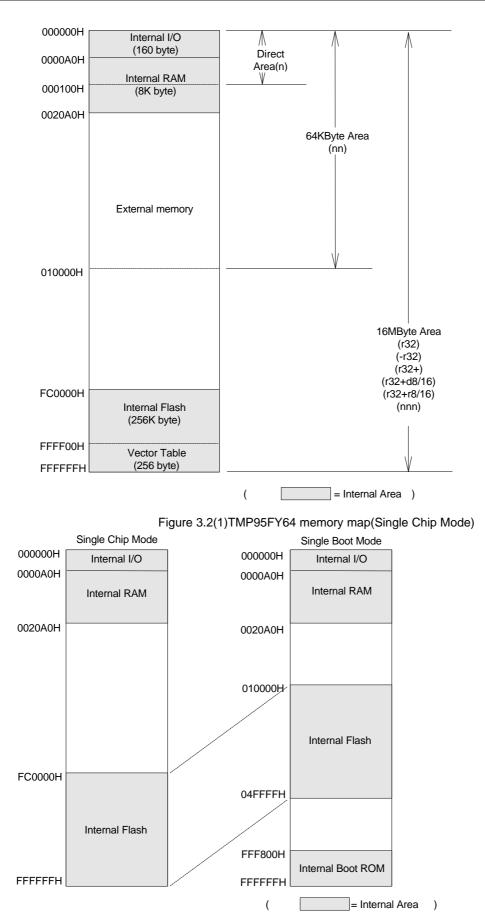

The figure 3.2(1) shows memory map and CPU addressing mode area on single chip mode.

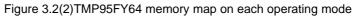

The figure 3.2(2) shows memory map on each operating mode.

# 3.3 Flash memory

The TMP95FY64 has Flash memory which can be erased and Programmed on 5V single voltage. Erase and program of Flash memory are operated by JEDEC standard command. After command input, programming and erasing are automatically operated. The erase function has a chip erase, a block erase, and a plural block erase.

#### Feature:

- Program/Erase voltage

Vcc=5V +/-10%

- Configuration

- 256K x 8 bit/128K x 16 bit(256K byte)

- Function

- Auto-Programming

- Auto-Chip erasing

- Auto-Block erasing

- Auto-Multi-Block erasing

- Data Polling/Toggle bit

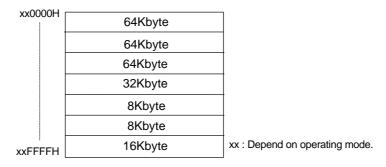

Block Configuration:

- Block erasing architecture

16K byte x 1/8K byte x 2/

32K byte x 1/64K byte x 3

- Mode control

JEDEC Standard command

- Flash memory Type 29F200T

Block protect/ID read are not supported.

Figure 3.3(1)Block configuration of Flash memory

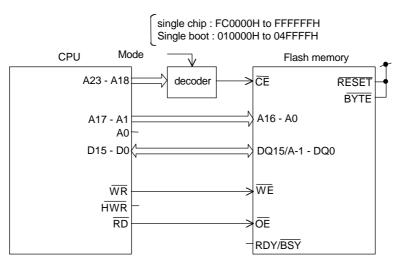

### Internal interface:

Command Sequence :Flash memory access by internal CPU

| command              | Bus<br>cycle | 1st bus<br>write cycle |      | 2nd bus<br>write cycle |      | 3rd bus<br>write cycle |      | 4th bus<br>read/write | cycle | 5th bus<br>write cycle |      | 6th bus<br>write cycle |      |

|----------------------|--------------|------------------------|------|------------------------|------|------------------------|------|-----------------------|-------|------------------------|------|------------------------|------|

| Sequence             |              | Addr.                  | Data | Addr.                  | Data | Addr.                  | Data | Addr.                 | Data  | Addr.                  | Data | Addr.                  | Data |

| read/reset           | 1            | xXXXXH                 | F0H  |                        |      |                        |      |                       |       |                        |      |                        |      |

| read/reset           | 3            | xAAAAH                 | AAH  | x5554H                 | 55H  | xAAAAH                 | F0H  | RA                    | RD    |                        |      |                        |      |

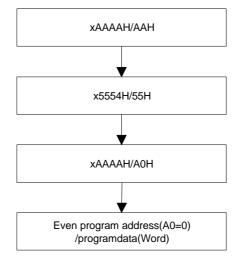

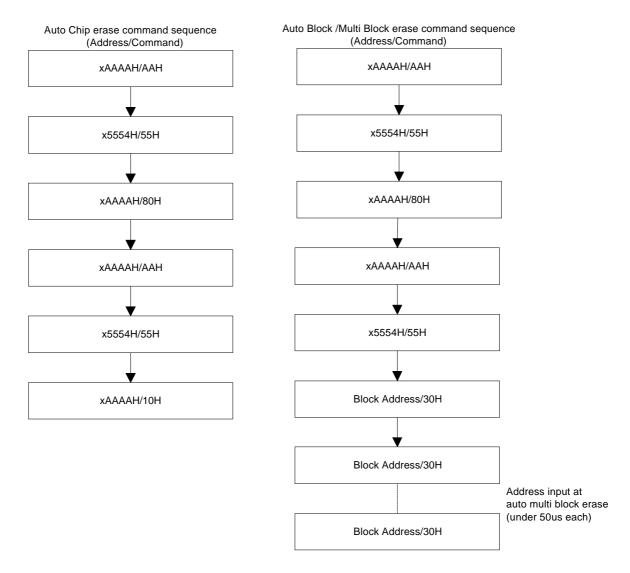

| Auto-<br>program     | 4            | хААААН                 | ААН  | x5554H                 | 55H  | хААААН                 | A0H  | PA                    | PD    |                        |      |                        |      |

| Auto-<br>Chip erase  | 6            | хААААН                 | ААН  | x5554H                 | 55H  | хААААН                 | 80H  | хААААН                | ААН   | x5554H                 | 55H  | хААААН                 | 10H  |

| Auto-<br>Block erase | 6            | хААААН                 | AAH  | x5554H                 | 55H  | хААААН                 | 80H  | хААААН                | AAH   | x5554H                 | 55H  | BA                     | 30H  |

# CPU address

| CPUaddress:A23 to A0 |        |            |                                                       |                                                                           |                                                                                               |                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|--------|------------|-------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A11                  | A10    | A9         | A8                                                    | A7                                                                        | A6                                                                                            | A5                                                              | A4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | A2                                                                                | A1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Х                    | х      | Х          | Х                                                     | х                                                                         | Х                                                                                             | Х                                                               | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Х                                                                                 | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                    | 0      | 1          | 0                                                     | 1                                                                         | 0                                                                                             | 1                                                               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0                    | 1      | 0          | 1                                                     | 0                                                                         | 1                                                                                             | 0                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -                    | X<br>1 | X X<br>1 0 | X         X         X           1         0         1 | x         x         x         x           1         0         1         0 | X         X         X         X         X           1         0         1         0         1 | X     X     X     X     X       1     0     1     0     1     0 | X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X | X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X         X | X     X     X     X     X     X     X       1     0     1     0     1     0     1 | X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X | X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X       X |

F0H,AAH,55H,A0H,80H,10H,30H:command data. Write to DQ7 to DQ0.

RA:Read address

data read by each byte or word.

data write by each even address/word.

RD:Read data output

PA:Program address

PD:Program data input

BA:Block address

Hardware sequence flag :flash memory access by internal CPU

|                     | status                           | DQ7             | DQ6    | DQ5 | DQ3 |

|---------------------|----------------------------------|-----------------|--------|-----|-----|

|                     | Auto-program                     | DQ7<br>inverted | toggle | 0   | 0   |

| executing automatic | Auto-erase(on erasing hold time) | 0               | toggle | 0   | 0   |

| operation.          | Auto-erase                       | 0               | toggle | 0   | 1   |

| time out(automatic  | Auto-program                     | DQ7<br>inverted | toggle | 1   | 1   |

| operation failed)   | Auto-erase                       | 0               | toggle | 1   | 1   |

Note : DQ8 to DQ15, DQ0to DQ2 are Don't care.

Block erase address table :Flash memory access by internal CPU

| Block |     | a   | address | s Address area |     |                   | Size              |          |

|-------|-----|-----|---------|----------------|-----|-------------------|-------------------|----------|

|       | A17 | A16 | A15     | A14            | A13 | Single chip       | Single boot       |          |

| BA0   | L   | L   | х       | х              | х   | FC0000H - FCFFFFH | 010000H - 01FFFFH | 64K byte |

| BA1   | L   | Н   | х       | х              | х   | FD0000H - FDFFFFH | 020000H - 02FFFFH | 64K byte |

| BA2   | Н   | L   | х       | х              | х   | FE0000H - FEFFFFH | 030000H - 03FFFFH | 64K byte |

| BA3   | Н   | Н   | L       | х              | х   | FF0000H - FF7FFFH | 040000H - 047FFFH | 32K byte |

| BA4   | Н   | Н   | Н       | L              | L   | FF8000H - FF9FFFH | 048000H - 049FFFH | 8K byte  |

| BA5   | Н   | Н   | Н       | L              | Н   | FFA000H - FFBFFFH | 04A000H - 04BFFFH | 8K byte  |

| BA6   | Н   | Н   | Н       | Н              | х   | FFC000H - FFFFFFH | 04C000H - 04FFFFH | 16K byte |

#### Basic operation: Flash memory access with internal CPU

This flash memory has two kinds of operation modes of the reading mode and the automatic operation mode roughly dividing. It is possible to move to the automatic operation mode by executing the command sequence in the reading mode. The automatic operation mode inside cannot read the memory data.

#### (1) Reading

When data is read, the flash memory is set in the reading mode. The flash memory becomes a reading mode at immediately after the power supply turning on and the normal termination of an automatic operation. The reset command described later is used for the return to the reading mode from abnormal termination of an automatic operation, and other modes.

(2) Command writing

This flash memory uses the method of the JEDEC standard command control. Writing in the command register is operated by executing the command sequence for the flash memory. The flash memory latches input address and data to the command register, and executes the operation corresponding to the command. The input of the command data uses DQ0-DQ7. The input of DQ8-DQ15 is disregarded. To cancel the command input while inputting the command sequence, the reset command is input. If the reset command is accepted, the flash memory resets the command register, and becomes a reading mode. Moreover, when a wrong command sequence is input, the flash memory resets the command register, and becomes a reading mode.

(3) Reset (reset command)

The flash memory does not return to the reading mode when an automatic operation terminates abnormally. In this case, the flash memory is returned to the reading mode by reading/the reset command. Moreover, when the command input on the way is canceled, the content of the command register can be cleared by reading/the reset command.

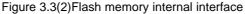

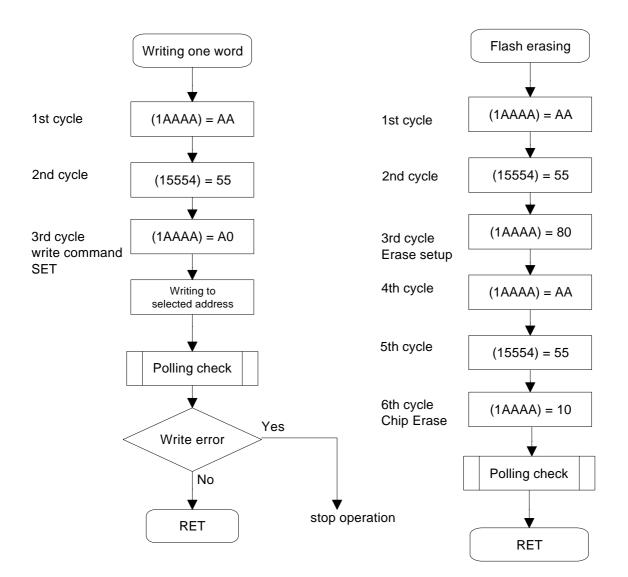

(4) Automatic program

It is necessary to be written in the flash memory every even number address/word byte. The automatic program operation latches the program address/the program data every even number address/word byte at the fourth bus writing cycle of the command cycle. An automatic program begins at time when the program data was latched. When the operation begins, the program and the program verify are automatically operated internally. The operation of an automatic program can be confirmed with the hardware sequence flag. The automatic program operation inside does not accept the input of the command sequence. "1" data cell can be made "0" data by writing in the flash memory. However, "0" data cell cannot be made "1" data. "0" data cell can be made "1" data by the erase operation. When the automatic program operation becomes defective, the flash memory is locked like this mode, and does not return to the reading mode. This state can be confirmed with the hardware sequence flag. It is necessary to reset the flash memory by the reset command. In this case, writing in this address should be defective, and the block which includes this address thereafter not be used.

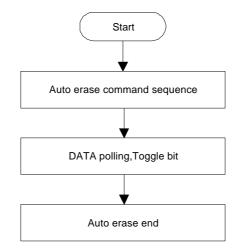

(5) Automatic chip erase

The automatic chip erase operation begins from the sixth bus writing cycle end at the command cycle. When the operation begins, preprogramming all the addresses to "0" data are executed automatically in the flash memory, and continuously, the erase and erase verify are executed. The state of the automatic chip erase operation can be confirmed with the hardware sequence flag. The automatic chip erase operation inside does not accept the command sequence input. When the automatic erase operation becomes defective, the flash memory is locked like this mode, and does not return to the reading mode. This state can be confirmed with the hardware sequence flag. Please reset the flash memory by the reset command. Moreover, the block where the defect occurs cannot be detected. It is necessary to stop the use of the device or not to use a defective block detected by the block erase.

(6) Automatic block erase/automatic multi block erase

The automatic block erase begins later in time of the erase holding from the sixth bus writing cycle end at the

command cycle. When the operation begins, preprogramming all the addresses in selected blocks to "0" data are executed automatically in the flash memory, and continuously, the erase and erase verify are executed. When do the erasure of the plural block, each block address and the automatic block erase command are input in the erase hold time repeating the sixth bus writing cycle. When the command sequences other than the automatic block erase are input during the erase hold time, the flash memory is reset, and becomes a reading mode. The erase hold time is 50us. The counting for the erase hold time is begun at each end of the sixth bus writing cycle. The state of the automatic block erase operation can be confirmed with the hardware sequence flag. The input of other command sequences is not accepted during the automatic block erase. When the automatic block erase operation becomes defective, the flash memory is locked like this mode, and does not return to the reading mode. This state can be confirmed with the hardware sequence flag. Please reset the flash memory by the reset command. When the plural block is selected, the block where the defect occurs cannot be detected. The use of the device is discontinued or it is necessary to do the block erasure individually, specify a defective block, and not use a defective block.

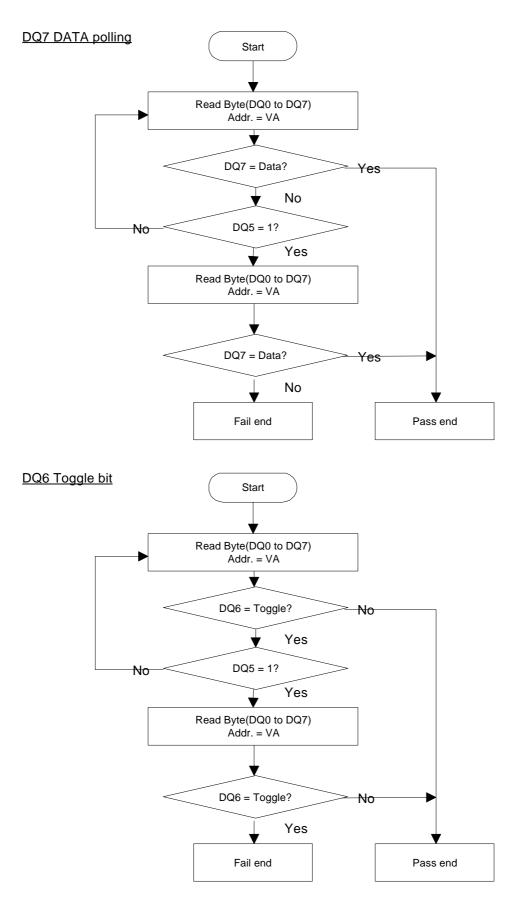

(7) Hardware sequence flag

The automatic operation execution of the flash memory can be confirmed with the hardware sequence flag. Data can be read while operating automatically according to the same timing as the reading mode. The flash memory automatically returns to the reading mode when an automatic operation is ended. The state of the operation can be confirmed during the automatic operation execution with the hardware sequence flag. Moreover, the automatic operation end can be confirmed by the read data's having matched with than the cell data.

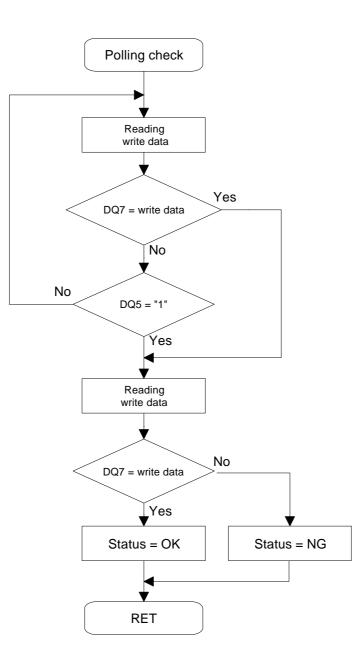

#### 1)DQ7 (DATA polling)

An automatic operation of the flash memory can be confirmed by the DATA polling function. The output of the DATA polling begins from end of the last bus writing cycle in the automatic operation command sequence. The automatic program operation inside outputs the reversing data of the data written in DQ7, and after an automatic program ends, outputs the cell data of DQ7. It is possible to identify the state of operation by reading DQ7. The automatic erase operation inside outputs "0" from DQ7, and after this operation ends, outputs "1" (cell data). Moreover, when the result of an automatic operation is defective, DQ7 outputs the automatic operation data continuously. When data is read, it is necessary to give a written address or an arbitrary block address under the erasure because the flash memory releases the address latch when the operation ends.

#### 2)DQ6 (toggle bit)

In addition to the DATA polling, The toggle bit output function is provided as a method of recognizing the state of an automatic operation. The output of the toggle begins from end of the last bus writing cycle in the automatic operation command sequence. However, the output of the toggle in the automatic block erase operation begins after end of the erase hold time. This toggle outputs to DQ6, and outputs the data of "1" and "0" alternately every reading cycle. When an automatic operation ends, DQ6 stops the output of the toggle, and outputs the cell data. When the result of an automatic operation is defective, DQ6 continues the toggle output.

#### 3)DQ5 (internal timer excess)

When an automatic operation is normally done, the flash memory outputs "0" to DQ5. The output of DQ5 changes into "1" if the time for which an automatic operation specify in the flash memory is exceeded. This has the possibility that it is shown that an automatic operation did not end normally, and the flash memory is defective. However, when the "1" data is written in the "0" data cell, DQ5 outputs "1", and the flash memory is judged to be defective. ("1" data cell can be made "0" data by writing in the flash memory. However, "0" data cell cannot be made "1" data. ) In this case, DQ5 does not show the defect of the flash memory. It is shown that use is not correct. The flash memory is locked, and does not return to the reading mode when an

automatic operation does not end normally. Please reset the flash memory by the reset command. 4)DQ3 (block erase timer)

The automatic block erase begins later in time of the erase holding(50us) from the sixth bus writing cycle end at the command cycle. The flash memory outputs "0" to DQ3 during the block erase hold time, and outputs "1" to DQ3 When the erasure begins. When the erase block is added, inputs the additional block erase command during the block erase hold time for the previous block erase. The block erase hold time is reset whenever the block erase command is input, and the flash memory counts a hold time from the beginning. When the result of an automatic operation is defective, DQ3 outputs "1".

5)RDY/BSY (Ready/Busy)

\* This function cannot be used because of no connection with internal CPU.

(8) Flash memory rewriting with internal CPU

The flash memory rewriting with internal CPU is done with the above-mentioned command sequence and a hardware sequence flag. However, the memory data is not able to read from the internal flash memory during the automatic operation mode. It is necessary to execute the rewriting program on the outside area of the flash memory. There are two methods of flash memory rewriting with internal CPU. It is a method of using the single boot mode prepared beforehand, and a method of using original user's protocol on the single chip mode (user boot).

1) Single boot:

It is a method of rewriting the flash memory by built-in boot ROM program by starting the microcomputer in the single boot mode. In this mode, the built-in boot ROM is mapped in the area where contains the vector table of interrupt, and the boot ROM program is executed. Moreover, the flash memory is mapped in the different area from the boot ROM. The boot ROM program operates receiving the rewrite data by the serial transfer, and rewriting the flash memory. Single boot is done with the interrupt prohibited. The non maskable interrupt(NMI etc.) also must to be prohibited. Please refer to 3.4 single boot mode for details.

2) User boot:

It is a method of using the original user's flash memory rewriting program. This mode is operated in the single chip mode (usual operation mode). This mode should execute the flash memory rewriting program on the different address space from the flash memory area. Moreover, it is necessary to prohibit all the interrupt including the non maskable interrupt as same as single boot. The flash memory rewriting program is prepared beforehand including the data taking routine for rewriting and the flash memory rewriting routine . In a main program, changing from the usual operation to the flash memory rewriting operation. The flash memory rewriting program which was prepared is transferred to outside the flash memory area and executing. For example, the flash memory rewriting program is transferred from on the flash memory to built-in RAM and executing. Preparing it in an external memory and executing.

99/01/19 11:43

Auto program

Auto program command sequence(address/command)

#### Auto erase

VA :Programmed address at auto program. Flash memory address at auto chip erase. Selected block address at auto block erase.

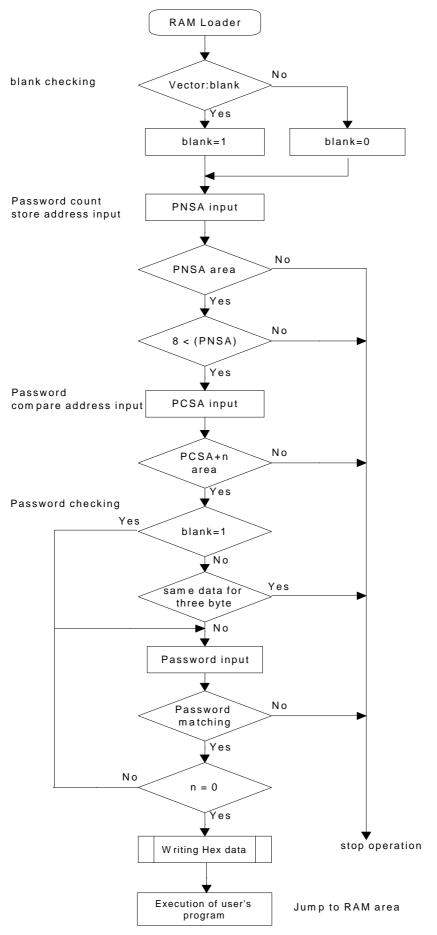

#### 3.4 Single Boot Mode

#### (1) Overview

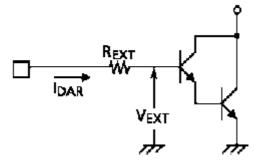

TMP95FY64 has the single boot mode as an operation mode to do the on board programming. The Boot ROM is mapped on the memory space when setting in the single boot mode. The Boot ROM is a mask ROM which does the flash memory rewriting on board. The on board programming is executed by connecting SIO of TMP95FY64 (channel 2) and writing TOOL (controller), and sending the command from the controller side.

Moreover, the loader function to transfer the program data from the outside to built-in RAM of the TMP95FY64 is provided in the boot program built into boot ROM.

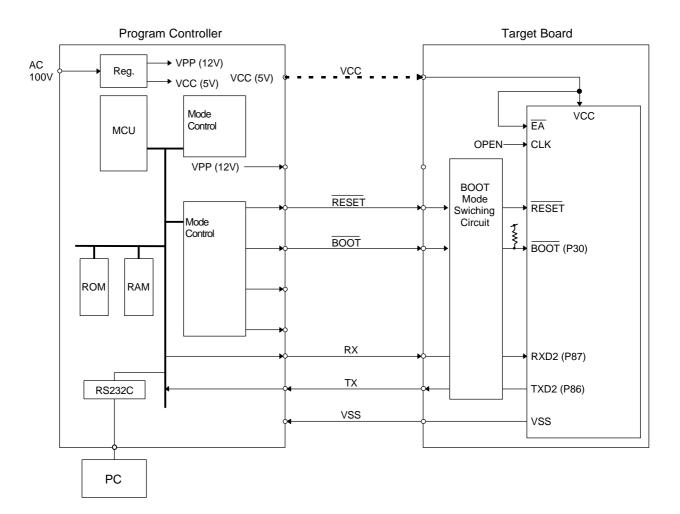

Figure 3.4(1) shows the example of connecting the writing controller and the target board.

Figure 3.4(1) Example of On-Board Programming Connection

Note 1: The AF200(advanced on-board flash microcomputer programmer) made by Yokogawa Digital Computer (YDC) supports on-board programming for this device. Refer to the AF200 manual for details.

Contact: Yokogawa Digital Computer Corporation

Micom-System Business Group

Instrument Business Division

tel : 81-423-33-6224

# (2) Mode setting

To execute on-board programming, start the TMP95FY64 in Single Boot mode as follows:

| CLK       | = | OPEN |

|-----------|---|------|

| EA        | = | н    |

| BOOT(P30) | = | L_   |

| RESET     | = | 1    |

Setting the CLK, EA, and BOOT pins as shown above, and inputting a rising edge to RESET pin starts the TMP95FY64 in Single Boot Mode.

#### (3) Memory map

Figure 3.4(2) shows the comparison of memory maps of the single chip mode and the single boot mode. The Internal flash memory is mapped from 10000H to 4FFFFH for the single boot mode. Moreover, the boot ROM(Mask ROM) is mapped from FFF800H to FFFFFFH.

Figure 3.4(2) Comparison of Memory Maps

### (4) Interface specifications

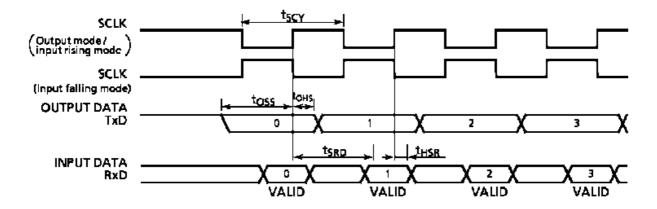

The SIO communication format in the single boot mode is shown below.

It is necessary to set the format of the communication on the writing controller side similarly to execute the on board programming.

It is possible to change as shown in Table 3.4(1) though the baud rate is initialize 9600bps.

| Communication channel | : SIO channel 2                        |

|-----------------------|----------------------------------------|

| Serial transfer mode  | : UART mode, full-duplex communication |

| Data length           | : 8 bits                               |

| Parity bit            | : None                                 |

| Stop bit              | : 1 bit                                |

| Initial Baud rate     | : 9600bps                              |

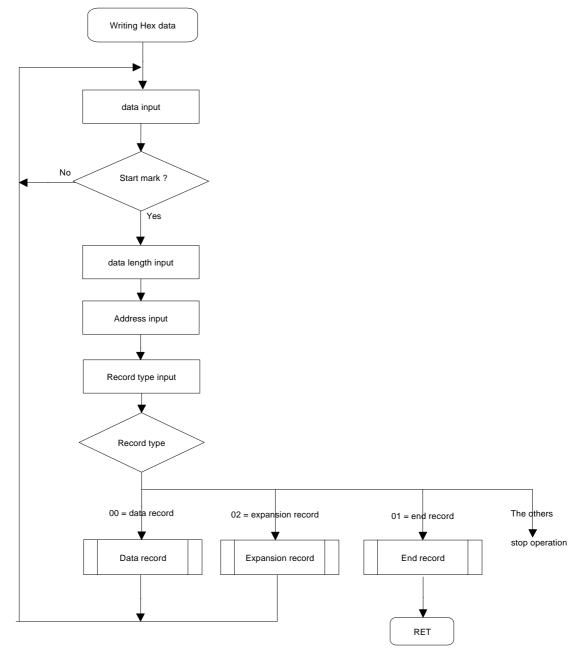

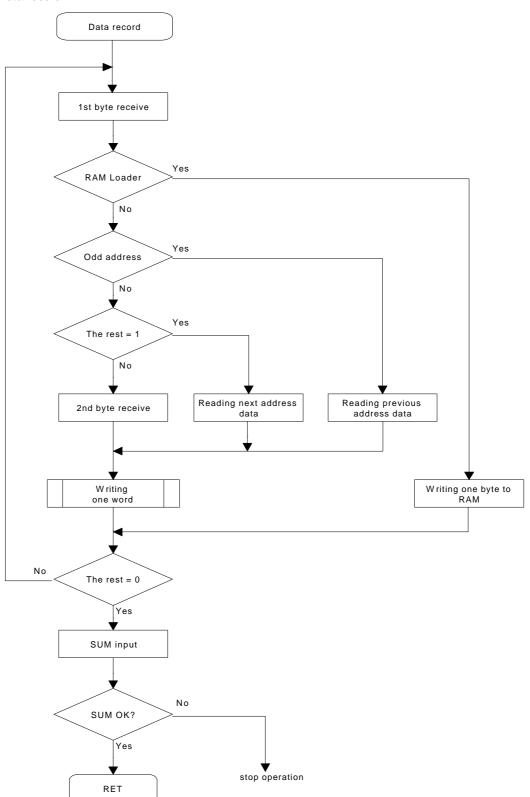

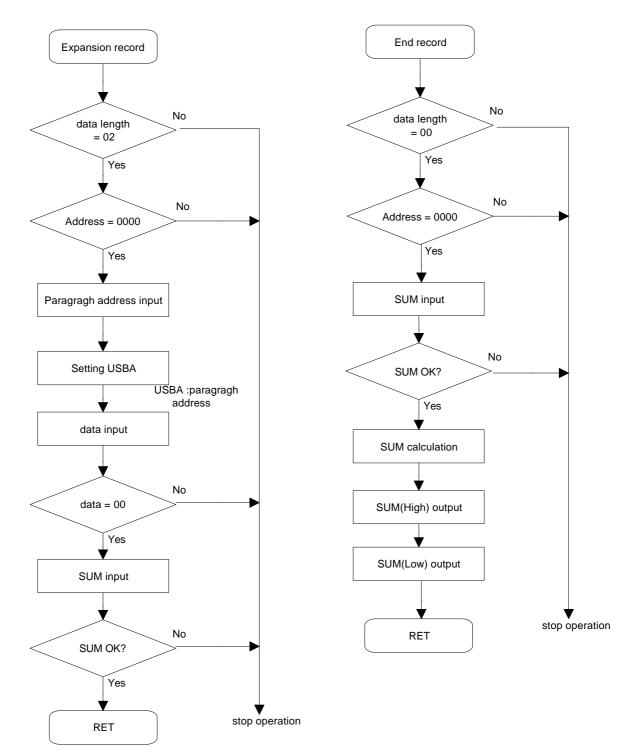

(5) Data transfer format

Table 3.4(1) to (5) show the baud rate change data, the operation command, and the data transfer format respectively.

Please read together with the following "Boot program operation explanation".

Table 3.4(1) Baud rate change data

| Baud rate change data | 04H   | 05H   | 06H   | 07H   | 0AH   | 18H   | 28H  |

|-----------------------|-------|-------|-------|-------|-------|-------|------|

| Baud rate(bps)        | 76800 | 62500 | 57600 | 38400 | 31250 | 19200 | 9600 |

Note : The AF200 supports only for 9600, 19200, 31250 and 62500 bps.

#### Operating frequency and baud rate in Single Boot mode. : TMP95FY64

| Reference ba   | ud rate(bps)   | 9600           |       | 19    | 200   | 312   | 250   | 38-   | 400   | 576   | 600   | 62    | 500   | 768   | 300   |

|----------------|----------------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Baud rate cl   | hange data     | 28h            |       | 18    | 3h    | 0/    | Ah 🛛  | 0     | 7h    | 06    | Sh    | 05    | ōh    | 04    | 4h    |

| Ref. Xtal(MHz) | Area(MHz)      | Baud rate(bps) | (%)   | (bps) | (%)   |

| 2.4576         | 2.44 to 2.48   | 9600           | 0     | 19200 | 0     |       |       | 38400 | 0     |       |       |       |       |       |       |

| 3              | 2.97 to 3.03   | 9375           | -2.34 |       |       |       |       |       |       |       |       |       |       |       |       |

| 3.6864         | 3.64 to 3.74   | 9600           | 0     | 19200 | 0     |       |       |       |       | 57600 | 0     |       |       |       |       |

| 4.9152         | 4.85 to 5.07   | 9600           | 0     | 19200 | 0     |       |       | 38400 | 0     |       |       |       |       | 76800 | 0     |

| 5              |                | 9766           | +1.73 | 19531 | +1.72 |       |       | 39063 | +1.73 |       |       |       |       | 78125 | +1.73 |

| 6              | 5.91 to 6.23   | 9375           | -2.34 | 18750 | -2.34 | 31250 | 0     |       |       |       |       |       |       |       |       |

| 6.144          |                | 9600           | 0     | 19200 | 0     | 32000 | +2.4  |       |       |       |       |       |       |       |       |

| 7.3728         | 7.26 to 7.48   | 9600           | 0     | 19200 | 0     |       |       | 38400 | 0     | 57600 | 0     |       |       |       |       |

| 8              | 7.84 to 8.16   | 9615           | +0.16 |       |       | 31250 | 0     |       |       |       |       | 62500 | 0     |       |       |

| 9.8304         | 9.64 to 10.20  | 9600           | 0     | 19200 | 0     | 30720 | -1.7  | 38400 | 0     |       |       |       |       | 76800 | 0     |

| 10             |                | 9766           | +1.73 | 19531 | +1.72 | 31250 | 0     | 39063 | +1.73 |       |       |       |       | 78125 | +1.73 |

| 12             | 11.76 to 12.75 | 9375           | -2.34 | 18750 | -2.34 | 31250 | 0     | 37500 | -2.34 |       |       | 62500 | 0     |       |       |

| 12.288         |                | 9600           | 0     | 19200 | 0     | 32000 | +2.4  | 38400 | 0     |       |       | 64000 | +2.4  |       |       |

| 12.5           |                | 9766           | +1.73 | 19531 | +1.72 | 32552 | +4.17 | 39063 | +1.73 |       |       | 65104 | +4.17 |       |       |

| 14.7456        | 14.46 to 15.04 | 9600           | 0     | 19200 | 0     | 32914 | +5.3  | 38400 | 0     | 57600 | 0     |       |       | 76800 | 0     |

| 16             | 15.68 to 16.32 | 9615           | +0.16 | 19231 | +0.16 | 31250 | 0     |       |       |       |       | 62500 | 0     |       |       |

| 18             | 17.64 to 18.36 | 9375           | -2.34 | 18750 | -2.34 | 31250 | 0     |       |       | 56250 | -2.34 |       |       |       |       |

| 19.6608        | 19.27 to 20.40 | 9600           | 0     | 19200 | 0     | 30720 | -1.7  | 38400 | 0     |       |       | 61440 | -1.7  | 76800 | 0     |

| 20             |                | 9766           | +1.73 | 19531 | +1.72 | 31250 | 0     | 39063 | +1.73 |       |       | 62500 | 0     | 78125 | +1.73 |

| 21.18          | 20.76 to 22.56 | 9193           | -4.24 | 18385 | -4.24 | 30085 | -3.73 | 36771 | -4.24 | 55156 | -4.24 |       |       |       |       |

| 22.1184        |                | 9600           | 0     | 19200 | 0     | 31418 | +0.54 | 38400 | 0     | 57600 | 0     |       |       |       |       |

| 24.5760        | 24.09 to 25.50 | 9600           | 0     | 19200 | 0     | 32000 | +2.4  | 38400 | 0     | 54857 | -4.76 | 64000 | +2.4  | 76800 | 0     |

| 25             |                | 9766           | +1.73 | 19531 | +1.72 | 32552 | 4.17  | 39063 | 1.73  | 55804 | -3.12 | 65104 | +4.17 | 78125 | +1.73 |

| 26.88          | 26.35 to 27.54 | 9545           | -0.57 | 19091 | -0.57 | 30000 | -4    | 38182 | -0.57 |       |       |       |       |       |       |

| 27             |                | 9588           | -0.13 | 19176 | -0.13 | 30134 | -3.57 | 38352 | -0.13 |       |       |       |       |       |       |

| 32             | 31.36 to 32.64 | 9615           | +0.16 | 19231 | +0.16 | 31250 | 0     | 38462 | +0.16 | 55556 | -3.55 | 62500 | 0     |       |       |

Reference frequency : High speed oscillator frequency supported in Single boot mode.

When the Single boot mode is used for programming Flash memory, each of reference frequency should be used.

Area :Clock frequency area detected for reference frequency. The Single boot would not be executed at the others frequency.

Note : The Auto-detection of MCU operating frequency will be normally done when the total error between transmit baud rate(9600bps) of

program controller, oscillator frequency and detecting timing of matching data is under +/-3%.

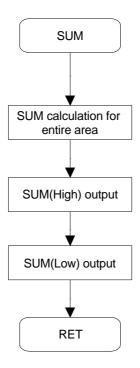

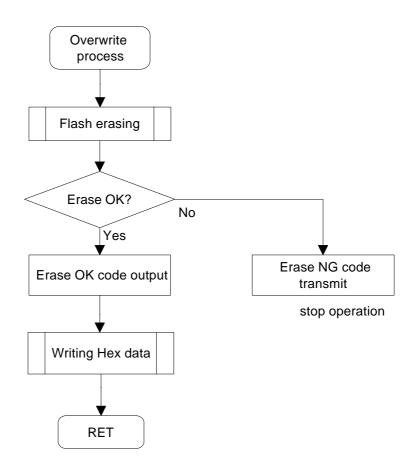

#### Table 3.4(2) Operating command data

| Operation command data | Operating mode         |

|------------------------|------------------------|

| 30H                    | Flash memory Overwrite |

| 60H                    | RAM Loader             |

| 90H                    | Flash memory SUM       |

|             | Byte<br>number          | Tool to TMP95FY64 transfer                 | Baud rate                              | TMP95FY64 to Tool transfer                                                                                                |

|-------------|-------------------------|--------------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| BOOT<br>ROM | Byte 1<br>Byte 2        | Matching data(5AH)<br>-                    | 9600bps<br>9600bps                     | <ul> <li>- (baud rate automatic setting)</li> <li>OK: Echo back data(5AH)</li> <li>NG: Does not send any data.</li> </ul> |

|             | Byte 3<br>Byte 4        | Baud rate change data<br>- (Table3.4(1))   | 9600bps<br>9600bps                     | -<br>OK: Echo back data<br>NG: A1H×3,A2H×3,A3H×3 *1                                                                       |

|             | Byte5<br>Byte 6         | Operating command data<br>(30H)<br>-       | Changed baud rate<br>Changed baud rate | -<br>OK: Echo back data (30H)<br>NG: A1H×3,A2H×3,A3H×3,63H×3                                                              |

|             | Byte 7                  | Changed baud rate<br>-                     | Changed baud rate                      | OK: C1H<br>NG: 64H×3                                                                                                      |

|             | Byte 8<br>:<br>Byte n-2 | Expanded<br>Intel Hex format (binary) *2   | Changed baud rate                      | -                                                                                                                         |