# D Series Tapped High Speed Charge-Coupled Photodiode Array

#### Introduction

EG&G Reticon's RL1282D, RL1284D and RL1288D are ultrahigh-speed, self-scanned charge-coupled linear arrays with video output taps every 128 diodes. The RL1282D has two sections and a resolution of 256, the RL1284D has four sections and a resolution of 512, and the RL1288D has eight sections with 1024 resolution.

Applications for these arrays include optical character recognition, high-speed document scanning, pattern recognition, noncontact measurement, or any process requiring a high-speed linear array.

#### **Key Features**

- · 256, 512 or 1024 elements

- 18 μm x 18 μm picture elements

- Low power requirements

- +15 and -5V supplies

- On-chip preamplifier

- Wide dynamic range

- Low noise equivalent exposure

- · Video sampling rates up to 15 MHz per output channel

- Effective data rates to 240 MHz

- 4.2 μs line scan time

- · Wide spectral response, near UV to near IR

- Antiblooming circuitry

- Line reset feature

# **Functional Description**

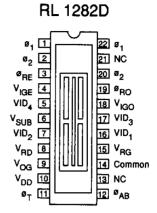

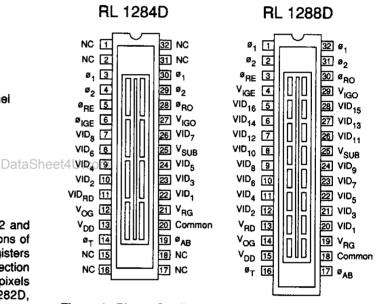

The RL1282D, RL1284D, and RL1288D have 256, 512 and 1024 contiguous diodes respectively, divided into sections of 128 pixels. Each block of 128 pixels has two shift registers for readout, one for odd-numbered pixels within a section (odd video channel), the other for even-numbered pixels within a section (even video channel). The RL1282D, RL1284D, and RL1288D have, respectively, 4, 8, and 16 CCD analog shift registers and the same number of video output lines. Each video output has a preamplifier and can obtain pixel rates up to 15 MHz. Pin configurations are shown in Figure 1. Figure 2 is a simplified schematic diagram.

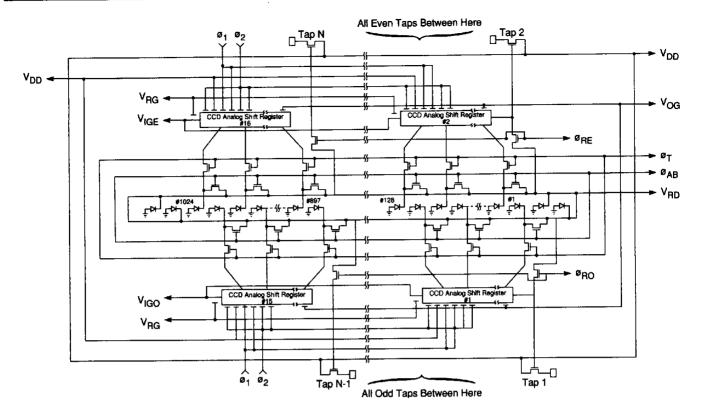

The sensing elements consist of a row of diffused p-n junction photodiodes spaced on 18  $\mu m$  centers and interdigitated into a sensing aperture 18  $\mu m$  wide. Figure 3 gives the aperture response function and sensor geometry where a=11  $\mu m$  photodiode diffusion width, b=18  $\mu m$  center-to-center spacing, and c=18  $\mu m$  aperture width. Light incident on the sensing aperture generates photocurrent which is integrated and stored as a charge on the capacitance of each of the photodiodes. If the charge accumulated on any diode exceeds a saturation value, the antiblooming gates  $\emptyset_{AB}$  turn on, shunting the excess to the reset drain  $V_{RD}$  (see Figure 2) thus reducing blooming effects.

Figure 1. Pinout Configurations

At the end of each integration period, the charges on all the diodes are simultaneously switched through transfer gates,  $\varnothing_T$ , into CCD analog shift registers for readout. The photodiodes of each 128 element section are divided, with the 64 odd diodes switched into one register and the 64 even diodes into the other. Immediately after this parallel line transfer, a new integration period begins.

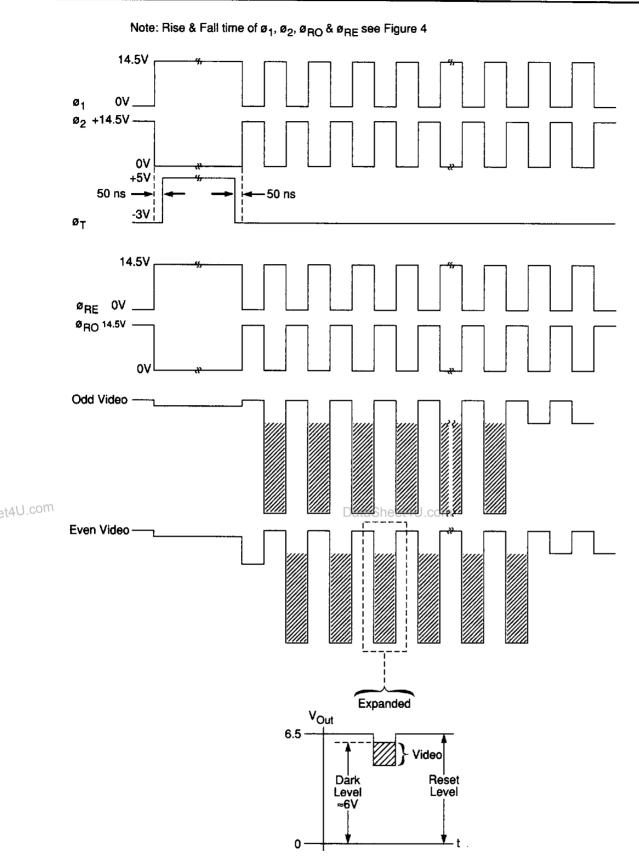

Readout for each block is accomplished by clocking the CCD shift registers so that the charge packets are delivered sequentially into two on-chip charge-detection circuits (refer to Figure 5 for timing). The registers deliver the charge packets alternately, allowing the inactive charge detector to be reset to a fixed level of ØRE or ØRO while the opposite detector is active. The outputs of the two detectors may then be multiplexed off-chip to obtain a stepwise-continuous video signal.

DataShe

27

Figure 2. Schematic Diagram

Figure 3. Sensor Geometry and Idealized Aperture Response

Figure 4. Two-Phase Clocks

## Operation

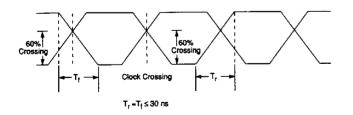

The D Series Tapped arrays require two clock phases, ø<sub>1</sub> and ø<sub>2</sub>, a transfer gate pulse, ø<sub>T</sub>, and several bias inputs (all voltage references are to common or ground level). The ø<sub>1</sub> tashed and ø<sub>2</sub> clock waveforms should swing between 0 and +15V. The two-phase clock waveforms are depicted in Figure 4 with waveforms crossing at the 60% amplitude level. The clock crossings must occur at or above 60% (see Figure 4). The ø<sub>1</sub> and ø<sub>2</sub> clock crossings must occur at or above 60% (see Figure 4). Likewise, the ø<sub>1</sub>/ø<sub>RO</sub> and ø<sub>2</sub>/ø<sub>RE</sub> clock crossings must occur at or below 50% for maximum performance. For high-speed operation, the rise and fall should be less than 30 nanoseconds, with no over- or under-shooting on the clock edges.

The transfer pulse,  $\varnothing_T$ , should swing between -3 and +5V and have a width greater than 0.5 µsec. In order to transfer the charge from the photodiodes into the CCD register, the  $\varnothing_1$  clock must remain high during the blanking and transfer interval, as shown in Figure 5. This same figure also shows  $\varnothing_{RE}$ , the even reset clock, and its relationship to  $\varnothing_1$  and  $\varnothing_2$  clocks, as well as the odd and even video outputs. The output reset clock,  $\varnothing_{RO}$ , can be derived from  $\varnothing_2$  and the even reset clock,  $\varnothing_{RE}$ , can be derived from  $\varnothing_1$ , provided the clock crossing requirements described above are met.

A bias charge level is required in the CCD registers to obtain operation. This charge is supplied by biasing the  $V_{IGE}$  and  $V_{IGO}$  inputs to the registers with a positive voltage which is nominally set at 8.5V. Also, in order to balance the dc output levels of the two registers, one input level can be adjusted relative to the other. Resistive dividers (potentiometers) may be used since very little current is required.

28

Figure 5. Timing Relationship of the Array's Clocks and Output

29

DataShee

Figure 6. High-speed Video Output Buffer

The optimum output gate bias voltage,  $V_{OG}$ , is between 4V and 8.5V and varies from device to device. Since the output gate draws negligible current, it may be biased using a simple resistive voltage divider.

The substrate,  $V_{SUB}$ , is held at -5V, the common reference and the antiblooming gate,  $\varnothing_{AB}$  (if not used), are at ground, and the output amplifier drain,  $V_{DD}$ , is at +15V. The  $V_{RG}$  gate is used for test purposes at the factory and is normally set at +10V during operation.

The reset drain,  $V_{RD}$ , normally is set to 2.5V below  $V_{DD}$  (see Table 3). In some applications, it may be desirable to define an integration period shorter than the readout time. This may be accomplished by resetting the diodes with the antiblooming gate. At the desired reset time,  $\emptyset_{AB}$  is pulsed to +3.5V nominal (2.5 - 4.5V) for at least one  $\mu$ sec and then back to ground. The integration period is then the time between the trailing edge of the  $\emptyset_{AB}$  pulse and the trailing edge of the next  $\emptyset_T$  pulse. At low voltages (typically 2-3V),  $\emptyset_{AB}$  drains off saturation charges. This can be used to eliminate blooming effects. With the output at saturation,  $\emptyset_{AB}$  is increased from ground until the output voltage begins to decrease. At this point, charge in excess of saturation is shunted to  $V_{RD}$ .

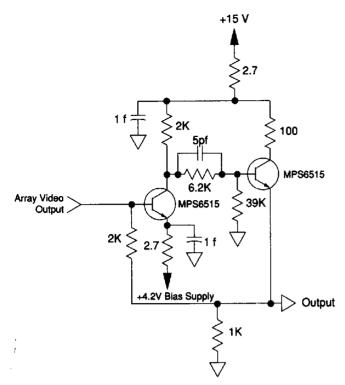

A suitable high-speed video output circuit is shown in Figure 6. This circuit is preferable to a  $3K\Omega$  load resistor because it reduces the current demand while maintaining speed capabilities.

#### **Performance**

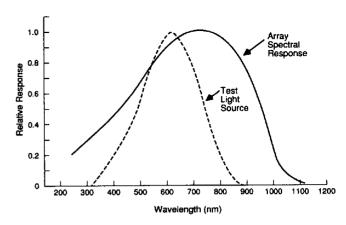

Spectral response of the D Series Tapped arrays is similar to that of other high-quality silicon photodetectors, covering the

Figure 7. Relative Spectral Response as a Function of Wavelength

range from near UV to near IR. A quartz window is standard. Relative spectral response is shown as a function of wavelength in Figure 7.

As most applications for these devices (OCR, machine vision, etc.) use visible light, the responsivity and uniformity of response are specified using a source with the spectral distribution shown by the dotted line in Figure 7. This spectral distribution is produced by filtering a 2870°K tungsten source with a Fish-Schurman HA-11 heat-absorbing 1 mm thick filter.

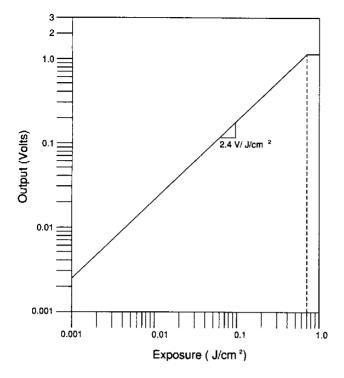

Transfer characteristics showing the saturation output voltage at a Sherican be seen in Figure 8. Since Reticon line scanners operate in the charge-storage mode, the charge output of each diode (below saturation) is proportional to exposure, i.e., the irradiance or light intensity multiplied by the integration time or the time interval between successive transfer pulses.

There is a trade-off between scanning speed and the required light intensity. Light intensity (watts), needed to saturate a pixel at a particular integration time, can be obtained by dividing saturation exposure by integration time. Longer integration times may be used to detect lower light levels. However, this approach is ultimately limited by dark leakage current which is integrated along with the photocurrent.

Video Output waveforms shown in Figure 5 typify video output performance as measured across a 3K load resistor. The rise and fall times are relative since they are affected by capacitive loading, including oscilloscope probe capacitance. For data rates greater than 3 MHz, an output circuit such as Figure 6 is recommended and video rise and fall times of 50 ns or less are typical.

#### Circuits

A complete evaluation circuit board is available for the D Series Tapped arrays (RL1284 and RL1288, only) and is recommended for first-time evaluation. The RC0716 Board contains all required drive circuitry and has buffered outputs capable of speeds to 10 MHz/tap.

et4U.com

30

Figure 8. Typical Transfer Characteristic

**Table 1. Absolute Maximum Ratings** (Above Which Useful Life May be Impaired)

Table 2. Typical Clock Capacitance \*

| Clock          | Capacitance (pF) |        |        |  |  |

|----------------|------------------|--------|--------|--|--|

|                | RL1282           | RL1284 | RL1288 |  |  |

| ø <sub>1</sub> | 65               | 137    | 186    |  |  |

| Ø2             | 64               | 143    | 183    |  |  |

| ø <sub>2</sub> | 65               | 155    | 187    |  |  |

| ø <sub>1</sub> | 65               | 120    | 194    |  |  |

| ø <sub>T</sub> | 19               | 42     | 56     |  |  |

| ØRO            | 7                | 11     | 18     |  |  |

| ØAB            | 19               | 19     | 19     |  |  |

| ØRE            | 9                | 13     | 19     |  |  |

Measured with 10V applied to the terminal

Table 3. Drive and Voltage Requirements <sup>1</sup>

| Sym                             | Parameter                     |      | Min    | Тур       | Max   | Units |

|---------------------------------|-------------------------------|------|--------|-----------|-------|-------|

| V <sub>RD</sub>                 | Reset drain bias <sup>2</sup> |      | DataSh | eet4U_com | 13    | V     |

| V <sub>DD</sub>                 | Output drain bias             |      | 14.5   | 1.5       | 15.5  | l v   |

| Vog                             | Output gate bias 3            |      | 4.0    | 6.5       | 8.5   | l v   |

| V <sub>IG</sub>                 | Input gate bias 4             |      | 6      | 7.8       | 9     | ĺ     |

| ØAB                             | Antiblooming gate 5           |      | -      | 0         | _     | V     |

| V <sub>SUB</sub>                | Substrate bias                |      | -5.25  | -5        | -4.75 | l v   |

| Ø <sub>1</sub> , Ø <sub>2</sub> | CCD transport clocks          | High | 14.5   | 15        | 15.5  | V     |

| -                               |                               | Low  | -0.3   | 0         | +0.5  | l v   |

| ØΤ                              | Transfer clock High           |      | 5      | 7         | 15    | ĺ     |

| '                               | Low                           |      | -5     | -3        | -2    | l v   |

| ØRE, ØRO                        | Reset - High                  |      | 14.5   | 15        | 15.5  | l v   |

| ØRE, ØRO                        | Clocks - Low                  |      | -0.3   | 0         | +0.5  | V     |

| V <sub>RG</sub>                 | Receive gate                  |      | 9.5    | 10        | 10.5  | V     |

| fclock                          | Video sampling rate 6         |      |        | -         | 15    | MH:   |

#### Notes:

- All voltage referenced to COMMON. Use typical values for best performance.

- <sup>2</sup> Optimum device performance is achieved when  $V_{RD}$  is set to 2.5V below  $V_{DD}$ .

- 3 The optimum bias level for V<sub>OG</sub> varies from device to device.

- 4 The odd and even input gate biases may be adjusted differentially to achieve an odd/even balance in the video output.

- <sup>5</sup> See text.

- Maximum effective array data rate is as follows (15 MHz per video output); RL1282D = 60 MHz; RL1284D = 120 MHz; RL1288D = 240 MHz.

DataShe

31

Table 4. Array Performance Characteristics (@ 200 kHz, 25°C) (Use Typical Voltages shown in Table 3)

| Sym               | Parameter                                | Min  | Тур     | Max | Units                    |

|-------------------|------------------------------------------|------|---------|-----|--------------------------|

| DRFPN             | Dynamic range FPN <sup>1,6</sup>         | 240  | 1500    |     | -                        |

| DRTN              | Dynamic range thermal noise 2            | 1200 | 7500    |     |                          |

| ENE               | Peak-to-peak noise equivalent exposure 3 | -    | .0004   |     | μj/cm <sup>2</sup>       |

| ESAT              | Saturation exposure 3                    | 0.45 | 0.7     | -   | μj/cm <sup>2</sup>       |

| -3A1              | Spectral response range limits           | -    | 0.2-1.1 | -   | μm                       |

| R                 | Responsivity 3,4                         | 2.0  | 2.4     | -   | V per μj/cm <sup>2</sup> |

| • •               | Photoresponse nonuniformity:             |      |         |     |                          |

|                   | Individual output 3,5,8                  |      | 5       | 10  | ±%                       |

|                   | Match across array 3,5,7,9               |      | 7       | 15  | %                        |

| V <sub>Dark</sub> | Average dark signal 6                    | -    | 0.5     | 4   | mV                       |

| FPN               | Fixed pattern noise 6                    | -    | 1       | 5   | mV                       |

| V <sub>Sat</sub>  | Saturation output voltage                | 1.2  | 1.5     | - 1 | ٧                        |

| P                 | Power dissipation DC 4                   | -    | 600     | -   | mW                       |

| Ro                | Output impedance                         | -    | 1500    | -   | Ω                        |

| Npp               | Peak-to-peak noise 2                     |      | 1       | 5   | mV                       |

|                   | Dark level DC mismatch                   |      | 150     | 400 | mV                       |

|                   | (output to output)                       |      |         |     |                          |

|                   | Dark level 7                             |      | 8.0     |     | V                        |

| CTE               | Charge transfer efficiency               |      | .99995  |     |                          |

#### Notes:

- 1 Dynamic range defined as V<sub>Sat/p</sub>-p fixed pattern noise

- 2 Dynamic range defined as V<sub>Sat</sub>/single pixel rms thermal noise; rms noise is defined as 1/5 of p-p noise

- 3 Measured using 2870°K light source of Figure 7. Filtered with Fish-Schurman HA-11 heat absorbing filter

- 4 3K $\Omega$  load resistors and  $V_{DD} = 14.5V$

- 5 Measured with uniform illumination at approximately 50% of saturation

- 6 At 20°C with 1 msec integration time. Dark signal and dark signal nonuniformity are proportional to integration time, and approximately double for every 7°C increase in temperature

- 7 See Figure 6 for output schematic

- DataSheet4U.com

- 8 Calculated as: + % NU = (Max Diode Avg./Avg.) x 100

- % NU = (Avg. Min. Diode/Avg.) x 100

- 9 Calculated as: X Y/X where X and Y are the average outputs of any two taps of the array, and X is the output of greater amplitude, output is defined as the difference between the diode dark level and the diode level in the light.

et4U.com

DataShe

#

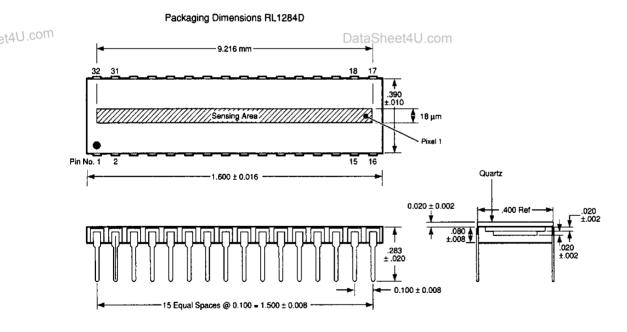

Figure 9. Package Dimensions

DataShee

33

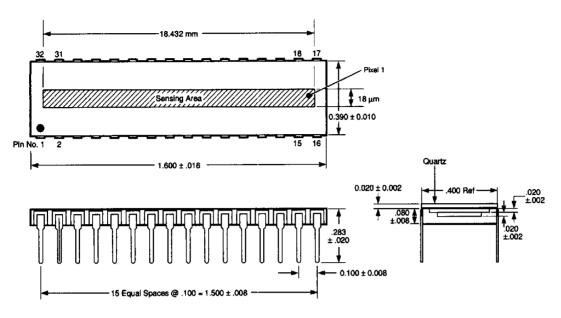

#### Packaging Dimensions RL1288D

Figure 9. Package Dimensions (Continued)

## Ordering Information \*

| Part Number   | Evaluation Board   |

|---------------|--------------------|

| RL1282DAQ-111 | No Board Available |

| RL1284DAQ-111 | RC0716LNB-020      |

| RL1288DAQ-111 | RC0716LNB-011      |

DataSheet4U.com

Includes standard devices. For options, consult EG&G Reticon sales offices.

> 055-0044 October 1991

et4U.com