## 5 VOLT SERIES 200 FLASH MEMORY MINIATURE CARD

iFM004G, iFM008G and iFM016G

- Low-Cost Linear Flash Card

5 Volt Intel<sup>®</sup> StrataFlash<sup>™</sup> Memory Flash Technology

- Fast Read Performance

150 ns Max Access Time

- High-Performance Writes — 12 µs Typical Byte Write

x16 Data Interface

December 1998

- 32 Byte Write Buffer

Frees CPU to Perform Other Tasks

- Low Deep Power-Down Current

145 μA Maximum for 4-MB Card

- Single Supply Operation

5 V Read/Write

- Automated Write and Erase Algorithms

CFI and SCS Compliant

- Enhanced Automated Suspend Options

Block Erase Suspend to Write

Block Erase Suspend to Read

- Enhanced Data Protection Features

Flexible Block Locking

- 100,000 Erase Cycles per Block

- 128-Kbyte Erase Blocks

The Intel<sup>®</sup> Series 200 Miniature Cards deliver the benefits of Intel<sup>®</sup> StrataFlash<sup>™</sup> memory to users of portable electronic systems. Capitalizing on two-bit-per-cell technology, Intel StrataFlash memory products provide 2X the bits in 1X the space. Intel StrataFlash memory devices are the first to bring reliable, two-bit-per-cell storage technology to the flash memory market.

Intel StrataFlash memory benefits include: more density in less space, lowest cost-per-bit NOR devices, support for code and data storage, and easy migration to future devices.

Using the same NOR-based ETOX<sup>™</sup> technology as Intel's one-bit-per-cell products, Intel StrataFlash memory devices take advantage of 400 million units of manufacturing experience since 1988. As a result, Intel StrataFlash components are ideal for code or data applications where high density and low cost are required. Examples include networking, telecommunications, audio recording, and digital imaging.

Intel StrataFlash memory components provide a new generation of forward-compatible software support built upon the Intel<sup>®</sup> FlashFile<sup>™</sup> memory architecture. By using the Common Flash Interface (CFI) and the Scaleable Command Set (SCS), customers can take advantage of density upgrades and optimized write capabilities of future Intel StrataFlash memory devices.

Manufactured on the Intel® 0.4 micron ETOX V process technology, Intel StrataFlash memory provides the highest levels of quality and reliability.

The 5 Volt Series 200 Miniature Cards, based on the Miniature Card Implementers Forum (MCIF), employ 5 Volt Intel StrataFlash components to provide the ultimate in convenient, low-cost data storage for users of portable electronics systems. To meet the demanding requirements of diverse portable electronic system, these Miniature Cards are designed as small form factor removable media and are favored for their cost-effectiveness and reliability. Ideal platforms for the 5 Volt Series 200 include digital still cameras, audio recorders, smart cellular phones and hand-held PCs. Such applications require low-cost, consumer-friendly data storage media, as well as a convenient method to transport data to a PC for file manipulation and enhancement.

Host-based filing system software, such as Flash Translation Layer (FTL), eliminates the need for expensive card-based microcontrollers and ASICs. The 5 Volt Series 200 Flash Memory Miniature Cards enable the consumer to enjoy compatibility across a wide range of systems, allowing easy data exchange with MS-DOS\* and Windows\* 95-based PCs.

NOTE: This document formerly known as Series 200 Flash Memory Miniature Card 4, 8, 16 Mbytes.

Order Number: 290620-005

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

The iFM004G, iFM008G and iFM016G may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation P.O. Box 5937 Denver, CO 80217-9808

or call 1-800-879-4725 or visit Intel's Website at http://www.intel.com

COPYRIGHT © INTEL CORPORATION 1998

CG-041493

\*Third-party brands and names are the property of their respective owners

# int<sub>el</sub>.

## CONTENTS

| F | Þ۵ | ( | 3 | F |

|---|----|---|---|---|

|   | '  | " | - | _ |

| Р | A | G | ٦F |

|---|---|---|----|

| • |   | - | ·  |

| TAGE                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0 SCOPE OF DOCUMENT5                                                                                                                                                                                                                                                                                                           |

| 2.0 PRODUCT OVERVIEW5                                                                                                                                                                                                                                                                                                            |

| 3.0 CARD ARCHITECTURE                                                                                                                                                                                                                                                                                                            |

| 4.0 MEMORY CONTROL LOGIC       10         4.1 Bus Operations       10         4.1.1 Read Array       10         4.1.2 Output Disable       10         4.1.3 Standby       11         4.1.4 Reset/Power-Down       11         4.1.5 Read Identifier Codes       12         4.1.6 Write       12         4.2 Decode Logic       12 |

| 5.0 COMMAND DEFINITION13                                                                                                                                                                                                                                                                                                         |

| 5.1 Basic Command Set13                                                                                                                                                                                                                                                                                                          |

| 5.1.1 Read Array Command13                                                                                                                                                                                                                                                                                                       |

| 5.1.2 Read Identifier Codes Command15                                                                                                                                                                                                                                                                                            |

| 5.1.3 Read Status Register Command15                                                                                                                                                                                                                                                                                             |

| 5.1.4 Clear Status Register Command15                                                                                                                                                                                                                                                                                            |

| 5.1.5 Block Erase Command                                                                                                                                                                                                                                                                                                        |

| 5.1.6 Block Erase Suspend Command                                                                                                                                                                                                                                                                                                |

| 5.1.8 Set Block Lock-Bit Command                                                                                                                                                                                                                                                                                                 |

| 5.1.6 Oct Diock Eock Dit Command                                                                                                                                                                                                                                                                                                 |

| 5 1 9 Clear Block Lock-Bits Command 18                                                                                                                                                                                                                                                                                           |

| 5.1.9 Clear Block Lock-Bits Command                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                  |

| 5.2 Scaleable Command Set18                                                                                                                                                                                                                                                                                                      |

| 5.2 Scaleable Command Set                                                                                                                                                                                                                                                                                                        |

| 6.0 CARD ATTRIBUTE INFORMATION       | 21 |

|--------------------------------------|----|

| 6.1 Card Information Structure       | 21 |

| 6.2 Attribute Information Structure  | 21 |

| 6.3 CIS Data                         | 22 |

| 7.0 ELECTRICAL SPECIFICATIONS        | 26 |

| 7.1 Absolute Maximum Ratings         | 26 |

| 7.2 Operating Conditions             | 26 |

| 7.3 Capacitance                      | 26 |

| 7.4 DC Characteristics               | 27 |

| 7.5 AC Characteristics               | 28 |

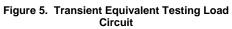

| 7.5.1 Read Operations                | 29 |

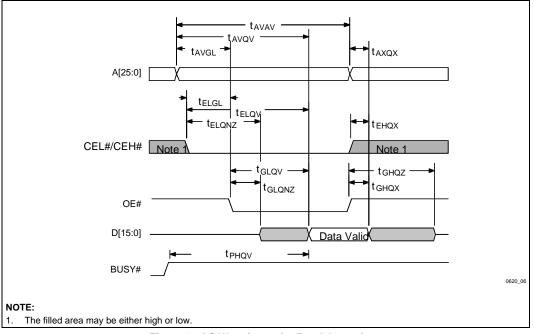

| 7.5.2 Write Operations               | 30 |

| 7.5.3 Power-Up Timing                | 31 |

| 7.6 Block Erase, Write, and Lock-Bit |    |

| Configuration Performance            | 33 |

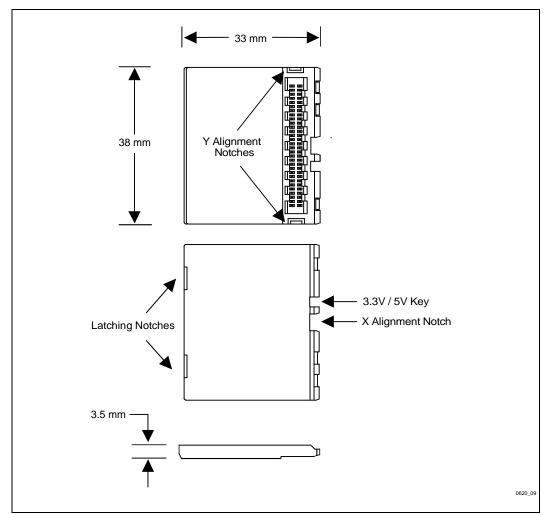

| 8.0 PACKAGING                        | 34 |

| 9.0 ORDERING INFORMATION             | 35 |

| 10.0 ADDITIONAL INFORMATION          | 35 |

|                                      |    |

### **REVISION HISTORY**

| Date of<br>Revision | Version | Description                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12/01/97            | -001    | Original version                                                                                                                                                                                                                                                                                                                                                               |

| 03/16/98            | -002    | Updated front cover sheet highlights: write speed changed to 7 $\mu s,$ erase cycles per block changed to 100,000                                                                                                                                                                                                                                                              |

|                     |         | In Table 5, <i>Card Signal Values for the Card's Bus Operations and Modes</i> , changed conditions for Word Read, Word Write and Standby operations                                                                                                                                                                                                                            |

|                     |         | In first sentence of paragraph 4.1.3, <i>Standby</i> , re-defined standby mode entry conditions                                                                                                                                                                                                                                                                                |

|                     |         | In Table 11, <i>CIS Memory Map</i> , removed CISTPL_DEVICE_OC row entry,<br>"bumped-up" the address locations for the final 2 row entries of the table                                                                                                                                                                                                                         |

|                     |         | In paragraph 6.3, <i>CIS Data</i> , eliminated all references to 4 MB–200 ns, 8 MB–<br>150 ns and 16 MB–150 ns card density-speed combinations and changed<br>description entry for addresses 05H – 0DH from null to CISTPL_NULL (in bold<br>font)                                                                                                                             |

|                     |         | In the last row (for $I_{CCES}$ ) of the DC Characteristics table of paragraph 7.4 changed CE_1# to CEL# and CE_2# to CEH#                                                                                                                                                                                                                                                     |

|                     |         | In note 1 of paragraph 7.5.2, <i>Write Operations</i> , restated the "CE# deasserted" conditions to be both CE#s (CEL# and CEH#) instead of either one of the CEs (CEL# or CEH#)                                                                                                                                                                                               |

|                     |         | In paragraph 7.6, <i>Block Erase, Write, and Lock-Bit Configuration Performance,</i> changed the "Typ" entries for first 3 parameters (pertaining to write time) to increase write times by 16.67%; added note 6 to describe expected write time performance relative to the specified maximum and typical values, and to suggest use of BUSY# to maximize system performance. |

| 05/01/98            | -003    | Updated front cover sheet highlights: changed write speed to $6.3 \mu s$                                                                                                                                                                                                                                                                                                       |

| 06/05/98            | -004    | Updated front cover sheet highlights: changed write speed to 12 $\mu s$                                                                                                                                                                                                                                                                                                        |

|                     |         | In Paragraph 7.6 <i>Block Erase, Write, and Lock-Bit Configuration Performance,</i> changed typical values for the following parameters: Write Buffer Word Write Time, Word Write Time (Using Word Write Command), and Block Write Time (Using Write to Buffer Command)                                                                                                        |

| 12/21/98            | -005    | All densities of the 5 Volt Series 200 Miniature Card are now based on the 28F320J5. Specifications were changed accordingly.                                                                                                                                                                                                                                                  |

|                     |         | Name of document changed from <i>Series 200 Flash Memory Miniature Card 4, 8, 16, Mbyte.</i>                                                                                                                                                                                                                                                                                   |

PRELIMINARY

### 1.0 SCOPE OF DOCUMENT

This datasheet describes a 5 Volt Intel<sup>®</sup> StrataFlash<sup>™</sup> memory card architecture, AC and DC characteristics and command definitions. Refer to Intel order number 290606 when ordering the datasheet.

### 2.0 PRODUCT OVERVIEW

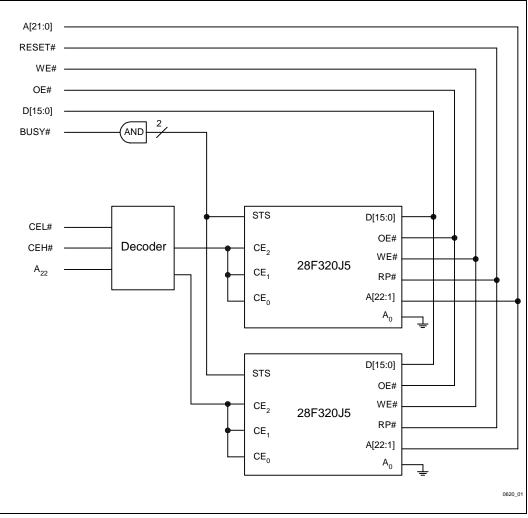

The 4-, 8- and 16-Mbyte flash memory cards each contain a flash memory array made up of 5 Volt Intel StrataFlash memory components. The 4-Mbyte card consists of a single 4-Mbyte component (product number 28F320J5) configured for x 16 operation. Similarly, the 8-Mbyte card consists of two 4-Mbyte components (Intel® 28F320J5) configured for x16 operation. The 16-Mbyte card consists of four 4-Mbyte components which are configured for x16 operation. Intel StrataFlash memory card store more than one bit per flash memory card store more than one bit per flash memory arrays. Figure 1 provides a generic block diagram which illustrates the card's functional layout and user interface.

A Command User Interface (CUI) serves as the interface between the system processor and internal operation of the card's memory device(s). A

valid command sequence written to the CUI initiates device automation. An internal Write State Machine (WSM) automatically executes the algorithms and timings necessary for block erase, write, and lock-bit configuration operations.

Each Intel StrataFlash memory device incorporates a 16 word (32 byte) write buffer. This dramatically improves write performance by optimizing a flash memory device's programming algorithm, thereby freeing the CPU from writing data and polling status on a word-by-word basis. The 32-byte buffer can be loaded at full bus speed; then a single command can be issued to transfer the buffer into the flash memory array. While the Write State Machine (WSM) is handling all of the flash memory programming details for a memory write operation, the host CPU is free to perform other tasks.

The 4-, 8-, and 16-Mbyte cards contain, respectively, 32, 64, and 128 separate 128-Kbyte erase blocks. A block erase operation erases one of the 128-Kbyte blocks typically within one second—independent of other blocks. Each block can be independently erased 100,000 times. Block erase suspend mode allows system software to suspend block erase to read data from or write data to any other block.

Figure 1. 8-Mbyte Flash Memory Card Block Diagram Showing Major Functional Elements

### 3.0 CARD ARCHITECTURE

The 5 Volt Series 200 Miniature Card implements the functionality of the Miniature Card Specification with X16 (word-wide) data transfers. The card does not support individual 8-bit (byte)—wide memory data transfers as the card's memory devices(s) and data bus interface are structured word-wide. The card ignores the Miniature Card interface signal BS#8 (for selecting between byte and word host data transfers) and assumes the BS#8 signal to be HIGH (for word access between the host and card).

Various information about the card is contained in an Attribute Information Structure (AIS) as defined in the PCMCIA Miniature Card Specification. The AIS is stored in Block 0 of the card's memory array. The high byte of the AIS is always FFH, the low byte contains the actual AIS data.

## 3.1 Card Signal Description

The signals for the 5 Volt Series 200 Miniature Card are listed in Table 1 and Table 2. They comply with the Miniature Card Specification. Table 3 and Table 4 describes the signals.

| Signal Name                     | Pad #                                                                                                                                                                                                                                                                                                                                               | Pad # Signal Name                                      |                                                                                                                                                                                                                                                                                                                                                                                       | Signal Name                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>18</sub>                 | 21                                                                                                                                                                                                                                                                                                                                                  | D <sub>12</sub>                                        | 41                                                                                                                                                                                                                                                                                                                                                                                    | A <sub>4</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A <sub>16</sub>                 | 22                                                                                                                                                                                                                                                                                                                                                  | D <sub>10</sub>                                        | 42                                                                                                                                                                                                                                                                                                                                                                                    | CEL#                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A <sub>14</sub>                 | 23                                                                                                                                                                                                                                                                                                                                                  | D <sub>9</sub>                                         | 43                                                                                                                                                                                                                                                                                                                                                                                    | A <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>CCR</sub> <sup>(1)</sup> | 24                                                                                                                                                                                                                                                                                                                                                  | D <sub>0</sub>                                         | 44                                                                                                                                                                                                                                                                                                                                                                                    | CASL#(1)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CEH#                            | 25                                                                                                                                                                                                                                                                                                                                                  | D <sub>2</sub>                                         | 45                                                                                                                                                                                                                                                                                                                                                                                    | CASH#(1)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A <sub>11</sub>                 | 26                                                                                                                                                                                                                                                                                                                                                  | D <sub>4</sub>                                         | 46                                                                                                                                                                                                                                                                                                                                                                                    | CD#                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A9                              | 27                                                                                                                                                                                                                                                                                                                                                  | RFU                                                    | 47                                                                                                                                                                                                                                                                                                                                                                                    | A <sub>21</sub> <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                   |

| A <sub>8</sub>                  | 28                                                                                                                                                                                                                                                                                                                                                  | D <sub>7</sub>                                         | 48                                                                                                                                                                                                                                                                                                                                                                                    | BUSY#                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A <sub>6</sub>                  | 29                                                                                                                                                                                                                                                                                                                                                  | SDA <sup>(1)</sup>                                     | 49                                                                                                                                                                                                                                                                                                                                                                                    | WE#                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A <sub>5</sub>                  | 30                                                                                                                                                                                                                                                                                                                                                  | SCL <sup>(1)</sup>                                     | 50                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>14</sub>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A <sub>3</sub>                  | 31                                                                                                                                                                                                                                                                                                                                                  | A <sub>19</sub>                                        | 51                                                                                                                                                                                                                                                                                                                                                                                    | RFU(1,2)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A <sub>2</sub>                  | 32                                                                                                                                                                                                                                                                                                                                                  | A <sub>17</sub>                                        | 52                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>11</sub>                                                                                                                                                                                                                                                                                                                                                                                                                  |

| A <sub>0</sub>                  | 33                                                                                                                                                                                                                                                                                                                                                  | A <sub>15</sub>                                        | 53                                                                                                                                                                                                                                                                                                                                                                                    | VS2#(1)                                                                                                                                                                                                                                                                                                                                                                                                                          |

| RAS#(1)                         | 34                                                                                                                                                                                                                                                                                                                                                  | A <sub>13</sub>                                        | 54                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>8</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A <sub>24</sub> <sup>(1)</sup>  | 35                                                                                                                                                                                                                                                                                                                                                  | A <sub>12</sub>                                        | 55                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>1</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A <sub>23</sub> <sup>(1)</sup>  | 36                                                                                                                                                                                                                                                                                                                                                  | RESET#                                                 | 56                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| A <sub>22</sub> (1)             | 37                                                                                                                                                                                                                                                                                                                                                  | A <sub>10</sub>                                        | 57                                                                                                                                                                                                                                                                                                                                                                                    | D5                                                                                                                                                                                                                                                                                                                                                                                                                               |

| OE#                             | 38                                                                                                                                                                                                                                                                                                                                                  | VS1#                                                   | 58                                                                                                                                                                                                                                                                                                                                                                                    | D <sub>6</sub>                                                                                                                                                                                                                                                                                                                                                                                                                   |

| D <sub>15</sub>                 | 39                                                                                                                                                                                                                                                                                                                                                  | A <sub>7</sub>                                         | 59                                                                                                                                                                                                                                                                                                                                                                                    | RFU(1,2)                                                                                                                                                                                                                                                                                                                                                                                                                         |

| D <sub>13</sub>                 | 40                                                                                                                                                                                                                                                                                                                                                  | BS8# <sup>(1)</sup>                                    | 60                                                                                                                                                                                                                                                                                                                                                                                    | A <sub>20</sub> <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                 | A <sub>18</sub> A <sub>16</sub> A <sub>14</sub> V <sub>CCR</sub> <sup>(1)</sup> CEH#           A <sub>11</sub> A <sub>9</sub> A <sub>8</sub> A <sub>6</sub> A <sub>5</sub> A <sub>3</sub> A <sub>2</sub> A <sub>0</sub> RAS#(1)           A <sub>22</sub> (1)           A <sub>22</sub> (1)           A <sub>22</sub> (1)           D <sub>15</sub> | $\begin{array}{c c c c c c c c c c c c c c c c c c c $ | $A_{18}$ $21$ $D_{12}$ $A_{16}$ $22$ $D_{10}$ $A_{14}$ $23$ $D_9$ $V_{CCR}^{(1)}$ $24$ $D_0$ $CEH#$ $25$ $D_2$ $A_{11}$ $26$ $D_4$ $A_9$ $27$ $RFU$ $A_8$ $28$ $D_7$ $A_6$ $29$ $SDA^{(1)}$ $A_5$ $30$ $SCL^{(1)}$ $A_3$ $31$ $A_{19}$ $A_2$ $32$ $A_{17}$ $A_0$ $33$ $A_{15}$ $RAS#^{(1)}$ $34$ $A_{13}$ $A_{24}^{(1)}$ $35$ $A_{12}$ $A_{22}^{(1)}$ $37$ $A_{10}$ $OE#$ $38$ $VS1#$ | $A_{18}$ $21$ $D_{12}$ $41$ $A_{16}$ $22$ $D_{10}$ $42$ $A_{14}$ $23$ $D_9$ $43$ $V_{CCR}^{(1)}$ $24$ $D_0$ $44$ CEH# $25$ $D_2$ $45$ $A_{11}$ $26$ $D_4$ $46$ $A_9$ $27$ RFU $47$ $A_8$ $28$ $D_7$ $48$ $A_6$ $29$ $SDA^{(1)}$ $49$ $A_5$ $30$ $SCL^{(1)}$ $50$ $A_3$ $31$ $A_{19}$ $51$ $A_2$ $32$ $A_{17}$ $52$ $A_0$ $33$ $A_{15}$ $53$ $RAS#^{(1)}$ $36$ RESET# $56$ $A_{22}^{(1)}$ $37$ $A_{10}$ $57$ $OE#$ $39$ $A7$ $59$ |

### Table 1. 5 Volt Series 200 Flash Memory Miniature Card Interface Signals

NOTES:

1. These signals make no internal connection into the card.

2. Reserved pins must not be driven by the host. They should be left floating.

3. A<sub>21</sub> and A<sub>22</sub> are not decoded on the 4-Mbyte card.

4. A<sub>22</sub> is not decoded on the 8-Mbyte card.

| Signal # | Signal Name     |

|----------|-----------------|

| 61       | GND             |

| 62       | CINS#           |

| 63       | V <sub>CC</sub> |

### Table 3. 5 Volt Series 200 Flash Memory Miniature Card Interface Signal Description

| Symbol                          | Туре             | Name and Function                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>24</sub> | INPUT            | <b>ADDRESS INPUTS:</b> Addresses $A_0$ through $A_{24}$ enable direct addressing of up to 64 MB of memory on the card. The memory will wrap at the card density boundary. The system should NOT try to access memory beyond the card's density, since the upper addresses are not decoded.                                                                       |

| D <sub>0</sub> D <sub>15</sub>  | INPUT/<br>OUTPUT | <b>DATA INPUT/OUTPUT:</b> $D_0$ through $D_{15}$ constitute the bi-directional data bus. $D_{15}$ is the most significant bit.                                                                                                                                                                                                                                   |

| CEL#,<br>CEH#                   | INPUT            | <b>CARD ENABLE LOW &amp; HIGH:</b> CEL# enables accesses on the low byte of the data bus $D_{0-7}$ . CEH# enables accesses on the high byte of the data bus $D_{8-15}$ . Both CEL# and CEH# are active low signals. A host is expected to assert both CEL# and CEH# as the card's memory provides for word-wide data transfers but not byte-wide data transfers. |

| OE#                             | INPUT            | OUTPUT ENABLE: Active low signal, enables read data from the memory card.                                                                                                                                                                                                                                                                                        |

| WE#                             | INPUT            | WRITE ENABLE: Active low signal, enables write data to the memory card.                                                                                                                                                                                                                                                                                          |

| BUSY#                           | OUTPUT           | <b>BUSY:</b> Active low signal, indicates the status of internally timed erase or write activities. A high output indicates the memory card is ready to accept another command.                                                                                                                                                                                  |

| CD#                             | OUTPUT           | <b>CARD DETECT:</b> Active low signal, provides for card insertion detection. CD# connects to ground internally on the memory card, and will be forced low when the CD# interface signal connects to the host.                                                                                                                                                   |

| RESET#                          | INPUT            | <b>RESET:</b> Active low input signal, resets the device's command user interface and places the card into a deep power-down mode. The host must drive this signal.                                                                                                                                                                                              |

| BS8#                            | INPUT            | <b>8-BIT BUS WIDTH:</b> This signal is not connected on the 5 Volt Series 200 Miniature Card. The card assumes the Miniature Card Implementers Forum Specification's HIGH state definition of this signal to provide for only 16-bit data transfers between the host and card.                                                                                   |

| VS1#,<br>VS2#                   | OUTPUT           | <b>VOLTAGE SENSE:</b> Notifies the host socket of the card's $V_{CC}$ requirements. $VS_1$ and $VS_2$ are both left <b>open</b> to indicate that the card only operates at 5 V.                                                                                                                                                                                  |

| RFU                             |                  | RESERVED FOR FUTURE USE                                                                                                                                                                                                                                                                                                                                          |

PRELIMINARY

Table 4. 5 Volt Series 200 Flash Memory Miniature Card Power/Insertion Signal Description

| Symbol          | Туре   | Name and Function                                                                                                                                                                                                           |

|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CINS#           | OUTPUT | <b>CARD INSERTION DETECT:</b> This signal provides for early card insertion detection. CINS# connects to ground internally on the memory card, and will be forced low when the power/insertion signals connect to the host. |

| V <sub>CC</sub> | -      | CARD POWER SUPPLY: 5 V                                                                                                                                                                                                      |

| GND             | -      | GROUND                                                                                                                                                                                                                      |

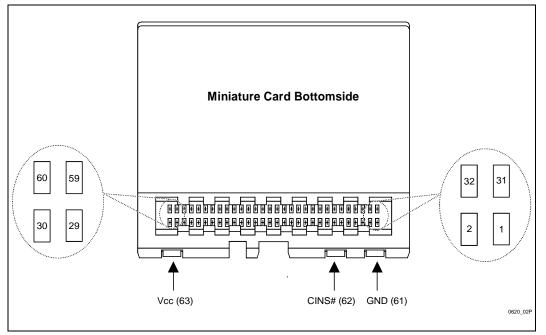

Figure 2. Card Interface Signal Assignment

### 4.0 MEMORY CONTROL LOGIC

### 4.1 Bus Operations

The host executes memory read, write and erase operations by issuing the appropriate command to the flash memory's Command User Interface (CUI). The CUI, which supports the command set of the card's memory devices, serves as the interface between the host processor and internal operation of a flash device. Commands can be issued to the CUI using standard microprocessor bus cycles.

Table 5 lists the Miniature Card's bus operations and modes. For each listed bus operation or mode the table defines the value of the card's relevant bus and control signals.

### 4.1.1 READ ARRAY

The host enables reads from the card by writing the appropriate read command to the CUI. The memory devices automatically reset to read array mode upon initial card power-up or after card reset. CEL#, CEH#, and OE# must be logically active to obtain 16 data bits at the outputs. The Card Enable (CEL# and CEH#) inputs together with the card's address inputs are used to select the addressed devices. Output Enable (OE#) is the data input/output (Do-D\_{15}) direction control, and when active, drives data from the selected memory onto the data bus. WE# must be driven to  $V_{\rm IH}$  (inactive) during a read access.

### 4.1.2 OUTPUT DISABLE

With OE# at a logic-high level (V<sub>IH</sub>), the device outputs are disabled. Outputs ( $D_0-D_{15}$ ) are placed in a high-impedance state.

| Bus<br>Operation/Mode | RESET# | CEL# | CEH# | OE# | WE# | <b>A</b> 1 | BS8# | D <sub>8-15</sub> | D <sub>0-7</sub> | Notes      |

|-----------------------|--------|------|------|-----|-----|------------|------|-------------------|------------------|------------|

| Word Read             | VIH    | VIL  | VIL  | VIL | VIH | Х          | Х    | High              | Low              | 1, 2, 4,   |

|                       | VIH    | VIH  | VIL  | VIL | VIH | Х          | Х    | High              | Low              | 1, 2, 4, 5 |

|                       | VIH    | VIL  | VIH  | VIL | VIH | Х          | Х    | High              | Low              | 1, 2, 4, 5 |

| Word Write            | VIH    | VIL  | VIL  | VIH | VIL | Х          | Х    | High              | Low              | 1, 2, 4    |

|                       | VIH    | VIH  | VIL  | VIH | VIL | Х          | Х    | High              | Low              | 1, 2, 4, 6 |

|                       | VIH    | VIL  | VIH  | VIH | VIL | Х          | Х    | High              | Low              | 1, 2, 4, 6 |

| Manufacturer ID       | VIH    | VIL  | VIL  | VIL | VIH | $V_{IL}$   | Х    | 00H               | 89H              |            |

| Device ID             | VIH    | VIL  | VIL  | VIL | VIH | VIH        | Х    | 00H               | ID               | 3          |

| Standby               | Vih    | Х    | VIH  | Х   | Х   | Х          | Х    | High-Z            | High-Z           |            |

|                       | Vih    | VIH  | Х    | Х   | Х   | Х          | Х    | High-Z            | High-Z           |            |

| Output Disable        | Vih    | Х    | Х    | VIH | VIH | Х          | Х    | High-Z            | High-Z           |            |

| Reset/Power-Down      | VIL    | Х    | Х    | Х   | Х   | Х          | Х    | High-Z            | High-Z           |            |

Table 5. Card Signal Values for the Card's Bus Operations and Modes

#### NOTES:

- 1. X can be  $V_{IL}$  or  $V_{IH}$  for control signals and address.

- 2. BUSY# is V<sub>OL</sub> when the WSM is executing internal write or block erase algorithms. It is V<sub>OH</sub> when the WSM is not busy, in erase suspend mode, or deep power-down mode.

- 3. The device code can be 14H, or 15H. Software should check for both cases for compatibility with future cards.

- 4. High indicates high byte data, low indicates low byte data.

- 5. Both memory bytes will be read from memory as the card's memory component data bus is word-wide and does not provide for individual byte access. The bus operation is non-compliant with the *PCMCIA PC Card Standard* as the *PC Card Standard* specifies a byte read operation instead of a word read operation for the listed signal conditions.

- 6. Both memory bytes will be written to memory as the card's memory component data bus is word-wide and does not provide for individual byte access. The bus operation is non-compliant with the *PCMCIA PC Card Standard* as the *PC Card Standard* specifies a byte write operation instead of a word write operation for the listed signal conditions. If a host system desires a byte write operation instead of a word write operation, then the host system must write V<sub>H</sub> to the unwanted active byte (which should be inactive according the *PC Card Standard*) in order to prevent the unwanted active byte from being written to card memory.

#### 4.1.3 STANDBY

If both CEL# and CEH# are at a logic-high level  $(V_{IH})$ , the card enters standby mode. Standby operation disables much of the card's circuitry and substantially reduces device power consumption. The outputs  $(D_0-D_{15})$  are placed in a high-impedance state independent of the status of OE#. If the host deselects the card during a write or erase, the card continues to function and consume normal active power until the operation completes.

#### 4.1.4 RESET/POWER-DOWN

RESET# at  $V_{\text{IL}}$  initiates the reset/power-down mode.

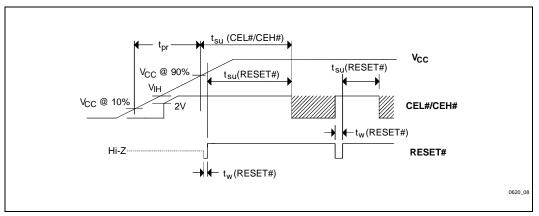

In read modes, RESET#-low deselects the card's memory, places output drivers in a high-impedance state, and turns off numerous internal memory circuits. RESET# must be held low for a minimum of  $t_w$ . Time  $t_{su}$  is required after return from reset mode until initial memory access outputs are valid. After this wake-up interval, normal operation is restored. The CUI is reset to read array mode and all memory device status registers are set to 80H.

During block erase, write, or lock-bit configuration modes, RESET#-low will abort the operation BUSY# transitions low and remains low for a maximum time of  $t_w + t_{su}$  until the reset operation is complete. Memory contents being altered are no longer valid; the data may be partially corrupted after a write operation or partially altered after an erase or lock-bit configuration operation. Time  $t_{su}$  is required after RESET# goes to logic-high (V<sub>IH</sub>) before another command can be written.

As with any automated device, it is important to assert RESET# during system reset. When the system comes out of reset, it expects to read data from the flash memory. Automated flash memories provide status information when accessed during block erase, write, or lock-bit configuration modes. If a CPU reset occurs with no flash memory reset, proper initialization may not occur because the flash memory may be providing status information instead of array data. Intel® Flash memories allow proper initialization following a system reset through the use of the RESET# input. In this application, RESET# is controlled by the same signal that resets the system CPU.

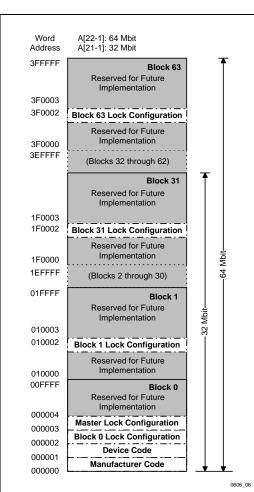

#### NOTES:

- 1. Data is always given on the low byte (upper byte contains 00h).

- Memory shown is accessed by the Read Identifier Codes command only and is physically distinct from the card's flash memory array.

- 3. Master Lock function of the card's underlying memory devices is not a card function. The Master Lock Configuration information identified in the above memory map is shown only for the sake of consistency between the illustrated memory map and a corresponding memory map shown in the datasheet for the memory devices.

Figure 3. Device Identifier Code Memory Map

#### 4.1.5 READ IDENTIFIER CODES

The read identifier codes operation outputs the manufacturer code, device code, block lock configuration codes for each block, and the master lock configuration code (see Figure 3) Using the manufacturer and device codes, the system CPU can automatically match the device with its proper algorithms. The block lock and master lock configuration codes identify locked and unlocked blocks and master lock-bit setting.

### 4.1.6 WRITE

Writing commands to the CUI enables reading of device data, query, identifier codes, inspection and clearing of the status register, as well as block erasure, writing of data and lock-bit configuration.

The Block Erase command requires appropriate command data and an address within the block to be erased. The Word Write command requires the command and address of the location to be written. The Write to Buffer command requires the command, starting address of the memory region to be written and the number of words to be written to the write buffer. Set Master and Block Lock-Bit commands require the command and address within the device (Master Lock) or block within the device (Block Lock) to be locked. The Clear Block Lock-Bits command requires the command and address within the device.

The CUI does not occupy an addressable memory location. It is part of each memory device and is written when the device is enabled and WE# is active. The address and data needed to execute a command are latched on the rising edge of WE# or the first edge of CEL# or CEH# that disables the device. Write cycle timing is specified in Section 9.2 (*Write Operations*).

### 4.2 Decode Logic

The card's decode logic enables the appropriate memory component during a read or write access of card memory. Unused upper addresses for the 5 Volt Series 200 Miniature Card will not be decoded. The address decoding will wrap around at the card's density.

PRELIMINARY

### 5.0 COMMAND DEFINITION

The operations of the card's memory device(s) are selected by the writing of specific commands into the CUI. The 5 Volt Series 200 Miniature Card implements two command sets: the basic command set and the scaleable command set. The Basic Command Set is backward compatible with the Series 100 Miniature Card with the exception that write (program) suspend is not supported in the 5 Volt Series 200. The Scaleable Command Set adds three capabilities to the Miniature Card in addition to the Basic Command Set:

- 1. Common Flash Interface (CFI)

- 2. Buffered writes which employ a 32-byte write buffer to allow higher performance writes than available with the Basic Command Set; and

- 3. A configurable BUSY# output.

### 5.1 Basic Command Set

Table 6 presents the 5 Volt Series 200 Miniature Card's Basic Command Set. The table indicates that the commands require one or more bus cycles to implement. The table and notes following the table describe each bus cycle. Complete descriptions of the individual commands follow in subsections of the current document section.

### 5.1.1 READ ARRAY COMMAND

Upon initial device power-up and after exit from reset/power-down mode, the card's memory devices default to read array mode. This operation is also initiated by writing the Read Array command to a memory device. The device remains enabled for reads until another command is written. Once the internal WSM has started a block erase, write, or lock-bit configuration, the device will not recognize the Read Array command until the WSM completes its operation unless the WSM is suspended via an Erase Suspend command.

| Command               | Bus<br>Cycles<br>Req'd. | Notes | First Bus Cycle     |                     |                       | Second Bus Cycle    |                     |                       |

|-----------------------|-------------------------|-------|---------------------|---------------------|-----------------------|---------------------|---------------------|-----------------------|

|                       |                         |       | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data <sup>(3,4)</sup> | Oper <sup>(1)</sup> | Addr <sup>(2)</sup> | Data <sup>(3,4)</sup> |

| Read Array            | 1                       |       | Write               | Х                   | XXFFH                 |                     |                     |                       |

| Read Identifier Codes | ≥2                      | 5     | Write               | Х                   | XX90H                 | Read                | IA                  | ID                    |

| Read Status Register  | 2                       |       | Write               | Х                   | XX70H                 | Read                | Х                   | SRD                   |

| Clear Status Register | 1                       |       | Write               | Х                   | XX50H                 |                     |                     |                       |

| Word Write            | 2                       | 6, 7  | Write               | Х                   | XX40H<br>or<br>XX10H  | Write               | WA                  | WD                    |

| Block Erase           | 2                       | 7     | Write               | Х                   | XX20H                 | Write               | BA                  | XXD0H                 |

| Block Erase Suspend   | 1                       | 7     | Write               | Х                   | XXB0H                 |                     |                     |                       |

| Block Erase Resume    | 1                       | 7     | Write               | Х                   | XXD0H                 |                     |                     |                       |

| Set Block Lock-Bit    | 2                       |       | Write               | Х                   | XX60H                 | Write               | BA                  | XX01H                 |

| Clear Block Lock-Bits | 2                       | 8     | Write               | Х                   | XX60H                 | Write               | Х                   | XXD0H                 |

### Table 6. Basic Command Set Definitions<sup>(9)</sup>

NOTES:

1. Card signal values for the identified bus operations are defined in Table 5.

2. X = Any valid address within the device.

IA = Identifier Code Address:

BA = Address within the block being erased or locked.

WA = Address of memory location to be written.

SRD = Data read from Status Register.

WD = Data to be written at location WA. Data is latched on the rising edge of WE#.

ID = Data read from Identifier Codes.

4. The upper byte of the data bus during command writes is a "Don't Care" (X).

5. Following the Read Identifier Codes command, read operations access manufacturer, device, block lock, and master lock codes. See Read Identifier Section for read identifier code data.

6. Either XX40H or XX10H are recognized by the WSM as the word-write command setup.

7. The issue of a block erase or write-word command to a locked block will fail.

8. The clear block lock-bits operation simultaneously clears all block lock-bits.

9. Commands other than those shown above are reserved by Intel for future device implementations and should not be used.

## PRELIMINARY

#### 5.1.2 READ IDENTIFIER CODES COMMAND

The identifier code operation is initiated by writing the Read Identifier Codes command to a memory device. Following the command write, read cycles from addresses shown in Figure 3 retrieve the manufacturer, device, block lock configuration and master lock configuration codes (see Table 7 for identifier code values). To terminate the operation, write another valid command. The Read Identifier Codes command is valid only when the WSM is off or the device is suspended. Following the Read Identifier Codes command, the following information can be read:

|  | Table 7. | Identifier | Codes(1) |

|--|----------|------------|----------|

|--|----------|------------|----------|

| Co                               | de                          | Address(1)           | Data              |

|----------------------------------|-----------------------------|----------------------|-------------------|

| Manufacture C                    | ode                         | 00000                | (00) 89           |

| Device Code                      | Device Code 32-Mbit         |                      | (00) 14           |

|                                  | 64-Mbit                     | 00001                | (00) 15           |

| Block Lock Cor                   | nfiguration                 | X0002 <sup>(2)</sup> |                   |

| Block Is Unlo                    | cked                        |                      | $DQ_0 = 0$        |

| Block Is Lock                    | ed                          |                      | $DQ_0 = 1$        |

| Reserved for                     | Future Use                  |                      | DQ <sub>1-7</sub> |

| Master Lock C                    | onfiguration <sup>(3)</sup> | 00003                |                   |

| Device Is Un                     | locked                      |                      | $DQ_0 = 0$        |

| Device Is Loc                    | cked                        |                      | $DQ_0 = 1$        |

| <ul> <li>Reserved for</li> </ul> | Future Use                  |                      | DQ <sub>1-7</sub> |

NOTES:

1. Data is always presented on the low byte (upper byte contains 00h).

X selects the specific block's lock configuration code. See Figure 3 for the device identifier code memory map.

See 5 Volt Intel<sup>®</sup> StrataFlash<sup>™</sup> Memory; 28F320J5 and 28F640J5 datasheet for a description of Master Lock Configuration information. For 5 Volt Series 200 Miniature Cards the Master Lock Configuration byte should indicate that the device is unlocked (DQ<sub>0</sub> = 0).

#### 5.1.3 READ STATUS REGISTER COMMAND

The status register may be read to determine when a block erase, write, or lock-bit configuration operation is complete and whether the operation completed successfully. Table 8 defines the content and format of the status register. The register may be read at any time by writing the Read Status Register command. After writing this command, all subsequent read operations output data from the status register until another valid command is written. The status register contents are latched on the falling edge of OE# or the first edge of CEL# and CEH# that enables the device (see Table 5, Card Signal Values for the Card's Bus Operations and Modes). OE# must toggle to VIH or the device enter standby mode (Table 5) before further reads to update the status register latch.

During a word write, write to buffer, block erase, set lock-bit, or clear lock-bit command sequence, only SR.7 is valid until the Write State Machine completes or suspends the operation. Device I/O pins  $DQ_0$ – $DQ_6$  and  $DQ_8$ – $DQ_{15}$  are placed in a high-impedance state. When the operation completes or suspends (check Status Register bit 7), all contents of the Status Register are valid when read.

#### 5.1.4 CLEAR STATUS REGISTER COMMAND

Status register bits SR.5, SR.4, SR.3, and SR.1 are set to "1"s by the WSM and can only be reset by the Clear Status Register command. These bits indicate various failure conditions (see Table 8). By allowing system software to reset these bits, several operations (such as cumulatively erasing or locking of multiple blocks or writing of several bytes in sequence) may be performed. The status register may be polled to determine if an error occurred during the sequence.

To clear the status register, the Clear Status Register command (50H) is written. The Clear Status Register Command is only valid when the WSM is off or the device is suspended.