**Features**

## **EEPROM-Based System Monitors with Nonvolatile Fault Memory**

## **General Description**

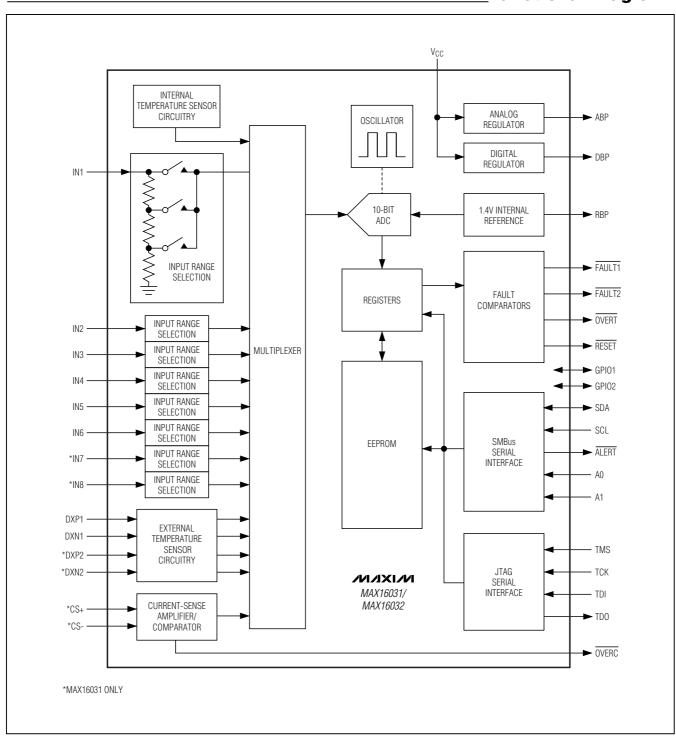

The MAX16031/MAX16032 EEPROM-configurable system monitors feature an integrated 10-bit analog-to-digital converter (ADC) designed to monitor voltages, temperatures, and current in complex systems. These EEPROM-configurable devices allow enormous flexibility in selecting operating ranges, upper and lower limits, fault output configuration, and operating modes with the capability of storing these values within the device.

The MAX16031 monitors up to eight voltages, three temperatures (one internal/two external remote temperature diodes), and a single current. The MAX16032 monitors up to six voltages and two temperatures (one internal/one remote temperature diode). Each of these monitored parameters is muxed into the ADC and written to its respective register that can be read back through the SMBus<sup>TM</sup> and JTAG interface.

Measured values are compared to the user-configurable upper and lower limits. For voltage measurements, there are two undervoltage and two overvoltage limits. For current and temperature, there are two sets of upper limits. Whenever the measured value is outside its limits, an alert signal is generated to notify the processor. Independent outputs are available for overcurrent, overtemperature, and undervoltage/overvoltage that are configured to assert on assigned channels. There are also undedicated fault outputs that are configured to offer a secondary limit for temperature, current, or voltage fault or provide a separate overvoltage output.

During a major fault event, such as a system shutdown, the MAX16031/MAX16032 automatically copy the internal ADC registers into the nonvolatile EEPROM registers that then are read back for diagnostic purposes.

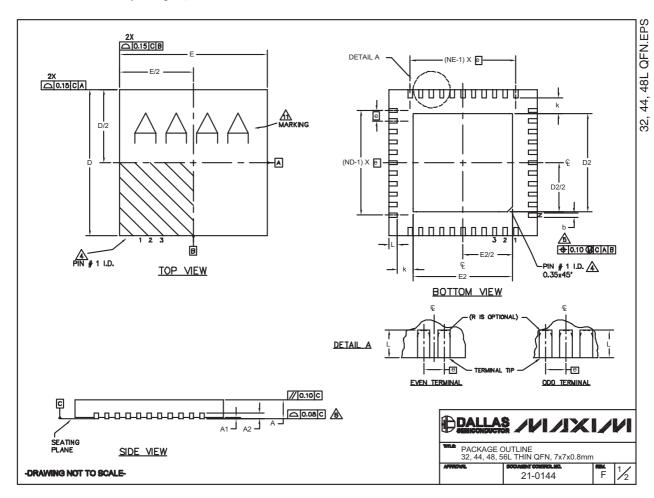

The MAX16031/MAX16032 offer additional GPIOs that are used for voltage sequencing, additional fault outputs, a manual reset input, or read/write logic levels. A separate current-sense amplifier with an independent output allows for fast shutoff during overcurrent conditions. The MAX16031/MAX16032 are available in a 7mm x 7mm TQFN package and are fully specified from -40°C to +85°C.

### **Applications**

Servers Workstations

Storage Systems Networking

Telecom

SMBus is a trademark of Intel Corp.

### ♦ Supply Voltage Operating Range of 2.85V to 14V

- ♦ Monitors Up to Eight Voltages (Single-Ended or Pseudo-Differential) with 1% Accuracy

- ♦ EEPROM-Configurable Limits

Two Undervoltage and Two Overvoltage

Two Overtemperature

Two Overcurrent

- High-Side Current-Sense Amplifier with Overcurrent Output (MAX16031 Only)

- ♦ Monitors Up to Three Temperatures (1 Internal/2 Remote)

- Nonvolatile Fault Memory Stores Fault Conditions for Later Retrieval

- **♦ Two Additional Configurable Fault Outputs**

- ♦ Two Configurable GPIOs

- ♦ SMBus/I<sup>2</sup>C-Compatible Interface with ALERT Output and Bus Timeout Function

- ♦ JTAG Interface

- ♦ 7mm x 7mm, 48-Pin TQFN Package

## **Ordering Information**

| PART                 | PART TEMP RANGE |             | PKG<br>CODE |  |

|----------------------|-----------------|-------------|-------------|--|

| MAX16031ETM+         | -40°C to +85°C  | 48 TQFN-EP* | T4877-6     |  |

| <b>MAX16032</b> ETM+ | -40°C to +85°C  | 48 TQFN-EP* | T4877-6     |  |

<sup>+</sup>Denotes a lead-free package.

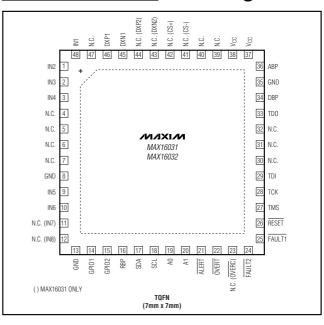

## **Pin Configuration**

Maxim Integrated Products

<sup>\*</sup>EP = Exposed paddle.

### **Selector Guide**

| PART         | VOLTAGE      | MONITORS     | TEMPERATU | RE SENSORS | CURRENT-   | FAULT   | GPIOs |

|--------------|--------------|--------------|-----------|------------|------------|---------|-------|

| FARI         | SINGLE ENDED | DIFFERENTIAL | INT       | EXT        | SENSE AMPS | OUTPUTS | GFIOS |

| MAX16031ETM+ | 8            | 4            | 1         | 2          | 1          | 4       | 2     |

| MAX16032ETM+ | 6            | 3            | 1         | 1          | _          | 4       | 2     |

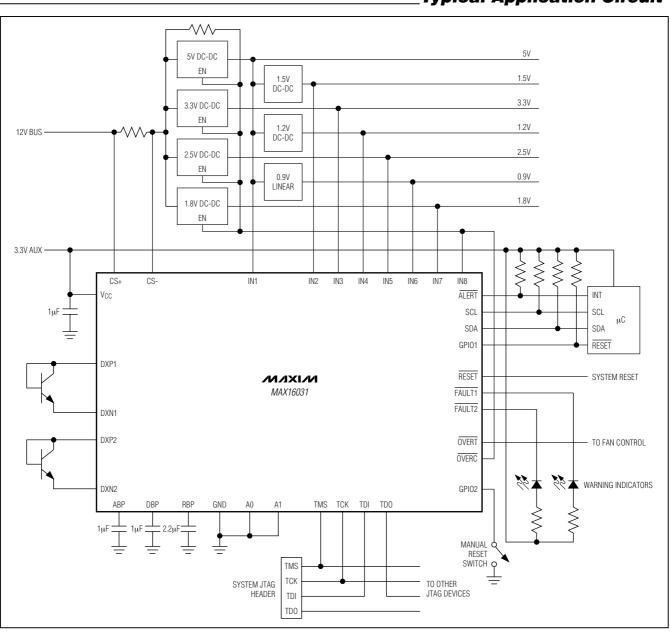

## **Typical Application Circuit**

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND                                               | Input/Output Current (all except DXN1, DXN2, SDA, and ALERT)20mA Continuous Power Dissipation (T <sub>A</sub> = +70°C) 48-Pin, 7mm x 7mm TQFN |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| RBP, ABP, DBP to GND0.3V to lower of (6V and V <sub>CC</sub> + 0.3V) | (derate 27.8mW/°C above +70°C)2222.2mW                                                                                                        |

| TDO, DXP1, DXP2 to GND0.3V to V <sub>DBP</sub> + 0.3V                | Operating Temperature Range40°C to +85°C                                                                                                      |

| CS+, CS- to GND0.3V to +30V                                          | Junction Temperature+150°C                                                                                                                    |

| (CS+ - CS-)±5V                                                       | Storage Temperature Range65°C to +150°C                                                                                                       |

| DXN1, DXN2 to GND0.3V to +0.8V                                       | Lead Temperature (soldering, 10s)+250°C                                                                                                       |

| SDA, ALERT Current1mA to +50mA                                       | , , , , , , , , , , , , , , , , , , , ,                                                                                                       |

| DXN1, DXN2 Current1mA                                                |                                                                                                                                               |

|                                                                      |                                                                                                                                               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.9 \text{V to } 14 \text{V}, T_A = -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are at } V_{CC} = 3.3 \text{V}, T_A = +25 ^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                        | SYMBOL             | CONDITIONS                                                          | MIN   | TYP | MAX   | UNITS |

|--------------------------------------------------|--------------------|---------------------------------------------------------------------|-------|-----|-------|-------|

| Operating Voltage Range                          | Vcc                |                                                                     | 2.90  |     | 14.00 | V     |

| Undervoltage Lockout                             | V <sub>U</sub> VLO | Minimum voltage at V <sub>CC</sub> to access the digital interfaces |       |     | 2.8   | V     |

| Undervoltage Lockout Hysteresis                  | Vuvlohys           |                                                                     |       | 100 |       | mV    |

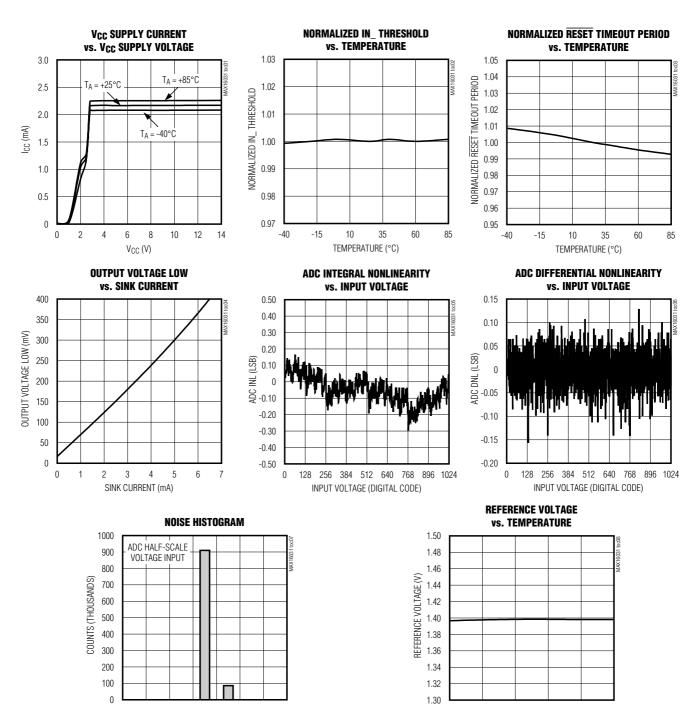

| Supply Current                                   | Icc                | Static (EEPROM not accessed)                                        |       | 3   | 5     | mA    |

| ADC DC ACCURACY                                  |                    |                                                                     |       |     |       |       |

| Resolution                                       |                    |                                                                     |       |     | 10    | Bits  |

| Total Unadjusted Error                           |                    | $T_A = -40$ °C to $+85$ °C                                          |       |     | 0.9   | % FSR |

| Integral Nonlinearity                            |                    |                                                                     |       | 1   |       | LSB   |

| Differential Nonlinearity                        |                    |                                                                     |       | 1   |       | LSB   |

| ADC Total Monitoring Cycle Time                  | tcycle             | Eight supply inputs, three temperatures, and current sense          |       | 80  | 100   | μs    |

|                                                  |                    | Register map bit set to 00 (LSB = 5.46mV)                           |       | 5.6 |       |       |

| ADC IN_ Voltage Ranges                           |                    | Register map bit set to 01 (LSB = 2.73mV)                           |       | 2.8 |       | V     |

|                                                  |                    | Register map bit set to 10 (LSB = 1.36mV)                           |       | 1.4 |       |       |

| Reference Voltage                                | V <sub>RBP</sub>   |                                                                     | 1.306 | 1.4 | 1.414 | V     |

| IN_ ANALOG INPUT                                 |                    |                                                                     |       |     |       |       |

| Absolute Input Voltage Range (Referenced to GND) |                    |                                                                     | 0     |     | 5.6   | V     |

| Input Impedance                                  |                    |                                                                     | 30    | 50  | 80    | kΩ    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.9V \text{ to } 14V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $V_{CC} = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                              | SYMBOL            | CONDITIONS                                   | }           | MIN  | TYP  | MAX  | UNITS |

|--------------------------------------------------------|-------------------|----------------------------------------------|-------------|------|------|------|-------|

|                                                        |                   | Percent of programmed                        | r5Ch[5] = 0 |      | 0.78 |      | 0/    |

| Input Hysteresis                                       |                   | threshold                                    | r5Ch[5] = 1 |      | 1.17 |      | %     |

| RESET OUTPUT                                           |                   |                                              |             |      |      |      |       |

|                                                        |                   | $r20h[5:3] = 000$ ; from $\overline{MR}$ goi | ng high     | 22.5 | 25   | 27.5 | μs    |

|                                                        | :                 | r20h[5:3]= 001                               |             | 2.25 | 2.5  | 2.75 |       |

|                                                        |                   | r20h[5:3]= 010                               |             | 9    | 10   | 11   |       |

| D 17 10 11                                             |                   | r20h[5:3]= 011                               |             | 36   | 40   | 44   |       |

| Reset Timeout Period                                   | t <sub>RP</sub>   | r20h[5:3]= 100                               |             | 144  | 160  | 176  | ms    |

|                                                        |                   | r20h[5:3]= 101                               |             | 576  | 640  | 704  |       |

|                                                        |                   | r20h[5:3]= 110                               |             | 1152 | 1280 | 1408 |       |

|                                                        |                   | r20h[5:3]= 111                               |             | 2304 | 2560 | 2816 |       |

| TEMPERATURE MEASUREMENT                                | S                 |                                              |             |      |      |      |       |

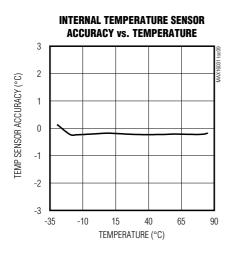

| Internal Sensor Measurement<br>Error                   |                   | (Note 2)                                     |             |      | ±3   |      | °C    |

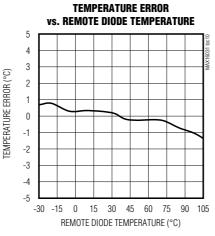

| External Remote Diode<br>Temperature Measurement Error |                   | (Note 2)                                     |             |      | ±5   |      | °C    |

| Temperature Measurement<br>Resolution                  |                   |                                              |             |      | 0.5  |      | °C    |

| Temperature Measurement Noise                          |                   | Internal sensor                              |             |      | 0.1  |      | °C    |

| External Diode Drive High                              |                   |                                              |             |      | 84   |      | μΑ    |

| External Diode Drive Low                               |                   |                                              |             |      | 6    |      | μA    |

| Diode Drive Current Ratio                              |                   |                                              |             |      | 14   |      |       |

| DXN_ Impedance to GND                                  |                   |                                              |             |      | 1.8  |      | kΩ    |

| Power-Supply Rejection                                 | PSR               | Internal sensor, DC condition                | l           |      | 0.1  |      | °C/V  |

| CURRENT SENSE                                          |                   |                                              |             |      |      |      | •     |

| CS+ Input Voltage Range                                | V <sub>CS+</sub>  |                                              |             | 3    |      | 28   | V     |

| Input Diag Current                                     | I <sub>CS+</sub>  | $V_{CS+} = V_{CS-}$                          |             |      | 14   | 25   |       |

| Input Bias Current                                     | Ics-              | $V_{CS-} = V_{CS+}$                          |             |      | 3    | 8    | μA    |

|                                                        |                   |                                              | A = 48      | 21.5 | 25   | 28.5 |       |

| Primary Current-Sense                                  | Voot              | V <sub>CS+</sub> - V <sub>CS-</sub>          | A = 24      | 45   | 50   | 55   | m\/   |

| Differential Thresholds                                | Vcsth             | VUS+ = VUS-                                  | A = 12      | 92   | 100  | 108  | mV    |

|                                                        |                   |                                              | A = 6       | 190  | 200  | 210  |       |

| Primary Current-Sense Threshold                        | CS <sub>HYS</sub> | Percent of V <sub>CSTH</sub>                 |             |      | 0.5  |      | %     |

|                                                        |                   | r5Ch[1:0] = 00                               |             |      | 50   |      | μs    |

| Secondary Overcurrent                                  |                   | r5Ch[1:0] = 01                               |             | 3.6  | 4    | 4.4  | _     |

| Threshold Timeout                                      |                   | r5Ch[1:0] = 10                               |             | 14.4 | 16   | 17.6 | ms    |

|                                                        |                   | r5Ch[1:0] = 11                               |             | 57.6 | 64   | 70.4 |       |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.9V \text{ to } 14V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise specified. Typical values are at } V_{CC} = 3.3V, T_A = +25^{\circ}\text{C.})$  (Note 1)

| PARAMETER                                      | SYMBOL          | CONDITIONS                                                           |                    | MIN | TYP  | MAX | UNITS   |

|------------------------------------------------|-----------------|----------------------------------------------------------------------|--------------------|-----|------|-----|---------|

|                                                |                 |                                                                      | A = 6              | İ   | 232  |     |         |

| Current-Sense Analog Input                     |                 | M. M.                                                                | A = 12             |     | 116  |     |         |

| Range                                          |                 | V <sub>CS+</sub> - V <sub>CS-</sub>                                  | A = 24             |     | 58   |     | mV      |

| <u> </u>                                       |                 |                                                                      | A = 48             |     | 29   |     | <u></u> |

|                                                |                 | VSENSE = 150mV, (A = 6 only)                                         |                    | -4  | ±0.2 | +4  |         |

| ADC Current-Sense                              |                 | V <sub>SENSE</sub> = 50mV, (A = 6, 12 only)                          | )                  | -10 | ±1.2 | +10 | %       |

| Measurement Accuracy                           |                 | V <sub>SENSE</sub> = 25mV                                            |                    |     | ±2   |     | 70      |

|                                                |                 | V <sub>SENSE</sub> = 10mV                                            |                    |     | ±10  |     |         |

| Gain Accuracy                                  |                 | V <sub>SENSE</sub> = 20mV to 100mV,<br>V <sub>CS+</sub> = 12V, A = 6 |                    | -3  |      | +3  | %       |

| Common-Mode Rejection Ratio                    | CMRRCS          | V <sub>CS+</sub> > 4V                                                |                    |     | 80   |     | dB      |

| Power-Supply Rejection Ratio                   | PSRRCS          |                                                                      |                    |     | 80   |     | dB      |

| OVERC Output Leakage Current                   | IOVERCLKG       |                                                                      |                    |     |      | 1   | μΑ      |

| OVERC Output Low Voltage                       | Voloverc        | I <sub>OUT</sub> = 3mA                                               |                    |     |      | 0.4 | V       |

| OVERC Propagation Delay                        | toverc          | VSENSE - VCSTH > 10% x VCSTH                                         |                    |     |      | 5   | μs      |

| SMBus INTERFACE (SCL, SDA)                     |                 |                                                                      |                    |     |      |     |         |

| Logic-Input Low Voltage                        | VIL             | Input voltage falling                                                |                    |     |      | 0.8 | V       |

| Logic-Input High Voltage                       | V <sub>IH</sub> | Input voltage rising                                                 |                    | 2.0 |      |     | V       |

| Input Leakage Current                          |                 | GND or 5.5V (V <sub>CC</sub> = 5.5V) V <sub>SCL</sub>                | , V <sub>SDA</sub> | -1  |      | +1  | μΑ      |

| Output Low Voltage                             | V <sub>OL</sub> | I <sub>SINK</sub> = 3mA                                              |                    |     |      | 0.4 | V       |

| Input Capacitance                              | CIN             |                                                                      |                    |     | 5    |     | рF      |

| ALERT, FAULT_, AND GPIO_ OU                    | TPUTS           |                                                                      |                    | _   |      |     |         |

| ALERT, FAULT_, and GPIO_<br>Output Low Voltage |                 | ISINK = 3mA                                                          |                    |     |      | 0.4 | V       |

| ALERT, FAULT_, and GPIO_<br>Leakage Current    |                 | VALERT, VFAULT, VGPIO_ = 5.5V                                        | or GND             | -1  |      | +1  | μΑ      |

| GPIO_ (INPUT)                                  |                 |                                                                      |                    |     |      |     |         |

| Logic-Low Voltage                              |                 | GPIO_ voltage falling                                                |                    |     |      | 0.8 | V       |

| Logic-High Voltage                             |                 | GPIO_ voltage rising                                                 |                    | 2.0 |      |     | V       |

| SMBus ADDRESS (A0 and A1)                      |                 |                                                                      |                    |     |      |     |         |

| Address Logic-Low                              |                 |                                                                      |                    |     |      | 0.4 | V       |

| Address Logic-High                             |                 |                                                                      |                    | 1.4 |      |     | V       |

| High-Impedance Leakage<br>Current              |                 | Maximum current to achieve hig impedance logic level                 | h-                 | -1  |      | +1  | μΑ      |

| Input Leakage Current                          |                 | 0 to 3V, V <sub>CC</sub> = 3V                                        |                    | -12 |      | +12 | μΑ      |

| -                                              | 1               | l .                                                                  |                    | 1   |      |     |         |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.9V \text{ to } 14V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $V_{CC} = 3.3V, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                       | SYMBOL            | CONDITIONS                         | MIN      | TYP | MAX  | UNITS |

|-------------------------------------------------|-------------------|------------------------------------|----------|-----|------|-------|

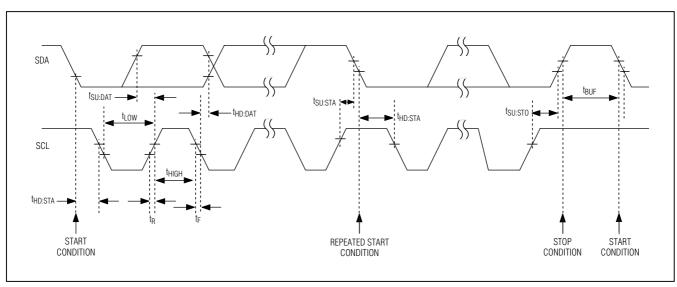

| SMBus TIMING (see Figure 1)                     | l.                |                                    | <b>'</b> |     |      | l     |

| Serial-Clock Frequency                          | fSCL              |                                    |          |     | 400  | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF              |                                    | 1.3      |     |      | μs    |

| START Condition Setup Time                      | tsu:sta           |                                    | 0.6      |     |      | μs    |

| START Condition Hold Time                       | thd:STA           |                                    | 0.6      |     |      | μs    |

| STOP Condition Setup Time                       | tsu:sto           |                                    | 0.6      |     |      | μs    |

| Clock Low Period                                | tLOW              |                                    | 1.3      |     |      | μs    |

| Clock High Period                               | thigh             |                                    | 0.6      |     |      | μs    |

| Data Setup Time                                 | tsu:DAT           |                                    | 100      |     |      | ns    |

| Output Fall Time                                | tof               | C <sub>BUS</sub> = 10pF to 400pF   |          |     | 250  | ns    |

| Data Hold Time                                  | thd:dat           | From 50% SCL falling to SDA change | 0.3      |     | 0.9  | μs    |

| Minimum Pulse Width Ignored                     |                   |                                    |          | 30  |      | ns    |

| SMBus Timeout                                   | †TIMEOUT          | SCL time low for reset             | 25       |     | 35   | ms    |

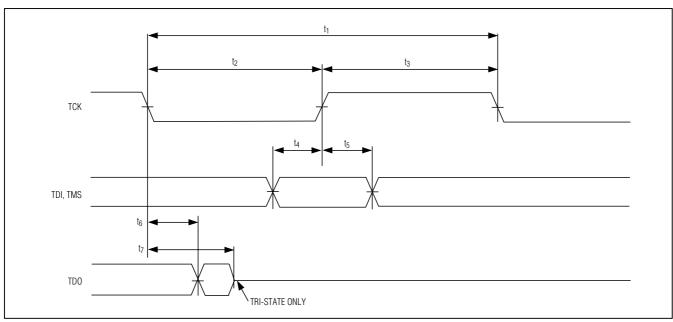

| JTAG INTERFACE (see Figure 2)                   |                   |                                    |          |     |      |       |

| TDI, TMS, TCK Logic-Low Input<br>Voltage        | V <sub>IL</sub>   | Input voltage falling              |          |     | 0.4  | ٧     |

| TDI, TMS, TCK Logic-High Input<br>Voltage       | V <sub>IH</sub>   | Input voltage rising               | 2.2      |     |      | ٧     |

| TDO Logic-Output Low Voltage                    | V <sub>OL</sub>   | ISINK = 4mA                        |          |     | 0.4  | V     |

| TDO Logic-Output High Voltage                   | Voh               | ISOURCE = 1mA                      | 2.2      |     |      | V     |

| TDO Leakage Current                             |                   | TDO high impedance                 | -10      |     | +10  | μΑ    |

| TDI, TMS Pullup Resistors                       | R <sub>JPU</sub>  | Pullup to V <sub>DBP</sub>         | 6.5      | 10  | 16   | kΩ    |

| I/O Capacitance                                 | C <sub>I/O</sub>  |                                    |          | 50  |      | рF    |

| TCK Clock Period                                | t <sub>1</sub>    |                                    |          |     | 1000 | ns    |

| TCK High/Low Time                               | t2, t3            | (Note 3)                           | 60       | 500 |      | ns    |

| TCK to TMS, TDI Setup Time                      | t <sub>4</sub>    |                                    | 15       |     |      | ns    |

| TCK to TMS, TDI Hold Time                       | t <sub>5</sub>    |                                    | 35       |     |      | ns    |

| TCK to TDO Delay                                | t <sub>6</sub>    |                                    |          |     | 500  | ns    |

| TCK to TDO High-Impedance<br>Delay              | t <sub>7</sub>    |                                    |          | _   | 500  | ns    |

| MISCELLANEOUS                                   | •                 | •                                  | •        |     |      | •     |

| Power-On Delay                                  | t <sub>D-PO</sub> |                                    |          |     | 4    | ms    |

| Single-Byte EEPROM Write Cycle<br>Delay         |                   | (Note 4)                           |          |     | 11   | ms    |

Note 1: Limits to -40°C are guaranteed by design.

Note 2: Guaranteed by design.

Note 3: TCK stops either high or low.

Note 4: An additional cycle is required when writing to configuration memory for the first time.

Figure 1. SMBus Interface Timing Diagram

Figure 2. JTAG Interface Timing Diagram

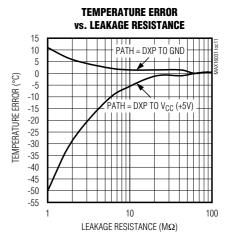

## **Typical Operating Characteristics**

(Typical values are at V<sub>CC</sub> = 3.3V, T<sub>A</sub> = +25°C, unless otherwise noted.)

-40

-15

TEMPERATURE (°C)

60

507 508 509 510 511 512 513

ADC OUTPUT CODE

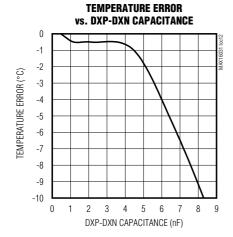

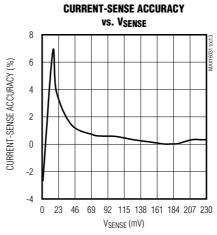

## Typical Operating Characteristics (continued)

(Typical values are at  $V_{CC} = 3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

## Pin Description

| Р                                 | PIN                                                 |       |                                                                                                                                                                                                                                                                                                  |

|-----------------------------------|-----------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16031                          | MAX16032                                            | NAME  | FUNCTION                                                                                                                                                                                                                                                                                         |

| 1                                 | 1                                                   | IN2   | Supply Monitor Input 2. IN2 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN1 and IN2 form the + and - of the differential pair. Each input must stay within the specified ADC IN_voltage range.  |

| 2                                 | 2                                                   | IN3   | Supply Monitor Input 3. IN3 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN3 and IN4 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| 3                                 | 3                                                   | IN4   | Supply Monitor Input 4. IN4 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN3 and IN4 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| 4–7, 30, 31,<br>32, 39, 40,<br>47 | 4–7, 11, 12,<br>23, 30, 31,<br>32, 39,<br>40–44, 47 | N.C.  | No Connection. Leave unconnected. Do not use.                                                                                                                                                                                                                                                    |

| 8, 13, 35                         | 8, 13, 35                                           | GND   | Ground. Connect all GND pins together.                                                                                                                                                                                                                                                           |

| 9                                 | 9                                                   | IN5   | Supply Monitor Input 5. IN5 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN5 and IN6 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| 10                                | 10                                                  | IN6   | Supply Monitor Input 6. IN6 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN5 and IN6 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| 11                                | _                                                   | IN7   | Supply Monitor Input 7. IN7 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN7 and IN8 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| 12                                | _                                                   | IN8   | Supply Monitor Input 8. IN8 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN7 and IN8 form the + and - of the differential pair. Each input must stay within the specified ADC IN_voltage range.  |

| 14                                | 14                                                  | GPIO1 | Configurable General-Purpose Input/Output 1                                                                                                                                                                                                                                                      |

| 15                                | 15                                                  | GPIO2 | Configurable General-Purpose Input/Output 2                                                                                                                                                                                                                                                      |

| 16                                | 16                                                  | RBP   | ADC Reference Bypass. RBP is an internally generated 1.4V reference for the ADC. Bypass RBP to GND with a 2.2µF capacitor. Do not use RBP to power any additional circuitry.                                                                                                                     |

| 17                                | 17                                                  | SDA   | SMBus Serial-Data, Open-Drain Input/Output                                                                                                                                                                                                                                                       |

| 18                                | 18                                                  | SCL   | SMBus Serial-Clock Input                                                                                                                                                                                                                                                                         |

| 19                                | 19                                                  | A0    | SMBus Address Input 0. Connect to DBP, GND, or leave unconnected to select the desired device address.                                                                                                                                                                                           |

| 20                                | 20                                                  | A1    | SMBus Address Input 1. Connect to DBP, GND, or leave unconnected to select the desired device address.                                                                                                                                                                                           |

## Pin Description (continued)

| Г        |          |        |                                                                                                                                                                                                                                                                                                  |

|----------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | PIN      | NAME   | FUNCTION                                                                                                                                                                                                                                                                                         |

| MAX16031 | MAX16032 |        |                                                                                                                                                                                                                                                                                                  |

| 21       | 21       | ALERT  | SMBus Alert Open-Drain Output. ALERT follows the SMBALERT# signal functionality described in Appendix A of the SMBus 2.0 Specification. ALERT asserts when the device detects a fault, thereby interrupting the host processor to query which device on the serial bus detected faults.          |

| 22       | 22       | OVERT  | Overtemperature, Open-Drain Output. OVERT asserts when an overtemperature condition is detected.                                                                                                                                                                                                 |

| 23       | _        | OVERC  | Overcurrent, Open-Drain Output. OVERC asserts when the primary overcurrent threshold is exceeded.                                                                                                                                                                                                |

| 24       | 24       | FAULT2 | Configurable Open-Drain Fault Output 2                                                                                                                                                                                                                                                           |

| 25       | 25       | FAULT1 | Configurable Open-Drain Fault Output 1                                                                                                                                                                                                                                                           |

| 26       | 26       | RESET  | Configurable Open-Drain Reset Output                                                                                                                                                                                                                                                             |

| 27       | 27       | TMS    | JTAG Test Mode Select Input. Internally pulled up to VDBP with a 10kΩ resistor.                                                                                                                                                                                                                  |

| 28       | 28       | TCK    | JTAG Test Clock Input                                                                                                                                                                                                                                                                            |

| 29       | 29       | TDI    | JTAG Test Data Input. Internally pulled up to VDBP with a $10k\Omega$ resistor.                                                                                                                                                                                                                  |

| 33       | 33       | TDO    | JTAG Test Data Output                                                                                                                                                                                                                                                                            |

| 34       | 34       | DBP    | Internal Digital Voltage Regulator Output. Connect a 1µF bypass capacitor from DBP to GND. Do not use DBP to power external circuitry.                                                                                                                                                           |

| 36       | 36       | ABP    | Internal Analog Voltage Regulator Output. Connect a 1µF bypass capacitor from ABP to GND. Do not use ABP to power external circuitry.                                                                                                                                                            |

| 37, 38   | 37, 38   | Vcc    | Device Power Supply. Bypass VCC to GND with a 1µF capacitor.                                                                                                                                                                                                                                     |

| 41       | 41       | CS-    | Current-Sense Negative Input. Must be biased between 3V to 28V for proper operation.                                                                                                                                                                                                             |

| 42       | 42       | CS+    | Current-Sense Positive Input. Must be biased between 3V to 28V for proper operation.                                                                                                                                                                                                             |

| 43       | _        | DXN2   | Remote Diode 2 Negative Input. If remote sensing is not used, connect DXP2 to DXN2.                                                                                                                                                                                                              |

| 44       | _        | DXP2   | Remote Diode 2 Positive Input. If remote sensing is not used, connect DXP2 to DXN2.                                                                                                                                                                                                              |

| 45       | 45       | DXN1   | Remote Diode 1 Negative Input. If remote sensing is not used, connect DXP1 to DXN1.                                                                                                                                                                                                              |

| 46       | 46       | DXP1   | Remote Diode 1 Positive Input. If remote sensing is not used, connect DXP1 to DXN1.                                                                                                                                                                                                              |

| 48       | 48       | IN1    | Supply Monitor Input 1. IN1 is internally sampled by the ADC. It is configurable for unipolar/bipolar and single-ended/pseudo-differential. In pseudo-differential mode, IN1 and IN2 form the + and - of the differential pair. Each input must stay within the specified ADC IN_ voltage range. |

| _        | _        | EP     | Exposed Paddle. Connect EP to ground. EP is internally connected to GND. Do not use as the main ground connection.                                                                                                                                                                               |

## **Functional Diagram**

**Table 1. Address Map**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | READ/<br>WRITE | DESCRIPTION                                                                                                      |

|---------------------|-----------------------------|----------------|------------------------------------------------------------------------------------------------------------------|

| 00h                 | _                           | R              | IN1 ADC Result Register (MSB)                                                                                    |

| 01h                 | _                           | R              | IN1 ADC Result Register (LSB)                                                                                    |

| 02h                 | _                           | R              | IN2 ADC Result Register (MSB)                                                                                    |

| 03h                 | _                           | R              | IN2 ADC Result Register (LSB)                                                                                    |

| 04h                 | _                           | R              | IN3 ADC Result Register (MSB)                                                                                    |

| 05h                 | _                           | R              | IN3 ADC Result Register (LSB)                                                                                    |

| 06h                 | _                           | R              | IN4 ADC Result Register (MSB)                                                                                    |

| 07h                 | _                           | R              | IN4 ADC Result Register (LSB)                                                                                    |

| 08h                 | _                           | R              | IN5 ADC Result Register (MSB)                                                                                    |

| 09h                 | _                           | R              | IN5 ADC Result Register (LSB)                                                                                    |

| 0Ah                 | _                           | R              | IN6 ADC Result Register (MSB)                                                                                    |

| 0Bh                 | _                           | R              | IN6 ADC Result Register (LSB)                                                                                    |

| 0Ch                 | _                           | R              | IN7 ADC Result Register (MSB)*                                                                                   |

| 0Dh                 | _                           | R              | IN7 ADC Result Register (LSB)*                                                                                   |

| 0Eh                 | _                           | R              | IN8 ADC Result Register (MSB)*                                                                                   |

| 0Fh                 | _                           | R              | IN8 ADC Result Register (LSB)*                                                                                   |

| 10h                 | _                           | R              | Internal Temperature Sensor ADC Result Register (MSB)                                                            |

| 11h                 | _                           | R              | Internal Temperature Sensor ADC Result Register (LSB)                                                            |

| 12h                 | _                           | R              | Remote Temperature Sensor 1 ADC Result Register (MSB)                                                            |

| 13h                 | _                           | R              | Remote Temperature Sensor 1 ADC Result Register (LSB)                                                            |

| 14h                 | _                           | R              | Remote Temperature Sensor 2 ADC Result Register (MSB)                                                            |

| 15h                 | _                           | R              | Remote Temperature Sensor 2 ADC Result Register (LSB)                                                            |

| 16h                 | _                           | R              | Current-Sense ADC Result Register                                                                                |

| 17h                 | 97h                         | R/W            | Voltage Monitoring Input ADC Range Selection (IN1–IN4)                                                           |

| 18h                 | 98h                         | R/W            | Voltage Monitoring Input ADC Range Selection (IN5–IN8)                                                           |

| 19h                 | 99h                         | R/W            | Current-Sense Gain/Primary Threshold and Remote Temperature Sensor 1 Gain Trim                                   |

| 1Ah                 | 9Ah                         | R/W            | Voltage Monitoring Input Enable                                                                                  |

| 1Bh                 | 9Bh                         | R/W            | Internal/Remote Temperature Sensor, Current Sense, and ALERT Enables and Remote Temperature Sensor 1 Offset Trim |

| 1Ch                 | 9Ch                         | R/W            | Voltage Monitoring Input Single-Ended/Differential and Unipolar/Bipolar Selection                                |

| 1Dh                 | 9Dh                         | R/W            | FAULT1 Dependency Selection                                                                                      |

| 1Eh                 | 9Eh                         | R/W            | FAULT2 Dependency Selection                                                                                      |

| 1Fh                 | 9Fh                         | R/W            | OVERT Dependency Selection                                                                                       |

| 20h                 | A0h                         | R/W            | RESET Dependency and Timeout Selection                                                                           |

| 21h                 | A1h                         | R/W            | RESET IN1-IN8 Dependency Selection                                                                               |

| 22h                 | A2h                         | R/W            | GPIO1 Configuration                                                                                              |

| 23h                 | A3h                         | R/W            | GPIO1 Dependency Selection                                                                                       |

| 24h                 | A4h                         | R/W            | GPIO2 Configuration                                                                                              |

**Table 1. Address Map (continued)**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | READ/<br>WRITE | DESCRIPTION                                                           |

|---------------------|-----------------------------|----------------|-----------------------------------------------------------------------|

| 25h                 | A5h                         | R/W            | GPIO2 Dependency Selection                                            |

| 26h                 | A6h                         | R/W            | IN1 Primary Undervoltage Threshold                                    |

| 27h                 | A7h                         | R/W            | IN1 Primary Overvoltage Threshold                                     |

| 28h                 | A8h                         | R/W            | IN1 Secondary Undervoltage Threshold                                  |

| 29h                 | A9h                         | R/W            | IN1 Secondary Overvoltage Threshold                                   |

| 2Ah                 | AAh                         | R/W            | IN2 Primary Undervoltage Threshold                                    |

| 2Bh                 | ABh                         | R/W            | IN2 Primary Overvoltage Threshold                                     |

| 2Ch                 | ACh                         | R/W            | IN2 Secondary Undervoltage Threshold                                  |

| 2Dh                 | ADh                         | R/W            | IN2 Secondary Overvoltage Threshold                                   |

| 2Eh                 | AEh                         | R/W            | IN3 Primary Undervoltage Threshold                                    |

| 2Fh                 | AFh                         | R/W            | IN3 Primary Overvoltage Threshold                                     |

| 30h                 | B0h                         | R/W            | IN3 Secondary Undervoltage Threshold                                  |

| 31h                 | B1h                         | R/W            | IN3 Secondary Overvoltage Threshold                                   |

| 32h                 | B2h                         | R/W            | IN4 Primary Undervoltage Threshold                                    |

| 33h                 | B3h                         | R/W            | IN4 Primary Overvoltage Threshold                                     |

| 34h                 | B4h                         | R/W            | IN4 Secondary Undervoltage Threshold                                  |

| 35h                 | B5h                         | R/W            | IN4 Secondary Overvoltage Threshold                                   |

| 36h                 | B6h                         | R/W            | IN5 Primary Undervoltage Threshold                                    |

| 37h                 | B7h                         | R/W            | IN5 Primary Overvoltage Threshold                                     |

| 38h                 | B8h                         | R/W            | IN5 Secondary Undervoltage Threshold                                  |

| 39h                 | B9h                         | R/W            | IN5 Secondary Overvoltage Threshold                                   |

| 3Ah                 | BAh                         | R/W            | IN6 Primary Undervoltage Threshold                                    |

| 3Bh                 | BBh                         | R/W            | IN6 Primary Overvoltage Threshold                                     |

| 3Ch                 | BCh                         | R/W            | IN6 Secondary Undervoltage Threshold                                  |

| 3Dh                 | BDh                         | R/W            | IN6 Secondary Overvoltage Threshold                                   |

| 3Eh                 | BEh                         | R/W            | IN7 Primary Undervoltage Threshold*                                   |

| 3Fh                 | BFh                         | R/W            | IN7 Primary Overvoltage Threshold*                                    |

| 40h                 | C0h                         | R/W            | IN7 Secondary Undervoltage Threshold*                                 |

| 41h                 | C1h                         | R/W            | IN7 Secondary Overvoltage Threshold*                                  |

| 42h                 | C2h                         | R/W            | IN8 Primary Undervoltage Threshold*                                   |

| 43h                 | C3h                         | R/W            | IN8 Primary Overvoltage Threshold*                                    |

| 44h                 | C4h                         | R/W            | IN8 Secondary Undervoltage Threshold*                                 |

| 45h                 | C5h                         | R/W            | IN8 Secondary Overvoltage Threshold*                                  |

| 46h                 | C6h                         | R/W            | Internal Temperature Sensor Primary Overtemperature Threshold (MSB)   |

| 47h                 | C7h                         | R/W            | Internal Temperature Sensor Secondary Overtemperature Threshold (MSB) |

| 48h                 | C8h                         | R/W            | Remote Temperature Sensor 1 Primary Overtemperature Threshold         |

| 49h                 | C9h                         | R/W            | Remote Temperature Sensor 1 Secondary Overtemperature Threshold       |

| 4Ah                 | CAh                         | R/W            | Remote Temperature Sensor 2 Primary Overtemperature Threshold         |

**Table 1. Address Map (continued)**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | READ/<br>WRITE | DESCRIPTION                                                                                                             |

|---------------------|-----------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------|

| 4Bh                 | CBh                         | R/W            | Remote Temperature Sensor 2 Secondary Overtemperature Threshold                                                         |

| 4Ch                 | CCh                         | R/W            | Overcurrent Secondary Threshold                                                                                         |

| 4Dh                 |                             |                | Remote Temperature Sensor Primary/Secondary Overtemperature Threshold (LSBs). External Temperature Sensor 2 Offset Trim |

| 4Eh                 | CEh                         | R/W            | Remote Temperature Sensor 1/2 Primary/Secondary Overtemperature Threshold (LSBs)                                        |

| 4Fh                 | CFh                         | R/W            | Remote Temperature Sensor 2 Gain Trim                                                                                   |

| 50h                 | D0h                         | R/W            | Remote Temperature Sensor Short/Open Status                                                                             |

| 51h                 | D1h                         | R/W            | IN1-IN8 Primary Threshold Fault Status                                                                                  |

| 52h                 | D2h                         | R/W            | IN1-IN8 Secondary Threshold Fault Status                                                                                |

| 53h                 | D3h                         | R/W            | Temperature/Current Threshold Fault Status                                                                              |

| 54h                 | D4h                         | R/W            | Remote Temperature Sensor Short/Open Fault Mask                                                                         |

| 55h                 | D5h                         | R/W            | IN1-IN8 Primary Threshold Fault Mask                                                                                    |

| 56h                 | D6h                         | R/W            | IN1-IN8 Secondary Threshold Fault Mask                                                                                  |

| 57h                 | D7h                         | R/W            | Temperature/Current Threshold Fault Mask                                                                                |

| 58h                 | D8h                         | R/W            | IN1-IN8 Primary Undervoltage Faults Triggering Fault EEPROM                                                             |

| 59h                 | D9h                         | R/W            | IN1-IN8 Primary Overvoltage Faults Triggering Fault EEPROM                                                              |

| 5Ah                 | DAh                         | R/W            | Temperature/Current Faults Triggering Fault EEPROM                                                                      |

| 5Bh                 | DBh                         | R/W            | Temperature Filter Selection and Postboot Fault Mask Time                                                               |

| 5Ch                 | DCh                         | R/W            | Threshold Fault Options and Overcurrent Fault Timeout                                                                   |

| 5Dh                 | DDh                         | _              | Reserved                                                                                                                |

| 5Eh                 | DEh                         | R/W            | Customer Firmware Version                                                                                               |

| 5Fh                 | DFh                         | R/W            | EEPROM and Configuration Lock                                                                                           |

| 60h-7Fh             | E0h-FFh                     | _              | Reserved                                                                                                                |

| _                   | 80h                         | R              | IN1-IN8 Primary Threshold Fault Status at Time of Fault                                                                 |

| _                   | 81h                         | R              | IN1–IN8 Secondary Threshold Fault Status at Time of Fault                                                               |

| _                   | 82h                         | R              | Temperature/Current Threshold Fault Status at Time of Fault                                                             |

| _                   | 83h                         | R              | IN1 Conversion Result at Time of Fault                                                                                  |

| _                   | 84h                         | R              | IN2 Conversion Result at Time of Fault                                                                                  |

| _                   | 85h                         | R              | IN3 Conversion Result at Time of Fault                                                                                  |

| _                   | 86h                         | R              | IN4 Conversion Result at Time of Fault                                                                                  |

| _                   | 87h                         | R              | IN5 Conversion Result at Time of Fault                                                                                  |

| _                   | 88h                         | R              | IN6 Conversion Result at Time of Fault                                                                                  |

|                     | 89h                         | R              | IN7 Conversion Result at Time of Fault*                                                                                 |

| _                   | 8Ah                         | R              | IN8 Conversion Result at Time of Fault*                                                                                 |

| _                   | 8Bh                         | R              | Internal Temperature Sensor Conversion Result at Time of Fault                                                          |

|                     | 8Ch                         | R              | Remote Temperature Sensor 1 Conversion Result at Time of Fault                                                          |

|                     | 8Dh                         | R              | Remote Temperature Sensor 2 Conversion Result at Time of Fault*                                                         |

| _                   | 8Eh                         | R              | Current-Sense Conversion Result at Time of Fault*                                                                       |

\*MAX16031 only.

## **Detailed Description**

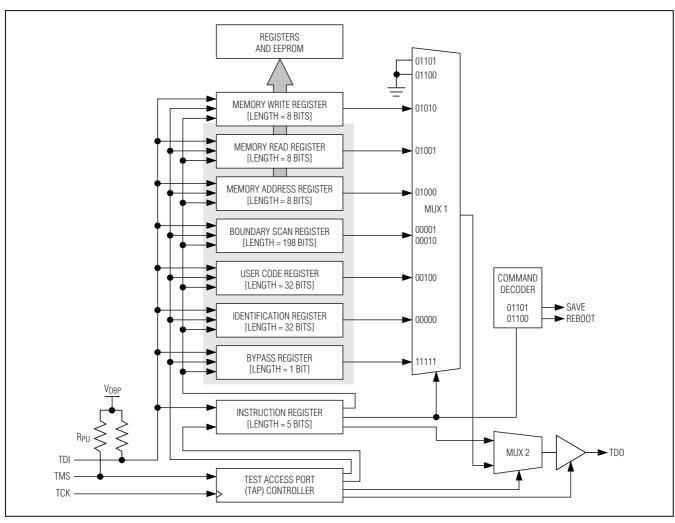

### **Getting Started**

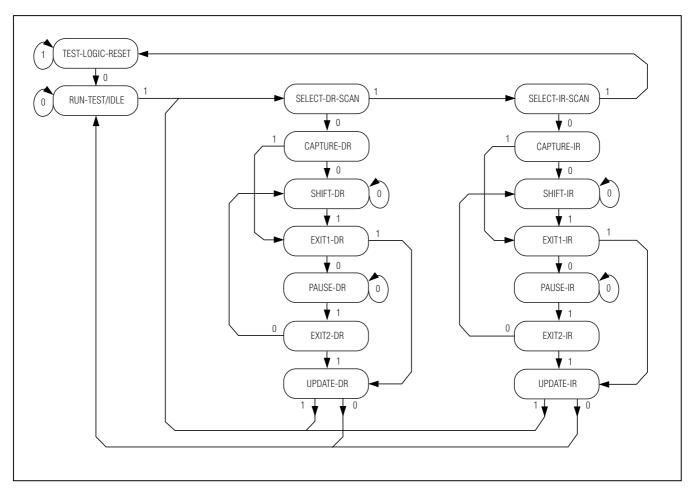

The MAX16031/MAX16032 contain both I<sup>2</sup>C/SMBus and JTAG serial interfaces for accessing registers and EEPROM. Use only one interface at any given time. For more information on how to access the internal memory through these interfaces, see the I<sup>2</sup>C/SMBus-Compatible Serial Interface and JTAG Serial Interface sections. This data sheet uses a specific convention for referring to bits within a particular address location. As an example, r15h[3:0] refers to bits 3 through 0 in register with address 15 hexadecimal.

The factory-default values at power-on reset (POR) for all EEPROM locations are zeros. POR occurs when V<sub>CC</sub> reaches the undervoltage lockout (UVLO) of 2.8V. At POR, the device begins a boot-up sequence. During the boot-up sequence, all monitored inputs are masked from initiating faults and EEPROM contents are copied to the respective register locations. The boot-up sequence takes up to 1.81ms. Monitoring is disabled for up to 16s past the boot-up sequence by programming r5Bh[3:0] (see the *Miscellaneous Settings* section). RESET is low during boot-up and remains low after boot-up for its programmed timeout period after all monitored channels are within their respective thresholds.

The MAX16031/MAX16032 monitor up to eight voltages, up to one current, and up to three temperatures. After boot-up, an internal multiplexer cycles through each input. At each multiplexer stop, the 10-bit ADC converts the analog parameter to a digital result and stores the result in a register. Each time the multiplexer completes a cycle, internal logic compares the conversion results to the thresholds stored in memory. When a conversion vio-

lates a programmed threshold, the conversion is configured to generate a fault. Logic outputs are programmed to depend on many combinations of faults. Additionally, faults are programmed to trigger a fault log, whereby all fault information is automatically written to EEPROM.

## Voltage Monitoring

The MAX16031 provides eight inputs, IN1–IN8, for voltage monitoring. The MAX16032 provides six inputs, IN1–IN6, for voltage monitoring. Each input voltage range is programmable through r17h[7:0] and r18h[7:0] (see Table 2). Voltage monitoring for each input is enabled through r1Ah[7:0] (see Table 2). There are four programmable thresholds per voltage monitor input: primary undervoltage, secondary undervoltage, primary overvoltage, and secondary overvoltage. All voltage thresholds are 8 bits wide. Only the 8 most significant bits of the conversion result are compared to the thresholds. See the *Miscellaneous Settings* section to set the amount of hysteresis for the thresholds. See Table 1 for an address map of all voltage monitor input threshold registers.

ADC inputs are configurable for two different modes: pseudo-differential and single-ended (see Table 3). In pseudo-differential mode, two inputs make up a differential pair. Psuedo-differential conversions are performed by taking a single-ended conversion at each input of a differential pair and then subtracting the results. The pseudo-differential mode is selectable for unipolar or bipolar operation. Unipolar differential operation allows only positive polarities of differential voltages. Bipolar differential operation allows negative and positive polarities of differential voltages. Bipolar conversions are in two's complement format. For example,

**Table 2. Input Monitor Ranges and Enables**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                                  |  |  |

|---------------------|-----------------------------|-----------|--------------------------------------------------------------------------------------------------------------|--|--|

|                     |                             | [1:0]     | IN1 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved                             |  |  |

| 17h                 | 97h                         | [3:2]     | 10 = 1.4V, 11 = Reserved<br>IN2 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved |  |  |

| 17h                 | 9711                        | [5:4]     |                                                                                                              |  |  |

|                     |                             | [7:6]     | IN4 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved                             |  |  |

**Table 2. Input Monitor Ranges and Enables (continued)**

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                      |                                                                               |

|---------------------|-----------------------------|-----------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

|                     |                             | [1:0]     | IN5 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved |                                                                               |

| 10h                 | OOh                         | [3:2]     | IN6 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved |                                                                               |

| 18h                 | 98h                         | [5:4]     | IN7 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved |                                                                               |

|                     |                             | [7:6]     | IN8 Voltage Range Selection:<br>00 = 5.6V, 01 = 2.8V<br>10 = 1.4V, 11 = Reserved |                                                                               |

|                     |                             | [0]       | IN1 Monitoring Enable: 0 = IN1 monitoring disabled 1 = IN1 monitoring enabled    |                                                                               |

|                     |                             |           | [1]                                                                              | IN2 Monitoring Enable: 0 = IN2 monitoring disabled 1 = IN2 monitoring enabled |

|                     |                             |           |                                                                                  | [2]                                                                           |

| 106                 | 0.4.5                       | [3]       | IN4 Monitoring Enable: 0 = IN4 monitoring disabled 1 = IN4 monitoring enabled    |                                                                               |

| 1Ah                 | 9Ah -                       | [4]       | IN5 Monitoring Enable: 0 = IN5 monitoring disabled 1 = IN5 monitoring enabled    |                                                                               |

|                     |                             |           | [5]                                                                              | IN6 Monitoring Enable: 0 = IN6 monitoring disabled 1 = IN6 monitoring enabled |

|                     |                             | [6]       | IN7 Monitoring Enable: 0 = IN7 monitoring disabled 1 = IN7 monitoring enabled    |                                                                               |

|                     |                             |           | [7]                                                                              | IN8 Monitoring Enable: 0 = IN8 monitoring disabled 1 = IN8 monitoring enabled |

a -1V differential input (range of 5.6V) gives a decimal code of -183, which is 1101001001 in two's complement binary form. In single-ended mode, conversions are performed between a single input and ground. When single-ended mode is selected, conversions are always unipolar regardless of r1Ch[7:4]. The single-ended and pseudo-differential ADC mode equations are shown below.

Unipolar single-ended mode:

$$X_{ADC} = INT \left( \frac{V_{IN-}}{V_{REF}} \times 1024 \right)$$

where  $X_{ADC}$  is the resulting code in decimal,  $V_{IN}$  is the voltage at a voltage monitoring input, and  $V_{RANGE}$  is the selected range programmed in r17h and r18h.

Bipolar/unipolar pseudo-differential mode:

$$X_{ADC} = INT \left( \frac{V_{IN+}}{V_{REF}} \times 1024 \right) - INT \left( \frac{V_{IN-}}{V_{REF}} \times 1024 \right)$$

where X<sub>ADC</sub> is the resulting code in decimal, V<sub>IN+</sub> is the voltage at a positive input of a differential voltage monitoring input pair, V<sub>IN-</sub> is the voltage at a negative input of a differential voltage monitoring input pair, and V<sub>RANGE</sub> is the selected range programmed in r17h and r18h.

Table 3. IN1-IN8 ADC Input Mode Selection

| REGISTER<br>ADDRESS | EEPROM<br>MEMORY<br>ADDRESS | BIT RANGE | DESCRIPTION                                                                                                                                               |     |                                                                                                                                   |  |

|---------------------|-----------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|--|

|                     |                             | [0]       | IN1/IN2 Single-Ended/Pseudo-Differential: 0 = IN1 and IN2 conversions are single-ended. 1 = IN1 and IN2 conversions are pseudo-differential (IN1 to IN2). |     |                                                                                                                                   |  |

|                     |                             | [1]       | IN3/IN4 Single-Ended/Pseudo-Differential: 0 = IN3 and IN4 conversions are single-ended. 1 = IN3 and IN4 conversions are pseudo-differential (IN3 to IN4). |     |                                                                                                                                   |  |

|                     |                             | [2]       |                                                                                                                                                           |     |                                                                                                                                   |  |

| 1Ch                 | 001                         | [3]       | IN7/IN8 Single-Ended/Pseudo-Differential: 0 = IN7 and IN8 conversions are single-ended. 1 = IN7 and IN8 conversions are pseudo-differential (IN7 to IN8). |     |                                                                                                                                   |  |

| ion                 | 9Ch                         | 9Cn       | 9OH                                                                                                                                                       | [4] | IN1/IN2 Unipolar/Bipolar:  0 = IN1 and IN2 conversions are unipolar.  1 = IN1 and IN2 conversions are bipolar (two's complement). |  |

|                     |                             | [5]       | IN3/IN4 Unipolar/Bipolar: 0 = IN3 and IN4 conversions are unipolar. 1 = IN3 and IN4 conversions are bipolar (two's complement).                           |     |                                                                                                                                   |  |

|                     |                             | [6]       | IN5/IN6 Unipolar/Bipolar:  0 = IN5 and IN6 conversions are unipolar.  1 = IN5 and IN6 conversions are bipolar (two's complement).                         |     |                                                                                                                                   |  |

|                     |                             | [7]       | IN7/IN8 Unipolar/Bipolar: 0 = IN7 and IN8 conversions are unipolar. 1 = IN7 and IN8 conversions are bipolar (two's complement).                           |     |                                                                                                                                   |  |

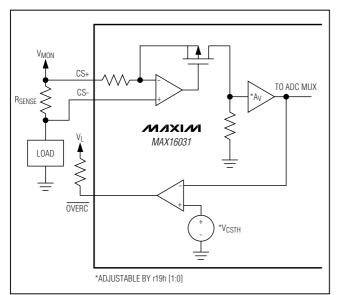

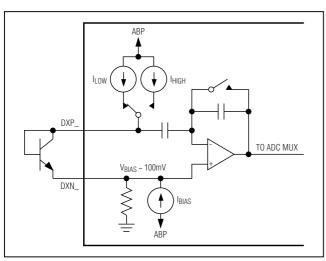

### **Current Monitoring**