# 8V/5V Low Dropout Dual Regulator with ENABLE

### Description

The CS-8165 is a low dropout, 8V/5V dual linear regulator. The second 5V/20mA output for powering systems with standby memory. Quiescent current drain is less than 2mA when supplying 10mA loads from the standby regulator.

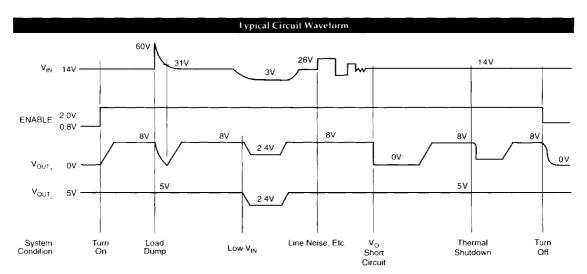

In automotive applications, the CS-8165 and all regulated circuits are protected from reverse battery installations, and over voltage

transients. During line transients, such as a 60V load dump, the 750mA output will automatically shut down to protect both internal circuits and the load, while the second output will continue to power any standby load.

The CS-8165 is packaged in a 5-lead TO-220, with copper tab for connection to a heat sink, if necessary.

#### **Absolute Maximum Ratings**

| Input Voltage                              |                    |

|--------------------------------------------|--------------------|

| Operating Range                            | 0.5V to 26V        |

| Overvoltage Protection                     | 60V                |

| Internal Power Dissipation                 | Internally Limited |

| Operating Temperature Range                | 40°C to +125°C     |

| Junction Temperature Range                 |                    |

| Storage Temperature Range                  | 65°C to +150°C     |

| Soldering Lead Temperature: TO-220 (10sec) | 260°C              |

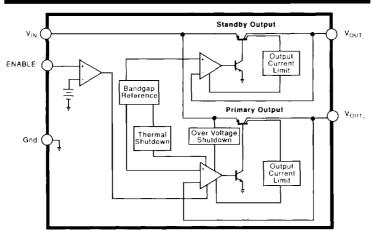

#### Block Diagram

# Features $V_{IN}$ 2 V<sub>OUT1</sub> Gnd

Cherry Semiconductor Corporation 2000 South County Trail East Greenwich, Rhode Island 02818-1530 Tel: (401)885-3600 Fax (401)885-5786 email: info@cherry-semi.com

4 ENABLE 5 V<sub>OUT2</sub>

| PARAMETER                                    | TEST CONDITIONS                                                                                                | MIN  | TYP  | MAX  | UNIT        |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|-------------|

| Output Stage (V <sub>OUT1</sub> )            |                                                                                                                |      |      |      |             |

| Output Voltage, V <sub>OUT1</sub>            | $13V \le V_{IN} \le 26V$ , $I_{OUT_1} \le 500 \text{mA}$ ,                                                     | 7.6  | 8.0  | 8.4  | V           |

| Dropout Voltage                              | I <sub>OUT1</sub> =500mA                                                                                       |      |      | 0.60 | V           |

| Line Regulation                              | $13V \le V_{1N} \le 16V$ , $I_{OUT_1} = 5mA$                                                                   |      | 15   | 80   | mV          |

| Load Regulation                              | $5\text{mA} \le I_{\text{OUT}_1} \le 500\text{mA}$                                                             |      | 15   | 80   | mV          |

| Quiescent Current                            | $l_{ m OUT_1} {\le} 10$ mA, No Load on $V_{ m OUT_2}$                                                          |      | 3    | 7    | mΑ          |

|                                              | I <sub>OUI<sub>1</sub></sub> 500mA, No Load on V <sub>OUI<sub>2</sub></sub>                                    |      | 40   | 100  | mA          |

| n. 1 n                                       | I <sub>OUT1</sub> =750mA, No Load on V <sub>OUT2</sub>                                                         |      | 90   |      | mA          |

| Ripple Rejection                             | f=120Hz                                                                                                        | 0.75 | 53   | 2.50 | dB          |

| Current Limit                                |                                                                                                                | 0.75 | 1.40 | 2.50 | A           |

| Maximum Line Transient                       | V <sub>OUT1</sub> ≤13V                                                                                         | 60   | 30   |      | V           |

| Reverse Polarity Input Voltage, DC           | V <sub>OUT1</sub> ≥-0.6V, 10 <b>Ω</b> Load                                                                     | -18  | -30  |      | V           |

| Reverse Polarity Input<br>Voltage, Transient | 1% Duty Cycle, t=100ms, V <sub>OUT</sub> ≥-6V,<br>10Ω Load                                                     | -50  | -80  |      | V           |

| Output Noise Voltage                         | 10Hz-100kHz                                                                                                    |      | 100  |      | μVrr        |

| Long Term Stability                          |                                                                                                                |      | 50   |      | mV/k        |

| Output Impedance                             | 500mA DC and 10mA rms,<br>100Hz-10kHz                                                                          |      | 200  |      | m <b>()</b> |

| Standby Output (V <sub>OUT2</sub> )          |                                                                                                                |      |      |      |             |

| Output Voltage, (V <sub>OUT2</sub> )         | 6V≤V <sub>IN</sub> ≤26V                                                                                        | 4.75 | 5.00 | 5.25 | V           |

| Dropout Voltage                              | I <sub>OUT2</sub> ≤10mA                                                                                        |      | 0.55 | 0.70 | V           |

| Line Regulation                              | 6V≤V <sub>IN</sub> ≤26V                                                                                        |      | 4    | 50   | mV          |

| Load Regulation                              | 1mA≤l <sub>OUT2</sub> ≤10mA                                                                                    |      | 10   | 50   | mV          |

| Quiescent Current                            | $I_{OU1_2} \le 10 \text{mA}, -40^{\circ}\text{C} \le T_{J} \le +125^{\circ}\text{C}$<br>$V_{OUT_1} \text{OFF}$ |      | 2    | 3    | mA          |

| Ripple Rejection                             | f=120Hz                                                                                                        |      | 66   |      | dB          |

| Current Limit                                |                                                                                                                | 25   | 70   |      | mΑ          |

| Output Noise Voltage                         | 10Hz-100kHz                                                                                                    |      | 300  |      | μV          |

| Long Term Stability                          |                                                                                                                |      | 20   |      | mV/l        |

| Output Impedance                             | 10mA DC and 1mA rms, 100Hz-10kHz                                                                               |      | 1    |      | Ω           |

| ENABLE Function (ENABL                       | Е)                                                                                                             |      |      |      |             |

| Input ENABLE Threshold                       | $V_{OUT_1}$ Off                                                                                                |      | 1.25 | 0.80 | V           |

|                                              | V <sub>OUI1</sub> On                                                                                           | 2.00 | 1.25 |      | V           |

| Input ENABLE Current                         | Input Voltage Range 0 to 26V                                                                                   | -10  |      | 10   | μΑ          |

| Package Pin Description |             |                                                                                                        |  |

|-------------------------|-------------|--------------------------------------------------------------------------------------------------------|--|

| PACKAGE PIN #           | PIN SYMBOL  | FUNCTION                                                                                               |  |

| TO-220                  |             |                                                                                                        |  |

| 1                       | $V_{IN}$    | Supply voltage, usually direct from battery.                                                           |  |

| 2                       | $V_{OUT_1}$ | Regulated output 8V, 750mA (typ)                                                                       |  |

| 3                       | Gnd         | Ground connection.                                                                                     |  |

| 4                       | ENABLE      | CMOS compatible input pin; switches $V_{OUT_1}$ on and off. When ENABLE is high $V_{OUT_1}$ is active. |  |

| 5                       | $V_{OUI_2}$ | Standby output 5V, 20mA (typ); always on.                                                              |  |

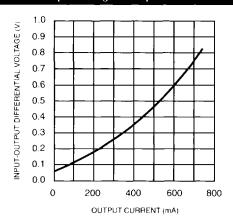

Dropout Voltage vs. Output Current

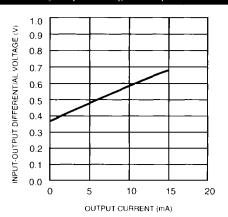

#### Standby Dropout Voltage vs. Output Current

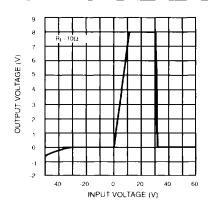

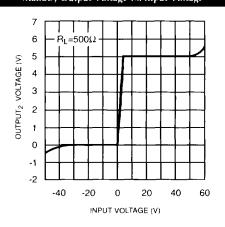

Output Voltage vs. Input Voltage

Standby Output Voltage vs. Input Voltage

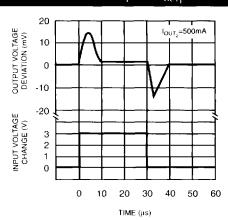

Line Transient Response (VOUL)

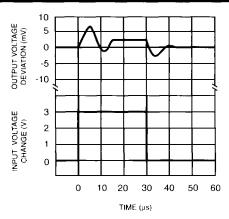

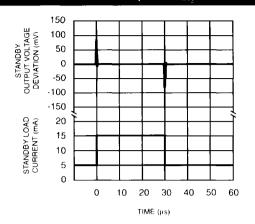

Line Transient Response (VOUT2)

#### Typical Performance Characteristics

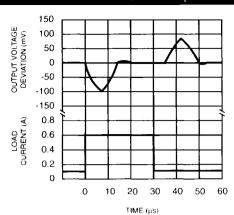

#### Load Transient Response (VOUL)

#### Load Transient Response (VOLL)

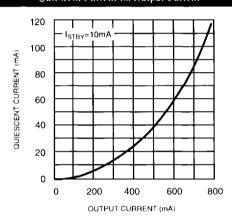

Quiescent Current vs. Output Current

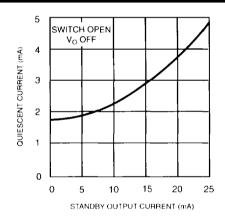

#### Quiescent Current vs. Standby Output Current

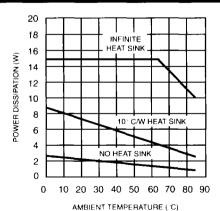

#### Maximum Power Dissipation (TO-220)

- Dropout Voltage: The input-output voltage differential at which the circuit ceases to regulate against further reduction in input voltage. Measured when the output voltage has dropped 100mV from the nominal value obtained at 14V input, dropout voltage is dependent upon load current and junction temperature.

- **Input Voltage:** The DC voltage applied to the input terminals with respect to ground.

- **Input Output Differential:** The voltage difference between the unregulated input voltage and the regulated output voltage for which the regulator will operate.

- Line Regulation: The change in output voltage for a change in the input voltage. The measurement is made under conditions of low dissipation or by using pulse techniques such that the average chip temperature is not significantly affected.

- **Load Regulation:** The change in output voltage for a change in load current at constant chip temperature.

- Long Term Stability: Output voltage stability under accelerated life-test conditions after 1000 hours with maximum rated voltage and junction temperature.

- Output Noise Voltage: The rms AC voltage at the output, with constant load and no input ripple, measured over a specified frequency range.

- **Quiescent Current:** The part of the positive input current that does not contribute to the positive load current. i.e., the regulator ground lead current.

- **Ripple Rejection:** The ratio of the peak-to-peak input ripple voltage to the peak-to-peak output ripple voltage.

- **Temperature Stability of V**<sub>OUT</sub>: The percentage change in output voltage for a thermal variation from room temperature to either temperature extreme.

#### Circuit Description

#### Standby Output (VOUT2)

The CS-8165 is equipped with two outputs. The second output is intended for use in systems requiring standby memory circuits. While the high current regulator output  $(V_{OUT_1})$  can be controlled with the ENABLE pin described below, the standby output remains on under all conditions as long as sufficient input voltage is applied to the IC. Thus, memory and other circuits powered by this output remain unaffected by positive line transients, thermal shutdown, etc.

The standby regulator circuit ( $V_{\rm OUI_3}$ ) is designed so that the quiescent current to the IC is very low (<2mA) when primary regulator output ( $V_{\rm OUI_3}$ ) is off.

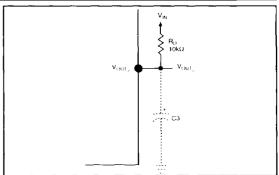

In applications where the standby output is not needed, it may be disabled by connecting a resistor from the standby

Disabling  $V_{\rm OUT_2}$  when it is not needed. C3 is no longer needed.

#### Cricuit Description: continued

$\stackrel{\bullet}{\mathcal{O}}$  output to the supply voltage. This eliminates the need for a capacitor on the output to prevent unwanted oscillations. The value of the resistor depends upon the minimum input voltage expected for a given system. Since the standby output is shunted with an internal 6.0V Zener, the current through the external resistor should be sufficient to bias V<sub>OUI</sub>, up to this point. Approximately 60μA of current is required. For most applications a  $10k\Omega$  external resistor is sufficient.

#### High Current Output (Voca)

Unlike the standby regulated output, which must remain on whenever possible, the high current regulated output is fault protected against overvoltage and overt tempera-

ture conditions. If the input voltage rises above approximately 30V (e.g., load dump), this output will automatically shutdown. This protects the internal circuitry and enables the IC to survive higher voltage transients than would otherwise be expected. Thermal shutdown is effective against die overheating since the high current output is the dominant source of power dissipation in the IC.

#### **ENABLE**

The ENABLE function controls V<sub>OUT1</sub> When ENABLE is high (5V), V<sub>OUT</sub> is on. When ENABLE is low, V<sub>OUT</sub> is off.

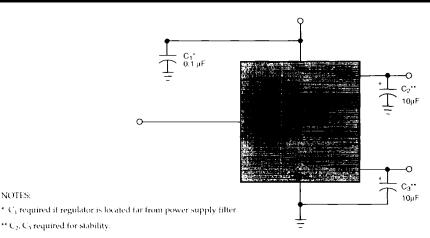

#### **Application Circuit**

## \*\* Cs. Cs required for stability

NOTES

#### Application Notes

#### Stability Considerations

The capacitor value and type should be based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR, can cause instability. The aluminum electrolytic capacitor is the cheapest solution, but, if the circuit operates at low temperatures. (-25°C to -40°C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturers data sheet usually provide this information.

The value for the output capacitors C2 and C3 shown in the test and applications circuit should work for most applications, however it is not necessarily the cheapest or best solution.

To determine acceptable values for C2 and C3 for a particular application, start with a tantalum capacitor of the recommended value and work towards a less expensive alternative part for each output.

**Step 1:** Place the completed circuit with the tantalum capacitors of the recommended values in an environmental chamber at the lowest specified operating temperature and monitor the outputs on the oscilloscope. A decade box connected in series with capacitor C<sub>2</sub> will simulate the higher ESR of an aluminum capacitor. (Leave the decade

box outside the chamber, the small resistance added by the longer leads is negligible)

**Step 2:** With the input voltage at its maximum value, increase the load current slowly from zero to full load on the output under observation. Look for any oscillations on the output. If no oscillations are observed, the capacitor is large enough to ensure a stable design under steady state conditions.

Step 3: Increase the ESR of the capacitor from zero using the decade box and vary the load current until oscillations appear. Record the values of load current and ESR that cause the greatest oscillation. This represents the worst case load conditions for the output at low temperature.

**Step 4:** Maintain the worst case load conditions set in step 3 and vary the input voltage until the oscillations increase. This point represents the worst case input voltage condi-

Step 5: If the capacitor is adequate, repeat steps 3 and 4 with the next smaller valued capacitor. (A smaller capacitor will usually cost less and occupy less board space.) If the capacitor oscillates within the range of expected operating conditions, repeat steps 3 and 4 with the next larger standard capacitor value.

**Step 6:** Test the load transient response by switching in various loads at several frequencies to simulate its real work environment. Vary the ESR to reduce ringing.

**Step 7:** Remove the unit from the environmental chamber and heat the IC with a heat gun. Vary the load current as instructed in step 5 to test for any oscillations.

Once the minimum capacitor value with the maximum ESR is found for each output, a safety factor should be added to allow for the tolerance of the capacitor and any variations in regulator performance. Most good quality aluminum electrolytic capacitors have a tolerance of +/-20% so the minimum value found should be increased by at least 50% to allow for this tolerance plus the variation which will occur at low temperatures. The ESR of the capacitors should be less than 50% of the maximum allowable ESR found in step 3 above.

Repeat steps 1 through 7 with the capacitor on the other output,  $C_{\rm b}$

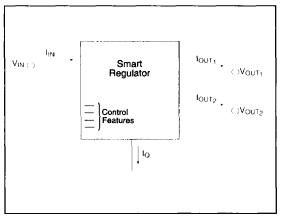

# Calculating Power Dissipation in a Dual Output Linear Regulator

The maximum power dissipation for a dual output regulator (Figure 1) is

$$\begin{split} P_{Dimaxj} &= \{V_{IN(max)} \cdot V_{OUT,PI(min)}\}I_{OUT,PI(max)} + \\ &+ \{V_{IN(max)} \cdot V_{OUT,PI(min)}\}I_{OUT,PI(max)}\}V_{IN(max)}IQ \; . \end{split} \tag{1}$$

#### Where

$V_{|N(max)}$  is the maximum input voltage,

$V_{OUI_1(min)}$  is the minimum output voltage from  $V_{OUI_1}$

$V_{OUT_{2}(min)}$  is the minimum output voltage from  $V_{OUT_{2}}$

$I_{\text{OUT}_{\underline{\mathbf{I}}}(max)}$  is the maximum output current, for the application

$I_{OUII_{2(max)}}$  is the maximum output current, for the application

$I_Q$  is the quiescent current the regulator consumes at  $I_{OUI(max)^{\ast}}$

Figure 1: Dual output regulator with key performance parameters labeled.

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R\Theta_{LX}$  can be calculated:

$$R\Theta_{IA} = \frac{150^{\circ}C - T_A}{P_D} \tag{2}$$

The value of  $R\Theta_{LN}$  can then be compared with those in the package section of the data sheet. Those packages with  $R\Theta_{LN}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

#### Heat Sinks

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R\Theta_{\rm IA}$ .

$$R\Theta_{JA} = R\Theta_{JC} + R\Theta_{CS} + R\Theta_{SA}$$

(3)

where

$R\Theta_{IC}$  = the junction–to–case thermal resistance,

$R\Theta_{CS}$  : the case–to–heatsink thermal resistance, and

$R\Theta_{SA}$  = the heatsink-to-ambient thermal resistance.

$R\Theta_{RC}$  appears in the package section of the data sheet. Like  $R\Theta_{IA}$ , it too is a function of package type,  $R\Theta_{CS}$  and  $R\Theta_{SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

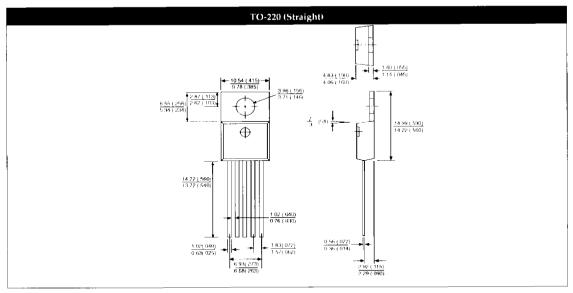

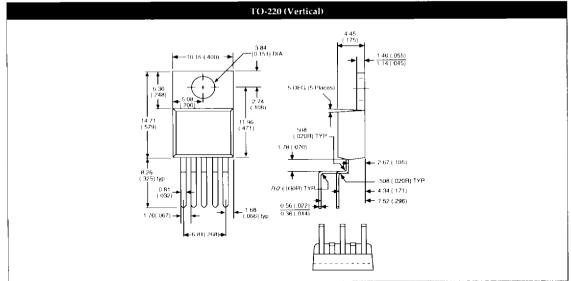

#### PACKAGE DIMENSIONS IN mm(INCHES)

|     | PACKAGE THERMAL DATA |        |  |  |  |   |

|-----|----------------------|--------|--|--|--|---|

| ata |                      | TO-220 |  |  |  | _ |

| Therma                 | l Data | TO-220 |      |

|------------------------|--------|--------|------|

| R⊖ <sub>i</sub>        | typ    | 3.5    | "C/W |

| $R\Theta_{\mathbb{N}}$ | typ    | 50     | °C/W |

242

#### Description Part Number 5 Lead TO-220 Straight CS-8165T5 CS-8165TV5 5 Lead TO-220 Vertical CS-8165TH5 5 Lead TO-220 Horizontal

Ordering Information

#### Preliminary

This product is in the preproduction stages of the design process. The data sheet contains preliminary data. CSC reserves the right to make changes to the specifications without notice. Please contact CSC for the latest available information.