# **CT1820**

# Data Terminal Bit Processor for MIL-STD-1553 A & B

www.aeroflex.com/Avionics

April 10, 2008

#### **FEATURES**

- Performs Encoder, Decoder, Logic and Control functions of a Data Bus Terminal to MIL-STD-1553 specifications, including Address, Mode Code and Broadcast Decoding and Terminal Fail Safe

- □ Flexibility all control lines accessible

- Parallel tri-state subsystem I/O bus compatible with both 16 bit and 8 bit systems

- Dual rank I/O registers for versatile subsystem tlmlng

- □ Operates from +5VDC @ 50mA

- □ Self-contained +5Vdc oscillator and clock driver @ 13 mA

- Look-ahead serial receive data output

- Self-test, on-line wraparound, plus off-line capability

- □ Full military (-55°C to +125°C) temperature range

- Designed for commercial, industrial and aerospace applications

- MIL-PRF-38534 compliant

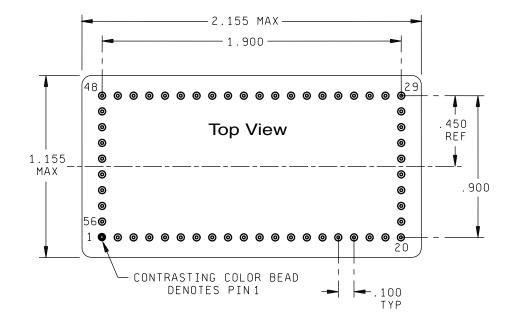

- Packaging Metal hermetic

- 56 pin, plug-in, 1.155"W x 2.155"L x .200"Ht

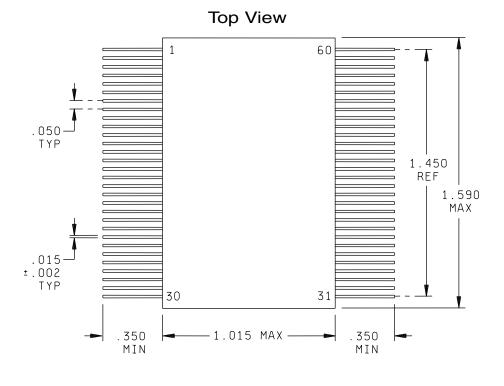

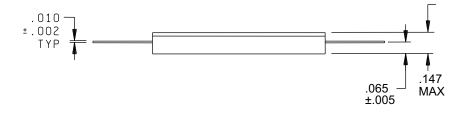

- 60 lead, flat-pack, 1.015"W x 1.59"L x .147"Ht

- □ DESC Standard microcircuit drawing (SMD): 5962-90636

### **DESCRIPTION**

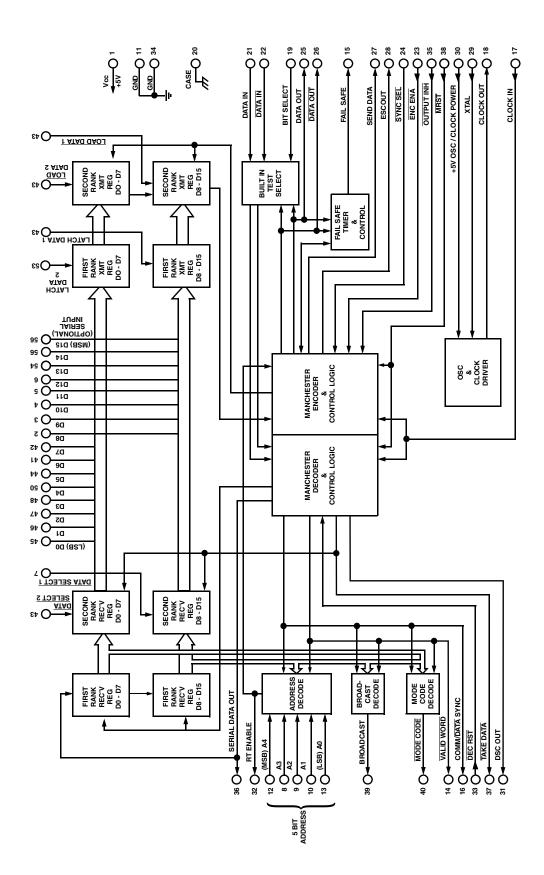

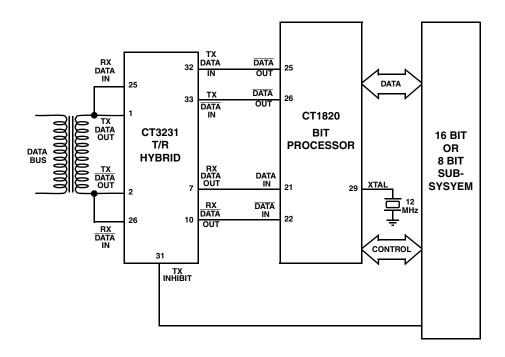

The Aeroflex Plainview CT1820 Bit Processor Unit (BPU) is an advanced Hybrid Microcircuit that provides the interface between a MIL-STD-1553 Transceiver such as CT3231M or CT3232M, and the subsystem internal parallel data bus. The unit can be employed as the mux bus interface for Remote Subsystems or Master Terminal Bus Controllers, thus providing a common interface for all systems communicating over the bus.

The unit places no restrictions on Command, Response or polling operations as it transfers all Command, Status and Data words from the bus to parallel output lines, together with error information, bus status and handshaking signals. It also contains 5 Bit Address Recognition, Broadcast and Mode Code Decode, Terminal Fail Safe Signal and Self Test.

In the transmit mode, it accepts parallel data from the user and transmits Command, Status and Data words, under subsystem control, to the data bus. Positive handshaking signals provide logic control synchronisation between the unit and the subsystem for direct data flow.

The hybrid is completely compatible with all the electrical and functional specification requirements of MIL-STD-1553 A & B.

Figure 1 – FUNCTIONAL DIAGRAM (Plug-in Pins shown)

Figure 2 – TyPICAL MIL-STD-1553 DATA TERMINAL

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                               | Range             | Units |

|-----------------------------------------|-------------------|-------|

| Supply Voltage                          | +7.0              | V     |

| Logic Input Voltage                     | -0.3 to +5.5      | V     |

| Clock Output Current (Pin 18 - Plug-in) | 15                | mA    |

| Clock In (Pin 17 - Plug-in)             | -0.3 to VCC +0.3V | V     |

| Storage Temperature Range               | -65 to +150       | °C    |

| Operating Case Temperature Range        | -55 to +125       | °C    |

# **ELECTRICAL CHARACTERISTICS**

$(VCC = 5.0V \pm 10\%, TC = -55^{\circ}C \text{ to } +125^{\circ}C)$

| Sym  | Parameter / Conditions            | Min          | Тур     | Max           | Units |

|------|-----------------------------------|--------------|---------|---------------|-------|

| VIH  | Logic "1" Input Voltage           | 2.0          | -       | -             | V     |

| VIL  | Logic "0" Input Voltage           | -            | -       | 0.7           | V     |

| Voн  | Logic "1" Output Voltage          | See Pin assi | gnments | and Loading   | g     |

| Vol  | Logic "0" Output Voltage          | See Pin assi | gnments | s and Loading | g     |

| VIHC | Logic "1" Input Voltage (CLOCK)   | Vcc-0.5      |         | -             | ٧     |

| VILC | Logic "0" Input Voltage (CLOCK)   | -            |         | GND+0.5       | V     |

| Vohc | Logic "1" Output Voltage (CLOCK)  | Vcc-0.3      |         | -             | ٧     |

| Volc | Logic "0" Output Voltage (CLOCK)  | -            |         | GND+0.3       | ٧     |

| loc  | Logic Supply Current              | -            | -       | 50            | mA    |

| losc | Oscillator / Clock Supply Current |              | 8       | 13            | mA    |

# **ELECTRICAL CHARACTERISTICS - PIN ASSIGNMENTS AND LOADING**

In the following table, the symbols are defined as follows: IIH= maximum input HIGH current with VIH = 2.5 volts IIL = maximum input LOW current with VIL = 0.4 volts IOH = maximum output HIGH current for VOH = 2.5 volts minimum IOL = maximum output LOW current for VOL = 0.4 volts maximum \* Indicates use of an internal pull-up resistor

| Pin  | No   | Name             | CT1820 |      | CT1820-2      | Description |      |                                                                                                                                               |

|------|------|------------------|--------|------|---------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Plug | Flat |                  | lін    | lıL  | Юн            | lol         | loL  |                                                                                                                                               |

| in   | Pack |                  | (µA)   | (mA) | (μ <b>A</b> ) | (mA         | (mA) |                                                                                                                                               |

| 1    | 6    | VCC              | -      | -    | -             | -           | -    | +5V Power Input                                                                                                                               |

| 2    | 7    | D8               | 20     | -0.4 | -1000         | 6.0         | 10.0 | Part of 16 Bit TRI-STATE I/O                                                                                                                  |

| 3    | 8    | D9               |        |      |               |             |      |                                                                                                                                               |

| 4    | 9    | D10              |        |      |               |             |      |                                                                                                                                               |

| 5    | 10   | D11              |        |      |               |             |      |                                                                                                                                               |

| 6    | 11   | D12              |        |      |               |             |      |                                                                                                                                               |

| 7    | 12   | DATA SELECT 1    | 20     | -0.4 |               |             |      | A LOW on this input applies the contents of the SECOND RANK REC'V REG to the D8-D15 I/O pins                                                  |

| 8    | 13   | A3*              | 20     | -0.4 |               |             |      | Part of 5 Bit ADDRESS INPUT                                                                                                                   |

| 9    | 14   | A2*              |        |      |               |             |      |                                                                                                                                               |

| 10   | 15   | A1*              |        |      |               |             |      |                                                                                                                                               |

| 11   | 16   | GROUND           |        |      |               |             |      | Logic and power return                                                                                                                        |

| 12   | 17   | A4*              | 20     | -0.4 |               |             |      | MSB of 5 Bit ADDRESS INPUT                                                                                                                    |

| 13   | 18   | A0*              |        |      |               |             | •    | LSB of 5 Bit ADDRESS INPUT                                                                                                                    |

| 14   | 19   | VALID WORD       |        |      | -400          | 4.0         | 4.0  | A LOW on this output indicates receipt of avalid word                                                                                         |

| 15   | 20   | FAIL SAFE        |        |      | -400          | 4.0         | 4.0  | A HIGH on this output indicates termination of a transmitted message that exceeds 768µs.                                                      |

| 16   | 21   | COMM / DATA SYNC |        |      | -400          | 4.0         | 4.0  | A HIGH on this output indicates COMMAND (or STATUS) word reception. A LOW indicates DATA word reception.                                      |

| 17   | 22   | CLOCK IN         | +100   | +0.1 |               |             |      | Input for 12MHz clock (20pf load).                                                                                                            |

| 18   | 23   | CLOCK OUT        |        |      | -1000         | 1.0         | 1.0  | Output of OSCILLATOR AND CLOCK DRIVER.                                                                                                        |

| 19   | 24   | S/T SELECT       | 20     | -0.4 |               |             |      | A HIGH on this input sets the unit in the self test mode.                                                                                     |

| 20   | 25   | CASE             |        |      |               |             |      | CASE CONNECTION                                                                                                                               |

| 21   | 26   | DATA IN          | 20     | -0.4 |               |             |      | A HIGH on this input represents a positive state on the bus.                                                                                  |

| 22   | 27   | DATA IN          | 20     | -0.4 |               |             |      | A HIGH on this input represents a negative state on the bus. (Pins 21 and 22 must both be high when the bus is inactive.)                     |

| 23   | 28   | ENC ENA          | 20     | -0.4 |               |             |      | A LOW on this input initiates a transmit cycle.                                                                                               |

| 24   | 29   | SYNC SEL         | 20     | -0.4 |               |             |      | Actuates COMMAND (or STATUS) sync for an input LOW and DATA sync for an input HIGH.                                                           |

| 25   | 32   | DATA OUT         |        |      | -400          | 4.0         | 4.0  | A HIGH on this output produces a positive state on the bus.                                                                                   |

| 26   | 33   | DATA OUT         |        |      | -400          | 4.0         | 4.0  | A HIGH on this output produces a negative state on the bus.                                                                                   |

| 27   | 34   | SEND DATA        |        |      | -400          | 4.0         | 4.0  | A HIGH on this output indicates data shifting during the transmit cycle.                                                                      |

| 28   | 35   | ESC OUT          |        |      | -1000         | 1.2         | 1.2  | LOW to HIGH transitions on this output during HIGH SEND DATA cause the transmit cycle data shifting to occur.                                 |

| 29   | 36   | XTAL             |        |      |               |             |      | A 12MHz (parallel resonant) crystal is connected between this pin and ground.                                                                 |

| 30   | 37   | +5V (OSC/CLOCK)  |        |      |               |             |      | +5V power for OSCILLATOR AND CLOCK POWER DRIVER.                                                                                              |

| 31   | 38   | DSC OUT          |        |      | -1000         | 1.2         | 1.2  | LOW to HIGH transitions on this output during LOW TAKE DATA cause receive cycle data shifting to occur.                                       |

| 32   | 39   | RT ENABLE        |        |      | -400          | 4.0         | 4.0  | A HIGH on this output indicates reception of a valid COMMAND (or STATUS) word containing the terminals address. It also resets the FAIL SAFE. |

# ELECTRICAL CHARACTERISTICS - PIN ASSIGNMENTS AND LOADING con't

In the following table, the symbols are defined as follows: IIH= maximum input HIGH current with VIH = 2.5 volts IIL = maximum input LOW current with VIL = 0.4 volts IOH = maximum output HIGH current for VOH = 2.5 volts minimum IOL = maximum output LOW current for VOL = 0.4 volts maximum \* Indicates use of an internal pull-up resistor

| Pin        | No           | Name            |             | CT1         | 820                  |            | CT1820-2    | Description                                                                                                                                                                  |

|------------|--------------|-----------------|-------------|-------------|----------------------|------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Plug<br>in | Flat<br>Pack |                 | lιн<br>(μΑ) | IIL<br>(mA) | Iон<br>(μ <b>A</b> ) | loL<br>(mA | IOL<br>(mA) |                                                                                                                                                                              |

| 33         | 40           | DEC RST         | 20          | -0.4        |                      |            |             | A LOW on this input (for 1µs minimum) resets the decoder to a condition ready for a new word, resets the COMM / DATA SYNC output LOW, and resets the VALID WORD output HIGH. |

| 34         | 41           | GROUND          |             |             |                      |            |             | Logic and Power Return.                                                                                                                                                      |

| 35         | 42           | OUTPUT INH      | 20          | -0.4        |                      |            |             | A LOW on this input holds output pins 25 and 26 LOW.                                                                                                                         |

| 36         | 43           | SERIAL DATA OUT |             |             | -400                 | 4.0        | 4.0         | The received serial data in NRZ format is available at this pin during LOW TAKE DATA.                                                                                        |

| 37         | 44           | TAKE DATA       |             |             | -400                 | 4.0        | 4.0         | A LOW on this output indicates data shifting during the receive cycle.                                                                                                       |

| 38         | 45           | MRST            | 20          | -0.4        |                      |            |             | A LOW on this input (for 1µs minimum) interrupts and clears the transmit cycle, resets the FAIL SAFE, and also performs the same functions as DEC RST.                       |

| 39         | 46           | BROADCAST*      |             |             | -400                 | 4.0        | 4.0         | A HIGH on this output indicates reception of a valid COMMAND (or STATUS) word containing all ONES in the address field.                                                      |

| 40         | 47           | MODE CODE*      |             |             | -600                 | 6.0        | 6.0         | A LOW on this output indicates reception of a valid COMMAND (or STATUS) word containing all ONES or all ZEROS in the sub-address field.                                      |

| 41         | 48           | D6              | 20          | -0.4        | -1000                | 6.0        | 10.0        | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 42         | 49           | D7              |             |             |                      |            |             |                                                                                                                                                                              |

| 43         | 50           | DATA SELECT 2   | 20          | -0.4        |                      |            |             | A LOW on this input applies the contents of the SECOND RANK REC'V REG to the D0-D7 I/O pins.                                                                                 |

| 44         | 51           | D5              | 20          | -0.4        | -1000                | 6.0        | 10.0        | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 45         | 52           | D0              |             |             |                      |            | •           | LSB of 16BIT TRI-STATE I/O                                                                                                                                                   |

| 46         | 53           | D1              |             |             |                      |            | •           | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 47         | 54           | D2              |             |             |                      |            |             | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 48         | 55           | D3              |             |             |                      |            |             | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 49         | 56           | LATCH DATA 2    |             | -0.4        |                      |            |             | A HIGH on this input allows the I/O data on D0-D7 to appear at the output of the FIRST RANK XMT REG. A LOW on this input holds the register outputs in their last state.     |

| 50         | 57           | D4              |             | -0.4        | -1000                | 6.0        | 10.0        | Part of 16 Bit TRI-STATE I/O                                                                                                                                                 |

| 51         | 58           | LOAD DATA 2     |             | -0.4        |                      |            |             | A LOW on this input loads the D0-D7 data into the SECOND RANK XMT REG. A HIGH on this input then locks out the data inputs to permit serial shifting.                        |

| 52         | 59           | LATCH DATA 1    |             |             |                      |            |             | A HIGH on this input allows the I/O data on D8-D15 to appear at the output of the FIRST RANK XMT REG. A LOW on this input holds the register outputs in their last state.    |

| 53         | 2            | LOAD DATA 1     | 20          | -0.4        |                      |            |             | A LOW on this input loads the D8-D15 data into the SECOND RANK XMT REG. A HIGH on this input then locks out the data inputs to permit serial shifting.                       |

| 54         | 3            | D13             |             | -0.4        | -1000                | 6.0        | 10.0        | Part of 16 Bit TRI-STATE I/O.                                                                                                                                                |

| 55         | 4            | D14             |             |             |                      |            |             | OPTIONAL SERIAL INPUT.                                                                                                                                                       |

| 56         | 5            | D15             |             |             |                      |            |             |                                                                                                                                                                              |

| -          | 1            | NC              | -           | -           | -                    | -          | -           | No Contact                                                                                                                                                                   |

| -          | 30           | NC              | -           | -           | -                    | -          | -           |                                                                                                                                                                              |

| -          | 31           | NC              | -           | -           | -                    | -          | -           |                                                                                                                                                                              |

| -          | 60           | NC              | -           | -           | -                    | -          | -           |                                                                                                                                                                              |

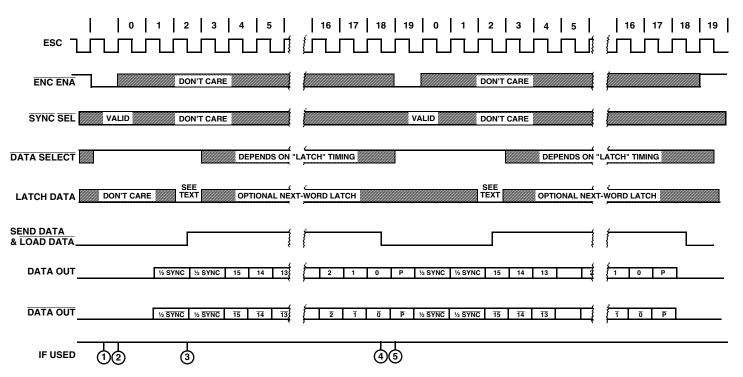

## TRANSMIT CYCLE OPERATION

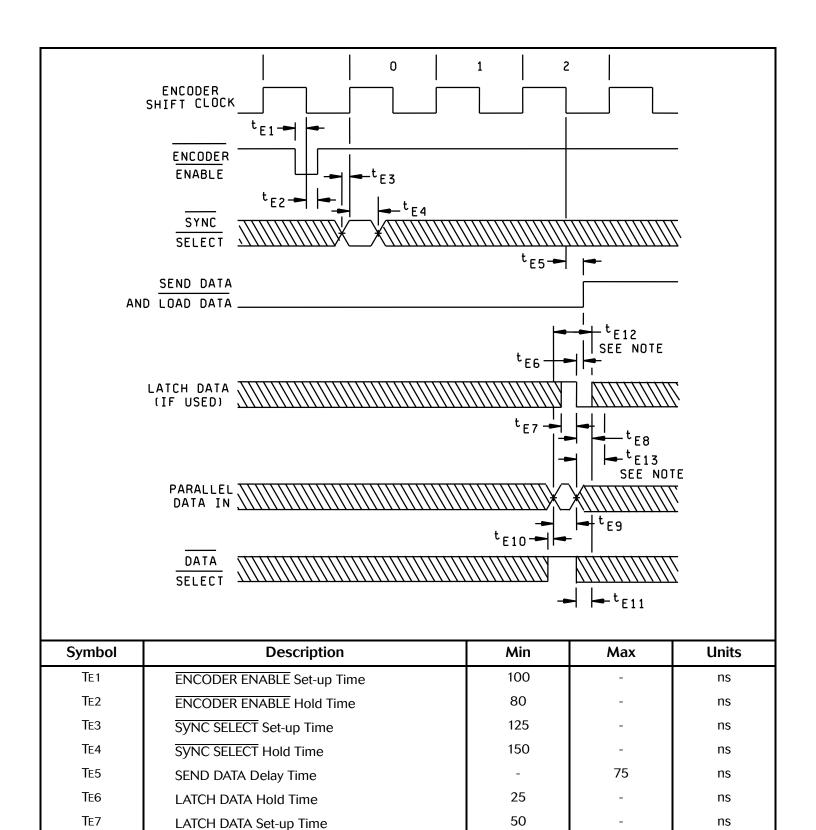

ENCODER SHIFT CLOCK (ESC) (see Figure 3) operates at the data rate (1MHz). A low at  $\overline{\text{ENCODER ENABLE}}$  ( $\overline{\text{ENC}}$   $\overline{\text{ENA}}$ ) during a falling edge of ESC 1 starts the Transmit cycle, which lasts for twenty ESC clock periods. The  $\overline{\text{SYNC}}$   $\overline{\text{SELECT}}$  (SYNC SEL) input is valid at the next low-to-high transition of ESC 2. A high at  $\overline{\text{SYNC}}$  SEL will produce a data sync, or a low will produce a command sync for that word.

Parallel data must be stable at the second rank transmit register before SEND DATA goes high ③. Since  $\overline{\text{ENC ENA}}$  is not synchronous with ESC, the minimum time to ③ is  $3\mu$ sec from  $\overline{\text{ENC ENA}}$  leading edge.

The first-rank transmit register may be operated transparently (LATCH DATA always high), or may be used to hold data ready for transmission, independent of the activity on the 16-line subsystem I/O bus. As long as LATCH DATA is held high, data present on the subsystem I/O bus appears at the output of the first rank transmit register. Stable data may be latched and held at the first rank register output by bringing LATCH DATA low. Data to be transmitted may be latched any time before the low-to high transition of SEND DATA (SEND DATA, when appled to the LOAD DATA inputs, locks out the data inputs to the second rank transmit register.) For multiple word transmissions, the next word may be inputted and latched any time after ③, but before the next low to-high transition of SEND DATA.

SEND DATA remains high for 16 ESC periods, during which the parallel transmit data is clocked to the MANCHESTER

ENCODER 3 to 4. After the sync and Manchester coded data are transmitted through the DATA OUT and  $\overrightarrow{DATA}$  OUT outputs, the ENCODER adds on the parity bit for that word 5

If the transmitted word is to be the last word of the transmission, ENC ENA must go high by ⑤ to prevent initiation of another transmit cycle.

At any time, a low applied to OUTPUT INHIBIT will force both DATA OUT and  $\overline{DATA}$  OUT to a low state without affecting any other operations.

The entire transmit cycle may be interrupted and cleared by applying a minimum of 1 $\mu$ sec negative pulse to the  $\overline{MASTER}$  RESET (MRST) input.

For 8-BIT I/O subsystems, D0 is tied to D8, D1 tied to D9, etc., through D7 tied to D15, and data is inputted in 8-BIT bytes by using LATCH DATA 1 and LATCH DATA 2 and/or LOAD DATA 1 and LOAD DATA 2 independently.

For serial data applications, D15 input serves as the serial transmit input. With  $\overline{\text{LOAD DATA 1}}$  held low and LATCH DATA 1 held high, D15 input is applied to the ENCODERís serial data input. Inputted data must be at the ESC rate with the MSB starting at the low-to-high transition of SEND DATA.

If a message length ever exceeds 768µsec, the 768µsec TIME OUT (FAIL SAFE) flag goes high, and DATA OUT and DATA OUT are both forced to a low state. This condition will remain until a valid command word (containing the terminalís address) is received or until MRST goes low.

Figure 3 – TRANSMIT CYCLE TIMING

NOTE:  $\underline{1}$ / TE12 and TE13 apply when LATCH DATA is not used.

**DATA SELECT Hold Time**

Parallel Data Set-up Time

**DATA SELECT** Disable Time

Parallel Data Hold Time

TE8, TE12 1/

TE9, TE13 1/

**TE10**

TE11

Figure 4 – ENCODER TIMING DETAIL

40

60

30

0

ns

ns

ns

ns

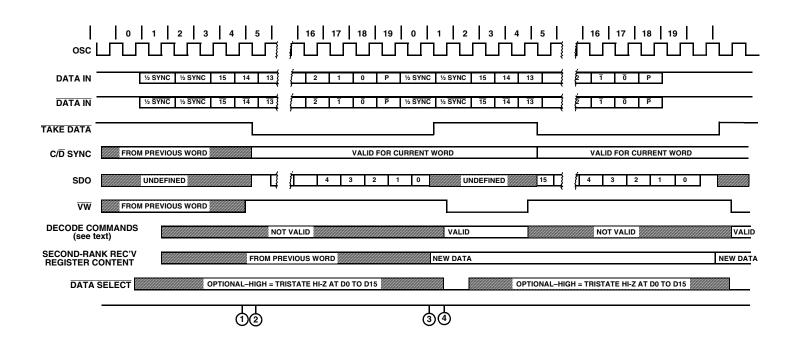

## **RECEIVE CYCLE OPERATION**

DECODER SHIFT CLOCK (DSC) (see Figure 5) operates at the data rate (1MHz). When the DECODER recognises a valid sync and two valid Manchester data bits ①, a receive cycle is initiated. The new sync is indicated at the COMMAND/ $\overline{D}$ ATA SYNC (C/ $\overline{D}$  SYNC) output and the TAKE DATA output goes low ②. The C/ $\overline{D}$  sync output will remain in its valid state until a new sync is detected on a subsequent word or until  $\overline{D}$ ECODER RESET ( $\overline{D}$ EC RST) or  $\overline{M}$ RST goes low. A low at  $\overline{D}$ EC RST or  $\overline{M}$ RST causes C/ $\overline{D}$ SYNC to go low.

TAKE DATA remains low for 16 DSC periods during which time the 16 serial data bits appear at the SERIAL DATA OUTPUT (SDO). This data is simultaneously loaded into the first-rank receive register. The low-to-high transition of TAKE DATA ③ makes the new data available at the output of the second-rank receive register. This data remains available until the next low-to-high transitions of TAKE DATA. It is not reset or cleared by any other signals. This data is applied to the D0 to D15 I/O bus by setting DATA SELECT lines low.

After all data has been loaded into the receive registers, the data is checked for odd parity. A low on  $\overline{\text{VALID WORD}}$  ( $\overline{\text{VW}}$ ) output ③, indicates successful reception of a word without any Manchester or parity errors. For consecutive word receptions,  $\overline{\text{VW}}$  will go high again in 3 to 3.5 $\mu$ s. In the absence of succeeding valid syncs,  $\overline{\text{VW}}$  will return high in 20 $\mu$ s. A  $\overline{\text{DEC RST}}$  (low) at any time will reset  $\overline{\text{VW}}$  high.

All decoded commands, including RT ENABLE (address recognition), BROADCAST and  $\overline{\text{MODE CODE}}$  are enabled internally by  $\overline{\text{VW}}$  and remain valid only as long as  $\overline{\text{VW}}$  is low. For 8-BIT I/O subsystems (D0 tied to D8, through D7 tied to D15), data may be extracted in 8 BIT bytes by selectively activating  $\overline{\text{DATA SELECT 1}}$  and  $\overline{\text{DATA SELECT 2}}$ .

For serial data systems, SERIAL DATA OUTPUT is available at the DSC rate from 2 to 3.

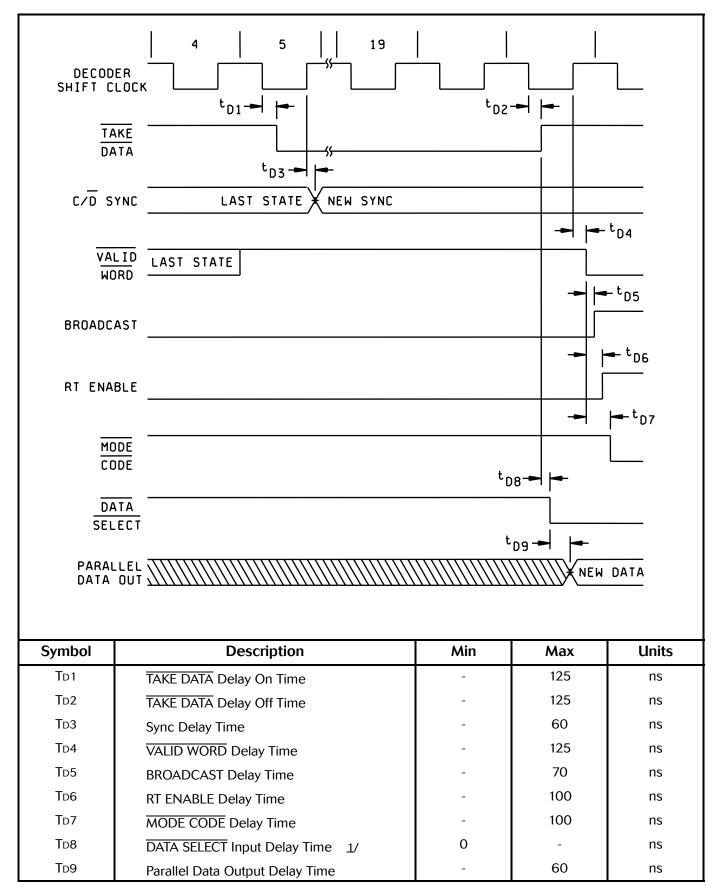

Figure 5 – RECEIVE CYCLE TIMING

NOTE: <u>1</u>/ DATA SELECT may be applied at any time that the 16 line I/O is otherwise free. The parallel Data Out, however, is not 'New Data' until after TAKE DATA goes high.

Figure 6 – DECODER TIMING DETAIL

#### **SELF TEST FUNCTION**

A high on the S/T SELECT input sets the hybrid in the SELF TEST mode. In this mode, the DATA and DATA output lines are connected to the Decoder inputs so that the unit may operate in the "wraparound" mode without actually going through the data bus transceiver. Note that the DATA and DATA output lines are active in this mode and the S/T SELECT command must also be used to inhibit the data bus transmitter to prevent arbitrary transmission on the data bus.

#### **TERMINAL FAIL SAFE**

In order to satisfy the Terminal Fail Safe requirements of MIL-STD-1553B, the DATA and DATA output lines are continuously monitored for length of message. A transmitted message in excess of 768µs sets the FAIL SAFE output high and terminates the transmission by setting both DATA and DATA output lines low. As a redundant safety factor, the FAILSAFE output may be applied to the INHIBIT input of the data bus transmitter (if so equipped). Further transmissions are prevented until the FAIL SAFE flag is reset either by reception of a valid command word containing the terminal address or by a negative pulse on the MRST input.

Note: Transmissions containing gaps of  $3\mu s$  or less are considered continuous, even if the gap is caused by a  $\overline{MRST}$  pulse.

#### **TERMINAL ADDRESS LINES**

The five-bit terminal address is set by hard wiring the 5-BIT ADDRESS lines. The hybrid contains internal pull-up resistors so that logic "1" lines may be left open circuited. Logic "0" lines must be grounded.

In operation, RT ENABLE goes high when a valid command word containing the hard-wired address is received. See "RECEIVE CYCLE OPERATION" for timing.

#### **OSCILLATOR AND CLOCK DRIVER**

The hybrid may be operated with either the internal clock or an external clock source.

For internal clock operation, a 12MHz parallel-resonant fundamental-mode crystal must be connected from XTAL to ground. Power (+5V) must be applied to +5V OSC/CLOCK POWER and CLOCK OUT must be connected to CLOCK IN.

For external clock operation, no power is applied to +5V OSC/CLOCK POWER and the external clock is applied to CLOCK IN (CLOCK OUT not connected). The external clock must be capable of driving a 20 picofarad load to within 0.5 volts of VCC and within 0.5 volts of ground with rise and fall times of less than 10 nanoseconds. Standard TTL levels are not satisfactory. For a normal 1MHz data rate, the clock frequency must be 12MHz.

#### **FALSE RT ENABLE**

Terminals that continuously monitor their own transmissions are subject to "END-AROUND" operation due to a false RT ENABLE. The terminal can erroneously interpret its own status word as a new command word. If no measures are taken to prevent or re-set RT ENABLE, it will remain high for 20µs or until the DECODER recognises a new valid sync (whichever time is shorter).

RT ENABLE may be inhibited by interrupting the RECEIVE CYCLE during a status word transmission. Inverted SEND DATA applied to  $\overline{\text{DEC RST}}$  will prevent reception of the status word.

If continuous monitoring is required, RT ENABLE may be reset immediately after it goes high by a  $1\mu$ s (minimum) low at  $\overline{DEC}$  RST. The status word will then be available at the second-rank receive register.

# PIN OUT DESCRIPTION (PLUG-IN)

| Pin<br># | Function       | Pin<br># | Function        |

|----------|----------------|----------|-----------------|

| 1        | VCC            | 29       | XTAL            |

| 2        | D8             | 30       | +5V (OSC/CLOCK) |

| 3        | D9             | 31       | DSC OUT         |

| 4        | D10            | 32       | RT ENABLE       |

| 5        | D11            | 33       | DEC RST         |

| 6        | D12            | 34       | GROUND          |

| 7        | DATA SELECT 1  | 35       | OUTPUT INH      |

| 8        | A3             | 36       | SERIAL DATA OUT |

| 9        | A2             | 37       | TAKE DATA       |

| 10       | A1             | 38       | MRST            |

| 11       | GROUND         | 39       | BROADCAST       |

| 12       | A4             | 40       | MODE CODE       |

| 13       | A0             | 41       | D6              |

| 14       | VALID WORD     | 42       | D7              |

| 15       | FAI L SAFE     | 43       | DATA SELECT 2   |

| 16       | COMM/DATA SYNC | 44       | D5              |

| 17       | CLOCK IN       | 45       | D0              |

| 18       | CLOCK OUT      | 46       | D1              |

| 19       | S/T SELECT     | 47       | D2              |

| 20       | CASE           | 48       | D3              |

| 21       | DATA IN        | 49       | LATCH DATA 2    |

| 22       | DATA IN        | 50       | D4              |

| 23       | ENC ENA        | 51       | LOAD DATA 2     |

| 24       | SYNC SEL       | 52       | LATCH DATA 1    |

| 25       | DATA OUT       | 53       | LOAD DATA 1     |

| 26       | DATA OUT       | 54       | D13             |

| 27       | SEND DATA      | 55       | D14             |

| 28       | ESC OUT        | 56       | D15             |

# PIN OUT DESCRIPTION (FLAT PACK)

| Pin<br># | Function       | Pin<br># | Function        |

|----------|----------------|----------|-----------------|

| 1        | NC             | 31       | NC              |

| 2        | LOAD DATA 1    | 32       | DATA OUT        |

| 3        | D13            | 33       | DATA OUT        |

| 4        | D14            | 34       | SEND DATA       |

| 5        | D15            | 35       | ESC OUT         |

| 6        | VCC            | 36       | XTAL            |

| 7        | D8             | 37       | +5V (OSC/CLOCK) |

| 8        | D9             | 38       | DSC OUT         |

| 9        | D10            | 39       | RT ENABLE       |

| 10       | D11            | 40       | DEC RST         |

| 11       | D12            | 41       | GROUND          |

| 12       | DATA SELECT 1  | 42       | OUTPUT INH      |

| 13       | A3             | 43       | SERIAL DATA OUT |

| 14       | A2             | 44       | TAKE DATA       |

| 15       | A1             | 45       | MRST            |

| 16       | GROUND         | 46       | BROADCAST       |

| 17       | A4             | 47       | MODE CODE       |

| 18       | A0             | 48       | D6              |

| 19       | VALID WORD     | 49       | D7              |

| 20       | FAIL SAFE      | 50       | DATA SELECT 2   |

| 21       | COMM/DATA SYNC | 51       | D5              |

| 22       | CLOCK IN       | 52       | D0              |

| 23       | CLOCK OUT      | 53       | D1              |

| 24       | S/T SELECT     | 54       | D2              |

| 25       | CASE           | 55       | D3              |

| 26       | DATA IN        | 56       | LATCH DATA 2    |

| 27       | DATA IN        | 57       | D4              |

| 28       | ENC ENA        | 58       | LOAD DATA 2     |

| 29       | SYNC SEL       | 59       | LATCH DATA 1    |

| 30       | NC             | 60       | NC              |

| Inches | mm    |

|--------|-------|

| .002   | .05   |

| .018   | .46   |

| .100   | 2.54  |

| .200   | 5.08  |

| .450   | 11.43 |

| .900   | 22.86 |

| 1.155  | 29.34 |

| 1.900  | 48.26 |

| 2.155  | 54.74 |

|        |       |

#### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

- 3. Unless otherwise specified, tolerances are  $\pm$  .005 (0.13 mm) for three place decimals.

# Plug-In Package Outline

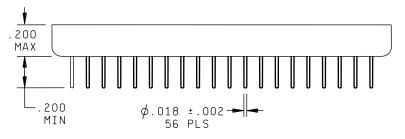

| Inches | mm    |

|--------|-------|

| .002   | .05   |

| .005   | .13   |

| .010   | .254  |

| .015   | .38   |

| .065   | 1.65  |

| .147   | 3.73  |

| .350   | 8.89  |

| 1.015  | 25.78 |

| 1.450  | 36.83 |

| 1.590  | 40.39 |

#### NOTES:

- 1. Dimensions are in inches.

- 2. Metric equivalents are given for general information only.

# Flat Package Outline

#### ORDERING INFORMATION

| Aeroflex Part #                  | DSCC SMD #                         | Screening                                                            | Package   |

|----------------------------------|------------------------------------|----------------------------------------------------------------------|-----------|

| CT1820                           | -                                  | Military Temperature, -55°C to +125°C<br>Screened in accordance with | Plug-in   |

| CT1820-FP                        | -                                  | MIL-PRF-38534, Class H                                               | Flat Pack |

| CT1820-2                         | -                                  |                                                                      | Plug-in   |

| CT1820-2-FP                      | -                                  |                                                                      | Flat Pack |

| CT1820-001-1<br>CT1820-001-2     | 5962-9063601HXC<br>5962-9063601HXA | Per DSCC SMD 5962-90636                                              | Plug-in   |

| CT1820-2-001-1<br>CT1820-2-001-2 | 5962-9063602HXC<br>5962-9063602HXA |                                                                      |           |

| CT1820-201-1                     | 5962-9063601HyC                    |                                                                      | Flat Pack |

| CT1820-2-201-1                   | 5962-9063602HYC                    |                                                                      |           |

#### **EXPORT CONTROL:**

This product is controlled for export under the International Traffic in Arms Regulations (ITAR). A license from the U.S. Department of State is required prior to the export of this product from the United States.

#### **EXPORT WARNING:**

Aeroflex's military and space products are controlled for export under the International Traffic in Arms Regulations (ITAR) and may not be sold or proposed or offered for sale to certain countries. (See ITAR 126.1 for complete information.)

PLAINVIEW, NEW YORK

INTERNATIONAL

NORTHEAST

Toll Free: 800-THE-1553

Tel: 805-778-9229

Tel: 603-888-3975

Fax: 516-694-6715

Fax: 805-778-1980

Fax: 603-888-4585

SE AND MID-ATLANTIC

WEST COAST

CENTRAL

Tel: 321-951-4164

Tel: 949-362-2260

Tel: 719-594-8017

Fax: 321-951-4254

Fax: 949-362-2266

Fax: 719-594-8468

www.aeroflex.com info-ams@aeroflex.com

Aeroflex Microelectronic Solutions reserves the right to change at any time without notice the specifications, design, function, or form of its products described herein. All parameters must be validated for each customer's application by engineering. No liability is assumed as a result of use of this product. No patent licenses are implied.

Our passion for performance is defined by three attributes represented by these three icons: solution-minded, performance-driven and customer-focused