## Old Company Name in Catalogs and Other Documents

On April 1<sup>st</sup>, 2010, NEC Electronics Corporation merged with Renesas Technology Corporation, and Renesas Electronics Corporation took over all the business of both companies. Therefore, although the old company name remains in this document, it is a valid Renesas Electronics document. We appreciate your understanding.

Renesas Electronics website: http://www.renesas.com

April 1<sup>st</sup>, 2010 Renesas Electronics Corporation

Issued by: Renesas Electronics Corporation (http://www.renesas.com)

Send any inquiries to http://www.renesas.com/inquiry.

#### Notice

- 1. All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majority-owned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

## 4 BIT SINGLE-CHIP MICROCOMPUTER

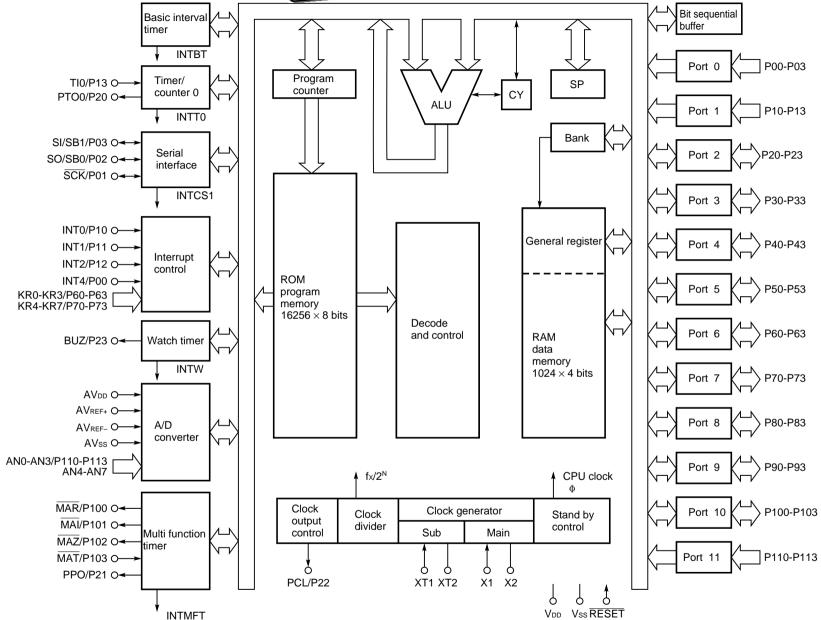

The  $\mu$ PD75036 is a 75X series 4-bit single-chip microcomputer.

The  $\mu$ PD75036 is an expanded version of the  $\mu$ PD75028. It has ROM and RAM with a larger capacity.

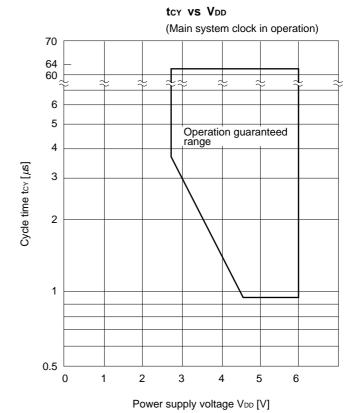

The minimum instruction execution time of the  $\mu$ PD75036 is 0.95  $\mu$ s. In addition to this high-speed capability, it contains an A/D converter and furnishes high-performance functions such as the serial bus interface (SBI) function that follows the NEC standard format, providing powerful features and high cost performance.

A built-in PROM product,  $\mu$ PD75P036, is also available. The  $\mu$ PD75P036 is suitable for small-scale production or experimental production in system development.

The following user's manual describes the details of functions. Be sure to read it before design.  $\mu$ PD75028 User's Manual: IEU-694

#### **FEATURES**

- Variable instruction execution time advantageous to high-speed operation and power-saving:

- 0.95  $\mu$ s, 1.91  $\mu$ s, or 15.3  $\mu$ s (at 4.19 MHz when the main system selected)

- 122 μs (at 32.768 kHz when the subsystem clock selected)

- Program memory (ROM) capacity: 16256 × 8 bits

- Data memory (RAM) capacity: 1024 × 4 bits

- Built-in A/D converter (8-bit resolution, successive approximation): 8 channels

- Powerful timer function: 4 channels

- Usable for 16-bit integral A/D conversion and PWM output

- Built-in NEC standard serial bus interface (SBI)

- Very low-power clock operation allowed (5  $\mu$ A TYP. at 3 V)

#### **APPLICATIONS**

Electric household appliances, air cooling/heating apparatus, cameras, and electronic measuring instruments

#### ORDERING INFORMATION

| Part number                                   | Package                             | Quality grade |

|-----------------------------------------------|-------------------------------------|---------------|

| $\mu$ PD75036CW- $\times\!\!\times\!\!\times$ | 64-pin plastic shrink DIP (750 mil) | Standard      |

| $\mu$ PD75036GC- $\times\times$ -AB8          | 64-pin plastic QFP (□14 mm)         | Standard      |

Remark xxx is a mask ROM code number.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

The information in this document is subject to change without notice.

Document No. IC-3115 (O.D. No. IC-8611) Date Published October 1993 P Printed in Japan

## **FUNCTIONS**

| Item                        |                             | Function                                                                                                            |                                                                                                                                                                                |                              |                                                                     |  |

|-----------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------|--|

| Instruction execution       | time                        | • 0.95, 1.91, 15.3 μs (Main system clock : 4.19 MHz operation)                                                      |                                                                                                                                                                                |                              |                                                                     |  |

|                             |                             | • 122 μs (Subsystem clock : 32.768 kHz operation)                                                                   |                                                                                                                                                                                |                              |                                                                     |  |

| On-chip memory              | ROM                         | 162                                                                                                                 | 56 × 8                                                                                                                                                                         | 8 bits                       |                                                                     |  |

|                             | RAM                         | 102                                                                                                                 | 4 × 4                                                                                                                                                                          | bits                         |                                                                     |  |

| General register            |                             |                                                                                                                     |                                                                                                                                                                                | anipulation: 8               |                                                                     |  |

|                             |                             | • 8                                                                                                                 | -bit m                                                                                                                                                                         | anipulation : 4              |                                                                     |  |

| I/O port                    |                             | 48                                                                                                                  | 12                                                                                                                                                                             | CMOS input pins              | On-chip pull-up resistor by software : 27                           |  |

|                             |                             |                                                                                                                     | 24                                                                                                                                                                             | CMOS I/O pins                | On-chip pull-down resistor by software: 4     Direct LED driving: 4 |  |

|                             |                             |                                                                                                                     | 12                                                                                                                                                                             | N-ch open-drain I/O pins     | Withstand voltage is 10 V                                           |  |

|                             |                             |                                                                                                                     |                                                                                                                                                                                |                              | On-chip pull-up resistor by mask option     Direct LED driving: 4   |  |

| Timer                       |                             |                                                                                                                     |                                                                                                                                                                                | imer/event counter           |                                                                     |  |

|                             |                             | nels                                                                                                                |                                                                                                                                                                                | asic interval timer : Can be |                                                                     |  |

|                             |                             | han                                                                                                                 | Basic interval timer : Can be used as watchdog timer     Clock timer : Buzzer output enabled     Multifunction timer : Can be used as timer, free-running timer or counter for |                              |                                                                     |  |

|                             |                             | 4                                                                                                                   |                                                                                                                                                                                |                              |                                                                     |  |

| Serial interface            |                             | Three-wire serial I/O mode                                                                                          |                                                                                                                                                                                |                              |                                                                     |  |

|                             |                             | Two-wire serial I/O mode                                                                                            |                                                                                                                                                                                |                              |                                                                     |  |

|                             |                             | SBI mode                                                                                                            |                                                                                                                                                                                |                              |                                                                     |  |

| Bit sequential buffer       |                             | 16 bits                                                                                                             |                                                                                                                                                                                |                              |                                                                     |  |

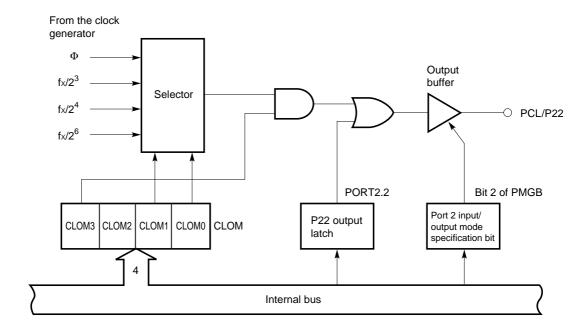

| Clock output                |                             | $\Phi$ , fx/2 <sup>3</sup> , fx/2 <sup>4</sup> , fx/2 <sup>6</sup> (Main system clock: 4.19 MHz operation)          |                                                                                                                                                                                |                              |                                                                     |  |

| A/D converter               |                             | 8-bit resolution × 8 channels (successive-approximation)                                                            |                                                                                                                                                                                |                              |                                                                     |  |

|                             |                             | Capable of low-voltage operation: VDD = 2.7 to 6.0 V                                                                |                                                                                                                                                                                |                              |                                                                     |  |

| Vectored interrupt          |                             | External: 3, Internal: 4                                                                                            |                                                                                                                                                                                |                              |                                                                     |  |

| Test input                  |                             | External : 1, Internal : 1                                                                                          |                                                                                                                                                                                |                              |                                                                     |  |

| System clock oscillator     |                             | Ceramic/crystal oscillator for main system clock oscillation     Crystal oscillator for subsystem clock oscillation |                                                                                                                                                                                |                              |                                                                     |  |

| Standby function            |                             | STOP/HALT mode                                                                                                      |                                                                                                                                                                                |                              |                                                                     |  |

| Operating temperature range |                             | -40 to +85 °C                                                                                                       |                                                                                                                                                                                |                              |                                                                     |  |

| Operating voltage           | 2.7 to 6.0 V                |                                                                                                                     |                                                                                                                                                                                |                              |                                                                     |  |

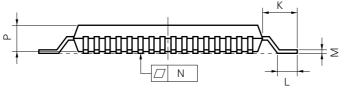

| Package                     |                             | 64-pin plastic shrink DIP (750 mil)                                                                                 |                                                                                                                                                                                |                              |                                                                     |  |

|                             | 64-pin plastic QFP (□14 mm) |                                                                                                                     |                                                                                                                                                                                |                              |                                                                     |  |

## **CONTENTS**

| 1.  | PIN CONFIGURATIONS (TOP VIEW)4                                                                                                                                                                                                      |                                    |  |  |  |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--|--|--|--|--|--|

| 2.  | BLOCK DIAGRAM                                                                                                                                                                                                                       | . 6                                |  |  |  |  |  |  |

| 3.  | PIN FUNCTIONS                                                                                                                                                                                                                       | . 7<br>. 9<br>. 11<br>. 13         |  |  |  |  |  |  |

| 4.  | ARCHITECTURE AND MEMORY MAP OF THE $\mu$ PD75036                                                                                                                                                                                    | . 15                               |  |  |  |  |  |  |

| 5.  | PERIPHERAL HARDWARE FUNCTIONS  5.1 PORTS  5.2 CLOCK GENERATOR  5.3 CLOCK OUTPUT CIRCUIT  5.4 BASIC INTERVAL TIMER  5.5 CLOCK TIMER  5.6 TIMER/EVENT COUNTER  5.7 SERIAL INTERFACE  5.8 A/D CONVERTER  5.9 MULTIFUNCTION TIMER (MFT) | . 17 . 19 . 20 . 21 . 22 . 24 . 26 |  |  |  |  |  |  |

| 6.  | INTERRUPT FUNCTION                                                                                                                                                                                                                  | . 29                               |  |  |  |  |  |  |

| 7.  | STANDBY FUNCTION                                                                                                                                                                                                                    | . 31                               |  |  |  |  |  |  |

| 8.  | RESET FUNCTION                                                                                                                                                                                                                      | . 31                               |  |  |  |  |  |  |

| 9.  | INSTRUCTION SET                                                                                                                                                                                                                     | . 32                               |  |  |  |  |  |  |

| 10. | . ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                        | . 39                               |  |  |  |  |  |  |

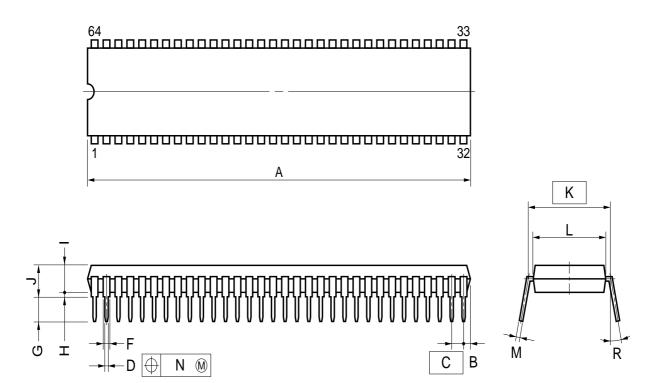

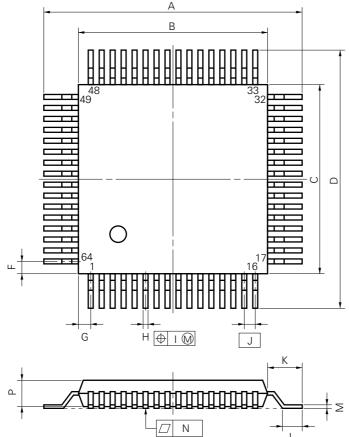

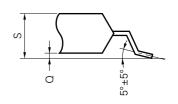

| 11. | . PACKAGE DIMENSIONS                                                                                                                                                                                                                | . 52                               |  |  |  |  |  |  |

| ΑP  | PPENDIX A DEVELOPMENT TOOLS                                                                                                                                                                                                         | . 54                               |  |  |  |  |  |  |

| ΑP  | PPENDIX B RELATED DOCUMENTS                                                                                                                                                                                                         | . 55                               |  |  |  |  |  |  |

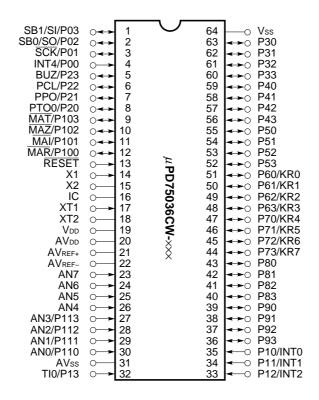

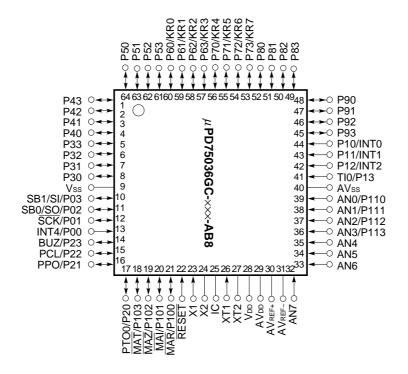

- 1. PIN CONFIGURATIONS (TOP VIEW)

- · 64-pin plastic shrink DIP

• 64-pin plastic QFP

IC: Internally connected (Should be directly connected to VDD)

## Pin names

| P00-03 :             | Port 0                              |         | : | Port 0                             |         |

|----------------------|-------------------------------------|---------|---|------------------------------------|---------|

| P10-13 :             | Port 1                              |         | : | Port 1                             |         |

| P20-23 :             | Port 2                              |         | : | Port 2                             |         |

| P30-33 :             | Port 3                              |         | : | Port 3                             |         |

| P40-43 :             | Port 4                              |         | : | Port 4                             |         |

| P50-53 :             | Port 5                              |         | : | Port 5                             |         |

| P60-63 :             | Port 6                              |         | : | Port 6                             |         |

| P70-73 :             | Port 7                              |         | : | Port 7                             |         |

| P80-83 :             | Port 8                              |         | : | Port 8                             |         |

| P90-93 :             | Port 9                              |         | : | Port 9                             |         |

| P100-103:            | Port 10                             |         | : | Port 10                            |         |

| P110-113:            | Port 11                             |         | : | Port 11                            |         |

| KR0-7 :              | Key Return                          |         | : | Key interrupt input                |         |

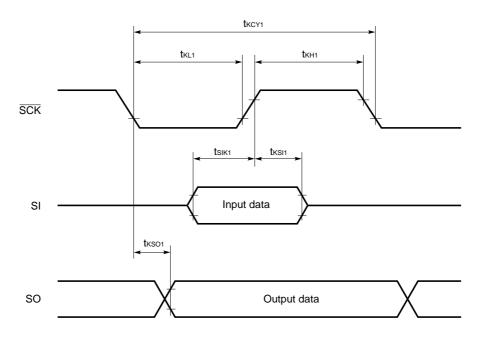

| SCK :                | Serial Clock                        |         | : | Serial clock I/0                   |         |

| SI :                 | Serial Input                        |         | : | Serial data input                  |         |

| SO :                 | Serial Output                       |         | : | Serial data output                 |         |

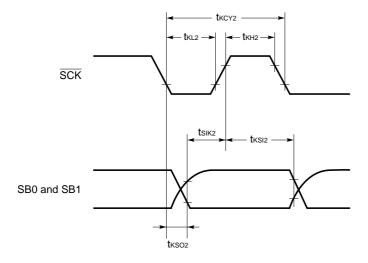

| SB0, 1 :             | Serial Bus 0, 1                     |         | : | Serial bus I/O                     |         |

| RESET :              | Reset Input                         |         | : | Reset input                        |         |

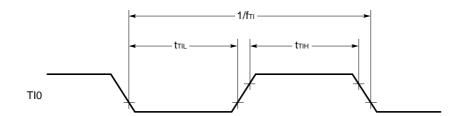

| TIO :                | Timer Input 0                       |         | : | External event pulse input         |         |

| PTO0 :               | Programmable Timer Output 0         |         | : | Timer/event counter output         |         |

| BUZ :                | Buzzer Clock                        |         | : | Arbitrary frequency output         |         |

| PCL :                | Programmable Clock                  |         | : | Clock output                       |         |

| INT0, 1, 4:          | External Vectored Interrupt 0, 1, 4 |         | : | External vectored interrupt input  |         |

| INT2 :               | External Test Input 2               |         | : | External test input                |         |

| X1, 2 :              | Main System Clock Oscillation 1, 2  |         | : | Main system clock oscillation pin  |         |

| XT1, 2 :             | Subsystem Clock Oscillation 1, 2    |         | : | Subsystem clock oscillation pin    |         |

| MAR :                | Reference Integration Control       | 1       | : | Reverse integration signal output  | 1       |

| MAI :                | Integration Control                 | MFT A/D | : | Integration signal output          | MFT A/D |

| MAZ :                | Autozero Control                    | mode    | : | Autozero signal output             | mode    |

| MAT :                | External Comparate Timing Input     | J       | : | External comparator signal input   | J       |

| PPO :                | Programmable Pulse Output           |         |   |                                    |         |

|                      | MFT timer mode                      |         | : | Pulse output MFT timer mode        |         |

| AN0-7 :              | Analog Input 0-7                    |         | : | Analog input                       |         |

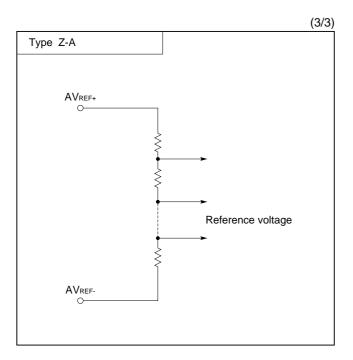

| AV <sub>REF+</sub> : | Analog Reference (+)                |         | : | Analog reference voltage (+) input |         |

| AVREF- :             | Analog Reference (-)                |         | : | Analog reference voltage (-) input |         |

| AV <sub>DD</sub> :   | Analog VDD                          |         | : | A/D converter power supply input   |         |

| AVss :               | Analog Vss                          |         | : | A/D converter GND input            |         |

| Vdd :                | Positive Power Supply               |         | : | Main power supply pin              |         |

| Vss :                | Ground                              |         | : | GND potential pin                  |         |

|                      |                                     |         |   |                                    |         |

Remark MFT: Multifunction timer

ы

**BLOCK DIAGRAM**

# Phase-out/Discontinued

## 3. PIN FUNCTIONS

## 3.1 PORT PINS (1/2)

| Pin             | Input/<br>output | Shared<br>pin | Function                                                                                                                                                     | 8-bit<br>I/O | When reset                                                                         | I/O circuit<br>type <sup>Note</sup> 1 |

|-----------------|------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------------------------|---------------------------------------|

| P00             | Input            | INT4          | 4-bit input port (PORT0).                                                                                                                                    | ×            | Input                                                                              | B                                     |

| P01             | I/O              | SCK           | For P01 - P03, pull-up resistors can be                                                                                                                      |              |                                                                                    | F -A                                  |

| P02             | I/O              | SO/SB0        | provided by software in units of 3 bits.                                                                                                                     |              |                                                                                    | (F) -B                                |

| P03             | I/O              | SI/SB1        |                                                                                                                                                              |              |                                                                                    | M-C                                   |

| P10             | Input            | INT0          | With noise elimination function                                                                                                                              | ×            | Input                                                                              | B -C                                  |

| P11             |                  | INT1          | 4-bit input port (PORT1).                                                                                                                                    |              |                                                                                    |                                       |

| P12             | ]                | INT2          | Pull-up resistors can be provided by                                                                                                                         |              |                                                                                    |                                       |

| P13             |                  | TI0           | software in units of 4 bits.                                                                                                                                 |              |                                                                                    |                                       |

| P20             | I/O              | PTO0          | 4-bit I/O port (PORT2).                                                                                                                                      | ×            | Input                                                                              | E-B                                   |

| P21             |                  | PPO           | Pull-up resistors can be provided by                                                                                                                         |              |                                                                                    |                                       |

| P22             | 1                | PCL           | software in units of 4 bits.                                                                                                                                 |              |                                                                                    |                                       |

| P23             |                  | BUZ           |                                                                                                                                                              |              |                                                                                    |                                       |

| P30Note 2       | I/O              | -             | Programmable 4-bit I/O port (PORT3).                                                                                                                         | ×            | Input                                                                              | E-B                                   |

| P31Note 2       | 1                | -             | I/O can be specified bit by bit. Pull-up                                                                                                                     |              |                                                                                    |                                       |

| P32Note 2       | ]                | _             | resistors can be provided by software in units of 4 bits.                                                                                                    |              |                                                                                    |                                       |

| P33Note 2       | 1                | _             |                                                                                                                                                              |              |                                                                                    |                                       |

| P40 - P43Note 2 | I/O              | -             | N-ch open-drain 4-bit I/O port (PORT4). A pull-up resistor can be provided for each bit (mask option). This open-drain port has a withstand voltage of 10 V. | 0            | High level<br>(when pull-<br>up resistors<br>are provided)<br>or high<br>impedance | М                                     |

| P50 - P53Note 2 | I/O              | _             | N-ch open-drain 4-bit I/O port (PORT5). A pull-up resistor can be provided for each bit (mask option). This open-drain port has a withstand voltage of 10 V. |              | High level<br>(when pull-<br>up resistors<br>are provided)<br>or high<br>impedance | М                                     |

Notes 1. The circle ( ) indicates the Schmitt trigger input.

2. Can directly drive the LED.

## 3.1 PORT PINS (2/2)

| Pin        | Input/<br>output | Shared<br>pin | Function                                                                                    | 8-bit<br>I/O | When reset                 | I/O circuit<br>type <sup>Note 1</sup> |

|------------|------------------|---------------|---------------------------------------------------------------------------------------------|--------------|----------------------------|---------------------------------------|

| P60        | I/O              | KR0           | Programmable 4-bit I/O port (PORT6).                                                        | 0            | Input                      | F-A                                   |

| P61        |                  | KR1           | I/O can be specified bit by bit. Pull-up resistors can be provided by software in           |              |                            |                                       |

| P62        |                  | KR2           | units of 4 bits.                                                                            |              |                            |                                       |

| P63        |                  | KR3           |                                                                                             |              |                            |                                       |

| P70        | I/O              | KR4           | 4-bit I/O port (PORT7).                                                                     |              | Input                      | F-A                                   |

| P71        |                  | KR5           | Pull-up resistors can be provided by software in units of 4 bits.                           |              |                            |                                       |

| P72        |                  | KR6           | software in units of 4 bits.                                                                |              |                            |                                       |

| P73        |                  | KR7           |                                                                                             |              |                            |                                       |

| P80-P83    | I/O              | _             | 4-bit I/O port (PORT8). Pull-up resistors can be provided by software in units of 4 bits.   | ×            | Input                      | E-B                                   |

| P90-P93    | I/O              | -             | 4-bit I/O port (PORT9). Pull-down resistors can be provided by software in units of 4 bits. |              | Input                      | E-D                                   |

| P100Note 2 | I/O              | MAR           | N-ch open-drain 4-bit I/O port (PORT10).                                                    | ×            | High level                 | М                                     |

| P101Note 2 | 1                | MAI           | A pull-up resistor can be provided bit by bit                                               |              | (when pull-up              |                                       |

| P102Note 2 |                  | MAZ           | (mask option). This open-drain port has a withstand                                         |              | resistors are provided) or |                                       |

| P103Note 2 |                  | MAT           | voltage of 10 V.                                                                            |              | high imped-<br>ance        |                                       |

| P110       | Input            | AN0           | 4-bit input port (PORT11)                                                                   |              | Input                      | Y-A                                   |

| P111       | 1                | AN1           | ]                                                                                           |              |                            |                                       |

| P112       |                  | AN2           |                                                                                             |              |                            |                                       |

| P113       | ]                | AN3           |                                                                                             |              |                            |                                       |

Notes 1. The circle (  $\bigcirc$  ) indicates the Schmitt trigger input.

2. Can directly drive the LED.

## 3.2 NON-PORT PINS (1/2)

| Pin                 | Input/<br>output | Shared pin  |                                   | Function                                                   |        | When reset | I/O circuit<br>type <sup>Note 1</sup> |

|---------------------|------------------|-------------|-----------------------------------|------------------------------------------------------------|--------|------------|---------------------------------------|

| TIO                 | Input            | P13         | Input for receive timer/event co  | ving external event pulse signa<br>unter                   | al for | -          | B -C                                  |

| PTO0                | I/O              | P20         | Timer/event co                    | ounter output                                              |        | Input      | E-B                                   |

| PCL                 | I/O              | P22         | Clock output                      |                                                            |        | Input      | E-B                                   |

| BUZ                 | I/O              | P23         |                                   | trary frequency output (for buz<br>em clock trimming)      | zzer   | Input      | E-B                                   |

| SCK                 | I/O              | P01         | Serial clock I/C                  | )                                                          |        | Input      | F -A                                  |

| SO/SB0              | I/O              | P02         | Serial data out<br>Serial bus I/O | put                                                        |        | Input      | (F) -B                                |

| SI/SB1              | I/O              | P03         | Serial data inp                   | ut                                                         |        | Input      | M -C                                  |

| INT4                | Input            | P00         | _                                 | n vectored interrupt input (either falling edge detection) | er     | -          | B                                     |

| INT0                | Input            | P10         | Edge detection                    | n vectored interrupt input                                 | Note 2 | _          | B-C                                   |

| INT1                |                  | P11         | (detection edg                    | e selectable)                                              | Note 3 |            |                                       |

| INT2                | Input            | P12         | Edge detection detection)         | n testable input (rising edge                              | Note 3 | -          | B -C                                  |

| KR0 - KR3           | I/O              | P60 - P63   | Parallel falling                  | edge detection testable input                              |        | Input      | F-A                                   |

| KR4-KR7             | I/O              | P70 - P73   | Parallel falling                  | edge detection testable input                              |        | Input      | F-A                                   |

| MAR                 | I/O              | P100        | In MFT                            | Reverse integration signal o                               | utput  | Note 4     | М                                     |

| MAI                 | I/O              | P101        | integral A/D                      | Integration signal output                                  |        | Note 4     | М                                     |

| MAZ                 | I/O              | P102        | converter<br>mode                 | Autozero signal output                                     |        | Note 4     | М                                     |

| MAT                 | I/O              | P103        |                                   | Comparator input                                           |        | Note 4     | М                                     |

| PPO                 | I/O              | P21         | In MFT timer mode                 | Timer pulse output                                         |        | Input      | E-B                                   |

| AN0 - AN3           | Input            | P110 - P113 | For A/D                           | 8-bit analog input                                         |        | Input      | Y-A                                   |

| AN4 - AN7           |                  | -           | converter                         |                                                            |        |            | Y                                     |

| AVREF+              | Input            | _           | only                              | Reference voltage input (on AV <sub>DD</sub> side)         |        | -          | Z-A                                   |

| AV <sub>REF</sub> - | Input            | -           |                                   | Reference voltage input (on AVss side)                     |        | -          | Z-A                                   |

| AV <sub>DD</sub>    | _                | _           |                                   | Operating power supply                                     |        | -          |                                       |

| AVss                | _                | _           |                                   | Reference GND potential                                    |        | _          | _                                     |

**Notes 1.** The circle (  $\bigcirc$  ) indicates the Schmitt trigger input.

- 2. Clock synchronous

- 3. Asynchronous

- 4. High level (when pull-up resistors are provided) or high impedance

Remark MFT: Multifunction Timer

## 3.2 NON-PORT PINS (2/2)

| Pin             | Input/<br>output | Shared<br>pin | Function                                                                                                                                                                                              | When reset | I/O circuit<br>type <sup>Note</sup> |

|-----------------|------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------------------------------|

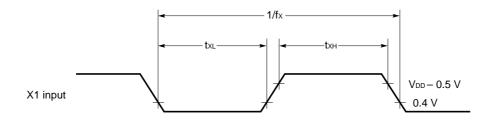

| X1, X2          | Input            | -             | Crystal/ceramic connection for main system clock generation. When external clock signal is used, it is applied to X1, and its reverse phase signal is applied to X2.                                  | _          | -                                   |

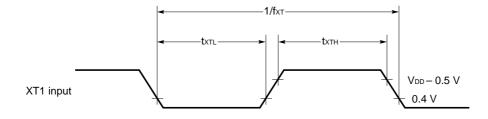

| XT1, XT2        | Input            | _             | Crystal connection for subsystem clock generation. When external clock signal is used, it is applied to XT1, and its reverse phase signal is applied to XT2, XT1 can be used as a 1-bit input (test). | _          | _                                   |

| RESET           | Input            | -             | System reset input                                                                                                                                                                                    | -          | B                                   |

| IC              | _                | _             | Internally connected. (To be directly connected to VDD)                                                                                                                                               | -          | _                                   |

| V <sub>DD</sub> | _                | _             | Positive power supply                                                                                                                                                                                 | _          | -                                   |

| Vss             | _                | _             | GND potential                                                                                                                                                                                         | _          | _                                   |

Note The circle (  $\bigcirc$  ) indicates the Schmitt trigger input.

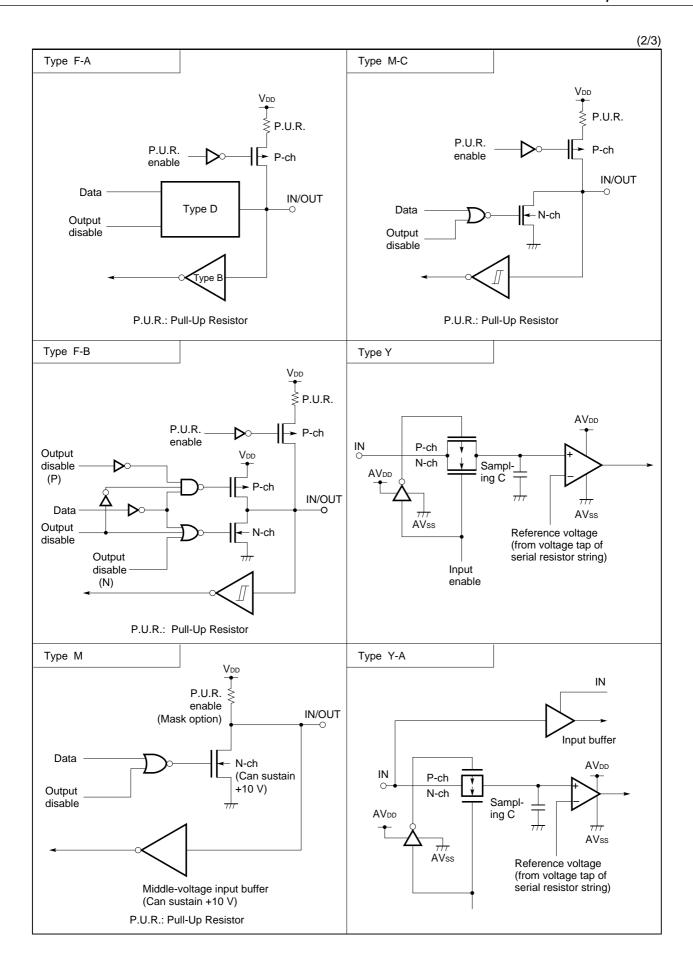

#### 3.3 PIN INPUT/OUTPUT CIRCUITS

The input/output circuit of each  $\mu$ PD75036 pin is shown below in a simplified manner.

(1/3)Type A (For type E-B) Type D (For type E-B, F-A) Data OUT IN Output disable Push-pull output which can be set to high-impedance output CMOS input buffer (off for both P-ch and N-ch) Type B Type E-B P.U.R. enable IN Data IN/OUT Type D Output disable Schmitt trigger input with hysteresis P.U.R.: Pull-Up Resistor Type B-C Type E-D Data IN/OUT Type D Output disable P.U.R. enable P.D.R IN O ≷ P.D.R. P.D.R.: Pull-Down Resistor P.U.R.: Pull-Up Resistor

## 3.4 MASK OPTION SELECTION

The following mask options are available for selection for each pin.

| Pin name                              | Mask option                                                   |                                                                        |  |  |  |

|---------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| P40 - P43,<br>P50 - P53,<br>P100-P103 | Pull-up resistor provided     (specifiable bit by bit)        | ② Pull-up resistor not provided<br>(specifiable bit by bit)            |  |  |  |

| XT1, XT2                              | Feedback resistor provided     (if a subsystem clock is used) | ② Feedback resistor not provided<br>(if a subsystem clock is not used) |  |  |  |

## **★** 3.5 CONNECTION OF UNUSED PINS

| Pin                 | Recommended connection                      |

|---------------------|---------------------------------------------|

| P00/INT4            | To be connected to Vss                      |

| P01/SCK             | To be connected to Vss or VDD               |

| P02/SO/SB0          |                                             |

| P03/SI/SB1          |                                             |

| P10/INT0-P12/INT2   | To be connected to Vss                      |

| P13/TI0             |                                             |

| P20/PTO0            | Input state : To be connected to Vss or     |

| P21/PPO             | V <sub>DD</sub>                             |

| P22/PCL             | Output state:To be open                     |

| P23/BUZ             |                                             |

| P30-P33             |                                             |

| P40-P43             |                                             |

| P50-P53             |                                             |

| P60/KR0-P63/KR3     |                                             |

| P70/KR4-P73/KR7     |                                             |

| P80-P83             |                                             |

| P90-P93             |                                             |

| P100/MAR            |                                             |

| P101/MAI            |                                             |

| P102/MAZ            |                                             |

| P103/MAT            |                                             |

| P110/AN0-P113/AN3   | To be connected to Vss or VDD               |

| AN4-AN7             |                                             |

| AV <sub>REF+</sub>  | To be connected to Vss                      |

| AV <sub>REF</sub> - |                                             |

| AVss                |                                             |

| AV <sub>DD</sub>    | To be connected to V <sub>DD</sub>          |

| XT1                 | To be connected to Vss or VDD               |

| XT2                 | To be open                                  |

| IC                  | To be directly connected to V <sub>DD</sub> |

#### 4. ARCHITECTURE AND MEMORY MAP OF THE $\mu$ PD75036

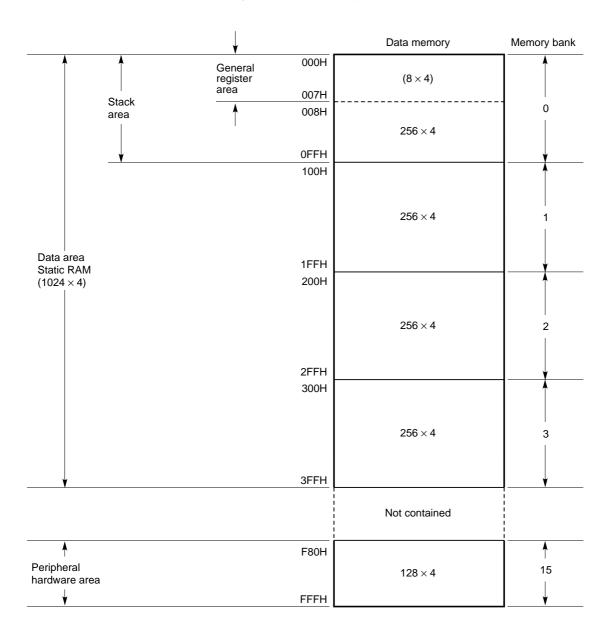

The  $\mu$ PD75036 has two architectural features:

- Bank configuration of data memory: Static RAM (1024 words × 4 bits)

Peripheral hardware (128 × 4 bits)

- Memory mapped I/O

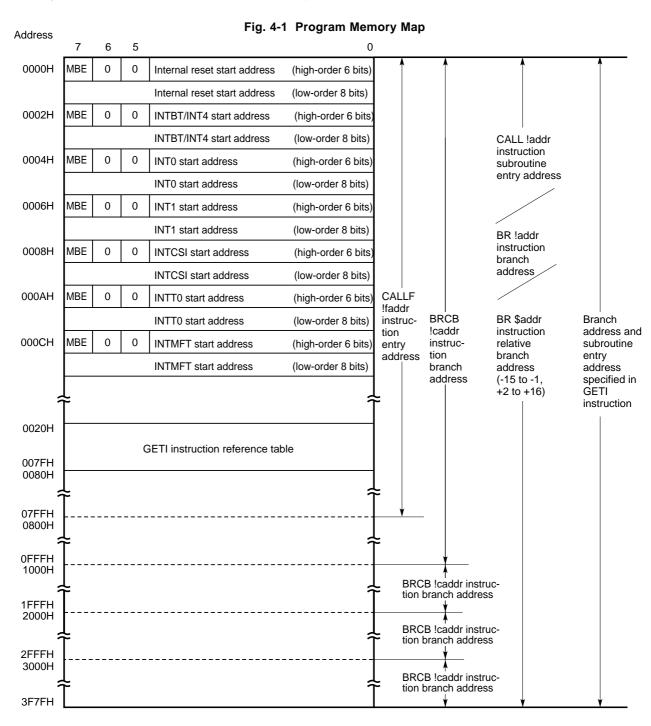

Fig. 4-1 and 4-2 show the memory maps for the  $\mu$ PD75036.

**Remark** In addition to the above, the BR PCDE and BR PCXA instructions can cause a branch to an address with only the low-order 8 bits of the PC changed.

Fig. 4-2 Data Memory Map

#### 5. PERIPHERAL HARDWARE FUNCTIONS

#### 5.1 PORTS

The  $\mu$ PD75036 has the following three types of I/O port:

- 12 CMOS input ports (Ports 0, 1, and 11)

- 24 CMOS I/O ports (Ports 2, 3, 6, 7, 8, and 9)

- 12 N-ch open-drain I/O ports (Ports 4, 5, and 10)

Total: 48 ports

Table 5-1 Functions of Ports

| Port (symbol)                                                            | Function                                       | Operation and feature                                                                                                            | Remarks                                                                         |

|--------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| PORT0<br>PORT1                                                           | 4-bit input                                    | Allows input and test at any time regardless of the operation modes of dual function pins.                                       | Also used as SO/SB0, SI/SB1, SCK, INT0-INT2, INT4, and TI0 pins.                |

| PORT3 <sup>Note</sup><br>PORT6                                           | 4-bit I/O                                      | Allows input or output mode setting in units of one bit.                                                                         | Port 6 is also used as KR0-KR3 pins.                                            |

| PORT2<br>PORT7                                                           |                                                | Allows input or output mode setting in units of four bits.  Ports 6 and 7 make a pair, allowing data I/O in units of             | Port 2 is also used as PTO0, PPO, PCL, and BUZ pins.                            |

|                                                                          |                                                | eight bits.                                                                                                                      | Also used as KR4-KR7 pins.                                                      |

| PORT4 <sup>Note</sup><br>PORT5 <sup>Note</sup><br>PORT10 <sup>Note</sup> | 4-bit I/O<br>(N-ch<br>open-drain,<br>withstand | Allows input or output mode setting in units of four bits.  Ports 4 and 5 make a pair, allowing data I/O in units of eight bits. | Use of an internal pull-up registor can be mask-programmed in units of one bit. |

|                                                                          | voltage:<br>10 V)                              |                                                                                                                                  | Port 10 is also used as MAR, MAI, MAZ, and MAT pins.                            |

| PORT8<br>PORT9                                                           | 4-bit I/O                                      | Allows input or output mode setting in units of four bits.                                                                       |                                                                                 |

| PORT11                                                                   | 4-bit input                                    | Port for 4-bit input                                                                                                             | Port 11 is also used as AN0-AN3 pins.                                           |

Note Ports 3, 4, 5 and 10 can directly drive an LED.

#### 5.2 CLOCK GENERATOR

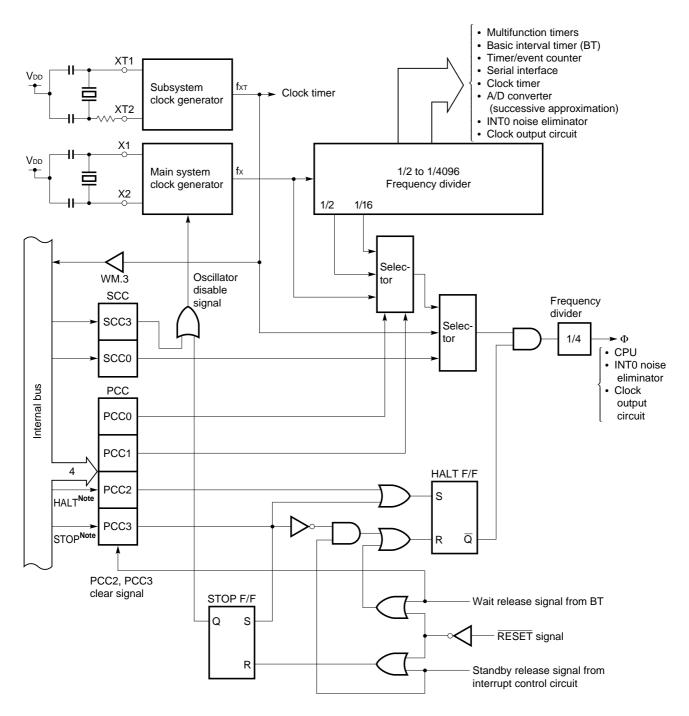

Operation of the clock generator is specified by the processor clock control register (PCC) and system clock control register (SCC).

The main system clock or subsystem clock can be selected.

The instruction execution time is variable.

- 0.95  $\mu$ s, 1.91  $\mu$ s, 15.3  $\mu$ s (main system clock: 4.19 MHz)

- 122 μs (subsystem clock: 32.768 kHz)

#### Fig. 5-1 Block Diagram of the Clock Generator

Note Instruction execution

Remarks 1. fx : Main system clock frequency

2. fxt : Subsystem clock frequency

3.  $\Phi = CPU clock$

4. PCC: Processor clock control register

5. SCC: System clock control register

**6.** One clock cycle (tcy) of the CPU clock  $(\Phi)$  is equal to one machine cycle of an instruction. See **Chapter 10** for details of tcy.

#### **5.3 CLOCK OUTPUT CIRCUIT**

The clock output circuit outputs a clock pulse signal on the P22/PCL pin for remote control or for supplying clock pulses to a peripheral LSI device.

Fig. 5-2 Configuration of the Clock Output Circuit

**Remark** The clock output circuit is designed so that pulses with short widths do not appear in enabling or disabling clock output.

#### **5.4 BASIC INTERVAL TIMER**

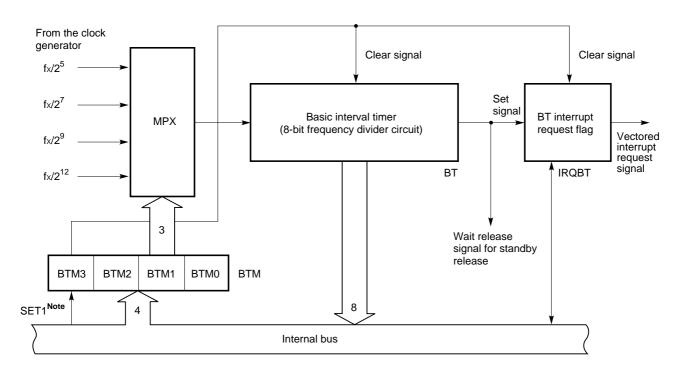

The basic interval timer provides the following functions:

- Interval timer operation that generates a reference time interrupt

- · Application of watchdog timer for detecting program crashes

- · Selection of a wait time for releasing the standby mode, and counting

- · Reading the count value

Fig. 5-3 Configuration of the Basic Interval Timer

Note Instruction execution

#### 5.5 CLOCK TIMER

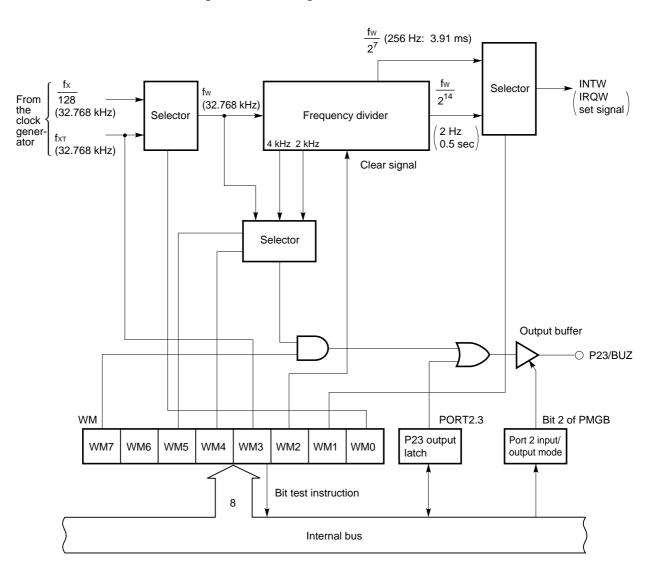

The  $\mu$ PD75036 contains one channel for a clock timer. The clock timer provides the following functions:

- The clock timer sets the test flag (IRQW) every 0.5 seconds.

The standby mode can be released with IRQW.

- Either the main system clock or subsystem clock can produce 0.5-second intervals.

- The fast-forward mode produces an interval 128 times faster (3.91 ms), which is useful for program debugging and testing.

- An arbitrary frequency (2.048, 4.096, or 32.768 kHz) can be output to the P23/BUZ pin, so that it can be used for sounding the buzzer and system clock frequency trimming.

- The frequency divider can be cleared, so the clock can start from zero seconds.

Fig. 5-4 Block Diagram of the Clock Timer

The values in parentheses indicates are for fx = 4.194304 MHz and fxT = 32.768 kHz

#### 5.6 TIMER/EVENT COUNTER

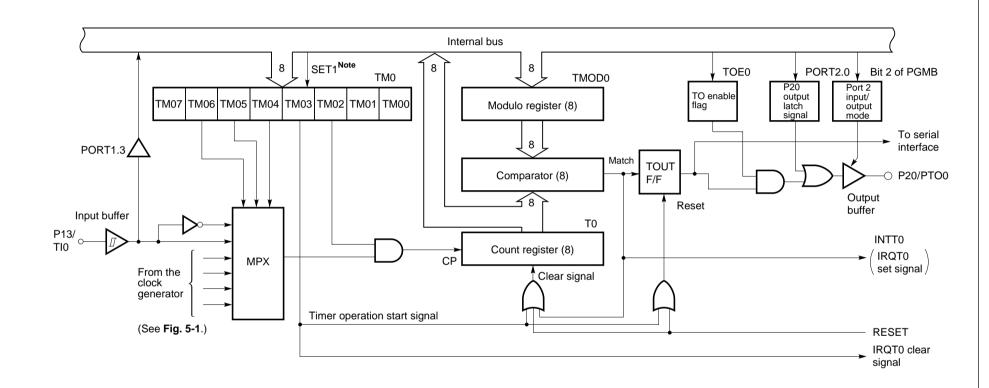

The  $\mu$ PD75036 contains one channel of timer/event counter. The timer/event counter provides the following functions:

- Programmable interval timer operation

- Output of a square wave at a given frequency to the PTO0 pin

- Event counter operation

- Frequency divider operation that divides TI0 pin input by N and outputs the result to the PTO0 pin

- Supply of serial shift clock signal to a serial interface circuit

- Function of reading the state of counting

Fig. 5-5 Block Diagram of the Timer/Event Counter

Note Instruction execution

#### 5.7 SERIAL INTERFACE

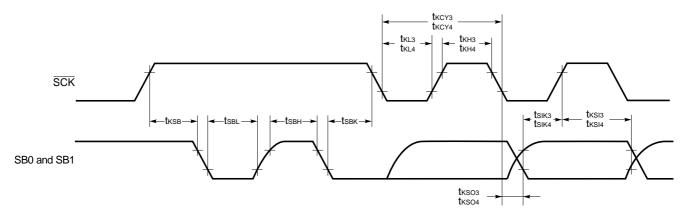

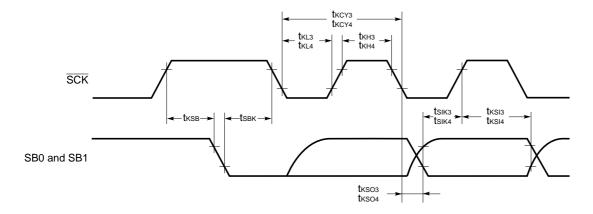

The  $\mu$ PD75036 has three modes.

- Three-wire serial I/O mode (The first bit is switchable between MSB and LSB.)

- Two-wire serial I/O mode (The first bit is MSB.)

- SBI mode (The first bit is MSB.)

The three-wire serial I/O mode enables connections to be made with the 75X series, 78K series, and many other types of I/O devices.

The two-wire serial I/O mode and SBI mode enable communication with two or more devices.

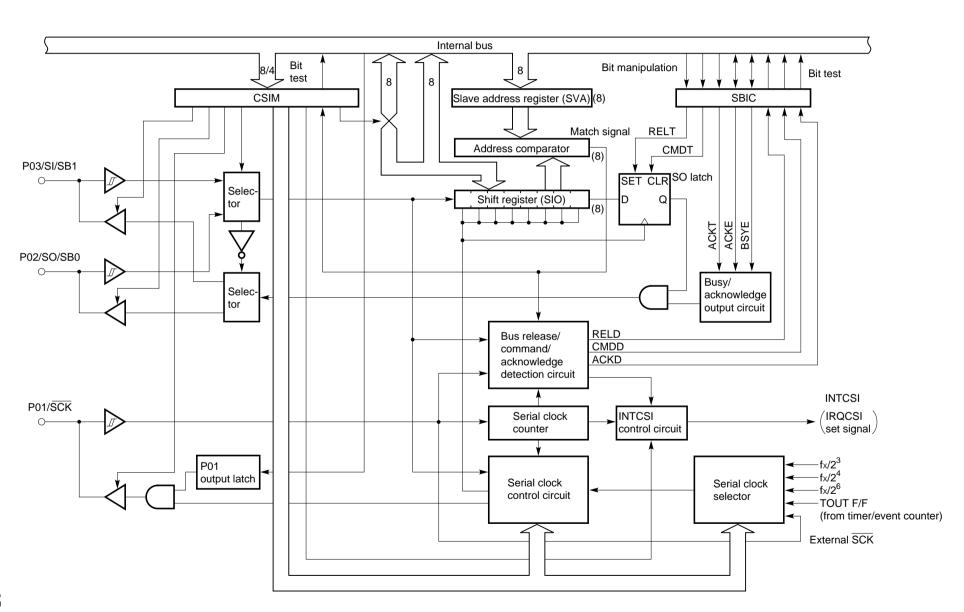

Fig. 5-6 Block Diagram of the Serial Interface

#### 5.8 A/D CONVERTER

The  $\mu$ PD75036 contains an 8-bit resolution analog/digital (A/D) converter that has eight analog input channels (AN0 - AN7).

The A/D converter employs the successive-approximation method.

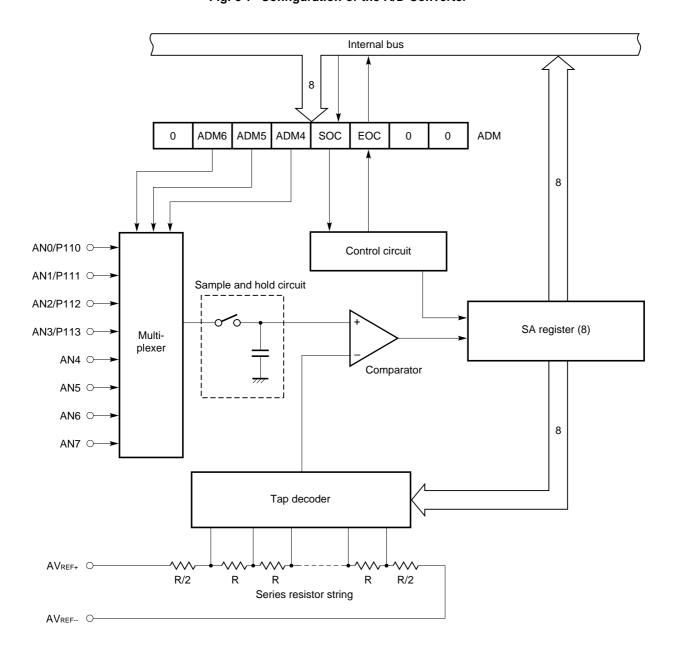

Fig. 5-7 Configuration of the A/D Converter

## 5.9 MULTIFUNCTION TIMER (MFT)

The  $\mu$ PD75036 contains one multifunction timer (MFT). The MFT has four operation modes. Each mode provides the following functions:

- 8-bit timer mode

- Operates as a programmable interval timer.

- Outputs a square wave of an arbitrary frequency on the PPO pin.

- PWM output mode

- Outputs a 6-bit, 7-bit, or 8-bit precision PWM signal on the PPO pin.

- 16-bit free-running timer mode

- Operates as an interval timer that generates an interrupt at specified time intervals.

- Usable as a one-shot timer.

- Integral A/D converter modes

- Outputs a control signal for a 16-bit integral A/D converter.

- Allows a resolution to be selected from 13 bits, 14 bits, 15 bits, and 16 bits.

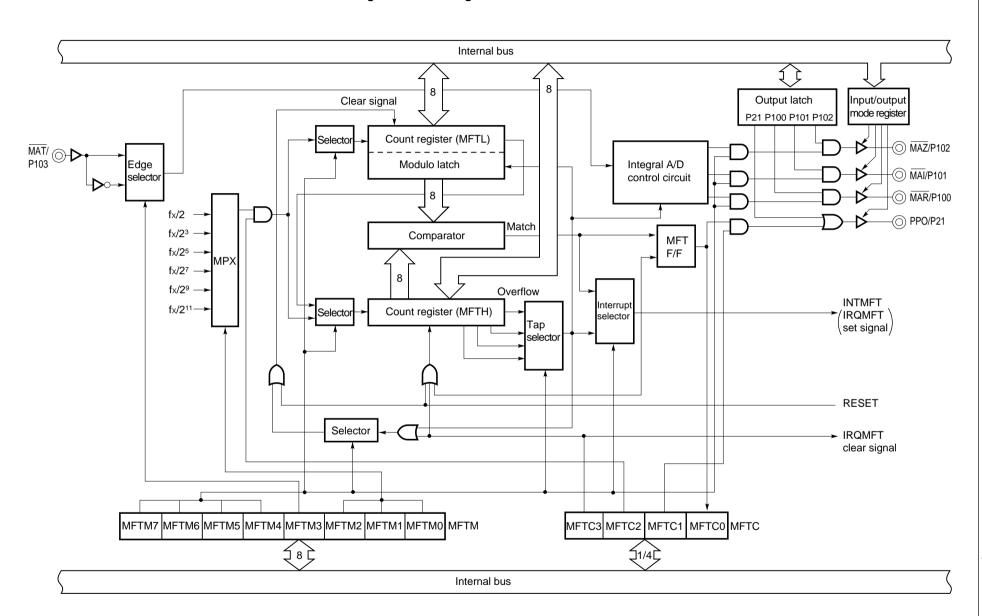

Fig. 5-8 Block Diagram of the Multifunction Timer

#### 6. INTERRUPT FUNCTION

The  $\mu$ PD75036 has nine vectored interrupt sources and provides multiple interrupts by software control. It also has two types of edge detected testable input pins.

The interrupt control circuitry of the  $\mu$ PD75036 has the following features:

- Vectored interrupts are controlled by the hardware. Whether to accept an interrupt is controlled by an interrupt flag (IE×××) and interrupt master enable flag (IME).

- An interrupt start address can be freely set.

- An interrupt request flag (IRQ×××) can be tested. (Whether an interrupt has occurred can be checked by software.)

- A standby mode can be released. (What interrupt source to release can be selected using an interrupt enable flag.)

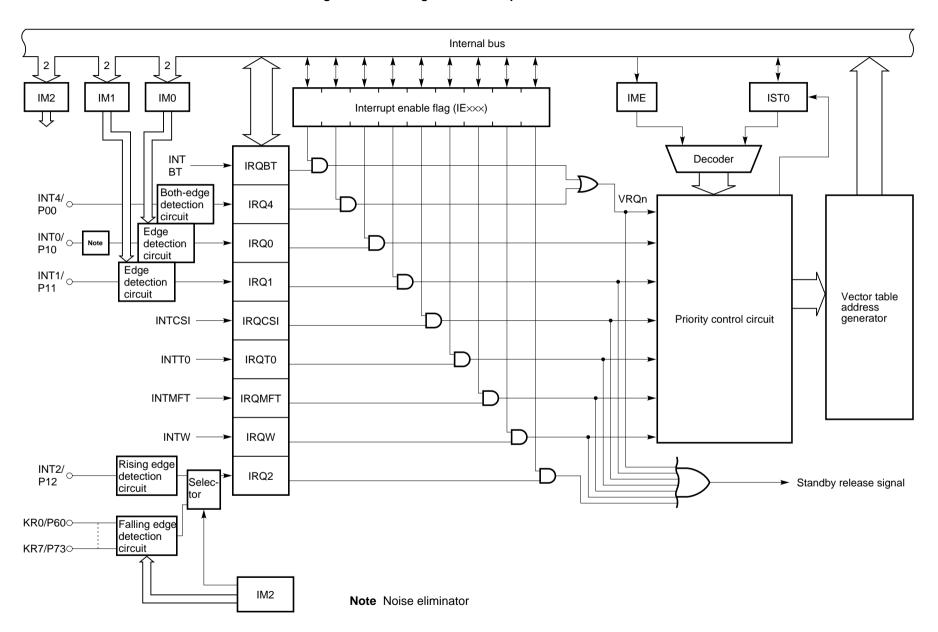

Fig. 6-1 Block Diagram of Interrupt Control Circuit

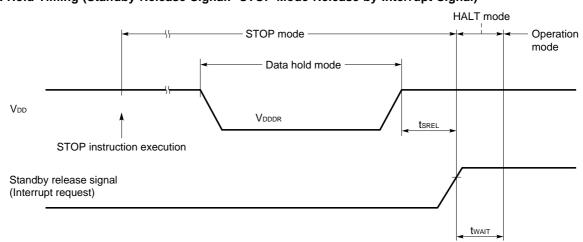

## 7. STANDBY FUNCTION

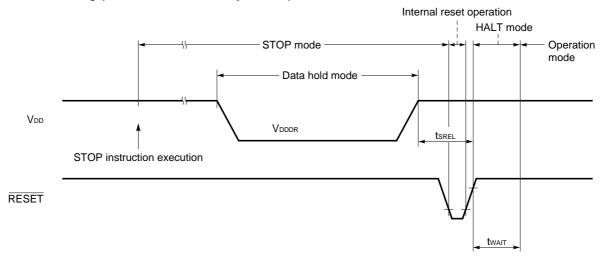

To reduce the power consumption of the system waiting for a program input, the  $\mu$ PD75036 has two standby modes STOP and HALT modes.

**Table 7-1 Standby Modes and Operation Status**

|                         |                      | STOP mode                                                                                                     | HALT mode                                                                                                                   |  |

|-------------------------|----------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Instruction for setting |                      | STOP instruction                                                                                              | HALT instruction                                                                                                            |  |

| Syste                   | m clock at setting   | This mode can be set only when the main system clock is used.                                                 | This mode can be set when either the main system clock or subsystem clock is used.                                          |  |

|                         | Clock generator      | Only the main system clock is stopped.                                                                        | Only CPU clock $\Phi$ is stopped (with oscillation continued).                                                              |  |

|                         | Basic interval timer | Operation is stopped.                                                                                         | Operation is possible only when the main system clock is oscillated. (Sets IRQBT at reference time intervals)               |  |

| tatus                   | Serial interface     | Operation is possible only when external SCK input is selected for the serial clock.                          | Operation is possible only when external SCK input is selected for the serial clock or the main system clock is oscillated. |  |

| Operation status        | Timer/event counter  | Operation is possible only when TI0 pin input is selected for the count clock.                                | Operation is possible only when TI0 pin input is selected for the count count clock or the main system clock is oscillated. |  |

|                         | Clock timer          | Operation is possible when $f_{XT}$ is selected for the count clock.                                          | Operation is possible.                                                                                                      |  |

|                         | A/D converter        | Operation is stopped.                                                                                         | Operation is possible. Note                                                                                                 |  |

|                         | Multifunction timer  | Operation is stopped.                                                                                         | Operation is possible. Note                                                                                                 |  |

|                         | External interrupt   | INT1, INT2, and INT4 are enabled. INT0 is dis                                                                 | sabled.                                                                                                                     |  |

|                         | CPU                  | Operation is stopped.                                                                                         |                                                                                                                             |  |

| Release signal          |                      | Interrupt request signals sent out from hardware, which are enabled by interrupt enable flags, or RESET input | Interrupt request signals sent out from hardware, which are enabled by interrupt enable flags, or RESET input               |  |

**Note** Operation is possible only when the main system clock operates.

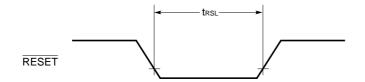

## 8. RESET FUNCTION

The  $\mu$ PD75036 is reset by  $\overline{\text{RESET}}$  signal input.

#### 9. INSTRUCTION SET

#### (1) Operand identifier and its descriptive method

The operands are described in the operand column of each instruction according to the descriptive method for the operand format of the appropriate instructions (refer to *RA75X Assembler Package User's Manual, Language* (EEU-1363) for details). For descriptions in which alternatives exist, one element should be selected. Capital letters and plus and minus signs are keywords; therefore, they should be described as they are.

For immediate data, the appropriate numerical values or labels should be described.

| Identifier                 | Description                                                                          |

|----------------------------|--------------------------------------------------------------------------------------|

| reg                        | X, A, B, C, D, E, H, L                                                               |

| reg1                       | X, B, C, D, E, H, L                                                                  |

| rp                         | XA, BC, DE, HL                                                                       |

| rp1                        | BC, DE, HL                                                                           |

| rp2                        | BC, DE                                                                               |

| rpa                        | HL, DE, DL                                                                           |

| rpa1                       | DE, DL                                                                               |

| n4                         | 4-bit immediate data or label                                                        |

| n8                         | 8-bit immediate data or label                                                        |

| mem <sup>Note</sup><br>bit | 8-bit immediate data or label 2-bit immediate data or label                          |

| fmem<br>pmem               | FB0H - FBFH, FF0H - FFFH immediate data or label FC0H - FFFH immediate data or label |

| addr                       | 0000H - 3F7FH immediate data or label                                                |

| caddr                      | 12-bit immediate data or label                                                       |

| faddr                      | 11-bit immediate data or label                                                       |

| taddr                      | 20H - 7FH immediate data (however, bit 0 = 0) or label                               |

| PORTn                      | PORT0 - PORT11                                                                       |

| IExxx                      | IEBT, IECSI, IET0, IE0, IE1, IE2, IE4, IEW, IEMFT                                    |

| MBn                        | MB0, MB1, MB2, MB3, MB15                                                             |

Note Only even address can be specified for mem when processing 8-bit data.

### (2) Symbol definitions in operation description

A : A register; 4-bit accumulator

B : B register

C : C register

D : D register

E : E register

H : H register

L : L register

X : X register

XA : Pair register (XA); 8-bit accumulator

BC : Pair register (BC)

DE : Pair register (DE)

HL : Pair register (HL)

PC : Program counter

SP : Stack pointer

CY: Carry flag; Bit accumulator

PSW: Program status word

MBE: Memory bank enable flag

PORTn: Port n (n = 0 to 11)

PORTI . PORTI (II = 0 to 11)

IME : Interrupt master enable flag

IExxx : Interrupt enable flag

MBS : Memory bank selection registerPCC : Processor clock control register

. : Address bit delimiter(xx) : Contents addressed by xxxxH : Hexadecimal data

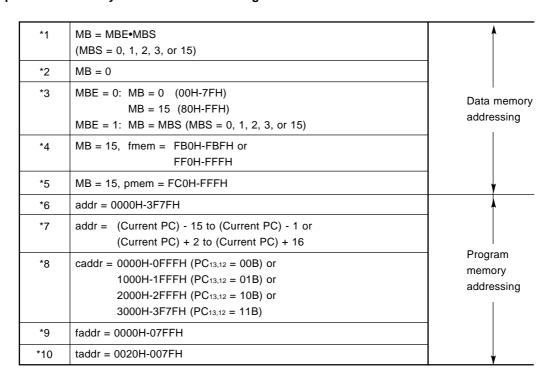

#### (3) Explanation of the symbols in the addressing area field

Remarks 1. MB indicates an accessible memory bank.

- 2. For \*2, MB is always 0 irrespective of MBE and MBS.

- 3. For \*4 and \*5, MB is always 15 irrespective of MBE and MBS.

- 4. \*6 to \*10 indicate each addressable area.

## (4) Description of machine cycle column

S indicates the number of machine cycles necessary for skipping any skip instruction. The value of S changes as follows:

| • | When no skip is performed                                               | S = 0 |

|---|-------------------------------------------------------------------------|-------|

| • | When a 1-byte or 2-byte instruction is skipped                          | S = 1 |

| • | When a 3-byte instruction (BR !addr, CALL !addr instruction) is skipped | S = 2 |

## Caution The GETI instruction is skipped in one machine cycle.

One machine cycle is equivalent to one CPU clock  $\Phi$  cycle (tc $\gamma$ ). Therefore, the length of the machine cycle can be selected from three different lengths by the PCC setting.

| Group     | Mne-<br>monic | Operand   | Bytes | Machin-<br>ing<br>cycle | Operation                                     | Address-<br>ing area | Skip<br>condition |

|-----------|---------------|-----------|-------|-------------------------|-----------------------------------------------|----------------------|-------------------|

| Transfer  | MOV           | A, #n4    | 1     | 1                       | A ← n4                                        |                      | String A          |