# THOMSON COMPOSANTS MILITAIRES ET SPATIAUX

# 27C1001

# 1024 K (128 K × 8) CMOS UV ERASABLE PROM

#### DESCRIPTION

The 27C1001 is a high speed 1 Mbit ultraviolet erasable and electrically programmable EPROM ideally suited for 8-bit microprocessors systems requiring large programs.

It is organized as 131072 words by 8 bits, and packaged in a 32 pin Window Ceramic Frit-Seal package or in a 32 pin LCCC. The 27C1001 has a single +5 V power supply and an access time of 150 ns

The 27C1001 also features a standby mode which reduces the power dissipation without increasing access time. The active current is 50 mA while the maximum standby current is only 1 mA. The standby mode is achieved by applying a TTL-high signal to the CE input. The 27C1001 enables implementation of new, advanced systems with firmware intensive architectures.

The combination of the 27C1001s high density, and new advanced microprocessors having mega-bit addressing capability provides designers with opportunities to engineer user-friendly, high reliability, high-performance systems. The 27C1001 large storage capability enables it to function as a high density software carrier. The 27C1001 has an «Electronic Signature» that allows programmers to automatically identify type and pinout.

#### **MAIN FEATURES**

- Very fast access time: 150 ns.

- Compatible to high speed microprocessors zero wait state.

- Low «CMOS» consumption: active current: 100 mA max standby current: 1 mA max

- Programming voltage: 12.5 V.

- Electronic signature for automated programming.

- Programming time in the 6 seconds range (PRESTO II algorithm).

- 32 pins JEDEC approved pin out.

- Power supply: V<sub>CC</sub> = 5 V<sub>DC</sub> ± 10 %.

- Military temperature range : T<sub>C</sub> = -55, +125°C.

## SCREENING / QUALITY

This product is manufactured in full compliance with:

- CECC 90000 (class B, quality assessment level Y).

- MIL-STD-883 B.

- TMS STANDARD.

32 pins CERDIP / Q suffix

32 pins LCCC / EQ suffix

September 1990

# SUMMARY

# A · GENERAL DESCRIPTION

- 1 DETAILED BLOCK DIAGRAM

- 2 PIN ASSIGNEMENTS

- 3 TERMINAL DESIGNATIONS

# **B** - DETAILED SPECIFICATIONS

- 1 SCOPE

- 2 APPLICABLE DOCUMENTS

- 2.1 MIL-STD 883

- 2.2 · CECC 90000

# 3 - REQUIREMENTS

- 3.1 General

- 3.2 Design and construction

- 3.3 Electrical characteristics

- 3.4 Thermal characteristics

- 3.5 · Mechanical and environment

- 3.6 Marking

# 4 - QUALITY CONFORMANCE INSPECTION4.1 - DESC / MIL-STD-883

- 4.2 CECC

## 5 - ELECTRICAL CHARACTERISTICS

- 5.1 · General requirements

- 5.2 Static characteristics

- 5.3 · Dynamic characteristics

- 5.4 Test conditions specific to the device

- 55 Capacitance

- 5.6 Burn-in conditions

# 6 - FUNCTIONAL DESCRIPTION

- 6.1 Device operation

- 6.2 Programming

- 6.3 High speed programming

- 6.4 · Erasure operation

- 6.5 Function table

# 7 - PREPARATION FOR DELIVERY

- 7.1 Packaging

- 7.2 Certificate of compliance

- 8 HANDLING

# 9 - PACKAGE MECHANICAL DATA

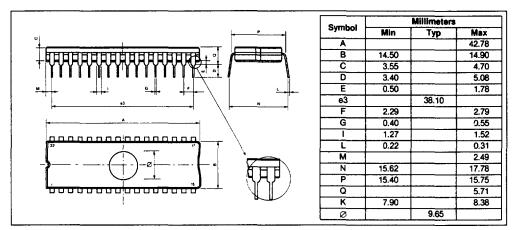

- 9.1 32 pins DIL CERDIP with window package

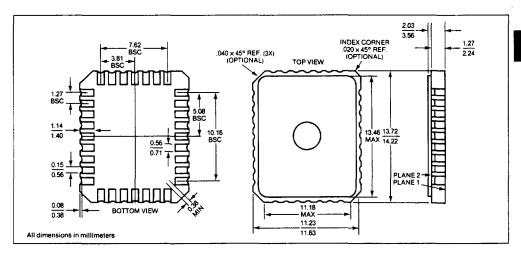

- 9.2 32 pins Lead Less Chip Carrier

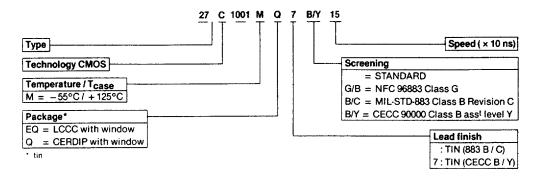

#### 10 - ORDERING INFORMATION

- 10.1 HI-REL product

- 10.2 Standard product

# A · GENERAL DESCRIPTION

#### INTRODUCTION

The 27C1001 series are 131072 words by 8-bit ultraviolet-light, erasable, electrically programmable read-only memories. These devices are fabricated using. CMOS E4 technology for high speed and simple interface with MOS and bipolar circuits. The data outputs are three-state for connecting multiple devices to a common bus. The 27C1001 is pin compatible with existing 32-pin EPROMs. It is offered in both and leadless chip carrier dual-in-line ceramic package (Q and EQ suffix) rated for operation from - 55°C to + 125°C.

Since these EPROMs operate from a single 5 V supply (in the read mode), they are ideal for use in microprocessor-based systems. One other (12.5 V) supply is needed for programming but all programming signals are TTL level.

There are seven modes of operation for the 27C1001. Read mode requires a single 5 V supply. All inputs are TTL level except for Vpp during programming (12.5 V) and 12 V on A9 for signature mode.

The 27C1001 has a standby mode that reduces the maximum power dissipation. But in this case the read access of the memory is not possible.

Maximum operating power dissipation: 550 mW at  $T_C = -55^{\circ}\text{C}/275 \text{ mW}$  at  $T_C = +125^{\circ}\text{C}$ .

Maximum standby power dissipation: 5 mW at 5 V.

This memory has static operation; no clocks no refresh.

This memory is fully compatible with TTL families S, LS, AS, ALS.

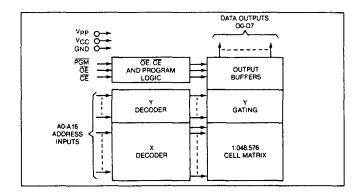

# 1 - DETAILED BLOCK DIAGRAM

The functional block diagram is given in Figure 1 below.

FIGURE 1 - 27C1001 BLOCK DIAGRAM.

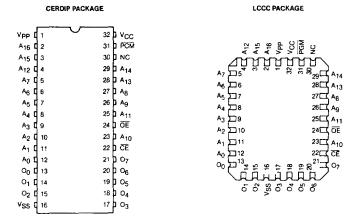

#### 2 · PIN ASSIGNEMENTS

FIGURE 2 - PIN CONFIGURATION.

#### 3 · TERMINAL DESIGNATIONS

The function and relevant symbol of each terminal of the device are given in the Figure 3 below.

# PIN FUNCTIONS

| A0-A16 | Address Input       |

|--------|---------------------|

| CE     | Chip Enable Input   |

| ÖĒ     | Output Enable       |

| PGM    | Program             |

| 00-07  | Data Input / Output |

| NC     | No Connected        |

FIGURE 3

# **B** · DETAILED SPECIFICATIONS

# 1 - SCOPE

This drawing describes the specific requirements for the CMOS UV erasable PROM memories 27C1001, in compliance either with MIL-M-38510 rev C or CECC 90000.

# 2 · APPLICABLE DOCUMENTS

#### 2.1 · MIL·STD-883

- 1) MIL-STD-883: test methods and procedures for electronics

- 2) MIL-M-38510: general specifications for microcircuits

#### 2.2 · CECC 90000

- 1) CECC 90000

- 2) Specification 9011x-0xx

#### 3 · REQUIREMENTS

#### 3.1 - General

The microcircuits are in accordance with the applicable document and as specified herein.

#### 3.2 · Design and construction

#### 3.2.1 - Terminal connections

Depending on the package, the terminal connections shall be is shown in figure 2.

#### 3.2.2 - Lead material and finish

Lead material and finish shall be any option of MIL-M-38510 tin dipped.

#### 3.2.3 - Package

The macrocircuits are packaged in a hermetically sealed ceramic package which is conform to case outlines of MIL-M-38510 appendix C (when defined):

- 32 lead DIL

- 32 lead LCCC, style C12.

The precise case outlines are described into MIL-M-38510.

#### 3.3 · Electrical characteristics

#### 3.3.1 - Absolute maximum ratings (Table 1)

Limiting conditions (ratings) defined below shall not be for inspection purposes. Some limiting conditions (ratings) may however be taken in other parts of this specification as detail conditions for an applicable test.

If limiting condition(s) is (are) got over during testing or using of the component, the device can be damaged, even destroyed. Anyhow, component characteristics can be disturbed and they are not guaranteed any more.

Table 1 - Absolute maximum ratings

Unless otherwise stated, all voltages are referenced to the reference terminal as defined in Figure 3.

| Symbol              | Parameter                           |                               | Min   | Max    | Unit |

|---------------------|-------------------------------------|-------------------------------|-------|--------|------|

| Vcc                 | Supply voltage                      |                               | - 0.6 | 7      | ٧    |

| Vpp                 | Programming supply voltage          |                               | - 0.6 | 14     | ٧    |

| ٧.                  | locut voltage                       | (Except A9)                   | - 0.6 | 6.5    | ٧    |

| VI                  | Input voltage                       | (A9)                          | - 0.6 | 13.5   | ٧    |

| ٧o                  | Output voltage                      |                               | - 0.6 | Vcc +1 | ٧    |

| Voz                 | Off-state voltage                   |                               | 0.6   | Vcc +1 | ٧    |

| 10                  | Output current                      |                               |       | 5      | mA   |

| l <sub>l</sub>      | Input current                       |                               |       | 15     | mA   |

| Do may              | May cover dissipation               | T <sub>C</sub> = 25°C / -55°C |       | 550    | mW   |

| P <sub>D</sub> max. | Max. power-dissipation              | $T_C \approx 125^{\circ}C$    |       | 275    | mW   |

| Tcase               | Operating temperature               |                               | - 55  | + 125  | °C   |

| T <sub>stg</sub>    | Storage temperature                 |                               | - 65  | + 150  | °C   |

| Tlead               | Lead temperature (soldering : 10 s) |                               |       | + 300  | °C   |

Note: Stresses above those listed under «Absolute maximum ratings» may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 3.3.2 - Recommanded conditions of use and guaranteed characteristics

#### a) Guaranteed characteristics (Tables 4 and 5)

The characteristics associated to a specified measurement in the detail specification shall only be for inspection purposes.

Such characteristic defined in this specification in guaranteed only under the conditions and within the limits which are specified for the relevant measurement. Unless otherwise specified, this guarantee applies within all the recommanded operating ranges specified below.

## b) Recommended conditions of use (Table 2)

To the correct operation of the device, the conditions of use shall be within the ranges specified below (see also above).

These conditions shall not be for inspection purposes.

Some recommanded values may, however, be taken in other parts of this specification as detail conditions for an applicable test (Table 10).

Table 2

| Symbol | Parameter                | Min  | Max '                 | Unit |

|--------|--------------------------|------|-----------------------|------|

| Vcc    | Supply voltage           | 4.5  | 5.5                   | ٧    |

| VIL    | Low level input voltage  | -0.1 | 0.8                   | V    |

| VIH    | High level input voltage | 2    | V <sub>CC</sub> + 0.5 | ٧    |

| Tcase  | Operating temperature    | 55   | + 125                 | °C   |

#### 3.4 · Thermal characteristics

#### Table 3

| Package          | Symbol | Parameter                                                               | Value    | Unit |

|------------------|--------|-------------------------------------------------------------------------|----------|------|

| CERDIP<br>DIL 28 | θJ-Q   | Thermal resistance - Ceramic<br>Junction-to-Ambient<br>Junction-to-Case | 50<br>7  | °C/W |

| LCCC 32          | θJ-A   | Thermal resistance - Ceramic<br>Junction-to-Ambient<br>Junction-to-Case | 55<br>15 | °CW  |

Power considerations: The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

$$T_{J} = T_{A} + (P_{D} \cdot \theta_{JA}) \tag{1}$$

TA = Ambient Temperature, °C

θJA = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD = PINT + PI/O

PINT = ICC × VCC, Watts - Chip Internal Power

PI/O = Power Dissipation on Input and Output

Pins - User Determined

For most applications PI/O < PINT and can be neglected.

An approximate reliationship between PD and TJ (if PI/O is neglected) is:

$$P_D = K : (T_J + 273)$$

(2)

Solving equations (1) and (2) for K gives:

$(\theta_{CA})$ . These terms are related by the equation :

$$K = P_D \bullet (T_A + 273) + \theta_{JA} \bullet P_D^2$$

where K is a constant pertaining to the particular part K can be determined from equation (3) by measuring PD (at equilibrium) for a known TA. Using this value of K, the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

The total thermal resistance of a package ( $\theta_{JA}$ ) can be separated into two components,  $\theta_{JC}$  and  $\theta_{CA}$ , representing the barrier to heat flow from the semiconductor junction to the package (case), surface ( $\theta_{JC}$ ) and from the case to the outside ambient

$$\theta_{\mathsf{J}\mathsf{A}} = \theta_{\mathsf{J}\mathsf{C}} + \theta_{\mathsf{C}\mathsf{A}} \tag{4}$$

$\theta_{

m JC}$  is device related and cannot be influenced by the user. However,  $\theta_{

m CA}$  is user dependent and can be minimized by such thermal management techniques as heat sinks, ambient air cooling and thermal convection. Thus, good thermal management on the part of the user can significantly reduce  $\theta_{

m CA}$  so that  $\theta_{

m JA}$  approximately equals  $\theta_{

m JC}$ . Substitution of  $\theta_{

m JC}$  for  $\theta_{

m JA}$  in equation (1) will result in a lower semiconductor junction temperature.

Values for thermal resistance presented in this document, unless estimated, were derived using the procedure described in «Thermal Resistance Measurement Method for EF 68xx Microcomponent Devices», and are provided for design purposes only. Thermal measurements are complex and dependent on procedure and setup. User derived values for thermal resistance may differ

#### 3.5 · Mechanical and environment

The microcircuits shall meet all mechanical environmental requirements of either MIL-STD-883 for class B devices or CECC 90000 devices.

#### 3.6 · Marking

The document where are defined the marking are identified in the related reference documents. Each microcircuit are legible and permanently marked with the following information as minimum:

- Thomson logo

- Manufacturer's part number

- Class B identification

- Date-code of inspection lot

- ESD identifier if available

- Country of manufacturing

#### 4 - QUALITY CONFORMANCE INSPECTION

#### 4.1 - DESC / MIL-STD-883

is in accordance with MIL-M-38510 and method 5005 of MIL-STD-883. Group A and B inspections are performed on each production lot. Group C and D inspection are performed on a periodical basis.

#### 4.2 - CECC

is in accordance with CECC 90000. Group A and B inspection are performed on each production lot as specified in CECC 9011x-0xx. Group C inspection is performed on a periodic basis in accordance with CECC 9011x-0xx.

#### 5 - ELECTRICAL CHARACTERISTICS

#### 5.1 - General requirements

All static and dynamic electrical characteristics specified for inspection purposes and the relevant measurements conditions are given below:

- Table 4: Static electrical characteristics for the electrical variants.

- Table 5 : Dynamic electrical characteristics.

For static characteristics (Table 4), test methods refer to IEC 748-2 method number, where existing.

For dynamic characteristics, test methods refer to clause § 5.4 of this specification (Table 5).

#### 5.2 - Static characteristics

All voltages are referenced to GND.

# Table 4 - DC and operating characteristics

$-55^{\circ}\text{C} \leqslant \text{T}_{\text{C}} \leqslant +125^{\circ}\text{C}$  ;  $\text{V}_{\text{CC}} = 5\,\text{V} \pm 10~\%$

| Symbol | Parameter                       | Test Conditions                                                                | Min   | Max                  | Unit |

|--------|---------------------------------|--------------------------------------------------------------------------------|-------|----------------------|------|

| †LI    | Input load current              | V <sub>IN</sub> = 5.5 V                                                        |       | 10                   | μА   |

| lLO    | Output leakage current          | V <sub>OUT</sub> = 5.5 V                                                       |       | 10                   | μА   |

| ICC1   | V <sub>CC</sub> active current  | CE = OE = V <sub>IL</sub> @f = 8 MHz<br>I <sub>OUT</sub> = 0 mA (Open Outputs) |       | 100                  | mA   |

| ICC2   | V <sub>CC</sub> standby current | CE = ViH                                                                       |       | 1                    | mA   |

| PP1    | Vpp read current                | VPP = VCC                                                                      |       | 0.1                  | mA   |

| VIL    | Input low voltage               |                                                                                | - 0.1 | 0.8                  | ٧    |

| VIH    | Input high voltage              |                                                                                | 2.0   | V <sub>CC</sub> +0.5 | V    |

| VOL    | Output low voltage              | i <sub>OL</sub> = 2.1 mA                                                       |       | 0.45                 | ٧    |

| Voн    | Ouput high voltage              | $I_{OH} = -400 \mu\text{A}$                                                    | 2.4   |                      | ٧    |

| Vpp    | Vpp read voltage                | V <sub>CC</sub> - 0.7 V                                                        |       | Vcc                  | ٧    |

# 5.3 - Dynamic characteristics

#### Table 5

$-55^{\circ}\text{C} \leqslant T_{\text{C}} \leqslant +125^{\circ}\text{C}$  ;  $V_{\text{CC}} = 5\,\text{V} \pm 10~\%$

| O               |                                                                 | Test conditions 27C1001Mx15 27C100 |     | 27C1001Mx15 27C1001Mx20 27C1001Mx25 |     | (20 27C1001Mx25 |     | 11  |      |

|-----------------|-----------------------------------------------------------------|------------------------------------|-----|-------------------------------------|-----|-----------------|-----|-----|------|

| Symbol          | Parameter                                                       | lest conditions                    | Min | Max                                 | Min | Max             | Min | Max | Unit |

| tACC            | Address to output delay                                         | CE = OE = VIL                      |     | 150                                 |     | 200             |     | 250 | ns   |

| tCE             | CE to output delay                                              | OE = VIL                           |     | 150                                 |     | 200             |     | 250 | ns   |

| <sup>t</sup> OE | OE to output delay                                              | CE = VIL                           |     | 65                                  |     | 70              |     | 100 | ns   |

| <sup>†</sup> DF | OE high to output float (see Note)                              | CE = VIL                           | 0   | 50                                  | 0   | 60              | 0   | 60  | ns   |

| tон             | Output hold from address<br>CE or OE whichever occured<br>first | CE = OE = VIL                      | 0   |                                     | 0   |                 | 0   |     | ns   |

Note: This parameter is only sampled and not 100 % tested. Output Float is defined as the point where data is no longer driven-see timing diagram.

#### 5.4 · Test conditions specific to the device

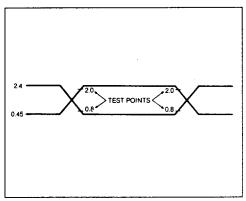

Output load Input rise and fall times Input pulse levels Timing measurement reference level inputs, outputs

1 TTL gate and CL = 100 pF ≤ 20 ns 0.45 V to 2.4 V 0.8 V and 2 V

$3.3 \text{ k}\Omega$ DEVICE UNDER TEST CL INCLUDES JIG CAPACITANCE

FIGURE 4 - AC TESTING INPUT / OUPUT WAVEFORM.

FIGURE 5 - AC TESTING LOAD CIRCUIT.

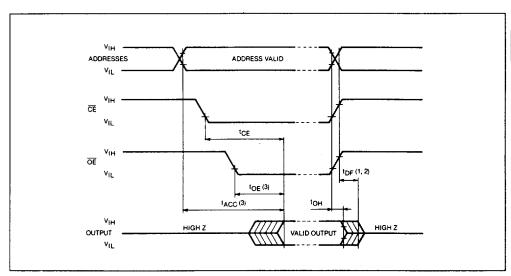

FIGURE 6 - AC WAVEFORMS.

Note 1: This parameter is only sampled and not 100 % tested.

Note 2: tDF is specified form OE or CE whichever occurs first.

Note 3: OE may be delayed up to toe - toe after the falling edge CE without impact on toe.

#### 5.5 - Capacitance (see note)

$T_{amb} = 25$ °C, f = 1 MHz.

| Symbol      | Parameter                                  | Test Conditions | Min | Typ.<br>(Note) | Max | Unit |

|-------------|--------------------------------------------|-----------------|-----|----------------|-----|------|

| CIN         | Input capacitance                          | VIN = 0 V       |     | 4              | 6   | pF   |

| COUT        | Output capacitance                         | VOUT = 0 V      |     | 8              | 12  | pF   |

| Note : Tyni | cal values are for Tamb = 25°C and nominal | supply voltages |     |                |     |      |

Note: This parameter is only sampled and not 100 % tested.

# 5.6 - Burn-in conditions

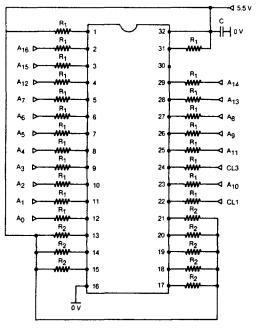

5.6.1 - In Cerdip

Power:

VSS = 0 V  $V_{CC} = 5.5 \text{ V}$

Frequency: 500 kHz Level «0»: 0 V Level «1»:5 V

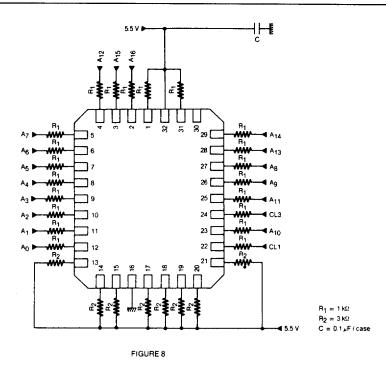

5.6.2 - In LCCC

Power:

VSS = 0 V  $V_{CC} = 5.5 V$

Frequency: 500 kHz Level «0»: 0 V Level «1»: 5.5 V

$R_1 = 1 k\Omega$  $R_2 = 3 \,\mathrm{k}\Omega$

$C = 0.1 \,\mu\text{F}/\text{case}$

FIGURE 7

#### 6 - FUNCTIONAL DESCRIPTION

#### 6.1 - Device operation

The modes of operations of the 27C1001 are listed in the function table (see § 6.5). A single 5 V power supply is required in the read mode. All inputs are TTL levels except for 12 V on A9 for Electronic Signature.

#### Read mode (See § 5.1)

The  $27C\underline{1001}$  has two control functions, both of which must be logically active in order to obtain data at the outputs. Chip Enable  $\overline{(CE)}$  is the power control and should be used for device selection. Output Enable  $\overline{(CE)}$  is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, the address access time (tACC) is equal to the delay from CE to output (tCE). Data is available at the outputs after delay at tQE from the falling edge of OE, assuming that CE has been low and addresses have been stable for at least tACC: tQE.

#### Standby mode

The 27C1001 has a standby mode which reduces the maximum active current from 50 mA to 1 mA. The 27C1001 is placed in the standby mode by applying a TTL high signal to the CE input. When in the standby mode, the outputs are in a high impedance state, independent of the OE input.

# Two line output control

Because EPROMs are usually used in larger memory arrays, the product features a 2 line control function which accommodates the use of multiple memory connection. The two line control function allows:

- a) the lowest possible memory power dissipation,

- b) complete assurance that output bus contention will not occur.

For the most efficient use of these two control lines, CE should be decoded and used as the primary device selecting function, while OE should be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### System considerations

The power switching characteristics of CMOS-E4 EPROMs require careful decoupling of the devices. The supply current, Icc. has three segments that are of interest to the system designer: the standby current level, the active current level, and transient current peaks that are produced by the falling and rising edges of CE. The magnitude of this transient current peaks is dependent on the ouput capacitive and inductive loading of the device. The associated transient voltage peaks can be suppressed by complying with the two line output control and by properly selected decoupling capacitors. It is recommended that a 1 µF ceramic capacitor be used on every device between VCC and GND. This should be a high frequency capacitor of low inherent inductance and should be placed as close to the device as possible. In addition, a 4.7 µF bulk electrolytic capacitors should be used between VCC and GND for every eight devices. The bulk capacitor should be located near where the power supply is connected to the array.

The purpose of the bulk capacitor is to overcome the voltage drop caused by the inductive effects of PCB traces.

#### 6.2 · Programming

Caution: exceeding 14 V on Vpp pin will permanently damage the 27C1001.

When delivered, and after each erasure, all bits of the 27C1001 are in the «1» state. Data is introduced by selectively programming «0s» into the desired bit locations. Although only «0s» will be programmed, both «1s» and «0s» can be present in the data word. The only way to change a «0» to a «1» is by ultraviolet light erasure.

The 27C1001 is in the programming mode when the Vpp input is at 12.75 V and CE and PGM are at TTL-low. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.  $V_{CC}$  is specified to be 6.25 V  $\pm$  0.25 V.

Very fast and reliable programming algorithm = PRESTO II

PRESTO II programming algorithm is available for the 27C1001.

During programming and verify operation a MARGIN MODETM Circuit is automatically activated. It provides, adequate margin on threshold voltage of programmed cells, thus writing margin is independent from VCC in verify mode and over program pulse is not necessary, reducing programming time down to a theoretical value of 12 seconds.

#### Program inhibit

Programming of multiple 27C1001s in parallel with different data is also easily accomplished. Except for CE, all like inputs of the parallel 27C1001 may be common. A TTL low-level pulse applied to a 27C1001's CE input, with Vpp at 12.5 V, will program that 27C1001. A high level CE input inhibits the other 27C1001s from being programmed. VCC is specified to be 6.25 V ± 0.25 V.

#### Program verify

A verify (read) should be performed on the programmed bits to determine that they were correctly programmed. The verify is accomplished with OE and CE at VIL, PGM at VIH and Vpp at 12.5 V and VCC at 6.25 V ± 0.25 V.

#### Electronic signature

The Electronic Signature mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the 25°C ±5°C ambient temperature range that is required when programming the 27C1001. To activate this mode, the programming equipment must force 11.5 V to 12.5 V on address line A9 of the 27C1001. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from VIL to VIH. All other address lines must be held at VIL during Electronic Signature mode.

Byte 0 (A0 = V<sub>II</sub>) represents the manufacturer code and byte 1 (A0 = V<sub>IH</sub>) the device identifier code. For the TMS 27C1101, these two identifier bytes are given here below, and can be read-out on outputs 00 to 07.

#### **ELECTRONIC SIGNATURE MODE**

|   |   | <del></del> | <del></del> |         |           |

|---|---|-------------|-------------|---------|-----------|

| 0 | 0 | 0           | 0           | 0       | 20        |

| 0 | 0 | 1           | 0           | 1       | 05        |

|   | 0 | 0 0         | 0 0 1       | 0 0 1 0 | 0 0 1 0 1 |

#### 6.3 · High speed programming

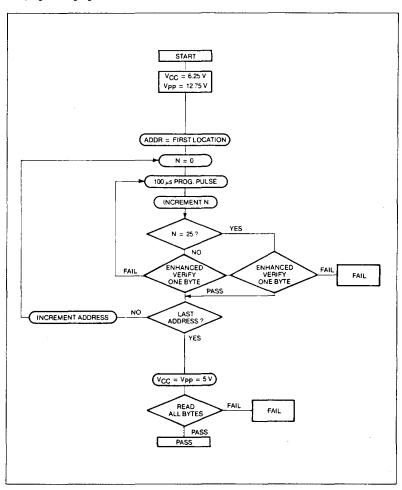

# 6.3.1 - PRESTO II programming algorithm flow chart

FIGURE 9

# **PROGRAMMING OPERATION** (T<sub>C</sub> = 25°C $\pm$ 5°C, V<sub>CC</sub>(1) = 6.25 V $\pm$ 0.25 V, V<sub>PP</sub>(1) = 12.75 V $\pm$ 0.25 V)

#### DC and operating characteristic

| Symbol   | Parameter                         | Test Conditions (see Note 1) | Min   | Max                   | Unit |

|----------|-----------------------------------|------------------------------|-------|-----------------------|------|

| ĮLI.     | Input current (all inputs)        | VIN = VIL or VIH             |       | 10                    | μΑ   |

| VIL      | Input low level (all inputs)      |                              | - 0.1 | 0.8                   | ٧    |

| $v_{IH}$ | Input high level                  |                              | 2.0   | V <sub>CC</sub> + 0.5 | ٧    |

| VOL      | Output low voltage during verify  | !OL = 2.1 mA                 |       | 0.45                  | ٧    |

| Vон      | Output high voltage during verify | $IOH = -400 \mu A$           | 2.4   |                       | ٧    |

| ICC2     | VCC supply current                |                              |       | 50                    | mA   |

| IPP2     | Vpp supply current (program)      | CE = VIL                     |       | 50                    | mA   |

| QIV      | A9 electronic signature voltage   |                              | 11.5  | 12.5                  | ٧    |

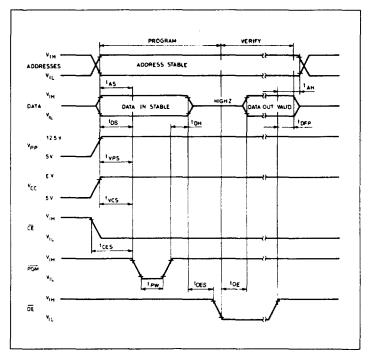

#### AC characteristics

| Symbol               | Parameter                        | Test Conditions (see Note 1) | Min | Max | Unit |

|----------------------|----------------------------------|------------------------------|-----|-----|------|

| tAS                  | Address setup time               |                              | 2   |     | μS   |

| tOES                 | OE setup time                    |                              | 2   |     | μS   |

| tDS                  | Data setup time                  |                              | 2   |     | μS   |

| tAH                  | Address hold time                |                              | 0   |     | μ\$  |

| tDH                  | Data hold time                   |                              | 2   |     | μS   |

| tDFP<br>(see Note 2) | Output enable output float delay |                              | 0   | 130 | ns   |

| tvps                 | Vpp setup time                   |                              | 2   |     | μS   |

| tvcs                 | V <sub>CC</sub> setup time       |                              | 2   |     | μ5   |

| †CES                 | CE setup time                    |                              | 2   |     | μS   |

| tpw                  | PGM initial program pulse width  |                              | 95  | 105 | μ5   |

| †OE                  | Data valid from OE               |                              |     | 100 | ns   |

Note 1: VCC must be applied simultaneously or before Vpp and removed simultaneously or after Vpp.

Note 2: This parameter is only sampled and not 100 % tested.

Output Float is defined as the point where data is no longer driven (see timing diagram).

# 6.3.2 - Wave forms

- Note 1 : The input timing reference level is 0.8 V for a  $V_{IL}$  and 2 V for a  $V_{IH}$

- Note 2: tOE and tOEP are characteristics of the device but must be accommodated by the programmer.

- Note 3: When programming the 27C1001, a 0.1 µF capacitor is required across Vpp and GND to suppress spurious voltage transients which can damage the device

FIGURE 10 - PROGRAMMING WAVEFORMS

#### 6.4 - Erasure operation

The erasure characteristic of the 27C1001 is such that erasure begins when the cells are exposed to light with wavelengths shorter than approximately 4000 Agnstrom A. It should be noted that sunlight and some type of fluorescent lamps have wavelengths in the 3000-4000 A range. Data shows that constant exposure to room level fluorescent lighting could erase a typical 27C1001 in about 3 years, while it would take approximately 1 week to cause erasure when expose to direct sunlight. If the 27C1001 is to be exposed to these types of lighting conditions for extended periods of time, it is suggested that opaque labels be put over the 27C1001 window to prevent unintentional erasure. The recommended erasure procedure for the 27C1001 is exposure to short wave ultraviolet light which has wavelength 2537 A. The integrated dose (i.e. UV intensity x exposure time) for erasure should be a minimum of 15 W-sec/cm². The erasure time with this dosage is approximately 15 to 20 minutes using an ultraviolet lamp with 12000 µW/cm² power rating. The 27C1001 should be placed within 2.5 cm (1 inch) of the lamp tubes during the erasure. Some lamps have a filter on their tubes which should be removed before erasure.

# 6.5 - Function table

#### **OPERATING MODES**

| OE<br>L | <b>A9</b> | PGM  | Vpp                | OUTPUTS |

|---------|-----------|------|--------------------|---------|

| L       | Х         |      |                    |         |

|         | 1         | X    | Vcc                | DOUT    |

| Н       | ×         | ×    | Vcc                | High Z  |

| х       | х         | x    | Vcc                | High Z  |

| х       | х         | L    | Vpp                | DIN     |

| L       | х         | н    | VPP                | DOUT    |

| х       | х         | ×    | Vpp                | High Z  |

| L       | νн        | Н    | Vcc                | CODE    |

|         | L         | L VH | L V <sub>H</sub> H |         |

#### 7 · PREPARATION FOR DELIVERY

#### 7.1 · Packaging

Microcircuits are prepared for delivery in accordance with MIL-M-38510 or CECC 90000.

#### 7.2 · Certificate of compliance

TMS offers a certificate of compliance with each shipment of parts, affirming the products are in compliance either with MIL-STD-883 or CECC 90000 and guarantying the parameters not tested at extreme temperature for the entire temperature range.

# 8 - HANDLING

MOS devices must be handled with certain precautions to avoid damage due to accumulation of static charge. Input protection devices have been designed in the chip to minimize the effect of this static buildup. However, the following handling practices are recommended:

- a) Device should be handled on benches with conductive and grounded surface.

- b) Ground test equipment, tools and operator.

- c) Do not handle devices by the leads.

- d) Store devices in conductive foam or carriers.

- e) Avoid use of plastic, rubber, or silk in MOS areas.

- f) Maintain relative humidity above 50 percent, if practical.

# 9 - PACKAGE MECHANICAL DATA

# 9.1 · DIL CERDIP with window package 32 pins

FIGURE 11 - 32-PIN WINDOW CERAMIC DUAL IN LINE FRIT-SEAL (F)

#### 9.2 · 32 pins leadless ceramic chip carrier

# 10 · ORDERING INFORMATION

# 10.1 · HI-REL product

| TMS part-number (1) | Norms                   | Package   | Temperature range<br>T <sub>C</sub> (°C) | TACC<br>(µs) | Drawing number |

|---------------------|-------------------------|-----------|------------------------------------------|--------------|----------------|

| 27C1001MQG/B15      | NFC 96883 - Class G     | Cerdip 32 | -55 / +125                               | 150          | Internal       |

| 27C1001MQG/B20      | NFC 96883 - Class G     | Cerdip 32 | - 55 / + 125                             | 200          | Internal       |

| 27C1001MQB/C15      | MIL-STD-883 C - Class B | Cerdip 32 | -55 / +125                               | 150          | Non available  |

| 27C1001MQB/C20      | MIL-STD-883 C - Class B | Cerdip 32 | -55 / + 125                              | 200          | Non available  |

| 27C1001MEQ1B/C15    | MIL-STD-883 C - Class B | LCCC 32   | -55/+125                                 | 150          | Non available  |

| 27C1001MEQ1B/C20    | MIL-STD-883 C - Class B | LCCC 32   | -55/+125                                 | 200          | Non available  |

| 27C1001MQ7B/Y15     | CECC 90000              | Cerdip 32 | -55 / +125                               | 150          | TBD            |

| 27C1001MQ7B/Y20     | CECC 90000              | Cerdip 32 | - 55 / + 125                             | 200          | TBD            |

| 27C1001MEQ7B/Y15    | CECC 90000              | LCCC 32   | -55 / + 125                              | 150          | TBD            |

| 27C1001MEQ7B/Y20    | CECC 90000              | LCCC 32   | -55 / + 125                              | 200          | TBD            |

| (1) THOMSON COMPO   | SANTS MILITAIRES ET SPA | ATIAUX.   |                                          |              |                |

# 10.2 · Standard product

| TMS part-number (1) | Norms        | Package   | Temperature range<br>T <sub>C</sub> (°C) | TACC<br>(μs) | Drawing numbe |

|---------------------|--------------|-----------|------------------------------------------|--------------|---------------|

| 27C1001MQ15         | TMS Standard | Cerdip 32 | -55/+125                                 | 150          | Internal      |

| 27C1001MQ20         | TMS Standard | Cerdip 32 | -55/+125                                 | 200          | Internal      |

| 27C1001MQ25         | TMS Standard | Cerdip 32 | - 55 / + 125                             | 250          | Internal      |

| 27C1001MEQ15        | TMS Standard | LCCC 32   | -55 / + 125                              | 150          | Internal      |

| 27C1001MEQ20        | TMS Standard | LCCC 32   | -55/+125                                 | 200          | Internal      |

| 27C1001MEQ25        | TMS Standard | LCCC 32   | -55 / + 125                              | 250          | Internal      |