T-79-40

-IN 2

10 OUT 2

٧+

NC

**DUAL HIGH-SPEED OPERATIONAL** TRANSCONDUCTANCE AMPLIFIER WITH LINEARIZING DIODES

# Incorporated

#### **FEATURES**

- Dual Version of VA703

- · Low Offset Voltage: 0.5mV

- Linearizing Diodes

- Wide Open-Loop Bandwidth: 75MHz

- · Large Output Swing: ±4V with 5V supplies

- Large Output Current: ±5mA

- Adjustable/Gatable Current-Controlled Gain

- Available in Commercial Version

#### APPLICATIONS

- Multiplexers

- Sample/Hold Circuits

- Current-Controlled Filters

- Multiplier

#### DESCRIPTION

The VA2703 is a dual high-speed operational transconductance amplifier with the added features of current-controlled gain and input linearizing diodes. The complementary bipolar process employed with this device combines excellent DC and AC characteristics. Offset voltages are typically 0.5mV while the wideband transistor characteristics provide stable, well-behaved amplifier configurations to 50MHz. The linearizing diodes are used to minimize distortion for high input level applications. The VA2703 is extremely versatile for use in applications such as current-controlled amplifiers, multipliers, sample/hold circuits and VCOs.

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltages                                  | ±6V             |

|--------------------------------------------------|-----------------|

| Differential Input Voltage                       | ±4.5V           |

| Common Mode Input Voltage                        | ±Vs             |

| Amp Blas Current                                 | 10mA            |

| Diode Blas Current                               | 10mA            |

| Power Dissipation (T <sub>A</sub> =70°C, Note 1) |                 |

| Output Short Circuit Current Duration            | Indefinite      |

| Operating Temperature Range: VA2703J             | 0°C to 70°C     |

| Storage Temperature Range                        | -65°C to ±150°C |

| Storage remperature (Coldering to 60 Coo.)       | 2000            |

| Lead Temperature (Soldering to 60 Sec.)          |                 |

Note 1: Power derating above TA = 70°C to be based on a maximum junction temperature of 150°C and the thermal resistance factors of  $\theta_{JC}$  = 75°C/W and  $\theta_{JA}$  = 145°C/W.

#### PACKAGE TYPES AVAILABLE

- 14-Pin Plastic DIP

- 14-Pin SOIC

#### 14-Lead Dual In-Line/SOIC Package Amp Blas 2 Amp Bias 1 Diode Bias 1 2 Diode Bias 2 +IN 1 3 12 +IN 2 -IN 1

CONNECTION DIAGRAM

OUT 1

NC

Top View

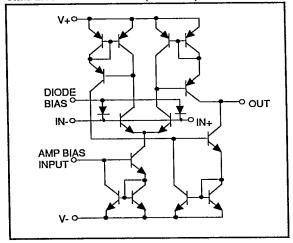

#### SIMPLIFIED SCHEMATIC (Each OTA)

#### **ELECTRICAL CHARACTERISTICS** ( $V_S = \pm 5V$ , $T_A = 25$ °C, $I_{ABC} = 500\mu A$ , unless otherwise specified) (Note 1)

|                                  |                  |                                                              |                                                                                   | MIN TYP MAX |          |            | UNITS        |

|----------------------------------|------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------|----------|------------|--------------|

| PARAMETER                        | SYMBOL           |                                                              |                                                                                   | MIIN        |          |            | UNITS        |

| Input Offset Voltage             | Vos              | IABC =5µA to 5mA                                             |                                                                                   |             | - 1      | 5          | mV<br>mV     |

|                                  |                  | T <sub>A</sub> =0° to 70°C<br>T <sub>A</sub> =-55° to +125°C |                                                                                   |             |          | 8          |              |

| Offset Voltage Change            | 41/00            | IABC =5µA to 5mA                                             |                                                                                   |             | 3        | 5          |              |

| Input Blas Current               | ΔVOS             | WBC ≡3trx to 3trx                                            |                                                                                   |             |          | 1114       |              |

|                                  |                  | T 004-7000                                                   |                                                                                   |             | 2.5      | 5<br>8     | μΑ           |

|                                  |                  | T <sub>A</sub> =0° to 70°C                                   |                                                                                   |             |          |            |              |

|                                  |                  | T <sub>A</sub> =-55° to +125°C                               |                                                                                   |             |          |            |              |

| Input Offset Current             | los              | 14 0 VOII                                                    | 10)/                                                                              |             | 0.12     | 0.6        | <u>μΑ</u>    |

| Differential Input Current       | DIFF             | IABC =0, VDII                                                | -F =±3V                                                                           |             | 10<br>+4 | 200        | n <b>A</b>   |

| Common Mode Range                | VCM              |                                                              |                                                                                   | ±2.75       | -3.3     |            | V            |

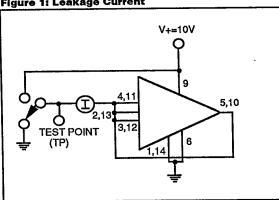

| Leakage Current                  | ILEAK            | I <sub>ABC</sub> =0, V <sub>TP</sub>                         | =0V<br>=10V (Figure 1)                                                            |             | 5<br>2   | 100<br>100 | nA<br>nA     |

| Differential Input Capacitance   | CIND             |                                                              |                                                                                   |             | 4        |            | pΕ           |

| Differential Input Resistance    | R <sub>IND</sub> | (Note 5)                                                     |                                                                                   | 10          | 26       |            | ΚΩ           |

| Common Mode Input<br>Capacitance | CINC             |                                                              |                                                                                   |             | 3        |            | рF           |

| Common Mode Input<br>Resistance  | RINC             | V <sub>CM</sub> =±2.75V                                      |                                                                                   |             | 1        |            | МΩ           |

| Forward<br>Transconductance      | g <sub>m</sub>   | l <sub>o</sub> =±120μΑ                                       | T <sub>A</sub> = Full                                                             | 7700        | 9900     | 15000      | μmho         |

| (Large Signai)                   | ļ                |                                                              | IA = Full                                                                         | 4000        |          |            | <del> </del> |

| Common Mode<br>Rejection Ratio   | CMRR             | ΔV <sub>CM</sub> = ±2.75                                     | <b>V</b>                                                                          | 80          | 110      |            | dB           |

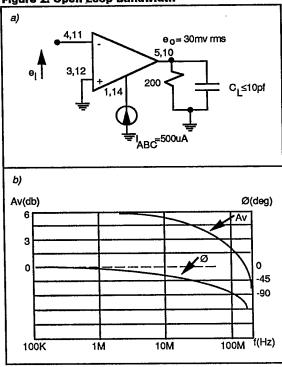

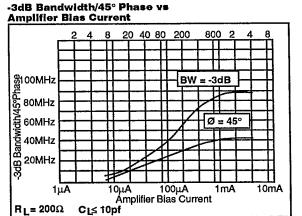

| Open Loop Bandwidth              | BW               | (Figure 2 a,b) f - 3dB<br>Ø(45°)<br>IABC =5µA to 5mA, RL=∞   |                                                                                   |             | 75       |            | MHz          |

|                                  |                  |                                                              |                                                                                   |             | 35       |            | MHz          |

| Output Voltage Swing             | VOUT             |                                                              | 5mA, RL=∞                                                                         | ±3.5        | ±4.25    |            | V            |

| Output Current                   | lout             | R <sub>L</sub> =0                                            |                                                                                   | 350         | 500      | 750        | ·            |

|                                  |                  | IABC =5µA, RL=0                                              |                                                                                   | 3           | 5        | 7          | μΑ           |

|                                  |                  | T <sub>A</sub> = Full                                        |                                                                                   | 300         |          |            |              |

| Output Capacitance               | COUT             |                                                              |                                                                                   |             | 3        |            | pF           |

| Output Resistance                | ROUT             | V <sub>0</sub> =±3.5V                                        |                                                                                   |             | 0.5      |            | MΩ           |

| Slew Rate                        | SR               | Unity Gain (Figure 3, Note 2)                                |                                                                                   |             | 50       |            | V/μs         |

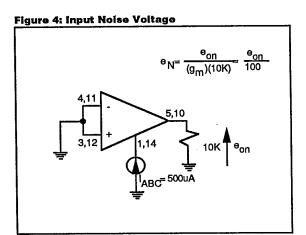

| Total Input Noise Voltage        | θN               | BW = 10Hz to 100kHz (Figure 4)                               |                                                                                   |             | 3        |            | μVrms        |

| Positive Supply Current          | 18+              | Both OTAs (Note 3)                                           |                                                                                   | 1.6         | 2        | 3          | mA           |

| Power Supply<br>Rejection Ratio  | PSRR             | ΔVps =±0.5V                                                  |                                                                                   | 70          | 86       |            | dB           |

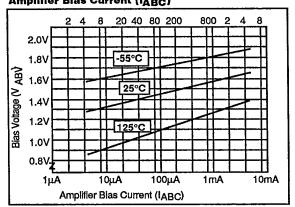

| Amplifier Blas Voltage           | VABV             | (1)                                                          | in 1(14) wrt Pin 6<br>lote 4)                                                     |             | 1.5      |            | V            |

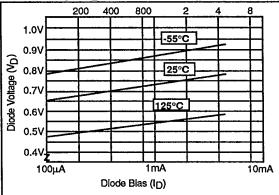

| Diode Voltage                    | V <sub>D</sub>   | Pin 13 wrt Pir                                               | 3, 4 (Com), 1 <sub>2</sub> = 2mA<br>n 11,12 (Com)1 <sub>13</sub> =2mA<br>(Note 4) |             | 0.75     |            | V            |

1.  $I_{ABC} = (Amplifier Bias Current)$  The current supplied to the amplifier bias terminal to establish its operating point. 2. Slew Rate =  $f(I_{ABC})$  per  $SR = \frac{\Delta V_{O}}{\Delta t} = \frac{I_{O}}{C_{L}} = \frac{I_{ABC}}{C_{L}}$  where  $Q_{L} = Total Load Capacitance$ Notes:

64

<sup>3.</sup> Negative Supply Current (IS.) = I S++2\*IABC 4. Dual In-line pins used for reference 5. Not tested, guaranteed by design.

#### **TEST CIRCUITS**

Figure 1: Leakage Current

T-79-40

Figure 3: Slew Rate 10K e<sub>o</sub> = ±2.5V 100 C<sub>L</sub>≤10pF ABC= 500uA

Figure 2: Open Loop Bandwidth

T-79-40

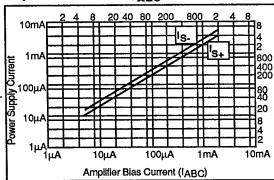

TYPICAL PERFORMANCE CHARACTERISTICS ( $V_S = \pm 5V$ ,  $T_A = 25$ ° C unless otherwise stated)

Amplifier Blas Voltage (VABV) vs Amplifier Blas Current (IABC)

Diode Voltage (Vp ) vs Diode Bias (Ip)

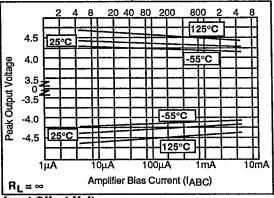

Peak Output Voltage vs Amplifier Blas Current (IABC)

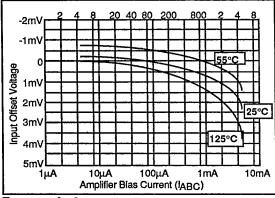

Input Offset Voltage vs Amplifier Bias Current (IABC)

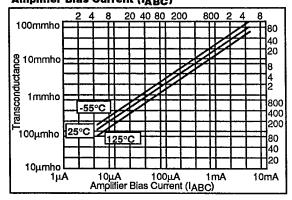

Transconductance vs Amplifier Bias Current (I<sub>ABC</sub>)

T-79-40

TYPICAL PERFORMANCE CHARACTERISTICS (V<sub>S</sub>=±5V, T<sub>A</sub> = 25° C unless otherwise stated)

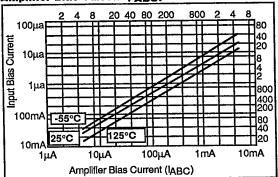

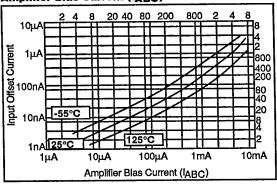

input Blas Current vs Amplifier Blas Current (IABC)

Input Offset Current vs Amplifier Bias Current (IABC)

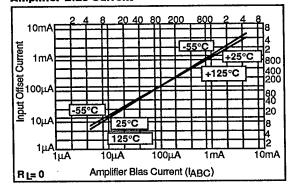

Peak Output Current vs Amplifier Blas Current

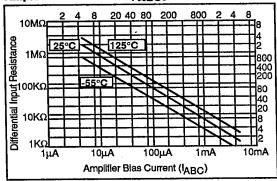

Differential Input Resistance vs Amplifier Bias Current (IABC)

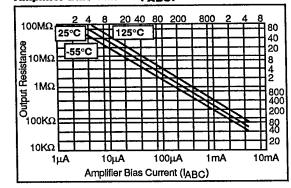

Output Resistance vs Amplifier Blas Current (IABC)

Power Supply Current vs Amplifier Bias Current (IABC) (Each OTA)

## T-79-40

#### **APPLICATION INFORMATION**

#### **Design Equations**

The operational transconductance amplifier (OTA) produces an output current proportional to the differential voltage (V<sub>D</sub>) applied at the input according to:

$$I_0 = g_m(V_{in+} - V_{in-}) = g_m V_D$$

$$I_0 = \frac{I_{ABC}}{2V_T} \cdot V_D$$

where  $g_m = \frac{I_{ABC}}{2V_T}$

Thus, the OTA becomes a very versatile building block. At a constant IABC, all of the standard operational amplifier circuits can be configured while modulation of IABC provides for such functions as current controlled active filters, sample/hold amplifiers and multipliers.

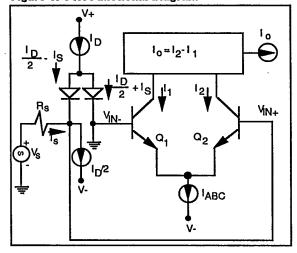

The defining equation I or g<sub>M</sub>V<sub>D</sub> becomes increasingly non-linear as the input differential voltage (V<sub>D</sub>) becomes greater than a few millivolts. In many applications the linearizing diodes can be used to minimize this non-linearity and resulting signal distortion. To understand the use of the linearizing diodes, some basic equations need to be developed. Figure 5 represents the basic functional parts of the OTA. For convenience, the diodes are shown biased with ideal current sources while in practice resistor biasing can be used with very good results.

Figure 5: OTA Functional Diagram

Without the linearizing diodes ( $I_D=0$ ), the input voltage  $V_s$  is seen at  $V_{IN+}$  based upon voltage divider action between the source impedance  $R_s$  and the differential input resistance of  $Q_1$  and  $Q_2$ .

where

$$R_{IND}$$

=  $\beta(r_{e1}+r_{e2})$

and  $r_{e}$  =  $\frac{2}{I_{ABC}} \cdot V_{T}$ ,  $\beta$  = current gain since  $V_{T}$  = 26mV at 25°C

$R_{IND}$  =  $\frac{104\beta}{I_{ABC}}$  (mA)

ex: at I ABC = 1mA

$\beta$  = 100

$R_{IND}$  = 10 • 4K

The current distribution in Q1 and Q2 is governed by:

$$V_{D} = V_{1N+} - V_{1N-} = V_{T} \ln \frac{I_{2}}{I_{1}}$$

For small differential input voltages  $| \mathbf{h} \approx |_2$ , and  $| \mathbf{h} \approx |_2$  can be represented in the Taylor series expansion as:

$$\ln \frac{I_2}{I_1} = \frac{I_2 - I_1}{I_1} = \frac{I_0}{I_1}$$

and since  $I_1 \approx I_2 \approx \frac{I_{ABC}}{2}$

$$V_D = 2V_T \cdot \frac{I_0}{I_{ABC}}$$

$$I_0 = \frac{I_{ABC}}{2} \cdot \frac{V_D}{V_T}$$

It is the I<sub>1</sub> $\approx$ I<sub>2</sub> assumption that limits the accuracy of the equation to small values of input voltage (V<sub>D</sub>). Even with an input voltage as small as V<sub>D</sub>= V<sub>T</sub>= 26mV, the I<sub>2</sub>/I<sub>1</sub> ratio = 2.7.

68

With a blas (ID) applied to the linearizing diodes a low Impedance shunt based upon the dynamic resistance of the diodes is placed across differential pair Q  $_{\mbox{\scriptsize 1}}$  and Q  $_{\mbox{\scriptsize 2}}.$ This shunting action is what linearizes the output current as a function of input voltage (current ) VS(Is). Looking at the defining equations:

I<sub>1</sub> and I<sub>2</sub>can be expressed as:

$$I_2 = \frac{I_{ABC} + I_0}{2}, \quad I_1 = \frac{I_{ABC} - I_0}{2}$$

$I_2 = \frac{|ABC+I_0|}{2}, \quad I_1 = \frac{|ABC-I_0|}{2}$  and since the diodes and Q  $_1$ ,Q  $_2$  are of the same geometry and see the same temperatures, the diode and transistor currents can be equated according to

$$V_T \ln \frac{ID'^2 + Is}{ID'^2 - Is} = V_T \ln \frac{I_{ABC} + I_0}{I_{ABC}^{-1}}$$

solving for lo yields:

$$I_0 = \frac{2 \, I_{\text{SIABC}}}{I_{\text{D}}}$$

An interesting result is that no assumptions have been made to affect linearity other than the diodes be blased (I ) and modulated (IS) with current sources and the diodes be kept in conduction | | c | s/2. The output current is also Independent of temperature.

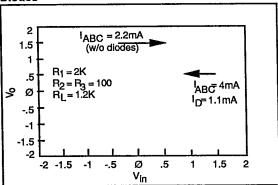

Figures 6 a, b and c illustrate the effects of using the linearizing diodes in an open loop amplifier configuration with a large signal voltage gain of approximately 1V/V. The transfer curve compares circuit operation with and without the diodes. Corresponding total harmonic distortion (THD) for a 3Vp-p 1KHz output sine wave is 5% for the non-diode case and 0.6% with linearizing diodes. For closed loop configurations, the linearizing diodes generally are not used since the degenerative feedback keeps the input differential voltage at small values.

Figure 6a: Open Loop Amplifier Without Diodes

Figure 6b: Open Loop Amplifier With Diodes

Figure 6c: Linearity Profile With and Without Diodes

It is instructive to look more closely at the defining I S equation when the linearizing diodes are used to see how well the current source assumption and attendant linearity are being met in practice.

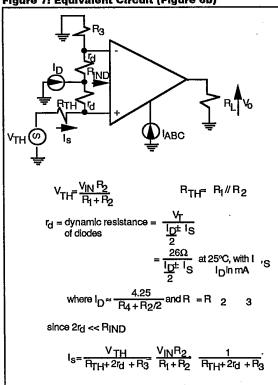

Referring to Figure 6b, the equivalent circuit can be reduced to Figure 7 below.

Figure 7: Equivalent Circuit (Figure 6b)

As the equations in Figure 7 indicate, to maximize linearity and minimize temperature effects,  $R_D$  should be kept small wrt  $R_{TH}$ +  $R_3$  and  $R_D$  and

In practice, I<sub>D</sub> values from 1mA to 5mA are the best choice for most applications.

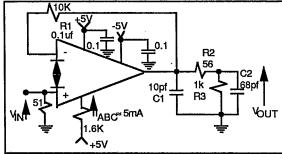

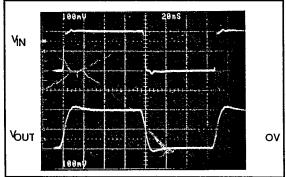

#### 60MHz Unity Gain Follower

Figure 8a is a unity gain follower configuration which emphasizes the basic speed capability of the VA2703. As illustrated in Figures 8b and 8c, small signal rise time = fall time = 5ns (measured small signal bandwidth  $\approx$  60MHz) and large signal ( $\pm 2.5 \text{V}$ ) slew rate plus small signal settling is less than 200ns. R2 is used for phase recovery by introducing a zero at approximately 40MHz while C1 ensures high frequency rolloff at frequencies above 100MHz.

## T-79-40

Figure 8a: 60MHz Unity Gain Follower

Figure 8b: Small Signal Step Response

Figure 8c: Large Signal Step Response

70

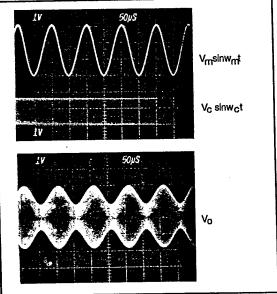

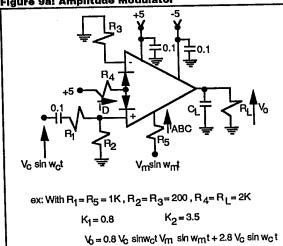

#### **Amplitude Modulator**

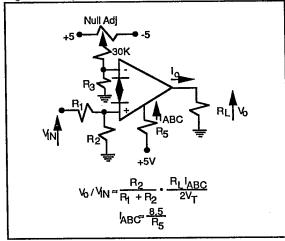

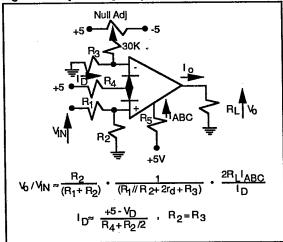

Figure 9a shows the transconductance amplifier operating as a 2 quadrant linearized multiplier to produce an amplitude modulated output waveform with defining equations:

Vo=K1(Vc sin wct Ym sin wm t+ 1/2 Vc sin w t)

where

$$K_1 = \frac{R_2}{R_1 + R_2}$$

,  $\frac{1}{R_1 /\!\!/ R_2 + 2rd + R_3}$ ,  $\frac{2R_L}{R_5}$ ,  $\frac{1}{I_D}$ ,

I D=

$$\frac{4.25}{R_4 + R_2/2}$$

and K2= 5-VABV=3.5,  $r_d \approx \frac{52}{I_{D(mA)}} \Omega$

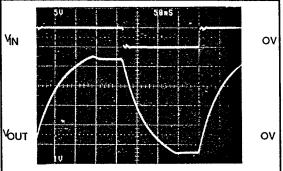

Figure 9b shows the input and output waveforms at a carrier frequency of fc = 1MHz and modulation frequency fn = 10kHz. Since the basic OTA has a bandwidth in excess of 50MHz the circuit bandwidth is determined by the load time constant =  $R_L(C_L+C_0)$ . For the above example at  $R_L=2K$  and  $C_L+C_0\approx$  9pf, the bandwidth = 4MHz. Attendant power bandwidth, (signal swing before distortion), being a function of C and I ABS actually larger than the small signal bandwidth. Power bandwidth = 5MHz at Vo = 6Vp-p.

Figure 9a: Amplitude Modulator

### T-79-40

#### **Layout Considerations**

As with any high-speed circuitry, certain layout considerations are necessary if stable operation is to be ensured and performance is to be optimized. All connections to the OTA should be kept as short as possible including the power supplies which should be bypassed with 0.1µF capacitors, or better yet, a combination of 1µF - 10µF electrolytics/tantalums in parallel with a 0.01µF ceramic. It is suggested that a ground plane be considered as the best method of maximizing performance because it minimizes stray inductance and unwanted coupling in the ground signal paths. To minimize capacitive effects, resistor values should be kept as small as possible consistent with the application.

Figure 9b: Amplitude Modulator Waveforms