## MPV3J & MPV5J Series 9x14 mm, 5.0 or 3.3 Volt, PECL/LVDS, VCXO

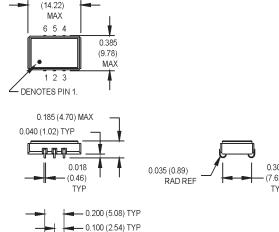

0.565

SUGGESTED SOLDER PAD LAYOUT

$\mathbf{H} \mathbf{H} \mathbf{H}$

- 0.200 (5.08) -- 0.050 (1.27) 0.118

(3.00)

- 0.100 (2.54)

0.346

(8.80)

- Integrated phase jitter of less than 1 ps from 12 kHz to 20 MHz

- Ideal for low noise PLL applications

All dimensions in inches (mm).

## **Pin Connections**

| PIN | FUNCTION                                  |  |  |  |  |

|-----|-------------------------------------------|--|--|--|--|

| 1   | Control Voltage                           |  |  |  |  |

| 2   | Output Enable or N/C Ground/Case Output Q |  |  |  |  |

| 3   |                                           |  |  |  |  |

| 4   |                                           |  |  |  |  |

| 5   | 5 Output Q or N/C                         |  |  |  |  |

| 6   | +Vcc                                      |  |  |  |  |

| M-tron reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or a | application. No rights under any patent accompany the sale of such product. |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

## MPV3J & MPV5J Series 9x14 mm, 5.0 or 3.3 Volt, PECL/LVDS, VCXO

|                           |                                            |                                                                       |                                                               |        | l                        |                  |                             |  |

|---------------------------|--------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|--------|--------------------------|------------------|-----------------------------|--|

|                           | PARAMETER                                  | Symbol                                                                | Min.                                                          | Тур.   | Max.                     | Units            | Condition                   |  |

|                           | Frequency Range                            | F                                                                     | 30 800 MHz (Consult factory for exact frequency availability) |        |                          |                  |                             |  |

|                           | Frequency Stability                        | ∆F/F                                                                  | (See Ordering Information)                                    |        |                          |                  | See Note 1                  |  |

|                           | Operating Temperature                      | TA                                                                    | (See Ordering Information)                                    |        |                          |                  |                             |  |

|                           | Storage Temperature                        | Ts                                                                    | -55 +125 °C                                                   |        |                          |                  |                             |  |

|                           | Input Voltage                              | Vcc                                                                   | 3.135                                                         | 3.3    | 3.465                    | V                | MPV3J                       |  |

|                           | input voitage                              | VCC                                                                   | 4.75                                                          | 5.0    | 5.25                     | V                | MPV5J                       |  |

|                           | Input Current                              | ldd                                                                   | 4.75                                                          | 60     | 70                       | mA               | IVIE V 33                   |  |

|                           | Symmetry (Duty Cycle)                      | laa                                                                   | 40                                                            |        | 60                       | %                | @ Vcc -1.3 VDC              |  |

|                           | (Per Symmetry Code)                        |                                                                       | 45                                                            |        | 55                       | %                | @ \$00 -1.0 \$DO            |  |

|                           | Load                                       |                                                                       | -10                                                           |        | -                        | ,,,              | See Note 2                  |  |

|                           | Rise/Fall Time                             | Tr/Tf                                                                 |                                                               | .35    | .55                      | ns               | @ 20/80%                    |  |

|                           | Logic "1" Level                            | Voh                                                                   | Vcc -1.02                                                     | .00    | .00                      | V                | PECL                        |  |

|                           | Logic "0" Level                            | Vol                                                                   | 100 1.02                                                      |        | Vcc -1.63                | V                | PECL                        |  |

| S I                       | Phase Jitter                               | φ <b>J</b>                                                            |                                                               |        | 700 1.00                 |                  | Integrated 12 kHz - 20 MHz  |  |

| atic                      | @ 77.76 MHz                                | Ψυ                                                                    |                                                               | 0.6    | 0.9                      | ps RMS           | integrated 12 km2 - 20 Minz |  |

| ific                      | @ 155.52 MHz                               |                                                                       |                                                               | 0.3    | 0.55                     | ps RMS           |                             |  |

| bec                       | @ 622.08 MHz                               |                                                                       |                                                               | 0.3    | 0.55                     | ps RMS           |                             |  |

| S                         | <u> </u>                                   | 100 Hz                                                                | 1 kHz                                                         | 10 kHz | 100 kHz                  | 1 MHz            | Offset from carrier         |  |

| Electrical Specifications | Phase Noise (Typical)                      | -80                                                                   | -110                                                          | -133   | -144                     | -147             | dBc/Hz                      |  |

|                           | @ 77.76 MHz                                | -80                                                                   | -110<br>-110                                                  | -133   | -144                     | -147<br>-147     | dBc/Hz                      |  |

|                           | @ 155.52 MHz                               | -80<br>-70                                                            | -110                                                          | -125   | -1 <del>44</del><br>-135 | -147             | dBc/Hz                      |  |

|                           | @ 622.08 MHz                               | -70                                                                   |                                                               | -125   | -135                     |                  | abc/nz                      |  |

|                           | Unwanted Mode Suppression                  | Vo                                                                    | <b>-50</b><br>250                                             | 240    | 450                      | d <b>B</b><br>mV | L)/DC                       |  |

|                           | Differential Voltage                       |                                                                       | 10                                                            | 340    | 450                      |                  | LVDS                        |  |

|                           | Modulation Bandwidth                       | fm                                                                    |                                                               |        |                          | kHz              | -3 dB bandwidth             |  |

|                           | Input Impedance                            | Zin                                                                   | 50                                                            |        |                          | ΚΩ               |                             |  |

|                           | Control Voltage                            | Vcc                                                                   | 0                                                             | 1.65   | 3.3                      | V                | Pin 1 voltage (MPV3J)       |  |

|                           |                                            |                                                                       | 0                                                             |        | 5.0                      | V                | Pin 1 voltage (MPV5J)       |  |

|                           | Center Frequency                           | Vc0                                                                   |                                                               | 1.65   |                          | V                | MPV3J                       |  |

|                           |                                            |                                                                       |                                                               | 2.5    |                          | V                | MPV5J                       |  |

|                           | Linearity                                  |                                                                       | 5 10 %                                                        |        |                          |                  |                             |  |

|                           | Pullability                                | APR                                                                   | (See Ordering Information)                                    |        |                          |                  | See Note 3                  |  |

|                           | Enable/Disable Logic                       |                                                                       | CMOS high, Vcc or N/C - enables output                        |        |                          |                  | Output Option B             |  |

|                           |                                            |                                                                       | CMOS low or GND - disables output                             |        |                          |                  |                             |  |

|                           |                                            |                                                                       | PECL low, GND, or N/C - enables output                        |        |                          |                  | Output Option S             |  |

| $\vdash$                  |                                            |                                                                       | PECL high - disables output                                   |        |                          |                  |                             |  |

| Ital                      | Mechanical Shock                           | Per MIL-STD-202, Method 213, Condition C                              |                                                               |        |                          |                  |                             |  |

| Environmental             | Vibration                                  | Per MIL-STD-202, Method 201 & 204                                     |                                                               |        |                          |                  |                             |  |

|                           | Reflow Solder Conditions                   | See "Figure 2" on page 147                                            |                                                               |        |                          |                  |                             |  |

|                           | Hermeticity                                | Per MIL-STD-202, Method 112 (1 x 10 <sup>-8</sup> atm.cc/s of helium) |                                                               |        |                          |                  |                             |  |

| ũ                         | Solderability Per MIL-STD-883, Method 2003 |                                                                       |                                                               |        |                          |                  |                             |  |

<sup>1.</sup> Stability given for deviation over temperature.

M-tron reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application. No rights under any patent accompany the sale of such product.

<sup>2.</sup> PECL load - see load circuit diagram #5 on page 149.

3. APR specification inclusive of initial tolerance, deviation over temperature, shock, vibration, supply voltage, and aging.