TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TMPN3120A20M, TMPN3120A20U

Neuron <sup>®</sup> Chip For Distributed Intelligent Control Networks (L<sub>ON</sub>W<sub>ORKS</sub><sup>®</sup>)

The Neuron Chip (TMPN3120A20M and TMPN3120A20U) provides double the performance of previous Neuron Chips. It supports a response time of 3 to 4 ms across a LONWORKS Network and has double the input / output (I / O) performance of the previous Neuron Chip in terms of both response time and data transmission speed. Neuron Chips have all the built-in communications and control functions required to implement LONWORKS nodes. These nodes may then be easily integrated into highly-reliable distributed intelligent control networks.

The typical functions for this chip are explained below.

#### FEATURES

New features

(In comparison with TMPN3120FE3M and TMPN3120A20M/U)

- Enhanced communication port

- The package is QFP44-P-1010-0.80 (TMPN3120A20U only)

SOP32-P-525-1.27 : 1.1g (Typ.) QFP44-P-1010-0.80 : 0.6g (Typ.)

000707EBA1

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document when the products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others

- The information contained herein is subject to change without notice.

### TOSHIBA

- Main features of the 20MHz Neuron Chip (In comparison with the TMPN3120E1M and TMPN3120A20M / U)

- Increased communication speed

- The maximum transmission speed has been increased two-fold.

- $1.25 \; \mathrm{Mbps}{\rightarrow} \; 2.5 \; \mathrm{Mbps} \; (*1)$

- \*1: This value applies to Single-Ended Mode only.

- Shortened response time

The amount of time required from I / O input to I / O output has been greatly reduced. Maximum speed  $7ms \rightarrow 3\sim 4 ms$

• Increased IO object speed

The execution time for all objects has been halved. Example) Serial I / O 9600bps Parallel I / O 1.2µs / byte

• Development tool support

The current LonBuilder<sup>®</sup> and NodeBuilder<sup>®</sup> development tools can be used to develop applications for the TMPN3120A20M and TMPN3120A20U (L.B ver. 3.0 or 3.01 is needed). Updated symbol table files for the Neuron Chip firmware are available from Echelon. If your application requires a 20MHz input clock, a utility program available from Echelon may be used to convert the programmer files.

#### \* The conversion utilities can be obtained from the Echelon Web Site at http://www.echelon.com.

- I / O Functions

- Eleven programmable I / O pins.

- Two programmable 16-bit timers and counters built in.

- 34 different types of I / O functions to handle a wide range of input and output.

- ROM firmware image containing pre-programmed I / O drivers, greatly simplifying application programs.

- Network functions

- Two CPUs for communication protocol processing built in. The communications and application CPUs execute in parallel.

- Equipped with a built-in LonTalk protocol which supports all seven levels of the OSI reference model with ISO.

- The ROM firmware image contains a complete network operating system, greatly simplifying application programs.

- Built-in twisted-pair wire transceiver with improved common mode and drive current capabilities.

- Equipped with communications modes and communication speeds which support various types of external transceivers.

Supports twisted-pair wire, power line, radio (RF), infrared, coaxial cables, and fiber optics.

• Communication port transceiver modes and logical addresses stored within the EEPROM. Can be amended via the network.

### TOSHIBA

Other functions

- Application programs are also stored within the EEPROM. Can be updated by downloading over the network.

- Built-in watch-dog timer.

- Each chip has a unique ID number. Effective during the logical installation of networks.

- Low electrical consumption mode supported with a sleep mode.

- Built in Selectable Reset time

- Prolongs the power-ON reset time for at least 50ms and keeps the operation stable during that time. The reset time can be selected 50ms delay mode or 3clock delay mode by program after the device is in power-ON.

- High-impedance communication port ( CP0 to CP3 )

The Communication port pins ( CP0 to CP3 ) attain high impedance. This eliminates the need for an external relay.

- Built-in low-voltage detection circuit. Prevents in correct operations and writing errors in the EEPROM during drops in power voltage. An external LVD must be used to assert reset at power supply voltage below 4.5 V if Neuron Chip is operated at 20 MHz.

- Programmable LVD (Low Voltage Detection) circuit.

LVDin pin is prepared in order to make it reset on arbitrary voltage.

- Firmware version 9.

- Timing for the main I / O objects during 20 MHz Neuron Chip operations

| I / O MODEL           | 10 MHz TIMING               | 20 MHz TIMING                |  |

|-----------------------|-----------------------------|------------------------------|--|

| Parallel              | 2.4µs / byte                | 1.2µs / byte                 |  |

| Bitshift              | 1, 10 or 15 kbps            | 2, 20 or 30 kbps             |  |

| Magcard               | Up to 8334 bps              | Up to 16668 bps              |  |

| Magtrack1             | Up to 7246 bps              | Up to 14492 bps              |  |

| Neurowire Master      | 1, 10 or 20 kbps            | 2, 20 or 40 kbps             |  |

| Neurowire Slave       | Up to 18 kbps               | Up to 36 kbps                |  |

| Serial                | 600, 1200, 2400 or 4800 bps | 1200, 2400, 4800 or 9600 bps |  |

| Touch                 | Supported                   | Not supported                |  |

| Francisco Octoret     | Resolution0.4 to 51.2µs     | Resolution0.2 to 25.6µs      |  |

| Frequency Output      | Max Range 26.21 to 3355 ms  | Max Range 13.1 to 1678 ms    |  |

| Other Timer / Counter | Resolution0.2 to 25.6µs     | Resolution0.1 to 12.8µs      |  |

| Other Timer / Counter | Max Range 13.1 to 1678 ms   | Max Range 6.55 to 839 ms     |  |

The specifications for the main timers during 20 MHz operations are as follows :

| Watchdog Timer               | 420 ms            |

|------------------------------|-------------------|

| Millisecond Timers           | 1 to 32000 ms     |

| Second Timers                | 1 to 65000 s      |

| Delay ( ) Function           | 1 to 32767 counts |

| Get_Tick_Count()<br>Function | 409.6µs per count |

# **TOSHIBA**

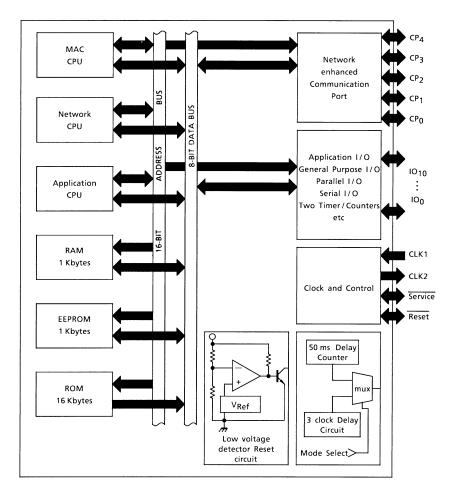

### **BLOCK DIAGRAM**

| ITEM                      | TMPN3120A20M  | TMPN3120A20U |

|---------------------------|---------------|--------------|

| CPU                       | 8-bit CPU × 3 | 8-bit CPU× 3 |

| RAM                       | 1,024 bytes   | 1,024 bytes  |

| ROM                       | 16,384 bytes  | 16,384 bytes |

| EEPROM                    | 1,024 bytes   | 1,024 bytes  |

| 16-bit Timer / Counter    | 2 channels    | 2 channels   |

| External Memory Interface | No            | No           |

| Package                   | 32-pin SOP    | 44-pin QFP   |

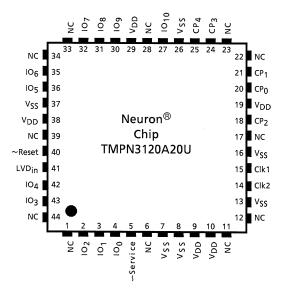

#### **PIN CONNECTION**

TOSHIBA

| 1                 | /                       |    | i i              |

|-------------------|-------------------------|----|------------------|

| ~RESET            |                         | 32 | VDD              |

| LVD <sub>in</sub> | 2                       | 31 | VSS              |

| 104               | 3                       | 30 | 105              |

| 103               | 4                       | 29 | 10 <sub>6</sub>  |

| 10 <sub>2</sub>   | 5                       | 28 | 10 <sub>7</sub>  |

| 10 <sub>1</sub>   | 6                       | 27 | 10 <sub>8</sub>  |

| 100               | 7                       | 26 | و0ا              |

| ~SERVICE          | 8 Neuron <sup>®</sup>   | 25 | VDD              |

| V <sub>SS</sub>   | Chip                    | 24 | 10 <sub>10</sub> |

| V <sub>SS</sub>   | <sup>TMPN3120A20M</sup> | 23 | V <sub>SS</sub>  |

| V <sub>DD</sub>   | 11                      | 22 | CP4              |

| V <sub>DD</sub>   | 12                      | 21 | CP3              |

| V <sub>SS</sub>   | 13                      | 20 | CP1              |

| CLK2              | 14                      | 19 | CP0              |

| CLK1              | 15                      | 18 | V <sub>DD</sub>  |

| V <sub>SS</sub>   | 16                      | 17 | CP2              |

\*: All NC pins should be open.

#### **PIN FUNCTION**

| PIN No.               |                                                    | PIN NAME                          | 1/0                                            |                                                                                                                                                                                                                             |

|-----------------------|----------------------------------------------------|-----------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMPN3120A20M          | TMPN3120A20U                                       | PIN NAME                          | 170                                            | PIN FUNCTION                                                                                                                                                                                                                |

| 15                    | 15                                                 | CLK1                              | Input                                          | Oscillator connection, or external clock input.                                                                                                                                                                             |

| 14                    | 14                                                 | CLK2                              | Output                                         | Oscillator connection. Leave open when external clock is input to CLK1.                                                                                                                                                     |

| 1                     | 40                                                 | ~RESET                            | I / O                                          | Reset pin. ( Active low )                                                                                                                                                                                                   |

|                       |                                                    |                                   | (built-in pull-up)                             |                                                                                                                                                                                                                             |

|                       |                                                    |                                   | I / O                                          |                                                                                                                                                                                                                             |

| 8                     | 5                                                  | ~SERVICE                          | (built-in<br>configurable<br>pull-up)          | Service pin. Indicator output during operation.                                                                                                                                                                             |

| 7~4                   | 4~2, 43                                            | 10 <sub>0</sub> ~10 <sub>3</sub>  | I/O                                            | Large current sink capacity ( 20 mA ).<br>General I / O port.                                                                                                                                                               |

| 3, 30~28              | 42, 36, 35, 32                                     | 10 <sub>4</sub> ~10 <sub>7</sub>  | I / O<br>(built-in<br>configurable<br>pull-up) | General I / O port. One of $IO_4$ to $IO_7$ can be<br>specified as No.1 timer / counter input. Output<br>signal can be output to $IO_0$ .<br>$IO_4$ can be used as the No.2 timer / counter input<br>with $IO_1$ as output. |

| 27, 26, 24            | 31, 30, 27                                         | 10 <sub>8</sub> ~10 <sub>10</sub> | I/O                                            | General I / O port. Can be used for serial communication with other device.                                                                                                                                                 |

| 11, 12, 18, 25, 32    | 9, 10, 19, 29, 38                                  | V <sub>DD</sub>                   | Input                                          | Power input ( 5.0 V Typ. )                                                                                                                                                                                                  |

| 9, 10, 13, 16, 23, 31 | 7, 8, 13, 16, 26, 37                               | V <sub>SS</sub>                   | Input                                          | Power input ( 0 V GND )                                                                                                                                                                                                     |

| 2                     | 41                                                 | LVD <sub>in</sub>                 | Input                                          | Input pin for programmable LVD<br>( Normally connect to V <sub>DD</sub> )                                                                                                                                                   |

| 19, 20, 17, 21, 22    | 20, 21, 18, 24, 25                                 | CP <sub>0</sub> ~CP <sub>4</sub>  | I/O                                            | Bidirectional port for communications. Supports several communications protocols by specifying mode.                                                                                                                        |

| _                     | 1, 6, 11, 12, 17, 22,<br>23, 28, 33, 34, 39,<br>44 | NC                                | _                                              | Do not connect anything. Leave pins open.                                                                                                                                                                                   |

\*: • The ~SERVICE and IO<sub>4</sub> to IO<sub>7</sub> terminals are programmable pull-ups.

$\bullet$  All  $V_{DD}$  terminals must be externally connected.

$\bullet$  All VSS terminals must be externally connected.

### MAXIMUM RATINGS ( V<sub>SS</sub> = 0V, V<sub>SS</sub> typ.)

| ITEM                  | SYMBOL              | RATING                                                       | UNIT |

|-----------------------|---------------------|--------------------------------------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub>     | -0.3~7.0                                                     | V    |

| Input Voltage         | V <sub>IN</sub>     | -0.3 to V <sub>DD</sub> + 0.3 V                              | V    |

| Input Voltage CP0-CP3 | V <sub>IN (2)</sub> | −0.5 to V <sub>DD</sub> + 1.3 V<br>V <sub>IN (2)</sub> < 7.3 | V    |

| Power Dissipation     | PD                  | 800                                                          | mW   |

| Storage Temperature   | T <sub>stg</sub>    | -65~150                                                      | °C   |

#### **OPERATING CONDITIONS**

| ITEM                   | SYMBOL           | MIN                     | TYP. | MAX                     | UNIT |

|------------------------|------------------|-------------------------|------|-------------------------|------|

| Operating Voltage      | V <sub>DD</sub>  | 4.5                     | 5.0  | 5.5                     | V    |

| Input Voltage ( TTL )  | V <sub>IH</sub>  | 2.0                     | —    | V <sub>DD</sub>         | V    |

| input voltage (TTL)    | V <sub>IL</sub>  | V <sub>SS</sub>         | —    | 0.8                     | V    |

| Input Voltage ( CMOS ) | V <sub>IH</sub>  | V <sub>DD</sub> – 0.8 V | —    | V <sub>DD</sub>         | V    |

|                        | V <sub>IL</sub>  | V <sub>SS</sub>         | —    | 0.8                     | V    |

| Input Voltage CP0-CP3  | V <sub>IH</sub>  | —                       | —    | V <sub>DD</sub> + 1.0 V | V    |

| ( differential mode )  | V <sub>IL</sub>  | -0.1                    | —    | _                       | v    |

| Operating Frequency    | f <sub>osc</sub> | 0.625                   | _    | 20                      | MHz  |

| Operating Temperature  | T <sub>opr</sub> | -40                     | _    | 85                      | °C   |

#### ELECTRICAL CHARACTERISTICS DC characteristic ( $V_{DD}$ = 5.0 V ± 10%, $V_{SS}$ = 0 V, Ta = -40~85°C) (Above operating conditions apply unless otherwise states.)

| ITEM                         | SYMBOL                      | PINS                                                                                                   | TEST CONDITION                                     | MIN                        | MAX                      | UNIT |

|------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------|--------------------------|------|

| LOW Level Input Voltage (1)  | V <sub>IL</sub> (1)         | IO <sub>0</sub> ~IO <sub>10</sub><br>CP <sub>0</sub> , CP <sub>3</sub> , CP <sub>4</sub> ,<br>~SERVICE | _                                                  | 0                          | 0.8                      | v    |

| LOW Level Input Voltage (2)  | V <sub>IL</sub> (2)         | ~RESET                                                                                                 | -                                                  | 0                          | V <sub>DD</sub><br>× 0.3 | V    |

| HIGH Level Input Voltage (1) | V <sub>IH</sub> (1)         | IO <sub>0</sub> ~IO <sub>10</sub><br>CP <sub>0</sub> , CP <sub>3</sub> , CP <sub>4</sub> ,<br>~SERVICE | _                                                  | 2.0                        | V <sub>DD</sub>          | V    |

| HIGH Level Input Voltage (2) | V <sub>IH</sub> (2)         | ~RESET                                                                                                 | _                                                  | V <sub>DD</sub><br>- 0.7 V | V <sub>DD</sub>          | V    |

|                              |                             | 10 <sub>0</sub> ~10 <sub>3</sub>                                                                       | I <sub>OL</sub> = 20mA                             | 0                          | 0.8                      | v    |

| LOW Output Voltage (1)       | V <sub>OL</sub> (1)         | ~SERVICE,<br>~RESET                                                                                    | I <sub>OL</sub> = 10mA                             | 0                          | 0.4                      |      |

| LOW Output Voltage (2)       | V <sub>OL</sub> (2)         | CP <sub>2</sub> , CP <sub>3</sub>                                                                      | I <sub>OL</sub> = 40mA                             | 0                          | 1.0                      | V    |

| LOW Output Voltage (3)       | V <sub>OL</sub> (3)         | Others (Note 1)                                                                                        | I <sub>OL</sub> =1.4mA                             | 0                          | 0.4                      | V    |

| HIGH Output Voltage (1)      | V <sub>OH</sub> (1)         | 10 <sub>0</sub> ~10 <sub>3</sub>                                                                       | I <sub>OH</sub> = −1.4mA                           | V <sub>DD</sub><br>- 0.4 V | V <sub>DD</sub>          | V    |

| HIGH Output Voltage (2)      | V <sub>OH</sub> (2)         | ~SERVICE                                                                                               | I <sub>OH</sub> = −1.4mA                           | V <sub>DD</sub><br>- 0.4 V | V <sub>DD</sub>          | V    |

| HIGH Output Voltage (3)      | V <sub>OH</sub> (3)         | CP <sub>2</sub> , CP <sub>3</sub>                                                                      | I <sub>OH</sub> = -40mA                            | V <sub>DD</sub><br>- 1.0 V | V <sub>DD</sub>          | V    |

| HIGH Output Voltage (4)      | V <sub>OH</sub> (4)         | Others ( Note 1 )                                                                                      | I <sub>OH</sub> = −1.4mA                           | V <sub>DD</sub><br>- 0.4 V | V <sub>DD</sub>          | V    |

| Input Current                | I <sub>IN</sub>             | ( Note 2 )                                                                                             | V <sub>IN</sub> = V <sub>SS</sub> ~V <sub>DD</sub> | -10                        | 10                       | μA   |

| Pull-up Current              | I <sub>PU</sub><br>(Note 3) | IO <sub>4</sub> ~IO <sub>7</sub><br>~SERVICE,<br>~RESET                                                | V <sub>IN</sub> = 0V                               | -30                        | -300                     | μA   |

| Low-voltage Detection Level  | V <sub>LVD</sub>            | V <sub>DD</sub>                                                                                        | _                                                  | 3.8                        | 4.5                      | V    |

Note1 : Output voltage characteristics exclude the CLK2 pin.

Note2 : Excludes pull-up input pins.

Note3 : The IO<sub>4</sub> to IO<sub>7</sub> and ~SERVICE pins have programmable pull-ups. ~RESET has a fixed pull-up.

| ITEM                                        |                 | SYMBOL                | TYP. | MAX | UNIT |

|---------------------------------------------|-----------------|-----------------------|------|-----|------|

| Operating<br>Mode<br>Current<br>Consumption | 20 MHz Clock    |                       | 33   | 55  |      |

|                                             | 10 MHz Clock    | I <sub>DD</sub> (OP)  | 15   | 30  |      |

|                                             | 5 MHz Clock     |                       | 7    | 15  | mA   |

|                                             | 2.5 MHz Clock   |                       | 4    | 8   | ШA   |

|                                             | 1.25 MHz Clock  |                       | 2.2  | 5   |      |

|                                             | 0.625 MHz Clock |                       | 1.2  | 3   |      |

| Sleep Mode Current<br>Consumption           |                 | I <sub>DD (SLP)</sub> | 16   | 100 | μA   |

Note: Test conditions for current dissipation

VDD = 5V, all output = with no load, all input = 0.2V or below or VDD - 0.2 V, programmable pull-up = off, crystal oscillator clock input, differential receiver disabled.

The current value ( typ. ) is a typical value when Ta = 25.°C

The current value (max) applies to the rated temperature range at VDD = 5.5 V.

$200 A\mu ($  typ. ) to  $600 \mu A$  ( max ) is added to the current of the differential receiver when the receiver is enabled.

The differential receiver is enabled by either of the following conditions :

- When the Neuron Chip is in Run mode and the communication ports are in Differential mode.

- When the Neuron Chip is in Sleep mode, the communication ports are in Differential mode, and the Comm Port Wakeup is not masked.

# <u>TOSHIBA</u>

- Echelon, Neuron, LON, LonTalk, LonBuilder, NodeBuilder, LonWORKS, 3150, 3120 and LonManager are the registered trade marks of America's Echelon Inc.

- The Neuron Chip is manufactured by Toshiba under license from Echelon Corporation, USA. A licensing agreement between the customer and Echelon Corporation must be concluded before purchasing any of the neuron chip products.

- The Neuron chip itself does not include the I<sup>2</sup>C object function. You need the "I<sup>2</sup>C Library" delivered by Echelon. The Neuron chip and the I<sup>2</sup>C Library do not convey nor imply a right under any I<sup>2</sup>C patent rights of Philips Electronics N.V. ("Philips") to make, use or sell any product employing such patent rights. Please refer all questions with respect to I<sup>2</sup>C patents and licenses to Philips at:

Mr. Gert-Jan Hessenlmann Corporate Intellectual Property Philips International B.V. Prof. Holstlaan 6 Building WAH 1-100 P.O. Box 220 5600 AE, Eindhoven, The Netherlands Phone : +31 40 274 32 61 Fax : +31 40 274 34 89 E-mail: Gert.Jan.Hesselmann@philips.com.

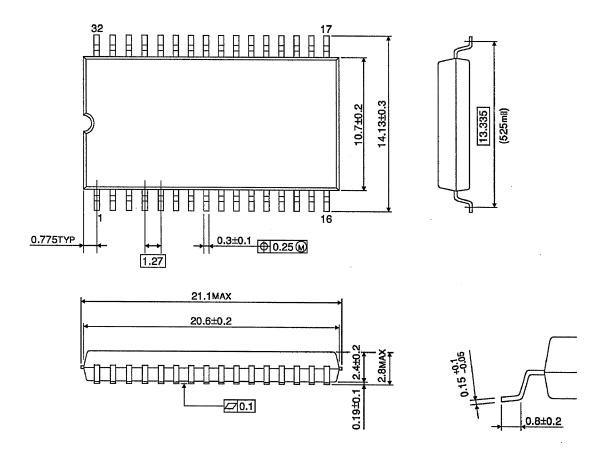

#### PACKEGE DIMENSIONS

SOP32-P-525-1.27

Unit : mm

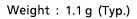

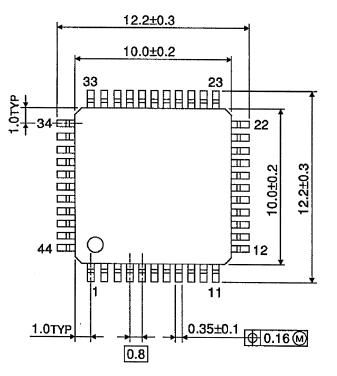

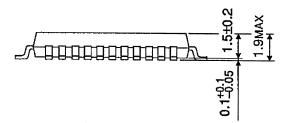

#### PACKEGE DIMENSIONS

QFP44-P-1010-0.80

Weight : 0.6 g (Typ.)