# L9217A/G Low-Cost Line Interface with Reverse Battery and PPM

#### **Features**

- Basic forward/reverse battery SLIC functionality at a low cost

- Pin compatible with Agere Systems Inc. L9218/ L9219 SLIC

- Low active power (typical 154 mW during on-hook transmission)

- Low-power scan mode for low-power, on-hook power dissipation (57 mW typical)

- Distortion-free, on-hook transmission

- Convenient operating states:

- Forward powerup

- Reverse powerup

- Low-power scan

- Disconnect (high impedance)

- PPM operational states

- Minimal external components required

- Two gain options to optimize the codec interface

- Adjustable supervision functions:

- Off-hook detector with hysteresis

- Ring trip detector

- Adjustable loop current limit

- Adjustable overhead voltage

- Ramped rate of battery reversal

- Periodic pulse metering (PPM) compatible

- Thermal protection with thermal shutdown indication

## **Description**

This general-purpose electronic subscriber loop interface circuit (SLIC) is optimized for low cost, while still providing a satisfactory set of features. This part is a pin-for-pin replacement for the Agere L9218/L9219 SLIC.

The L9217 requires a 5 V power supply and single battery to operate. This device offers forward and reverse battery operation. The rate of battery reversal may be ramped to meet international requirements. Additionally, a low-power scan mode, wherein all circuitry except the off-hook supervision is shut down to conserve power, is available.

The dc current limit may be programmed via a single external resistor. Both the loop supervision and ring trip supervision functions are offered with user-controlled thresholds via external resistors. Overhead is adequate for 3.14 dBm into 900  $\Omega$  of on-hook transmission.

The device is periodic pulse metering (PPM) compatible, offering a convenient point for meter pulse injection and filter point for rejection of the meter pulse signal. In the PPM active modes, overhead voltage is automatically increased to accommodate on-hook transmission of meter pulse signals. The level that the overhead is increased to is set by a single external resistor. In this way, the L9217 can accommodate high-voltage meter pulse signals.

The L9217 is offered with a receive gain that is optimized to interface to a first-generation type codec (L9217A). It is also offered with a gain option that is optimized to interface to a third- or fourth-generation type codec (L9217G). In both cases, minimizing external components is required at this interface.

Data control is via a parallel data control scheme.

The device is available in a 28-pin PLCC package. It is built by using a 90 V complementary bipolar (CBIC) process.

# **Table of Contents**

| Contents                                   | Page | Figures                                                  | Page  |

|--------------------------------------------|------|----------------------------------------------------------|-------|

| Features                                   | 1    | Figure 1. Functional Diagram                             | 3     |

| Description                                | 1    | Figure 2. 28-Pin PLCC                                    |       |

| Pin Information                            | 4    | Figure 3. Ring Trip Circuits                             |       |

| Functional Description                     |      | Figure 4. L9217 Basic Test Circuit                       |       |

| Absolute Maximum Ratings                   |      | Figure 5. Metallic PSRR                                  |       |

| Recommended Operating Conditions           |      | Figure 6. Longitudinal PSRR                              |       |

| Electrical Characteristics                 |      | Figure 7. Longitudinal Balance                           |       |

| Ring Trip Requirements                     |      | Figure 8. RFI Rejection                                  |       |

| Test Configurations                        |      | Figure 9. Longitudinal Impedance                         |       |

| Applications                               |      | Figure 10. ac Gains                                      |       |

| dc Applications                            |      | Figure 11. Basic Loop Start Application Circuit          |       |

| Battery Feed                               |      | Using T7504-Type Codec                                   | 15    |

| Overhead Voltage                           |      | Figure 12. Basic Loop Start Application Circuit          |       |

| Rate of Battery Reversal                   |      | Using T8536-Type Codec                                   | 17    |

| Loop Range                                 |      | Figure 13. Loop Current vs. Loop Voltage                 |       |

| Off-Hook Detection                         |      | Figure 14. Off-Hook Detection Circuit                    |       |

| Ring Trip Detection                        |      | Figure 15. Ring Trip Equivalent Circuit and              |       |

| Longitudinal Balance                       |      | Equivalent Application                                   | 20    |

| Periodic Pulse Metering (PPM)              |      | Figure 16. ac Equivalent Circuit                         |       |

| ac Design                                  |      | Figure 17. Interface Circuit Using First-Generation      |       |

| Codec Types                                |      | Codec (±5 V Codec)                                       |       |

| ac Interface Network                       |      | Figure 18. Interface Circuit Using First-Generation      |       |

| Receive Interface                          |      | Codec (+5 V Only Codec)                                  |       |

| Example 1: Real Termination                |      |                                                          |       |

| (First-Generation Codec)                   | 24   | Tables                                                   | Page  |

| Example 2: Complex Termination             |      | 148100                                                   | . ago |

| (First-Generation Codec)                   | 26   | Table 1. Pin Descriptions                                | 1     |

| Power Derating                             |      | Table 2. Input State Coding                              |       |

| Pin-for-Pin Compatibility with L9218/L9219 |      | Table 3. Supervision Coding                              |       |

| PCB Layout Information                     |      | Table 4. Power Supply                                    |       |

| Outline Diagram                            |      | Table 5. 2-Wire Port                                     |       |

| 28-Pin PLCC                                |      | Table 6. Analog Pin Characteristics                      |       |

| Ordering Information                       |      | Table 7. PPM                                             |       |

|                                            |      | Table 8. ac Feed Characteristics                         |       |

|                                            |      | Table 9. Logic Inputs and Outputs                        |       |

|                                            |      | Table 11. Parts List for Loop Start Application Ci       |       |

|                                            |      | Using T7504-Type Codec                                   |       |

|                                            |      | Table 10. 900 $\Omega$ Termination, 850 $\Omega$ + 50 nF | 10    |

|                                            |      | Hybrid First-Generation Codec Design                     |       |

|                                            |      | Parameters                                               |       |

|                                            |      | Table 12. Parts List for Loop Start Application          | 13    |

|                                            |      | Circuit Using T8536-Type Codec                           | 10    |

|                                            |      | Table 13. FB1/FB2 Values vs.Typical Ramp                 | 10    |

|                                            |      | Time                                                     | 20    |

|                                            |      | I II I I I C                                             | ∠∪    |

# **Description** (continued)

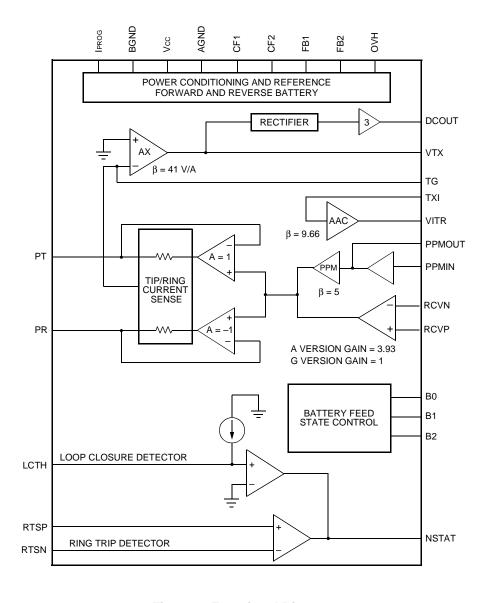

12-3557 (F)

Figure 1. Functional Diagram

## **Pin Information**

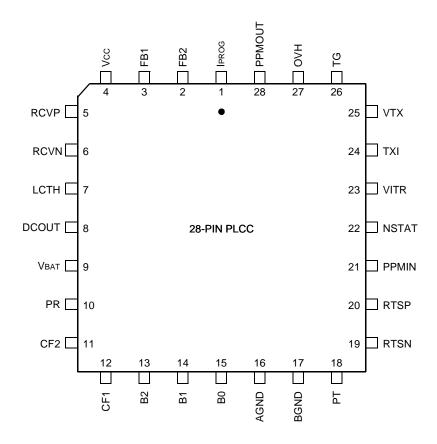

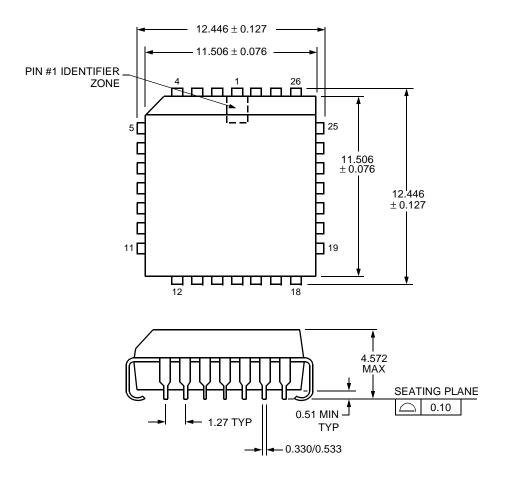

12-3558 (F).c

Figure 2. 28-Pin PLCC

**Table 1. Pin Descriptions**

| PLCC | Symbol | Туре | Description                                                                                                                    |

|------|--------|------|--------------------------------------------------------------------------------------------------------------------------------|

| 1    | IPROG  | l    | <b>Current-Limit Program Input.</b> A resistor to DCOUT sets the dc current limit of the device.                               |

| 2    | FB2    | _    | <b>Polarity Reversal Slowdown.</b> Connect a capacitor to ground to control the rate of battery reversal.                      |

| 3    | FB1    | _    | <b>Polarity Reversal Slowdown.</b> Connect a capacitor to ground to control the rate of battery reversal.                      |

| 4    | Vcc    | _    | 5 V Power Supply.                                                                                                              |

| 5    | RCVP   | I    | <b>Receive ac Signal Input (Noninverting).</b> This high-impedance input controls the ac differential voltage on tip and ring. |

| 6    | RCVN   | I    | <b>Receive ac Signal Input (Inverting).</b> This high-impedance input controls the ac differential voltage on tip and ring.    |

# Pin Information (continued)

Table 1. Pin Descriptions (continued)

| PLCC | Symbol | Type | Description                                                                                                                                                                                                                                                                                                    |  |  |  |

|------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7    | LCTH   | I    | <b>Loop Closure Threshold Input.</b> Connect a resistor to DCOUT to set off-hook threshold.                                                                                                                                                                                                                    |  |  |  |

| 8    | DCOUT  | 0    | <b>C Output Voltage.</b> This output is a voltage that is directly proportional to the absote value of the differential tip/ring current.                                                                                                                                                                      |  |  |  |

| 9    | VBAT   | _    | Battery Supply. Negative high-voltage power supply.                                                                                                                                                                                                                                                            |  |  |  |

| 10   | PR     | I/O  | <b>Protected Ring.</b> The output of the ring driver amplifier and input to loop sensing circuitry. Connect to the loop through overvoltage protection.                                                                                                                                                        |  |  |  |

| 11   | CF2    | _    | Filter Capacitor 2. Connect a 0.1 μF capacitor from this pin to AGND.                                                                                                                                                                                                                                          |  |  |  |

| 12   | CF1    | _    | Filter Capacitor 1. Connect a 0.47 μF capacitor from this pin to pin CF2.                                                                                                                                                                                                                                      |  |  |  |

| 13   | B2     | I    | <b>State Control Input.</b> B0, B1, and B2 determine the state of the SLIC. See Table 2. Pin B2 has internal pull-down.                                                                                                                                                                                        |  |  |  |

| 14   | B1     | _    | <b>State Control Input.</b> B0, B1, and B2 determine the state of the SLIC. See Table 2. Pin B1 has internal pull-down.                                                                                                                                                                                        |  |  |  |

| 15   | B0     | _    | <b>State Control Input.</b> B0, B1, and B2 determine the state of the SLIC. See Table 2. Pin B0 has internal pull-down.                                                                                                                                                                                        |  |  |  |

| 16   | AGND   |      | Analog Signal Ground.                                                                                                                                                                                                                                                                                          |  |  |  |

| 17   | BGND   |      | Battery Ground. Ground return for the battery supply.                                                                                                                                                                                                                                                          |  |  |  |

| 18   | PT     | I/O  | <b>Protected Tip.</b> The output of the tip driver amplifier and input to loop sensing circuitry. Connect to loop through overvoltage protection.                                                                                                                                                              |  |  |  |

| 19   | RTSN   | I    | <b>Ring Trip Sense Negative.</b> Connect this pin to the ringing generator signal through a high-value resistor.                                                                                                                                                                                               |  |  |  |

| 20   | RTSP   | I    | Ring Trip Sense Positive. Connect this pin to the ring relay and the ringer series resistor through a high-value resistor.                                                                                                                                                                                     |  |  |  |

| 21   | PPMIN  | I    | <b>Receive PPM Signal Input.</b> This high-impedance input controls the PPM differential voltage on tip and ring. The PPM signal may be present at this pin at all times: however, PPM will only be transmitted to tip and ring if the appropriate PPM state is chosen. ac couple the PPM signal to this node. |  |  |  |

| 22   | NSTAT  | 0    | Ring Trip Detector Output/Loop Detector Output. When low, this logic output indicates that ringing is tripped or that an off-hook condition exists.                                                                                                                                                            |  |  |  |

| 23   | VITR   | 0    | <b>ac Output Voltage.</b> The voltage at this point is directly proportional to the differential tip/ring current.                                                                                                                                                                                             |  |  |  |

| 24   | TXI    | I    | ac/dc Separation. Connect a 0.1 μF capacitor from this point to VTX.                                                                                                                                                                                                                                           |  |  |  |

| 25   | VTX    | 0    | <b>ac Output Voltage.</b> This output is a voltage that is directly proportional to the differential tip/ring current.                                                                                                                                                                                         |  |  |  |

| 26   | TG     | _    | <b>Transmit Gain.</b> Connect an 8.06 k $\Omega$ from TG to VTX to set the transmit gain of the SLIC.                                                                                                                                                                                                          |  |  |  |

| 27   | OVH    | _    | <b>PPM Overhead.</b> Connect a resistor from this node to ground to set the overhead voltage during PPM high overhead modes.                                                                                                                                                                                   |  |  |  |

| 28   | PPMOUT | 0    | <b>PPM Signal Output.</b> Connect a resistor from this node to TG for hybrid cancellation of the periodic pulse metering (PPM) signal.                                                                                                                                                                         |  |  |  |

# **Functional Description**

# **Table 2. Input State Coding**

| В0 | B1 | B2 | State/Definition                                                                                                                                                                                                                                                                  |

|----|----|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 1  | 1  | <b>Powerup, Forward Battery, Normal Overhead.</b> Normal talk and battery feed state. Pin PT is positive with respect to PR. On-hook transmission is enabled. PPM is not active. Overhead is unaffected by resistor OVH and is adequate for 3.14 dBm overload into 900 $\Omega$ . |

| 1  | 0  | 1  | <b>Powerup, Reverse Battery, Normal Overhead.</b> Normal talk and battery feed state. Pin PT is negative with respect to PR. On-hook transmission is enabled. PPM is not active. Overhead is unaffected by resistor OVH and is adequate for 3.14 dBm overload into 900 $\Omega$ . |

| 1  | 1  | 0  | <b>Powerup, Forward Battery, High Overhead.</b> Normal talk and battery feed state. Pin PT is positive with respect to PR. On-hook transmission is enabled. PPM is not active. Overhead is increased via resistor OVH.                                                            |

| 1  | 0  | 0  | <b>Powerup, Reverse Battery, High Overhead.</b> Normal talk and battery feed state. Pin PT is negative with respect to PR. On-hook transmission is enabled. PPM is not active. Overhead is increased via resistor OVH.                                                            |

| 0  | 1  | 1  | <b>Low-Power Scan.</b> Except for off-hook detection, all circuits are shut down to conserve power. Pin PT is positive with respect to pin PR. On-hook transmission is disabled.                                                                                                  |

| 0  | 0  | 1  | <b>Disconnect.</b> The tip and ring amplifiers are turned off, and the SLIC goes to a high-impedance state (>100 k $\Omega$ ). Supervision outputs read on hook. Device will power up in this state.                                                                              |

| 0  | 0  | 0  | <b>Powerup, Reverse Battery, High Overhead with PPM.</b> Normal talk and battery feed state. Pin PT is negative with respect to PR. On-hook transmission is enabled. PPM is active. Overhead is increased via resistor OVH.                                                       |

| 0  | 1  | 0  | <b>Powerup, Forward Battery, High Overhead with PPM.</b> Normal talk and battery feed state. Pin PT is positive with respect to PR. On-hook transmission is enabled. PPM is active. Overhead is increased via resistor OVH.                                                       |

# **Table 3. Supervision Coding**

| NSTAT                         |

|-------------------------------|

| 0 = off-hook or ring trip.    |

| 1 = on-hook and no ring trip. |

# **Absolute Maximum Ratings** (at TA = 25 °C)

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect device reliability.

| Parameter                                  | Symbol       | Min       | Тур  | Max             | Unit |

|--------------------------------------------|--------------|-----------|------|-----------------|------|

| 5 V Power Supply                           | Vcc          | _         | _    | 7.0             | V    |

| Battery (Talking) Supply                   | VBAT         | _         | _    | <del>-</del> 75 | V    |

| Logic Input Voltage                        | _            | -0.5      | _    | 7.0             | V    |

| Analog Input Voltage                       | _            | -7.0      | _    | 7.0             | V    |

| Maximum Junction Temperature               | Тл           | 150       | _    |                 | °C   |

| Storage Temperature Range                  | Tstg         | -40       | _    | 125             | °C   |

| Relative Humidity Range                    | Rн           | 5         | _    | 95              | %    |

| Ground Potential Difference (BGND to AGND) | _            | _         | ±3   | _               | V    |

| PT or PR Fault Voltage (dc)                | VPT, VPR     | VBAT – 5  | _    | 3               | V    |

| PT or PR Fault Voltage (10 x 1000 μs)      | Vpt, Vpr     | VBAT – 15 | _    | 15              | V    |

| Current into Ring Trip Inputs              | IRTSP, IRTSN | _         | ±240 | _               | μΑ   |

Note: The IC can be damaged unless all ground connections are applied before, and removed after, all other connections. Furthermore, when powering the device, the user must guarantee that no external potential creates a voltage on any pin of the device that exceeds the device ratings. Some of the known examples of conditions that cause such potentials during powerup are the following:

- 1. An inductor connected to tip and ring can force an overvoltage on VBAT through the protection devices if the VBAT connection chatters.

- 2. Inductance in the VBAT lead could resonate with the VBAT filter capacitor to cause a destructive overvoltage.

# **Recommended Operating Conditions**

| Parameter           | Min  | Тур | Max             | Unit |

|---------------------|------|-----|-----------------|------|

| Ambient Temperature | -40  | _   | 85              | °C   |

| Vcc Supply Voltage  | 4.75 | 5.0 | 5.25            | V    |

| VBAT Supply Voltage | -24  | -48 | <del>-7</del> 0 | V    |

#### **Electrical Characteristics**

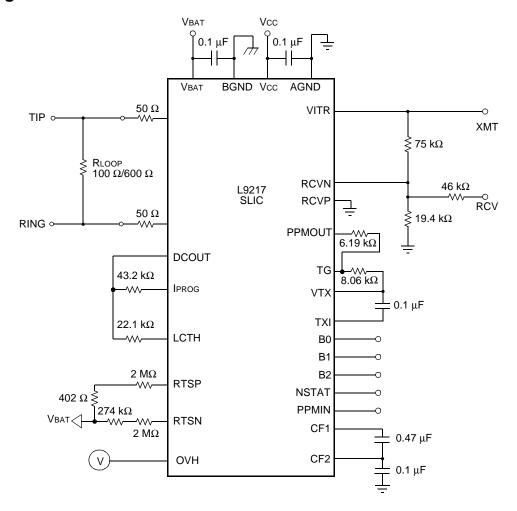

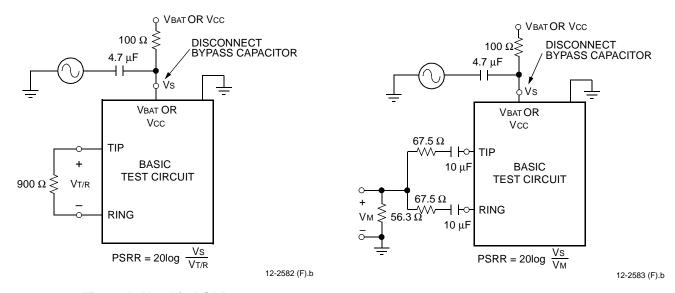

Minimum and maximum values are testing requirements in the temperature range of 25 °C to 85 °C and battery range of –24 V to –70 V. These minimum and maximum values are guaranteed to –40 °C based on component simulations and design verification of samples, but devices are not tested to –40 °C in production. The test circuit shown in Figure 4 is used, unless otherwise noted. Positive currents flow into the device.

Typical values are characteristics of the device design at 25 °C based on engineering evaluations and are not part of the test requirements. Supply values used for typical characterization are Vcc = 5.0 V, VBAT = -48 V, unless otherwise noted.

**Table 4. Power Supply**

| Parameter                                                                 | Min      | Тур   | Max      | Unit |

|---------------------------------------------------------------------------|----------|-------|----------|------|

| Power Supply—Powerup, No Loop Current:                                    |          |       |          |      |

| lcc                                                                       |          | 5.2   | 6.5      | mA   |

| $IBAT\;(VBAT=-48\;V)$                                                     | _        | -2.66 | -2.95    | mA   |

| Power Dissipation (VBAT = -48 V)                                          | _        | 154   | 175      | mW   |

| Power Supply—Scan, No Loop Current:                                       |          |       |          |      |

| lcc                                                                       | _        | 3.4   | 4.3      | mA   |

| $IBAT\;(VBAT=-48\;V)$                                                     | _        | -0.9  | -1       | mA   |

| Power Dissipation (VBAT = -48 V)                                          | _        | 57    | 70       | mW   |

| Power Supply—Disconnect, No Loop Current:                                 |          |       |          |      |

| lcc                                                                       | _        | 1.9   | _        | mA   |

| $IBAT\;(VBAT=-48\;V)$                                                     | _        | -0.1  | _        | mA   |

| Power Dissipation (VBAT = -48 V)                                          | _        | 14    | _        | mW   |

| Power Supply Rejection 500 Hz to 3 kHz                                    |          |       |          |      |

| (See Figures 5, 6, 16, and 17.) <sup>1</sup> :                            |          |       |          |      |

| Vcc                                                                       | 30       | _     | _        | dB   |

| VBAT                                                                      | 36       | _     | _        | dB   |

| Thermal Protection Shutdown (Tjc) <sup>1</sup>                            | 150      | 165   | _        | °C   |

| Thermal Resistance Still Air, Junction to Ambient (θJA) <sup>1, 2</sup> : |          |       |          |      |

| Natural Convection 2S2P Board                                             | _        | 30    | _        | °C/W |

| Natural Convection 2S0P Board                                             | _        | 43    | _        | °C/W |

| Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S2P Board                  | _        | 27    | -        | °C/W |

| Wind Tunnel 100 Linear Feet per Minute (LFPM) 2S0P Board                  | <u> </u> | 36    | <u> </u> | °C/W |

<sup>1.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>2.</sup> Airflow, PCB board layers, and other factors can greatly affect this parameter.

Table 5. 2-Wire Port

| Parameter                                                                                                                                                                             | Min                              | Тур                                   | Max                              | Unit        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------------|----------------------------------|-------------|

| Tip or Ring Drive Current = dc + Longitudinal + Signal Currents                                                                                                                       | 80                               | _                                     | _                                | mA          |

| Signal Current                                                                                                                                                                        | 15                               | _                                     | _                                | mArms       |

| Longitudinal Current Capability per Wire <sup>1</sup>                                                                                                                                 | 8.5                              | 15                                    | _                                | mArms       |

| dc Loop Current Limit <sup>2</sup> :  Allowed Range Including Tolerance <sup>3</sup> Accuracy (RLOOP = 100 $\Omega$ , VBAT = -48 V)                                                   | 15<br>—                          | <br>±5                                | 45<br>—                          | mA<br>%     |

| Powerup Open Loop Voltage Levels (PPMOFF): Common-mode Voltage Differential Voltage VBAT = -48 V <sup>4</sup> (Gain = 2) Differential Voltage VBAT = -48 V <sup>4</sup> (Gain = 7.86) | —<br> Vват + 7.5 <br> Vват + 8.0 | VBAT/2<br> VBAT + 6.5 <br> VBAT + 6.5 | —<br> Vват + 5.9 <br> Vват + 5.9 | V<br>V<br>V |

| Powerup Open Loop Voltage Levels (PPMON) Minimum Programmed Overhead: Differential Voltage VBAT = -48 V (Gain = 7.86)                                                                 | _                                | _                                     | VBAT + 18.67                     | V           |

| Disconnect State:<br>Leakage                                                                                                                                                          | _                                | 10                                    | 150                              | μΑ          |

| dc Feed Resistance (for ILOOP below regulation level) (does not include protection resistor)                                                                                          | _                                | 72                                    | 100                              | Ω           |

| Loop Resistance Range (–3.17 dBm overload into 900 $\Omega$ ; not including protection): ILOOP = 20 mA at VBAT = –48 V                                                                | 1800                             | _                                     | _                                | Ω           |

| Longitudinal to Metallic Balance—IEEE® Std. 455 (See Figure 7.) <sup>5</sup> : 200 Hz to 3400 Hz                                                                                      | 58                               | 61                                    | _                                | dB          |

| Metallic to Longitudinal Balance (open loop): 200 Hz to 4 kHz                                                                                                                         | 40                               | _                                     | _                                | dB          |

| RFI Rejection (See Figure 8.) $^3$ , 0.5 Vrms, 50 $\Omega$ Source, 30% AM Mod 1 kHz: 500 kHz to 100 MHz                                                                               | _                                | <br>_55                               | <br>_45                          | —<br>dBV    |

<sup>1.</sup> The longitudinal current is independent of dc loop current.

<sup>2.</sup> Current-limit ILIM is programmed by a resistor, RPROG, from pin IPROG to DCOUT. ILIM is specified at the loop resistance where current limiting begins (see Figure 13).

<sup>3.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>4.</sup> Specification is reduced to |VBAT1 + 10.5 V| minimum when VBAT1 = -70 V at 85 °C.

<sup>5.</sup> Longitudinal balance of circuit card will depend on loop series protection resistor matching and magnitude. More information is available in the Applications section of this document.

**Table 6. Analog Pin Characteristics**

| Parameter                                                                                                                                               | Min                   | Тур               | Max                   | Unit          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|-----------------------|---------------|

| Differential PT/PR Current Sense (DCOUT): Gain (PT/PR to DCOUT) Offset Voltage at ILOOP = 0                                                             | 121<br>-100           | 125<br>—          | 129<br>100            | V/A<br>mV     |

| Loop Closure Detector Threshold (RLCTH = 22.1 k $\Omega$ ) <sup>1</sup> : On- to Off-hook Threshold (scan mode) Off- to On-hook Threshold (active mode) | 8.8<br>6.0            |                   | 13.6<br>10.2          | mA<br>mA      |

| Ring Trip Comparator: Input Offset Voltage <sup>2</sup> Internal Voltage Source Current at Input RTSP <sup>3</sup>                                      | —<br>-9.1<br>In – 0.5 | ±10<br>-8.6<br>In | —<br>-8.1<br>In + 0.5 | mV<br>V<br>μA |

| RCVN, RCVP: Input Bias Current Input Resistance                                                                                                         | _                     | -0.2<br>1         | -1<br>-               | μΑ<br>ΜΩ      |

<sup>1.</sup> Loop closure threshold is programmed by resistor RLCTH from pin LCTH to pin DCOUT. The programming equation or relationship between off-hook threshold and resistor value is different for active mode versus scan mode (see Applications section for more details).

Table 7. PPM

| Parameter                                     | Min   | Тур | Max   | Unit |

|-----------------------------------------------|-------|-----|-------|------|

| PPM Source*:                                  |       |     |       |      |

| Frequency (f1)                                | 11.88 | 12  | 12.12 | kHz  |

| Frequency (f2)                                | 15.80 | 16  | 16.20 | kHz  |

| Input Signal                                  | 0     | _   | 0.525 | Vrms |

| Signal Gain (from PPMIN to amplifier outputs) | 9     | 10  | 11    | _    |

| Harmonic Distortion                           | _     | 5   | _     | %    |

| Isolation                                     | 50    | _   | _     | dB   |

<sup>\*</sup> PPM signal should be ac-coupled into PPMIN.

<sup>2.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>3.</sup> In is the sourcing current at RTSN. Guaranteed if In is within 5  $\mu A$  to 30  $\mu A$  .

**Table 8. ac Feed Characteristics**

| Parameter                                                                                                                                                                                                                                                           | Min                            | Тур                            | Max                            | Unit                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|--------------------------------|-----------------------|

| ac Termination Impedance <sup>1</sup>                                                                                                                                                                                                                               | 150                            | _                              | 1300                           | Ω                     |

| Longitudinal Impedance at PT/PR <sup>2</sup>                                                                                                                                                                                                                        | _                              | 0                              | _                              | Ω                     |

| Total Harmonic Distortion—200 Hz to 4 kHz <sup>2</sup> : Off-hook On-hook                                                                                                                                                                                           | _<br>_                         |                                | 0.3<br>1.0                     | %<br>%                |

| Transmit Gain, f = 1 kHz (PT/PR to VITR) (current limit)                                                                                                                                                                                                            | -391                           | -403                           | <del>-4</del> 15               | V/A                   |

| L9217A, Open Loop:  Receive + Gain, f = 1 kHz (RCVP to PT/PR) <sup>3</sup> Receive - Gain, f = 1 kHz (RCVN to PT/PR) <sup>3</sup> L9217G, Open Loop:  Receive + Gain, f = 1 kHz (RCVP to PT/PR) <sup>4</sup> Receive - Gain, f = 1 kHz (RCVN to PT/PR) <sup>4</sup> | 7.62<br>-7.62<br>1.94<br>-1.94 | 7.86<br>-7.86<br>2.00<br>-2.00 | 8.09<br>-8.09<br>2.06<br>-2.06 |                       |

| Gain vs. Frequency (transmit and receive) (600 Ω termination; reference 1 kHz²): 200 Hz to 300 Hz 300 Hz to 3.4 kHz 3.4 kHz to 16 kHz 16 kHz to 266 kHz                                                                                                             | -1.00<br>-0.3<br>-3.0<br>      | 0.0<br>0.0<br>-0.1<br>—        | 0.05<br>0.05<br>0.3<br>2.5     | dB<br>dB<br>dB<br>dB  |

| Gain vs. Level (transmit and receive)(reference 0 dBV²): -55 dB to +3 dB                                                                                                                                                                                            | -0.05                          | 0                              | 0.05                           | dB                    |

| 2-Wire Idle-channel Noise (600 $\Omega$ termination):<br>Psophometric <sup>2</sup><br>C-message<br>3 kHz Flat <sup>2</sup>                                                                                                                                          | _<br>_<br>_                    | -87<br>2<br>10                 | -77<br>12<br>20                | dBmp<br>dBrnC<br>dBrn |

| Transmit Idle-channel Noise: Psophometric <sup>2</sup> C-message 3 kHz Flat <sup>2</sup>                                                                                                                                                                            | _<br>_<br>_                    | -82<br>7<br>15                 | -77<br>12<br>20                | dBmp<br>dBrnC<br>dBrn |

<sup>1.</sup> With a first-generation codec, this parameter is set by external components. Any complex impedance R1 + R2  $\parallel$  C between 150  $\Omega$  and 1300  $\Omega$  can be synthesized. With a third-generation codec, this parameter is set by a codec or by a combination of a codec and an external network

<sup>2.</sup> This parameter is not tested in production. It is guaranteed by design and device characterization.

<sup>3.</sup> Use this gain option with an Agere first-generation or third-generation codec.

<sup>4.</sup> Use this gain option with an Agere third-generation codec.

#### **Table 9. Logic Inputs and Outputs**

All outputs are open collectors with internal, 30 k $\Omega$  pull-up resistor. Input pins have internal pull-down or some method to power up in the disconnect state.

| Parameter                                                                                                                                                 | Symbol     | Min         | Тур        | Max        | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|------------|----------|

| Input Voltages: Low Level (permissible range) High Level (permissible range)                                                                              | VIL<br>VIH | -0.5<br>2.0 | 0.4<br>2.4 | 0.7<br>Vcc | V        |

| Input Currents:  Low Level (Vcc = 5.25 V, Vı = 0.4 V)  High Level (Vcc = 5.25 V, Vı = 2.4 V)                                                              | lıL<br>lıн | 0<br>10     | 4<br>24    | 10<br>50   | μΑ<br>μΑ |

| Output Voltages (open collector with internal pull-up resistor): Low Level (Vcc = 4.75 V, lol = 200 $\mu$ A) High Level (Vcc = 4.75 V, loh = -20 $\mu$ A) |            | 0<br>2.4    | 0.2        | 0.4<br>Vcc | V        |

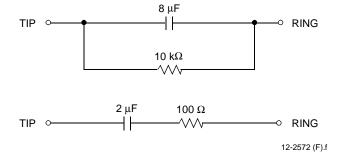

## **Ring Trip Requirements**

- Ringing signal:

- Voltage, minimum 35 Vrms, maximum 100 Vrms.

- Frequency, 17 Hz to 33 Hz.

- Crest factor, 1.2 to 1.6.

- Ring trip:

- ≤100 ms (typical).

- Pretrip:

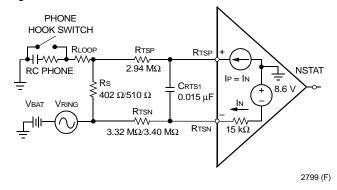

- The circuits in Figure 3 will not cause ring trip.

Figure 3. Ring Trip Circuits

# **Test Configurations**

12-3559 (F).Em

Figure 4. L9217 Basic Test Circuit

Figure 5. Metallic PSRR

Figure 6. Longitudinal PSRR

# **Test Configurations** (continued)

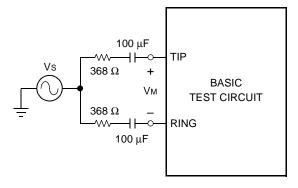

LONGITUDINAL BALANCE =  $20 \log \frac{Vs}{VM}$

12-2584 (F).c

**I**LONG TIP VPT **BASIC TEST CIRCUIT** Vpr **I**LONG RING  $ZLONG = \frac{\Delta VPT}{\Delta ILONG} OR \frac{\Delta VPR}{\Delta ILONG}$

12-2585 (F).a

Figure 7. Longitudinal Balance

5-6756 (F).bm

Vs = 0.5 Vrms 30% AM 1 kHz modulation, f = 500 kHz—1 MHz device in powerup mode, 600  $\Omega$  termination.

Figure 8. RFI Rejection

Figure 9. Longitudinal Impedance

12-2587 (F).e

Figure 10. ac Gains

## **Applications**

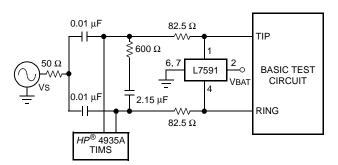

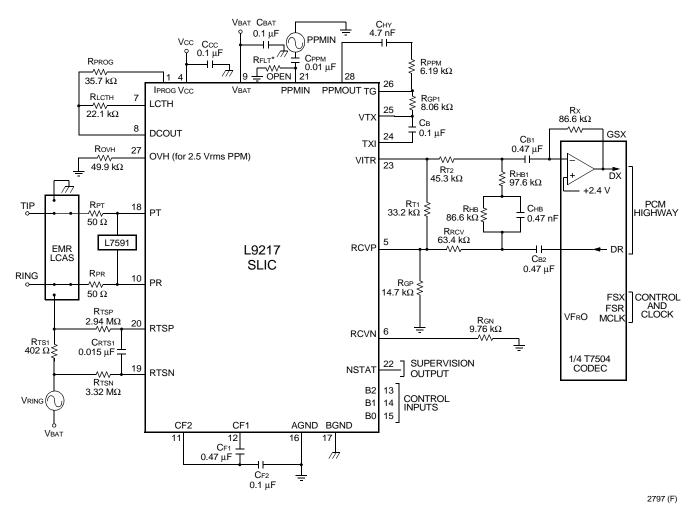

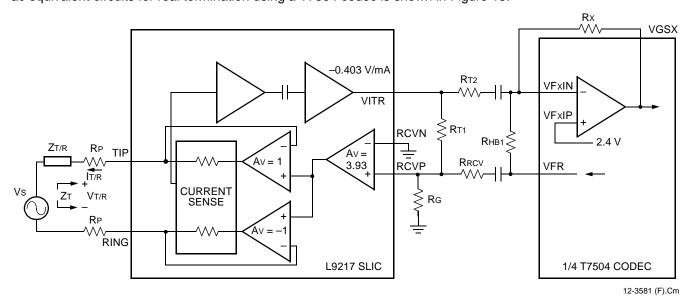

A basic loop start reference circuit, using bused ringing with the L9217 SLIC and the T7504 first-generation codec, is shown in Figure 11. This circuit is designed for a 900  $\Omega$  termination impedance and an 850  $\Omega$  + 50 nF transhybrid. Transmit gain is set at 0 dBm and receive gain is set at –7 dBm.

\* Placeholder for potential resistor to form filter against PPM generator noise if necessary.

Figure 11. Basic Loop Start Application Circuit Using T7504-Type Codec

Table 10 shows the design parameters of the application circuit shown in Figure 11. Components that are adjusted to program these values are also shown.

Table 10. 900  $\Omega$  Termination, 850  $\Omega$  + 50 nF Hybrid First-Generation Codec Design Parameters

| Design Parameter              | Parameter Value | Components Adjusted   |

|-------------------------------|-----------------|-----------------------|

| Loop Closure Threshold        | 10 mA           | Rьстн                 |

| dc Loop Current Limit         | 20 mA           | Rprog                 |

| ac Termination Impedance      | 900 Ω           | Rt1, Rgp, Rrcv, Rgp1  |

| Hybrid Balance Line Impedance | 850 Ω + 50 nF   | Снв, Rнв, Rнв1        |

| Transmit Gain                 | 0 dBm           | RT2, RX, RN1, RN2, CN |

| Receive Gain                  | −7 dBm          | Rrcv, Rgp, Rt1        |

Table 11. Parts List for Loop Start Application Circuit Using T7504-Type Codec

| Name                | Value                  | Function                                            |  |

|---------------------|------------------------|-----------------------------------------------------|--|

| Integrated Circuits |                        |                                                     |  |

| SLIC                | L9217                  | Subscriber loop interface circuit (SLIC).           |  |

| Protector           | Agere L7591            | Secondary protection.                               |  |

| Ringing Relay       | Agere L7581/2/3 or EMR | Switches ringing signals.                           |  |

| Codec               | T7504                  | First-generation codec.                             |  |

| Overvoltage Protect | ion                    |                                                     |  |

| Rрт                 | 50 Ω, Fusible          | Protection resistor.                                |  |

| RPR                 | 50 Ω, Fusible          | Protection resistor.                                |  |

| Power Supply        | •                      |                                                     |  |

| Сват1               | 0.1 μF, 20%, 100 V     | VBAT filter capacitor.                              |  |

| Ccc                 | 0.1 μF, 20%, 10 V      | Vcc filter capacitor.                               |  |

| CF1                 | 0.47 μF, 20%, 100 V    | With CF2, improves idle-channel noise.              |  |

| CF2                 | 0.1 μF, 20%, 100 V     | With C <sub>F1</sub> , improves idle-channel noise. |  |

| dc Characteristics  | ·                      |                                                     |  |

| Rprog               | 35.7 kΩ, 1%, 1/16 W    | Set low current limit.                              |  |

| ac Characteristics  |                        | '                                                   |  |

| Св1                 | 0.47 μF, 20%, 10 V     | ac/dc separation capacitor.                         |  |

| Св2                 | 0.47 μF, 20%, 10 V     | ac/dc separation capacitor.                         |  |

| Св                  | 0.1 μF, 20%, 10 V      | dc blocking capacitor.                              |  |

| R <sub>T1</sub>     | 33.2 kΩ, 1%, 1/16 W    | With RgP and RRCV, sets ac termination impedance.   |  |

| Rrcv                | 63.4 kΩ, 1%, 1/16 W    | With RgP and RT1, sets receive gain.                |  |

| Rgp                 | 14.7 kΩ, 1%, 1/16 W    | With RT1 and RRCV, sets ac termination impedance    |  |

|                     |                        | and receive gain.                                   |  |

| RT2                 | 45.3 kΩ, 1%, 1/16 W    | With Rx, sets transmit gain in codec.               |  |

| Rx                  | 86.6 kΩ, 1%, 1/16 W    | With RT2, sets transmit gain in codec.              |  |

| Rнв1                | 97.6 kΩ, 1%, 1/16 W    | Sets hybrid balance.                                |  |

| Снв                 | 0.47 nF, 10%, 10 V     | With Rgs provides gain shaping for hybrid.          |  |

| Rнв                 | 86.6 kΩ, 1%, 1/16 W    | With CGs provides gain shaping for hybrid.          |  |

| R <sub>GP1</sub>    | 8.06 kΩ, 1%, 1/16 W    | Sets dc transmit gain of SLIC.                      |  |

| Rgn                 | 9.76 kΩ, 1%, 1/16 W    | dc offset.                                          |  |

| Meter Pulse         |                        |                                                     |  |

| Сну                 | 4.7 nF, 20%, 10 V      | Meter pulse rejection.                              |  |

| Сррм                | 0.01 μF, 20%, 10 V     | Meter pulse injection.                              |  |

| <b>R</b> PPM        | 6.19 kΩ, 1%, 1/16 W    | Meter pulse rejection.                              |  |

| Rovн                | 49.9 kΩ, 1%, 1/16 W    | Increases PPM overhead mode.                        |  |

| Supervision         |                        |                                                     |  |

| Rьстн               | 22.1 kΩ, 1%, 1/16 W    | Sets loop closure (off-hook) threshold.             |  |

| RTS1                | 402 Ω, 5%, 2 W         | Ringing source series resistor.                     |  |

| CRTS1               | 0.015 μF, 20%, 10 V    | With RTSN, RTSP, forms filter pole.                 |  |

| Rtsn                | 3.32 MΩ, 1%, 1/16 W    | With RTSP, sets threshold.                          |  |

| RTSP                | 2.94 MΩ, 1%, 1/16 W    | With CRTS1, RTSN, sets threshold.                   |  |

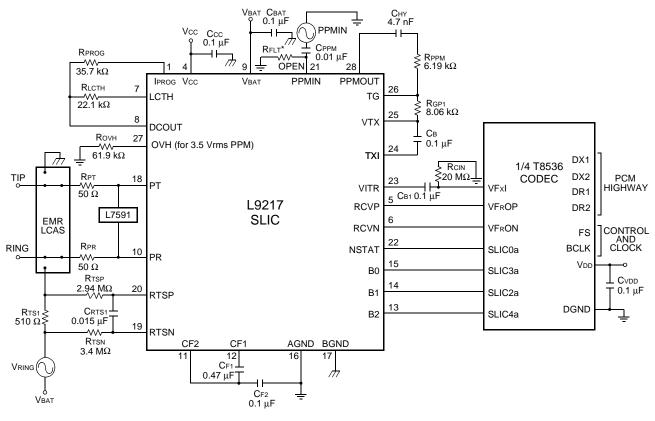

A basic loop start reference circuit, using bused ringing with the L9217 SLIC and the T8536 third-generation codec, is shown in Figure 12.

2798 (F)

\* Placeholder for potential resistor to form filter against PPM generator noise if necessary.

Figure 12. Basic Loop Start Application Circuit Using T8536-Type Codec

Table 12. Parts List for Loop Start Application Circuit Using T8536-Type Codec

| Name                   | Value                  | Function                                            |  |  |

|------------------------|------------------------|-----------------------------------------------------|--|--|

| Integrated Circuits    |                        |                                                     |  |  |

| SLIC                   | L9217                  | Subscriber loop interface circuit (SLIC).           |  |  |

| Protector              | Agere L7591            | Secondary protection.                               |  |  |

| Ringing Relay          | Agere L7581/2/3 or EMR | Switches ringing signals.                           |  |  |

| Codec                  | T8536                  | Third-generation codec.                             |  |  |

| Overvoltage Protection |                        |                                                     |  |  |

| Rрт                    | 50 Ω, Fusible          | Protection resistor.                                |  |  |

| RPR                    | 50 Ω, Fusible          | Protection resistor.                                |  |  |

| Power Supply           |                        |                                                     |  |  |

| Сват1                  | 0.1 μF, 20%, 100 V     | VBAT filter capacitor.                              |  |  |

| Ccc                    | 0.1 μF, 20%, 10 V      | Vcc filter capacitor.                               |  |  |

| CF1                    | 0.47 μF, 20%, 100 V    | With C <sub>F2</sub> , improves idle-channel noise. |  |  |

| CF2                    | 0.1 μF, 20%, 100 V     | With C <sub>F1</sub> , improves idle-channel noise. |  |  |

| dc Characteristics     | •                      | ·                                                   |  |  |

| RPROG                  | 35.7 kΩ, 1%, 1/16 W    | Set low current limit.                              |  |  |

| ac Characteristics     | •                      |                                                     |  |  |

| Св1                    | 0.1 μF, 20%, 10 V      | ac/dc separation capacitor.                         |  |  |

| Св                     | 0.1 μF, 20%, 10 V      | dc blocking capacitor.                              |  |  |

| R <sub>GP1</sub>       | 8.06 kΩ, 1%, 1/16 W    | Sets dc transmit gain of SLIC.                      |  |  |

| Rcin                   | 20 MΩ, 5%, 1/16 W      | dc bias.                                            |  |  |

| Supervision            |                        |                                                     |  |  |

| Rьстн                  | 22.1 kΩ, 1%, 1/16 W    | Sets loop closure (off-hook) threshold.             |  |  |

| RTS1                   | 510 Ω, 5%, 2 W         | Ringing source series resistor.                     |  |  |

| CRTS1                  | 0.015 μF, 20%, 10 V    | With RTSN and RTSP, forms second 2 Hz filter pole.  |  |  |

| Rtsn                   | 3.4 MΩ, 1%, 1/16 W     | With RTSP, sets threshold.                          |  |  |

| RTSP                   | 2.94 MΩ, 1%, 1/16 W    | With RTSN, sets threshold.                          |  |  |

| Meter Pulse            |                        |                                                     |  |  |

| Сну                    | 4.7 nF, 20%, 10 V      | Meter pulse rejection.                              |  |  |

| СРРМ                   | 0.01 μF, 20%, 10 V     | Meter pulse injection.                              |  |  |

| Rррм                   | 6.19 kΩ, 1%, 1/16 W    | Meter pulse rejection.                              |  |  |

| Rovн                   | 61.9 kΩ, 1%, 1/16 W    | Increases PPM overhead mode.                        |  |  |

## dc Applications

#### **Battery Feed**

The dc feed characteristic can be described by:

$$V_{T/R} = \frac{(|V_{BAT}| - V_{OH}) \times R_L}{R_L + 2R_P + R_{dc}}$$

$$I_L = \frac{|V_{BAT}| - V_{OH}}{R_L + 2R_P + R_{dc}}$$

where:

IL = dc loop current.

$V_{T/R} = dc loop voltage.$

|VBAT| = battery voltage magnitude.

Voh = overhead voltage. This is the difference between the battery voltage and the open loop tip/ring voltage.

RL = loop resistance, not including protection resistors.

RP = protection resistor value.

Rdc = SLIC internal dc feed resistance.

12-3050 (F).i

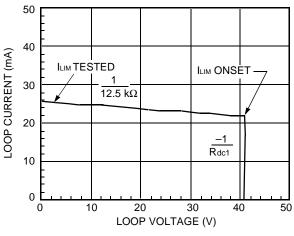

Note: VBAT = -48 V; ILIM = 22 mA; Rdc1 = 115  $\Omega$ .

Figure 13. Loop Current vs. Loop Voltage

Starting from the on-hook condition and going through to a short circuit, the curve passes through the following two regions:

Region 1: On-hook and low-loop currents. The slope corresponds to the dc resistance of the SLIC,  $R_{\text{dc1}}$  (default is 72  $\Omega$  typical). The open circuit voltage is the battery voltage minus the overhead voltage of the device, VoH (default is 6.5 V typical). These values are suitable for most applications but can be adjusted if needed.

Region 2: Current limit. The dc current is limited to a starting value determined by external resistor Rprog, an internal current source, and the gain from tip/ring to pin VITR. Current limit with a 100  $\Omega$  load is set by the following equation:

0.637 RPROG (k $\Omega$ ) + 2 mA = ILIM x (mA)

#### **Overhead Voltage**

In order to drive an on-hook ac signal, the SLIC must set up the tip and ring voltage to a value less than the battery voltage. The amount that the open loop voltage is decreased relative to the battery is referred to as the overhead voltage. This is expressed as the following equation:

$$VOH = |VBAT| - (VPT - VPR)$$

Without this buffer voltage, amplifier saturation will occur and the signal will be clipped. In modes without PPM, the L9217 is set to allow undistorted on-hook transmission of a 3.17 dBm signal into a 900  $\Omega$  loop impedance. A minimum 11.1 V overhead is needed to pass 3.5 Vrms meter pulse.

In high overhead and PPM modes, overhead is automatically increased to accommodate on-hook transmission of meter pulse signals. The increase in overhead is set by a resistor from pin OVH to ground. This is expressed as the following equation:

Vovh (V) =

$$6.37 + 0.09535 \times \text{Rovh} (k\Omega)$$

#### dc Applications (continued)

#### Rate of Battery Reversal

The rate of battery reversal is controlled or ramped by capacitors FB1 and FB2. A chart showing FB1/FB2 values versus typical ramp rate is given below. Leave FB1/FB2 open if it is not desired to ramp the rate of battery reversal.

Table 13. FB1/FB2 Values vs. Typical Ramp Time

| CFB1/CFB2 | Transition<br>Time | CFB1/CFB2 | Transition<br>Time |

|-----------|--------------------|-----------|--------------------|

| 0.01 μF   | 20 ms              | 1.22 μF   | 2.25 s             |

| 0.1 μF    | 220 ms             | 1.3 μF    | 2.5 s              |

| 0.22 μF   | 440 ms             | 1.4 μF    | 2.7 s              |

| 0.47 μF   | 900 ms             | 1.6 μF    | 3.2 s              |

| 1.0 μF    | 1.8 s              |           |                    |

#### **Loop Range**

The equation below can be rearranged to provide the loop range for a required loop current:

$$RL = \frac{|V_{BAT}| - V_{OH}}{I_{I}} - 2R_{P} - R_{DC}$$

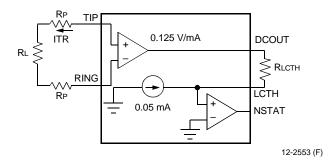

#### **Off-Hook Detection**

The loop closure detection threshold is set by resistor RLCTH. The supervision output bit NSTAT is high in an on-hook condition. The off-hook comparator goes low during an off-hook condition:

ITR (mA) =

$$0.4167 \text{ RLCTH } (k\Omega) - 1.9 \text{ mA ACTIVE}$$

off-hook to on-hook

ITR (mA) =

$$0.4167 \text{ RLCTH } (k\Omega) + 2.7 \text{ mA SCAN}$$

on-hook to off-hook

Figure 14. Off-Hook Detection Circuit

#### **Ring Trip Detection**

The ring trip circuit is a comparator that has a special input section optimized for this application. The equivalent circuit is shown in Figure 15, along with its use in an application using unbalanced, battery-backed ringing.

Figure 15. Ring Trip Equivalent Circuit and Equivalent Application

Ring trip detection threshold is given by the following equation:

ITH

$$(mA) =$$

$$\frac{[\mathsf{RTSN}(\mathsf{M}\Omega) + 0.015 - \mathsf{RTSP}(\mathsf{M}\Omega)] \times [|\mathsf{VBAT}| - 8.6] \times 1000}{[\mathsf{RTSN}(\mathsf{M}\Omega) + 0.015] \times \mathsf{RS}}$$

The ring trip detector requires bias at either the RTSN or RTSP input. This bias is typically derived from the presence of the actual ring generator or the dc battery backing of the ring generator. If no bias is present at RTSN or RTSP the ring trip detector will indicate an off-hook condition, regardless of the state of the subscriber loop. The ring trip detector is active only during forward and reverse battery active states, so this condition will not be seen if the SLIC is in scan or disconnect modes.

If for some reason there are periods of time when the ring generator is not active, this false loop closure indication can be avoided by using an 18  $M\Omega$  pulldown from the talk battery to RTSP.

#### **Longitudinal Balance**

The SLIC is graded to certain longitudinal balance specifications. The numbers are guaranteed by testing (Figure 5 and Figure 8). However, for specific applications, the longitudinal balance may also be determined by termination impedance, protection resistance, and especially by the mismatch between protection resistors at tip and ring. This can be illustrated by the following equation:

$$LB = 20 \times log \frac{(368 + RP) \times (368 + ZT - RP)}{368 \times (2 \times [ZT - 2 \times RP] \times \Delta + \epsilon)}$$

where:

LB: longitudinal balance.

RP: protection resistor value in  $\Omega$ .

ZT: magnitude of the termination impedance in  $\Omega$ .

$\epsilon$ : protection resistor mismatch in  $\Omega$ .

Δ: SLIC internal tip/ring sensing mismatch.

The  $\Delta$  can be calculated using the above equation with these exceptions:  $\varepsilon = 0$ ,  $ZT = 600 \Omega$ ,  $RP = 100 \Omega$ , and the longitudinal balance specification on a specific code.

Now with  $\Delta$  available, the equation will predict the actual longitudinal balance for RP, ZT, and  $\epsilon$ .

Be aware that ZT may vary with frequency for complex impedance applications.

## **Periodic Pulse Metering (PPM)**

Periodic pulse metering (PPM), also referred to as TTX, is input to the PPMIN input of the L9217. Upon application of appropriate logic control, this signal is presented to the tip/ring subscriber loop. The state of the L9217 may be changed while applying PPM signals. The L9217 assumes that a shaped PPM signal is applied to the PPMIN input.

Sufficient drive current is available in the tip and ring drive amplifiers to support 3.5 Vrms PPM signals into a 200  $\Omega$  load with a 45 mA dc current limit.

PPM signals are input to a separate PPMIN input. This input is controlled via the logic table. PPMIN is off during all states except the forward/reverse PPM active state. Thus, PPM signals may be present at all times, even during non-PPM active times. To apply PPM to tip/ring, from a normal overhead state first switch to a high overhead state without PPM; the overhead voltage at tip/ring will increase to 7 V to 13 V. The ramp up time of the overhead increase is on the order of hundreds of milliseconds. Thus, wait 1 s before applying the PPM signal by going to a PPM active high overhead state. Once in a high overhead, there is no timing requirement in switching in and out of a PPM active mode. Without the initial 1 s delay, AT/AR will get into saturation and PPM signal at T/R will get distorted, producing crosstalk in the handset.

PPM input signals may be a maximum 0.525 Vrms at PPMIN. The gain from PPMIN tip/ring is 10. Thus, for 2.5 Vrms at tip and ring, apply a 0.375 Vrms signal at PPMIN. The PPM signal should be ac coupled to PPMIN through a 0.01  $\mu$ F capacitor.

When applied to tip and ring, the PPM signal will also be returned through the SLIC and will appear at the SLIC VITR output. The concern is that this high-voltage signal can overload the codec input and cause distortion of the (desired) ac signal. Therefore, some sort of PPM rejection scheme must be employed, see Figure 1. The L9217 outputs on the PPMOUT pin, which is the output of the PPM input amplifier. Connecting a resistor, RPPM, from PPMOUT to node TG will provide a path for a hybrid reject of the returned meter pulse signal. The return path from tip and ring to VITR for the PPM signal is through the internal AX amplifier. TG is the input to this amplifier. Through RPPM, by applying a PPM signal equal in magnitude, but 180 degrees out of phase to the returned PPM signal at TG, the PPM signal is cancelled, preventing overload at the codec input. Even if the cancellation is not perfect, the idea is to reduce the PPM signal so as not to overload the codec. Codecs typically have a low-pass filter at their input to reject any residual meter pulse signal.

The value of RPPM is selected by:

$RPPM = [{(VPPMIN x 10)/(RPPMLOAD + RDC + 2RP)}/201.2]^{-1}$

For undistorted transmission of meter pulse signals, increase the overhead as described in the Overhead Voltage section of this data sheet.

#### ac Design

#### **Codec Types**

At this point in the design, the codec needs to be selected. The interface network between the SLIC and codec can then be designed. There are four key ac design parameters. Termination impedance is the impedance looking into the 2-wire port of the line card. It is set to match the impedance of the telephone loop in order to minimize echo return to the telephone set. Transmit gain is measured from the 2-wire port to the PCM highway, while receive gain is done from the PCM highway to the transmit port. Finally, the hybrid balance network cancels the unwanted amount of the receive signal that appears at the transmit port.

Below is a brief codec feature summary.

**First-Generation Codecs.** These perform the basic filtering, A/D (transmit), D/A (receive), and  $\mu$ -law/A-law companding. They all have an op amp in front of the A/D converter for transmit gain setting and hybrid balance (cancellation at the summing node). Depending on the type, some have differential analog input stages, differential analog output stages, 5 V only or  $\pm 5$  V operation, and  $\mu$ -law/A-law selectability. These are available in single and quad designs. This type of codec requires continuous time analog filtering via external resistor/capacitor networks to set the ac design parameters. An example of this type of codec is the Agere T7504 quad 5 V only codec.

This type of codec tends to be the most economical in terms of piece part price, but tends to require more external components than a third-generation codec. Furthermore, ac parameters are fixed by the external R/C network, so software control of ac parameters is difficult.

**Third-Generation Codecs.** This class of devices includes all ac parameters set digitally under microprocessor control. Depending on the device, it may or may not have data control latches. Additional functionality sometimes offered includes tone plant generation and reception, TTX generation, test algorithms, and echo cancellation. Again, this type of codec may be 5 V only or  $\pm 5$  V operation, single quad or 16-channel, and  $\mu$ -law/A-law or 16-bit linear coding selectable. Examples of this type of codec are the Agere T8535/6 (5 V only, quad, standard features), T8533/4 (5 V only, quad with echo cancellation), and the T8531/36 (5 V only 16-channel with self-test).

#### ac Interface Network

The ac interface network between the L9217 and the codec will vary depending on the codec selected. With a first-generation codec, the interface between the L9217 and codec actually sets the ac parameters. With a third-generation codec, all ac parameters are set digitally, internal to the codec; thus, the interface between the L9217 and this type of codec is designed to avoid overload at the codec input in the transmit direction, and to optimize signal-to-noise ratio (S/N) in the receive direction.

#### **Receive Interface**

Because the design requirements are very different with a first- or third-generation codec, the L9217 is offered with two different receive gains. Each receive gain was chosen to optimize, in terms of external components required, the ac interface between the L9217 and the codec.

With a first-generation codec, the termination impedance is set by providing gain shaping through a feedback network from the SLIC VITR output to the SLIC RCVN/RCVP inputs. The L9217 provides a transconductance from T/R to VITR in the transmit direction and a single ended to differential gain in the receive direction from either RCVN or RCVP to T/R. Assuming a short from VITR to RCVN or RCVP, the maximum impedance that is seen looking into the SLIC is the product of the SLIC transconductance times the SLIC receive gain, plus the protection resistors. The various specified termination impedance can range over the voice band as low as 300  $\Omega$  up to over 1000  $\Omega$ . Thus, if the SLIC gains are too low, it will be impossible to synthesize the higher termination impedances. Furthermore, the termination that is achieved will be far less than what is calculated by assuming a short for SLIC output to SLIC input. In the receive direction, in order to control echo, the gain is typically a loss, which requires a loss network at the SLIC RCVN/RCVP inputs, which will reduce the amount of gain that is available for termination impedance. For this reason a high-gain SLIC is required with a first-generation codec.

#### ac Design (continued)

#### Receive Interface (continued)

With a third-generation codec, the line card designer has different concerns. To design the ac interface, the designer must first decide upon all termination impedance, hybrid balances, and transmission level points (TLP) requirements that the line card must meet. In the transmit direction, the only concern is that the SLIC does not provide a signal that is too hot and overloads the codec input. Thus, for the highest TLP that is being designed to, given the SLIC gain, the designer, as a function of voice band frequency, must ensure that the codec is not overloaded. With a given TLP and a given SLIC gain (if the signal will cause a codec overload), the designer must insert some sort of loss, typically a resistor divider, between the SLIC output and codec input.

In the receive direction, the issue is to optimize S/N. Again, the designer must consider all the considered TLPs. The idea is, for all desired TLPs, to run the codec at or as close as possible to its maximum output signal, to optimize the S/N. Remember noise floor is constant, so the hotter the signal from the codec, the better the

S/N. The problem is, if the codec is feeding a high-gain SLIC, either an external resistor divider is needed to knock the gain down to meet the TLP requirements, or the codec is not operating near maximum signal levels, thus compromising the S/N.

It appears the solution is to have a SLIC with a low gain, especially in the receive direction. This will allow the codec to operate near its maximum output signal (to optimize S/N), without an external resistor divider (to minimize cost).

Note also that some third-generation codecs require the designer to provide an inherent resistive termination via external networks. The codec will then provide gain shaping, as a function of frequency to meet the return loss requirements. Further stability issues may add external components or excessive ground plane requirements to the design.

To meet the unique requirements of both types of codecs, the L9217 offers two receive gain choices. These receive gains are mask programmable at the factory and are offered as two different code variations. For interface with a first-generation codec, the L9217A is offered with a receive gain of 7.86. For interface with a third-generation codec, the L9217G is offered with a receive gain of 2. In either case, the transconductance in the transmit direction, or the transmit gain is 403  $\Omega$ .

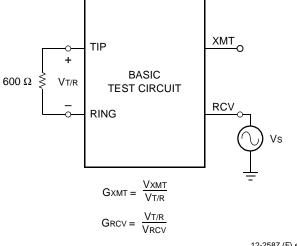

#### **Example 1: Real Termination (First-Generation Codec)**

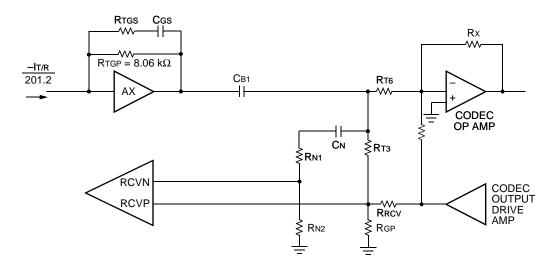

ac equivalent circuits for real termination using a T7504 codec is shown in Figure 15.

Figure 16. ac Equivalent Circuit

ac Design (continued)

#### Example 1: Real Termination (First-Generation Codec) (continued)

The following design equations refer to the circuit in Figure 16. Use these to synthesize real termination impedance.

#### **Termination Impedance:**

$$\mathsf{ZT} = \frac{\mathsf{VT/R}}{-\mathsf{IT/R}}$$

$$ZT = 2RP + \frac{3168}{1 + \frac{RT3}{RGP} + \frac{RT3}{RRCV}}$$

#### **Receive Gain:**

$$g_{rcv} = \frac{V_{T/R}}{V_{fr}}$$

$$g_{\text{rcv}} = \frac{7.86}{\left(1 + \frac{R_{\text{RCV}}}{R_{\text{T3}}} + \frac{R_{\text{RCV}}}{R_{\text{GP}}}\right)\left(1 + \frac{Z_{\text{T}}}{Z_{\text{T/R}}}\right)}$$

#### **Transmit Gain:**

$$g_{tx} = \frac{V_{GSX}}{V_{T/R}}$$

$$g_{tx} = \frac{Rx}{R_{T6}} x \frac{403}{Z_T}$$

#### **Hybrid Balance:**

$$h_{bal} = 20log \frac{V_{GSX}}{V_{T/R}}$$

To optimize the hybrid balance, the sum of the currents at the VFX input of the codec op amp should be set to 0. The following expressions assume the test network is the same as the termination impedance:

$$RHB = \frac{Rx}{gtx \times grcv}$$

$$h_{bal} = 20log \ \left(\frac{Rx}{R_{HB}} - g_{tx} \times g_{rcv}\right)$$

#### ac Design (continued)

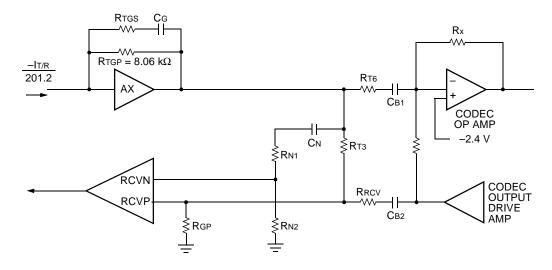

#### **Example 2: Complex Termination (First-Generation Codec)**

Below are design equations for complex termination (see Figure 17 and Figure 18).

$$R_{T1} = 2R_P + \frac{7.86}{201.2} \bullet \left( \frac{1}{1 + \frac{R_{T3}}{R_{GP}} + \frac{R_{T3}}{R_{RCV}}} - \frac{1}{1 + \frac{R_{N1}}{R_{N2}}} \right) R_{TGP} \parallel R_{TGS}$$

$$R_{T2} = \frac{7.86}{201.2} + \left( \frac{R_{TGP}/R_{TGS}}{1 + \frac{R_{T3}}{R_{GP}} + \frac{R_{T3}}{R_{RCV}}} + \frac{1}{1 + \frac{R_{N1}}{R_{N2}}} \right) R_{TGP} || R_{TGS}$$

$$\frac{1}{C \text{T}} = \frac{7.86}{201.2} \left( \frac{1}{C \text{N1}} \frac{R \text{N2}}{(R \text{N1} + R \text{N2})^2} R \text{TGP} \parallel R \text{TGS} + \frac{1}{C \text{TG}} \bullet \left( \frac{R \text{TGP}}{R \text{TGP} + R \text{TGS}} \right)^2 \bullet \left( \frac{1}{1 + \frac{R \text{T3}}{R \text{GP}} + \frac{R \text{T3}}{R \text{RCV}}} - \frac{1}{1 + \frac{R \text{N1}}{R \text{N2}}} \right) \right)$$

$$g_{tx} = \frac{Rx}{R_{T6}} \frac{1}{201.2} \frac{Z_{TG}}{Z_{T}}$$

$$grcv = \frac{7.86}{1 + \frac{RRCV}{RT3} + \frac{RRCV}{RGP}} \times \frac{1}{1 + \frac{ZT}{ZT/R}}$$

$$h_{bal} = 20log \; \left( \frac{Rx}{R_{HB}} - g_{tx} \times g_{rcv} \right)$$

where:

$$Z_{T/R} = R_1 + R_2 \parallel C$$

$$ZTG = RTGP || (RTGS + CG)$$

$$\mathsf{RTGP} = 8.06 \; \mathsf{k}\Omega$$

$$RTGS = \frac{R_1}{R_2} RTGP$$

$$C_G = \frac{R_2^2}{R_{TGP}(R_1 + R_2)} \times C$$

and

$$C_NR_{N2} = \frac{2R_P}{3167} C_G R_{TGP}$$

$$R_{N1} = R_{N2} \left[ \frac{3167}{2R_P} \left( \frac{R_{TGS}}{R_{TGP}} \right) - 1 \right]$$

The equations above do not include the blocking capacitors.

## ac Design (continued)

#### **Example 2: Complex Termination (First-Generation Codec)** (continued)

5-6401 (F).I

Figure 17. Interface Circuit Using First-Generation Codec (±5 V Codec)

5-6400 (F).o

Figure 18. Interface Circuit Using First-Generation Codec (5 V Only Codec)

## **Power Derating**

Operating temperature range, maximum current limit, maximum battery voltage, minimum dc loop, and protection resistor values will influence the overall thermal performance. This section shows the relevant design equations and considerations in evaluating the SLIC thermal performance.

Consider the L9217 SLIC in a 28-pin PLCC package. The thermal resistance on a 2-layer board with natural convection is 43 °C/W.

The SLIC will enter the thermal shutdown state at a minimum of 150 °C. The thermal shutdown design should ensure that the SLIC temperature does not reach 150 °C under normal operating conditions.

Assume a maximum ambient operating temperature of 85 °C, a design current limit of 25 mA, and a maximum battery of –52 V. Furthermore, assume a (worst-case) minimum dc loop of 200  $\Omega$ , and that 50  $\Omega$  protection resistors are used at both tip and ring.

1. TTSD - TAMBIENT(max) = allowed thermal rise.

$$150 \, ^{\circ}\text{C} - 85 \, ^{\circ}\text{C} = 65 \, ^{\circ}\text{C}$$

2. Allowed thermal rise = package thermal impedance ● SLIC power dissipation.

65 °C = 43 °C/W ● SLIC power dissipation

SLIC power dissipation (PDISS) = 1.51 W

Thus, if the total power dissipated in the SLIC is less than 1.51 W, it will not enter the thermal shutdown state. Total SLIC power is calculated as:

Total Poiss = Maximum battery ● maximum current limit (including effects of accuracy)

+ SLIC quiescent power

For the L9217, SLIC quiescent power (Pq) is maximum at 0.175 W. Thus,

Total PDISS =  $(-52 \text{ V} \bullet [25 \text{ mA} \bullet 1.08]) + 0.175 \text{ W}$

Total PDISS = 1.404 W + 0.175 W

Total PDISS = 1.579 W

The power dissipated in the SLIC is the total power dissipation minus the power that is dissipated in the loop.

SLIC PDISS = Total power – loop power Loop power =  $(ILIM)^2 \bullet (RdcLOOP min + 2RP)$  Loop power =  $(25 \text{ mA} \cdot 1.08)^2 \cdot (200 \Omega + 100 \Omega)$

Loop power = 0.219 W

SLIC power = 1.579 W - 0.219 W = 1.36

SLIC power = 1.36 W < 1.51 W

Thus, in this example, the thermal design ensures that the SLIC will not enter the thermal shutdown state.

## Pin-for-Pin Compatibility with L9218/L9219

The L9217 can be a pin-for-pin replacement for the L9218/L9219. The exceptions are as follows: L9217 has three logic control inputs: B0, B1, and B2. The L9218 has only two logic control inputs: B0 and B1. Pin 13 in L9218 is NC, so a connection between the controller and pin 13 will not affect L9218 operation. In L9217, pin 28 is PPMOUT, pin 21 is PPMIN, and pin 27 is OVH. In L9218/9, pin 28 is NC, pin 21 is NC, and pin 27 is TSD

## **PCB Layout Information**

Make the leads to BGND and VBAT as wide as possible for thermal and electrical reasons. Also, maximize the amount of PCB copper in the area of (and specifically on) the leads connected to this device for the lowest operating temperature.

When powering the device, make certain that no external potential creates a voltage on any pin of the device that exceeds the device ratings. In this application, some of the conditions that cause such potentials during powerup are the following:

- 1. An inductor connected to PT and PR (this can force an overvoltage on VBAT through the protection devices if the VBAT connection chatters).

- Inductance in the VBAT lead (this could resonate with the VBAT filter capacitor to cause a destructive overvoltage).

This device is normally used on a circuit card that is subjected to hot plug-in, meaning the card is plugged into a biased backplane connector. In order to prevent damage to the IC, all ground connections must be applied before, and removed after, all other connections.

# **Outline Diagram**

## 28-Pin PLCC

Dimensions are in millimeters.

5-2506 (F) r.8

## **Ordering Information**

| Device         | Package                                               | Comcode   |

|----------------|-------------------------------------------------------|-----------|

| LUCL9217AAR-DT | 28-Pin PLCC<br>(Tape & Reel, Dry-bagged)<br>Gain of 8 | 108760737 |

| LUCL9217AAR-D  | 28-Pin PLCC<br>(Dry-bagged)<br>Gain of 8              | 108760729 |

| LUCL9217GAR-DT | 28-Pin PLCC<br>(Tape & Reel, Dry-bagged)<br>Gain of 2 | 108760760 |

| LUCL9217GAR-D  | 28-Pin PLCC<br>(Dry-bagged)<br>Gain of 2              | 108760752 |

*IEEE* is a registered trademark of The Institute of Electrical and Electronics Engineers, Inc. *HP* is a registered trademark of Hewlett-Packard Company.

For additional information, contact your Agere Systems Account Manager or the following:

INTERNET: http://www.agere.com docmaster@agere.com