# T7504 and T5504 Quad PCM Codecs with Filters

#### **Features**

- +5 V only

- Low-power, latch-up-free CMOS technology

- 37 mW/channel typical operating power dissipation

- 1 mW/channel typical powerdown dissipation

- Automatic master clock frequency selection

2.048 MHz or 4.096 MHz

- On-chip sample and hold, autozero, and precision voltage reference

- Differential architecture for high noise immunity and power supply rejection

- Flexible time-slotted PCM interface

2.048 MHz or 4.096 MHz data rate

- Meets or exceeds D3/D4 (as per AT&T PUB43801) and CCITT G.711—G.714 requirements

- Operating temperature range: -40 °C to +85 °C

- μ-law/A-law companding selectable

## **Description**

The T7504 and T5504 devices are single-chip, four-channel  $\mu$ -law/A-law PCM codecs with filters. These integrated circuits provide analog-to-digital and digital-to-analog conversion. They provide the transmit and receive filtering necessary to interface a voice telephone circuit to a time-division multiplexed system. These devices are packaged in both 28-pin DIPs and 28-pin PLCCs.

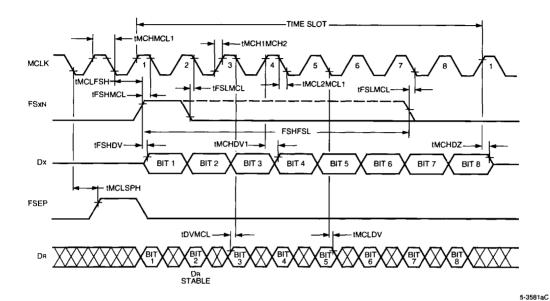

The T5504 differs from the T7504 in its timing mode. The T5504 operates in the nondelay timing mode (digital data valid when frame sync goes high), and the T7504 operates in the delayed timing mode (digital data is valid one clock cycle after frame sync goes high) (see Figures 5—8).

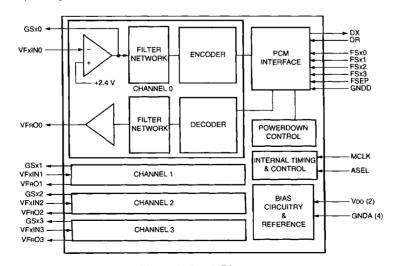

Figure 1. Block Diagram

5-3579C

### **Functional Description**

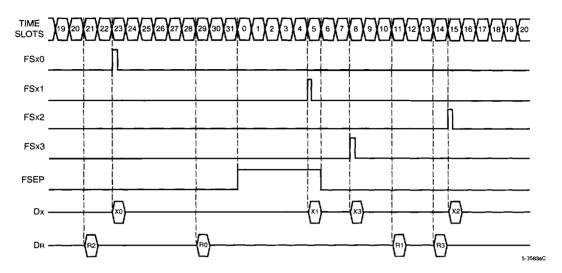

Four channels of PCM data input and output are passed through only two ports. Dx and DR, so some type of time-slot assignment is necessary. The scheme used here is to utilize timing modes of 32 or 64 time slots corresponding to master clock frequencies of either 2.048 MHz or 4.096 MHz, respectively. Each device has four transmit frame sync (FSx) inputs, one for each channel. During a single 125 us frame, each transmit frame sync input is supplied a single pulse. The timing of the pulse indicates the beginning of the time slot during which the data for that channel is clocked out of the device. During a frame, transmit frame sync pulses must be separated from each other by one or more time slots. A channel is placed in a standby (low-power) mode if its FSx input has been low for 500 us.

There is a single frame sync separation input (FSEP). The number of negative clock edges minus one that occur while FSEP is high is the delay (in clock periods) that is placed between the rising edge of a transmit frame sign bit and the falling edge used by the receiver to sample the sign bit. There must always be a pulse on the FSEP input since this input provides the 8 kHz signal required to maintain internal timing. If the FSEP pulse is one clock period or less, the device makes the transmit edges and receive sampling edges one half clock period apart. The entire device is placed in a powerdown mode if FSEP remains low for 500 µs.

Time slot zero is defined as starting on the first rising MCLK edge after FSEP = "1" is detected by a negative MCLK edge. In the T7504, MCLK negative-going edges that detect the start of FSEP and FSxN must be

integer multiples of eight MCLK periods apart (zero multiples are allowed). Since FSEP is assumed to define time slot 0, the number of multiples separating FSxN and FSEP is the time-slot number. In the T5504, FSxN for time slot 0 nominally starts on the MCLK positive edge following the negative edge which detects FSEP

The frequency of the master clock must be either 2.048 MHz or 4.096 MHz. Internal circuitry determines the master clock frequency during the powerup reset interval.

Powerdown is not guaranteed if MCLK is lost unless the device is already in the powerdown mode due to FSEP low for at least  $500 \mu s$ .

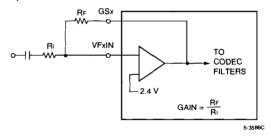

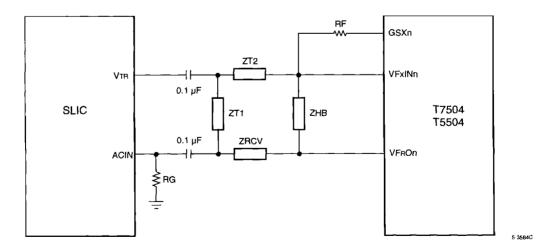

The analog input section in Figure 2 includes an onchip op amp that is used in conjunction with external, user-supplied resistors to vary encoder passband gain. The load impedance to ground at the GSx outputs should be greater than  $10~\mathrm{k}\Omega$  in parallel with less than 50 pF. The input signal at VFxIN should be ac coupled. For best performance, the maximum gain of this op amp should be limited to 20 dB or less.

Figure 2. Typical Analog Input Section

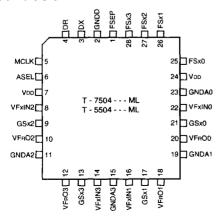

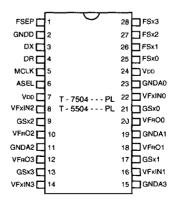

#### Pin Information

5-3580B

Figure 3. Pin Diagrams

## Pin Information

**Table 1. Pin Descriptions**

| Symbol                               | Pin                  | Type* | Name/Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VFxIN3<br>VFxIN2<br>VFxIN1<br>VFxIN0 | 14<br>8<br>16<br>22  | ı     | Voice Frequency Transmitter Input. Analog inverting input to the uncommitted operational amplifier at the transmit filter input. Connect the signal to be digitized to this pin through a resistor Ri (see Figure 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GSx3<br>GSx2<br>GSx1<br>GSx0         | 13<br>9<br>17<br>21  | 0     | Gain Set for Transmitter. Output of the transmit uncommitted operational amplifier.  The pin is the input to the transmit differential filters. Connect the pin to its corresponding VFxIN through a resistor RF (see Figure 2).                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| VFRO3<br>VFRO2<br>VFRO1<br>VFRO0     | 12<br>10<br>18<br>20 | 0     | Voice Frequency Receiver Output. This pin can drive 2000 $\Omega$ (or greater) loads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Voo [1:0]                            | 7, 24                | . }   | +5 V Analog Power Supplies. Both pins must be connected on the circuit board. Each pin should be bypassed to ground with at least 0.1 $\mu$ F of capacitance as close to the device as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| GNDA3<br>GNDA2<br>GNDA1<br>GNDA0     | 15<br>11<br>19<br>23 |       | Analog Grounds. All ground pins must be connected on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DR                                   | 4                    | -     | Receive PCM Data Input. The data on this pin is shifted into the device on the falling edges of MCLK. Data is only entered for valid time slots as defined by the relationship of the pulses on the FSx inputs and the pulse on the FSEP input.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Dx                                   | 3                    | 0     | <b>Transmit PCM Data Output</b> . This pin remains in the high-impedance state except during active transmit time slots. An active transmit time slot is defined as one in which a pulse is present on one of the FSx inputs. Data is shifted out on the rising edge of MCLK.                                                                                                                                                                                                                                                                                                                                                                                                          |

| MCLK                                 | 5                    | I     | Master Clock Input. The frequency must be 2.048 MHz or 4.096 MHz. This clock serves as the bit clock for all PCM data transfer. A 40% to 60% duty cycle is required.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GNDD                                 | 2                    |       | <b>Digital Ground.</b> Ground connection for the digital circuitry. All ground pins must be connected on the circuit board.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| FSx3<br>FSx2<br>FSx1<br>FSx0         | 28<br>27<br>26<br>25 | lq    | Transmit Frame Sync. This signal is an edge trigger and must be high for a minimum of one MCLK cycle. This signal must be derived from MCLK. The division ratio is 1:256 or 1:512 (FSx:MCLK). Each FSx input must have a pulse present at the start of the desired active output time slot. Pulses on the various FSx inputs must be separated by one or more integer multiples of time slots. An internal pull-down device is included on each FSx.                                                                                                                                                                                                                                   |

| ASEL                                 | 6                    | lq    | <b>A-Law/</b> μ- <b>Law Select</b> . A logic low selects $\mu$ -law coding. A logic high selects A-law coding. A pull-down device is included.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FSEP                                 | 1                    | 1     | Frame Sync Separation. The pulse width of this 8 kHz signal defines the timing offset between the transmit and receive frames. Internally generated receive frame sync pulses are delayed from the corresponding transmit frame sync pulse rising edge by one less than the FSEP pulse width in negative MCLK edges. If the pulse width is one MCLK period or less, the transmit and receive frame sync are made coincident. Loss of FSEP causes the device to powerdown. If the master clock frequency is 2.048 MHz or 4.096 MHz, delays of 255 or 511 clock pulses are not allowed, respectively. Timing relationships between FSEP, FSxN, and time slot 0 are given in Figures 5—8. |

<sup>\*</sup> I<sup>d</sup> A pull-down device is included on this lead.

AT&T Microelectronics 6-33

## **Absolute Maximum Ratings**

Stresses in excess of the Absolute Maximum Ratings can cause permanent damage to the device. These are absolute stress ratings only. Functional operation of the device is not implied at these or any other conditions in excess of those given in the operational sections of this data sheet. Exposure to Absolute Maximum Ratings for extended periods can adversely affect device reliability.

| Parameter                                 | Symbol | Min  | Max       | Units |

|-------------------------------------------|--------|------|-----------|-------|

| Storage Temperature Range                 | Tstg   | -55  | 150       | °C    |

| Power Supply Voltage                      | Voo    |      | 6.5       | V     |

| Voltage on Any Pin with Respect to Ground | _      | ~0.5 | 0.5 + VDD | V     |

| Maximum Power Dissipation (package limit) | Poiss  | -    | 600       | mW    |

## **Handling Precautions**

Although protection circuitry has been designed into this device, proper precautions should be taken to avoid exposure to electrostatic discharge (ESD) during handling and mounting. AT&T employs a human-body model (HBM) and a charged-device model (CDM) for ESD susceptibility testing and protection design evaluation. ESD voltage thresholds are dependent on the circuit parameters used to define the model. No industry-wide standard has been adopted for CDM. However, a standard HBM (resistance = 1500  $\Omega$ , capacitance = 100 pF) is widely used and therefore can be used for comparison purposes. The HBM ESD threshold presented here was obtained by using these circuit parameters.

| HBM ESD Threshold Voltage |         |  |  |  |  |  |  |

|---------------------------|---------|--|--|--|--|--|--|

| Device                    | Rating  |  |  |  |  |  |  |

| T7504                     | >2000 V |  |  |  |  |  |  |

| T5504                     | >2000 V |  |  |  |  |  |  |

#### **Electrical Characteristics**

Specifications apply for Ta = -40 °C to + 85 °C, Vdd = 5 V  $\pm$  5%, MCLK = either 2.048 MHz or 4.096 MHz, and GND = 0 V, unless otherwise noted.

#### dc Characteristics

Table 2. Digital Interface

| Parameter                              | Symbol | Test Conditions                   | Min | Тур | Max | Units |

|----------------------------------------|--------|-----------------------------------|-----|-----|-----|-------|

| Input Low Voltage                      | VIL    | All digital inputs                |     | 1   | 0.8 | V     |

| Input High Voltage                     | ViH    | All digital inputs                | 2.0 | -   |     | V     |

| Output Low Voltage                     | Vol    | Dx, IL = 3.2 mA                   | _   | 1   | 0.4 | ٧     |

| Output High Voltage                    | Voн    | Dx, IL = -3.2 mA                  | 2.4 | _   |     | V     |

|                                        |        | Dx, IL = -320 μA                  | 3.5 |     | _   | V     |

| Input Current, Pins without Pull-down  | lı lı  | Any digital input GND < VIN < VDD | -10 | -   | 10  | μΑ    |

| Input Current, Pins with Pull-down     | lı .   | Any digital input GND < VIN < VDD |     | -   | 150 | μA    |

| Output Current in High-impedance State | loz    | Dx                                | -30 | _   | 30  | μА    |

| Input Capacitance                      | Cı     | _                                 | _   | _   | 5   | pF    |

# **Electrical Characteristics** (continued)

#### dc Characteristics

#### **Table 3. Power Dissipation**

Power measurements are made at MCLK = 4.096 MHz, outputs unloaded.

| Parameter         | Symbol | Test Conditions                              | Min | Тур | Max | Units |

|-------------------|--------|----------------------------------------------|-----|-----|-----|-------|

| Powerdown Current | IDDO   | MCLK present, FSx[3:0] = 0.4 V, FSEP = 0.4 V | -   | 0.2 | 1   | mA    |

| Powerup Current   | IDD1   | MCLK, FSx[3:0], FSEP present                 |     | 30  | 50  | mA    |

| Standby Current   | loos   | MCLK, FSEP present; FSx[3:0] = 0.4 V         |     | 6   | 10  | mA    |

## **Transmission Characteristics**

Table 4. Analog Interface

| Parameter                               | Symbol | Test Conditions                                       | Min  | Тур | Max   | Units |

|-----------------------------------------|--------|-------------------------------------------------------|------|-----|-------|-------|

| Input Resistance, VFxIN                 | Rvfxi  | 0.25 V < VFxI < 4.75 V                                | 1.0  | _   | _     | МΩ    |

| Input Leakage Current, VFxIN            | İBVFXI | 0.25 V < VFxI < 4.75 V                                | _    |     | 2.4   | μÁ    |

| dc Open-loop Voltage Gain, GSx          | Avol   |                                                       | 5000 | _   | _     | _     |

| Open-loop Unity Gain Bandwidth, GSx     | fo     |                                                       | 1    | 3   | 1     | MHz   |

| Load Capacitance, GSx                   | CLx1   | <del>-</del>                                          | _    | _   | 50    | pF    |

| Load Resistance, GSx                    | RLx1   |                                                       | 10   | _   |       | kΩ    |

| Input Voltage, VFxIN                    | Vix    | Relative to ground                                    | 2.3  | 2.4 | 2.5   | ٧     |

| Load Resistance, VFRO                   | RLvfro |                                                       | 2000 | _   | -     | Ω     |

| Load Capacitance, VFnO                  | CLvFro |                                                       | _    |     | 100   | pF    |

| Output Resistance, VFnO                 | ROvFro | 0 dBm0, 1020 Hz PCM code<br>applied to Dn             | -    | _   | 20    | Ω     |

|                                         |        | Partial powerdown FSx = "0" for<br>channel under test | 3000 | _   | 10000 | Ω     |

| Output Voltage, VFnO                    | Vor    | Alternating ± zero μ-law PCM code applied to DR       | 2.3  | 2.4 | 2.5   | · V   |

| Output Voltage, VFRO, Standby           | VORPD  | FSx[3:0] = 0.4 V, FSEP = active,<br>no load           | 2.15 | 2.4 | 2.65  | ν     |

| Output Leakage Current, VFnO, Powerdown | IOVFRO | FSEP = 0.4 V                                          | -30  |     | 30    | μА    |

| Output Voltage Swing, VFRO              | Vswn   | RL = 2000 Ω                                           | 3.2  | _   | _     | VPP   |

#### ac Transmission Characteristics

Unless otherwise noted, the analog input is a 0 dBm0, 1020 Hz sine wave; the input amplifier is set for unity gain. The digital input is a PCM bit stream equivalent to that obtained by passing a 0 dBm0, 1020 Hz sine wave through an ideal encoder. The output level is  $\sin(x)/x$ -corrected.

Table 5. Absolute Gain

| Parameter                                             | Symbol | Test Conditions                                                                        |       | Тур | Max  | Units |

|-------------------------------------------------------|--------|----------------------------------------------------------------------------------------|-------|-----|------|-------|

| Encoder Milliwatt Response (transmit gain tolerance)  | EmW    | Signal input of 0.775 Vrms, μ-law or A-<br>law                                         | -0.25 | _   | 0.25 | dBm0  |

| Decoder Milliwatt Response (receive gain toler- ance) | DmW    | Measured relative to 0.775 Vrms μ-law or A-law, PCM input of 0 dBm0 1020 Hz RL = 10 kΩ | -0.25 |     | 0.25 | dBm0  |

#### Table 6. Gain Tracking

| Parameter                                                    | Symbol | Test Conditions                             | Min            | Тур | Max          | Units    |

|--------------------------------------------------------------|--------|---------------------------------------------|----------------|-----|--------------|----------|

| Transmit Gain Tracking Error<br>Sinusoidal Input μ-Law/A-Law | GTx    | +3 dBm0 to -37 dBm0<br>-37 dBm0 to -50 dBm0 | -0.25<br>-0.50 |     | 0.25<br>0.50 | dB<br>dB |

| Receive Gain Tracking Error<br>Sinusoidal Input µ-Law/A-Law  | GTR    | +3 dBm0 to -37 dBm0<br>-37 dBm0 to -50 dBm0 | -0.25<br>-0.50 |     | 0.25<br>0.50 | dB<br>dB |

Table 7. Distortion

| Parameter                                | Symbol | Test Conditions                                                                 | Min | Тур | Max             | Units |

|------------------------------------------|--------|---------------------------------------------------------------------------------|-----|-----|-----------------|-------|

| Transmit Signal to Distortion            | SDx    | $\mu$ -law 3 dBm0 $\leq$ VFxI $\leq$ -30 dBm0                                   | 36  | -   | _               | dB    |

|                                          |        | A-law 3 dBm0 $\leq$ VFx1 $\leq$ -30 dBm0                                        | 35  | 1   |                 | dB    |

|                                          |        | $\mu$ -law -30 dBm0 $\leq$ VFxI $\leq$ -40 dBm0                                 | 30  | _   |                 | dB    |

|                                          |        | A-law -30 dBm0 ≤ VFxl ≤ -40 dBm0                                                | 29  |     |                 | dB_   |

|                                          |        | $\mu$ -law40 dBm0 $\leq$ VFxI $\leq$ -45 dBm0                                   | 25  | _   |                 | dB    |

|                                          |        | A-law $-40 \text{ dBm0} \le VFxI \le -45 \text{ dBm0}$                          | 25  | _   | _               | dB    |

| Receive Signal to Distortion             | SDR    | $\mu$ -law 3 dBm0 $\leq$ VFRO $\leq$ -30 dBm0                                   | 36  |     |                 | dB    |

|                                          |        | A-law 3 dBm0 $\leq$ VFnO $\leq$ -30 dBm0                                        | 35  | - ' | _               | dB    |

|                                          |        | $\mu$ -law $-30 \text{ dBm}0 \le VF_RO \le -40 \text{ dBm}0$                    | 30  | -   | -               | dB    |

|                                          |        | A-law $-30 \text{ dBm}0 \le \text{VF}_{R}O \le -40 \text{ dBm}0$                | 29  | _   | _               | dB    |

|                                          |        | μ-law –40 dBm0 ≤ VFnO ≤ –45 dBm0                                                | 25  | 1   | _               | dB    |

|                                          |        | A-law40 dBm0 $\leq$ VFrO $\leq$ 45 dBm0                                         | 25  | _   | _               | dB    |

| Single Frequency Distortion,<br>Transmit | SFDx   | 200 Hz—3400 Hz, 0 dBm0 input,<br>output any other single<br>frequency ≤ 3400 Hz | -   |     | -38             | dBm0  |

| Single Frequency Distortion,<br>Receive  | SFDR   | 200 Hz—3400 Hz, 0 dBm0 input,<br>output any other single<br>frequency ≤ 3400 Hz |     | _   | <del>-4</del> 0 | dBm0  |

| Intermodulation Distortion               | IMD    | Transmit or receive, two frequencies in the range (300 Hz—3400 Hz) at -6 dBm0   |     | _   | <del>-4</del> 2 | dBm0  |

6-36 AT&T Microelectronics

### ac Transmission Characteristics (continued)

**Table 8. Envelope Delay Distortion**

| Parameter                     | Symbol | Test Conditions                                                  | Min      | Тур | Max        | Units |

|-------------------------------|--------|------------------------------------------------------------------|----------|-----|------------|-------|

| Tx Delay, Absolute*           | Dxa    | f = 1600 Hz                                                      |          | _   | 175 to 425 | μs    |

| Tx Delay, Relative to 1600 Hz | DxR    | f = 500 Hz—600 Hz                                                | _        | _   | 220        | μs    |

| ·                             |        | f = 600 Hz800 Hz                                                 |          | _   | 145        | μs    |

|                               |        | f = 800 Hz—1000 Hz                                               | -        | _   | 75         | μs    |

| 1                             |        | $f \approx 1000 \text{ Hz} - 1600 \text{ Hz}$                    | _        | _   | 40         | μs    |

|                               |        | f ≈ 1600 Hz2600 Hz                                               |          | _   | 75         | μs    |

|                               | 1      | f = 2600 Hz—2800 Hz                                              | _        |     | 105        | μs    |

|                               | L      | f ≈ 2800 Hz—3000 Hz                                              | _        |     | 155        | μs    |

| Rx Delay, Absolute*           | DRA    | f = 1600 Hz                                                      | _        |     | 150 to 405 | μs    |

| Rx Delay, Relative to 1600 Hz | DRR    | f = 500 Hz1000 Hz                                                | -40      |     | _          | μs    |

|                               |        | f = 1000  Hz - 1600  Hz                                          | -30      | -   | l —        | μs    |

|                               |        | f = 1600 Hz-2600 Hz                                              | - 1      | _   | 90         | μs    |

|                               |        | f ≈ 2600 Hz—2800 Hz                                              | <u> </u> | _   | 125        | μs    |

| i                             | ,      | f ≈ 2800 Hz—3000 Hz                                              |          |     | 175        | μs    |

| Round Trip Delay, Absolute*   | DRTA   | Any time slot/channel to<br>any time slot/channel<br>f = 1600 Hz |          | _   | 325 to 650 | μs    |

<sup>\*</sup> Varies as a function of time slots chosen.

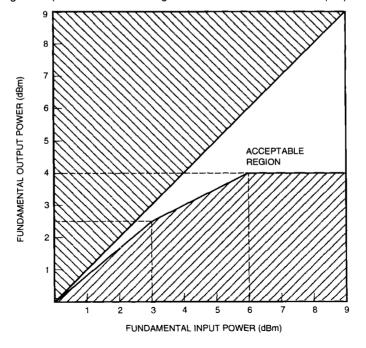

#### **Overload Compression**

Figure 4 shows the region of operation for encoder signal levels above the reference input power (0 dBm0).

Figure 4. Overload Compression

6-37

5-35**86**C

## ac Transmission Characteristics (continued)

Table 9. Noise

| Parameter                                              | Symbol | Test Conditions                                                                                                 | Min            | Тур   | Max               | Units          |

|--------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------|----------------|-------|-------------------|----------------|

| Transmit Noise                                         | Nxc    |                                                                                                                 |                |       | 18                | dBrnC0         |

| μ-Law                                                  |        | Input amplifier gain = 20 dB                                                                                    |                |       | 19                | dBrnC0         |

| Transmit Noise<br>A-Law                                | Nxp    | _                                                                                                               | -              |       | -68               | dBm0p          |

| Receive Noise<br>μ-Law                                 | NRC    | PCM code is alternating positive and negative zero                                                              | _              | -     | 13                | dBrnC0         |

| Receive Noise<br>A-Law                                 | NRP    | PCM code is A-law positive one                                                                                  | _              | 1     | -75               | dBm0p          |

| Noise, Single Frequency<br>f = 0 kHz—100 kHz           | Nas    | VFxIN = 0 Vrms, measurement at VFRO, DR = Dx                                                                    | _              | 1     | -53               | dBm0           |

| Power Supply Rejection Transmit                        | PSRx   | VDD = 5.0 V <sub>dc</sub> + 100 mVrms:<br>f = 0 kHz—4 kHz<br>f = 4 kHz—50 kHz                                   | 36<br>30       |       | -                 | dB<br>dB       |

| Power Supply Rejection Receive                         | PSRx   | PCM code is positive one LSB.  VDD = 5.0 Vdc + 100 mVrms:  f = 0 kHz—4 kHz  f = 4 kHz—25 kHz  f = 25 kHz—50 kHz | 36<br>40<br>30 | 1 1 1 |                   | dB<br>dB<br>dB |

| Spurious Out-of-Band Signals at VFnO Relative to Input | SOS    | 0 dBm0, 300 Hz—3400 Hz input<br>PCM code applied:<br>4600 Hz—7600 Hz<br>7600 Hz—8400 Hz<br>8400 Hz—50 kHz       | -              |       | -30<br>-40<br>-30 | dB<br>dB<br>dB |

Table 10. Receive Gain Relative to Gain at 1.02 kHz

| Frequency (Hz) | Min    | Тур   | Max   | Unit |

|----------------|--------|-------|-------|------|

| Below 3000     | -0.150 | ±0.04 | 0.150 | dB   |

| 3140           | -0.570 | ±0.04 | 0.150 | dB   |

| 3380           | -0.885 | -0.58 | 0.010 | dB   |

| 3860           | _      | -10.7 | -9.4  | dB   |

| 4600 and above |        |       | -28   | dB   |

Table 11. Transmit Gain Relative to Gain at 1.02 kHz

| Frequency (Hz) | Min    | Тур   | Max   | Unit |

|----------------|--------|-------|-------|------|

| 16.67          | _      | -50   | -30   | dB   |

| 40             |        | -34   | -26   | dB   |

| 50             | _      | -36   | -30   | dB   |

| 60             |        | -50   | -30   | dB   |

| 200            | -1.8   | -0.5  | . 0   | dB   |

| 300 to 3000    | -0.150 | ±0.04 | 0.150 | dB   |

| 3140           | -0.570 | ±0.04 | 0.150 | dB   |

| 3380           | -0.885 | -0.58 | 0.010 | dB   |

| 3860           |        | -10.7 | -9.4  | dB   |

| 4600 and above | _      |       | -32   | dB   |

### ac Transmission Characteristics (continued)

Table 12. Interchannel Crosstalk (Between Channels) R<sub>F</sub> = ≤ 200 kΩ (See Note.)

| Parameter                                                        | Symbol              | Test Conditions                                                                                                     | Min         | Тур | Max             | Units |

|------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------|-------------|-----|-----------------|-------|

| Transmit to Receive<br>Crosstalk 0 dBm0<br>Transmit Levels       | CTxx-ry             | f = 300 Hz—3400 Hz<br>idle PCM code for channel under test;<br>0 dBm0 into any other single channel VFxIN           | _           | _   | <del>-</del> 75 | dΒ    |

| Receive to Transmit<br>Crosstalk 0 dBm0<br>Receive Levels        | CTRX-XY             | f = 300 Hz—3400 Hz VFxIN = 0 Vrms for channel under test; 0 dBm0 code level on any other single channel Da          |             | 1   | -75             | dB    |

| Transmit to Trans-<br>mit Crosstalk 0<br>dBm0 Transmit<br>Levels | СТхх-хү             | f = 300 Hz—3400 Hz 0 dBm0 applied to any single channel VFxIN except channel under test, which has VFxIN = 0 Vrms   | <del></del> |     | -75             | d₿    |

| Receive to Receive<br>Crosstalk 0 dBm0<br>Receive Levels         | CT <sub>RX-RY</sub> | f = 300 Hz—3400 Hz 0 dBm0 code level on any single channel Dn except channel under test which has idle code applied |             |     | <b>−</b> 75     | dB    |

Table 13. Intrachannel Crosstalk (Within Channels) RF =  $\leq$  200 k $\Omega$  (See Note.)

| Parameter                                                  | Symbol              | Test Conditions                                                                         | Min | Тур | Max            | Units |

|------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------|-----|-----|----------------|-------|

| Transmit to Receive<br>Crosstalk 0 dBm0<br>Transmit Levels | CTxx-nx             | f = 300 Hz—3400 Hz<br>idle PCM code for channel under test;<br>0 dBm0 into VFxIN        |     |     | <del>-65</del> | dB    |

| Receive to Transmit<br>Crosstalk 0 dBm0<br>Receive Levels  | CT <sub>RX-XX</sub> | f = 300 Hz—3400 Hz<br>VFxIN = 0 Vrms for channel under test;<br>0 dBm0 code level on Da |     |     | -65            | dB    |

Note: For Tables 12 and 13, crosstalk into the transmit channels (VFxIN) can be significantly affected by parasitic capacitive feeds from GSx and VFxO outputs. PWB layouts should be arranged to keep these parasitics low. The resistor value of RF (from GSx to VFxIN) should also be kept as low as possible (while maintaining the load on GSx above 10 kΩ per Table 4) to minimize crosstalk.

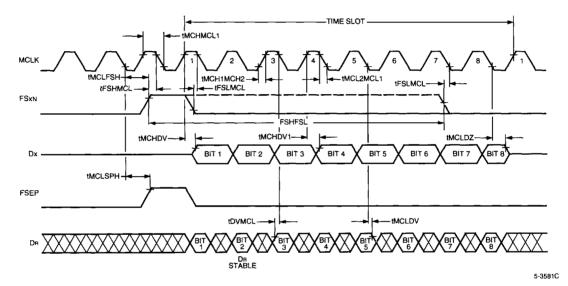

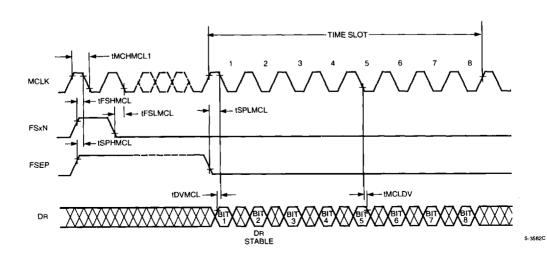

# **Timing Characteristics**

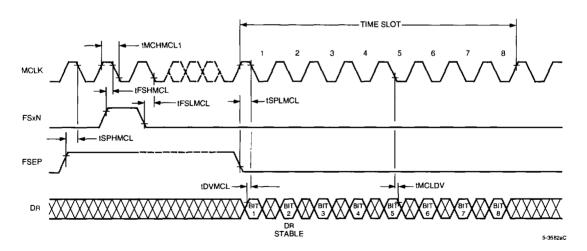

Table 14. Clock Section (See Figures 5, 6, 7, and 8.)

| Symbol                 | Parameter                   | Test Conditions | Min | Тур | Max | Units |

|------------------------|-----------------------------|-----------------|-----|-----|-----|-------|

| tMCHMCL1               | Clock Pulse Width           | -               | 97  |     |     | ns    |

| tCDC                   | Duty Cycle, MC              | _               | 40  | _   | 60  | %     |

| tMCH1MCH2<br>tMCL2MCL1 | Clock Rise and<br>Fall Time | -               | 0   |     | 15  | ns    |

Table 15. T7504 Transmit Section (See Figure 5.)

| Symbol  | Parameter                | Test Conditions    | Min | Тур | Max           | Units |

|---------|--------------------------|--------------------|-----|-----|---------------|-------|

| tMCHDV  | Data Enabled on TS Entry | 0 < CLOAD < 100 pF | 0   | _   | 60            | ns    |

| tMCHDV1 | Data Delay from MC       | 0 < CLOAD < 100 pF | 0   |     | 60            | ns    |

| tMCLDZ* | Data Float on TS Exit    | CLOAD = 0          | 10  |     | 100           | ns    |

| tFSHMCL | Frame-sync Hold Time     |                    | 50  | _   | _             | ns    |

| tMCLFSH | Frame-sync High Setup    | -                  | 50  |     | _             | ns    |

| tFSLMCL | Frame-sync Low Setup     |                    | 50  |     | _             | ns    |

| tFSHFSL | Frame-sync Pulse Width   | _                  | 0.1 |     | 125 – tMCHMCH | μs    |

<sup>\*</sup> Timing parameter tMCLDZ is referenced to a high-impedance state.

Table 16. T5504 Transmit Section (See Figure 7.)

| Symbol  | Parameter                | Test Conditions    | Min | Тур | Max           | Units |

|---------|--------------------------|--------------------|-----|-----|---------------|-------|

| tFSHDV  | Data Enabled on TS Entry | 0 < CLOAD < 100 pF | 0   |     | 80            | ns    |

| tMCHDV1 | Data Delay from FSx      | 0 < CLOAD < 100 pF | 0   |     | 60            | пѕ    |

| tMCHDZ* | Data Float on TS Exit    | CLOAD = 0          | 0   |     | 30            | ns    |

| tFSHMCL | Frame-sync Hold Time     |                    | 50  |     | _             | ns    |

| tMCLFSH | Frame-sync High Setup    |                    | 50  |     |               | ns    |

| tFSLMCL | Frame-sync Low Setup     | <del></del>        | 50  |     |               | ns    |

| tFSHFSL | Frame-sync Pulse Width   | _                  | 0.1 |     | 125 – tMCHMCH | μs    |

<sup>\*</sup> Timing parameter tMCHDZ is referenced to a high-impedance state.

6-40 AT&T Microelectronics

# Timing Characteristics (continued)

Table 17. T7504 and T5504 Receive Section (See Figures 5, 6, 7, and 8.)

| Symbol  | Parameter                   | Test Conditions | Min | Тур | Max | Units |

|---------|-----------------------------|-----------------|-----|-----|-----|-------|

| tDVMCL  | Receive Data Setup          |                 | 30  |     | _   | ns    |

| tMCLDV  | Receive Data Hold           |                 | 15  | _   | _   | ns    |

| tFSHMCL | Frame Separation Hold Time  |                 | 50  |     |     | ns    |

| tMCLSPH | Frame Separation High Setup |                 | 50  | _   | _   | ns    |

| tFSLMCL | Frame Separation Low Setup  | _               | 50  |     | _   | ns    |

Figure 5. T7504 Transmit & Receive Timing, FSEP = 1 MCLK

Figure 6. T7504 Receive Timing, FSEP > 1 MCLK

# Timing Characteristics (continued)

Figure 7. T5504 Transmit & Receive Timing, FSEP = 1 MCLK

Figure 8. T5504 Receive Timing, FSEP > 1 MCLK

# Timing Characteristics (continued)

Figure 9. Typical Frame Sync Timing (2 MHz operation)

# **Applications**

Figure 10. Typical T7504 and T5504/SLIC Interconnection

AT&T Microelectronics 6-43

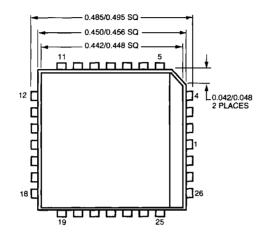

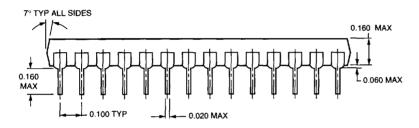

# **Outline Diagrams**

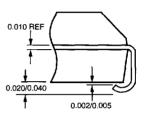

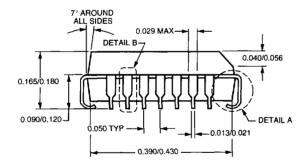

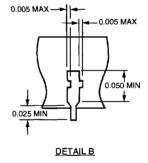

#### 28-Pin PLCC

Controlling dimensions are in inches.

DETAIL A

5-2608C

6-44 AT&T Microelectronics

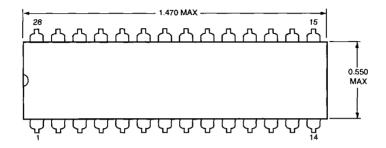

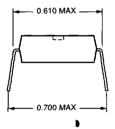

# **Outline Diagrams** (continued)

### 28-Pin DIP

Controlling dimensions are in inches.

5-2650C