# STK14CB16 256K x 16 AutoStore<sup>™</sup> nvSRAM QuantumTrap<sup>™</sup> CMOS Nonvolatile Static RAM

**Advanced Information**

#### **FEATURES**

- 25ns Access Time

- "Hands-off" Automatic *STORE* on Power Down with only a small capacitor

- STORE to QuantumTrap<sup>™</sup> Nonvolatile Elements is Initiated by Software , device pin or AutoStore<sup>™</sup> on Power Down

- *RECALL* to SRAM Initiated by Software or Power Up

- Unlimited READ, WRITE and RECALL Cycles

- 10mA Typical Icc at 200ns Cycle Time

- 500,000 STORE Cycles to QuantumTrap<sup>™</sup>

- 100-Year Data Retention to QuantumTrap™

- Single 3V +20%, -10% Operation

- Commercial and Industrial Temperatures

- SSOP and TSOP II packages

- RoHS Compliance

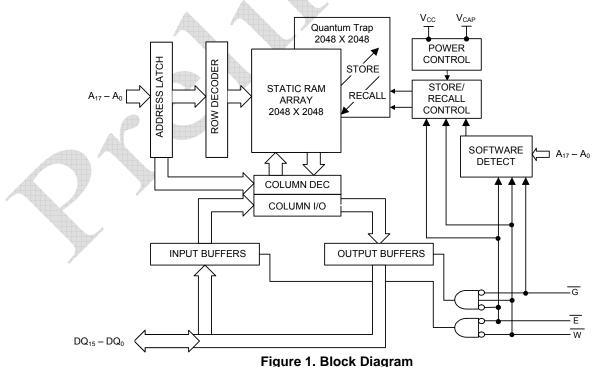

#### **BLOCK DIAGRAM**

#### DESCRIPTION

The Simtek STK14CB16 is a fast static RAM with a nonvolatile element in each memory cell. The embedded nonvolatile elements incorporate Simtek's *QuantumTrap*<sup>TM</sup> technology producing the world's most reliable nonvolatile memory. The SRAM provides unlimited read and write cycles, while independent, nonvolatile data resides in the highly reliable *QuantumTrap*<sup>TM</sup> cell. Data transfers from the SRAM to the nonvolatile elements (the *STORE* operation) takes place automatically at power down. On power up, data is restored to the SRAM (the *RECALL* operation) from the nonvolatile memory. Both the *STORE* and *RECALL* operations are also available under software control.

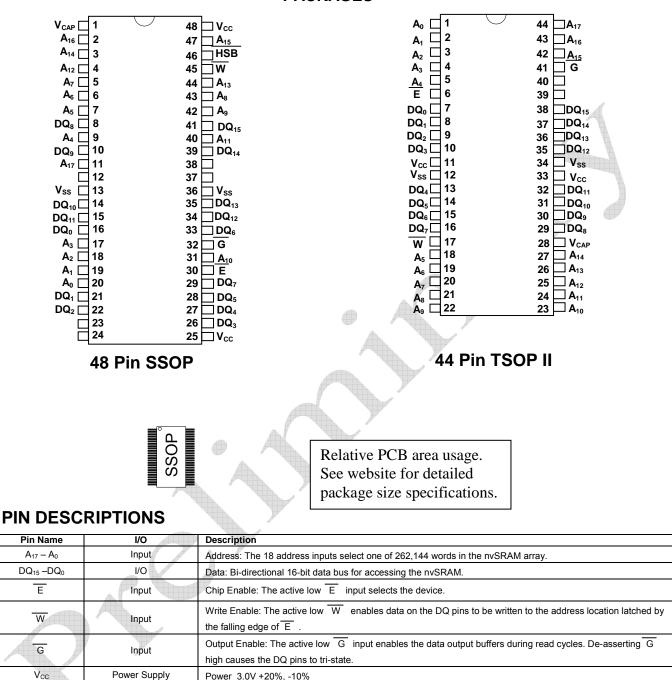

PACKAGES

HSB

VCAP

$V_{SS}$

(Blank)

I/O

Power Supply

Power Supply

No Connect

connected. (Connection Optional)

Unlabeled pins have no internal connection.

elements

Ground

Hardware Store Busy: When low this output indicates a Hardware Store is in progress. When pulled low external

to the chip it will initiate a nonvolatile STORE operation. A weak internal pull up resistor keeps this pin high if not

Autostore Capacitor: Supplies power to nvSRAM during power loss to store data from SRAM to nonvolatile

### **ABSOLUTE MAXIMUM RATINGS**<sup>a</sup>

Power Supply Voltage -0.5V to +4.1V Voltage on Input Relative to V<sub>SS</sub> -0.5V to (V<sub>CC</sub> + 0.5V) Voltage on Outputs -0.5V to ( $V_{CC}$  + 0.5V) Temperature under Bias –55°C to 125°C Junction Temperature –55°C to 140°C Storage Temperature -65°C to 150°C Power Dissipation 1W DC Output Current (1 output at a time, 1s duration) 15mA

Notes

a: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

Package Thermal Characteristics see website: <u>http://www.simtek.com/</u>

| DC CHARACTERISTICS |

|--------------------|

|--------------------|

|                  |                                                                        | Comr           | nercial               | Indu           | strial                |                |                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------|----------------|-----------------------|----------------|-----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                                                              | MIN            | MAX                   | MIN            | MAX                   | Units          | Notes                                                                                                                                                                                                                                  |

| I <sub>CC1</sub> | Average V <sub>cc</sub> Current                                        |                | 55<br>45<br>30        |                | 60<br>50<br>45        | mA<br>mA<br>mA | $t_{AVAV}$ = 25ns<br>$t_{AVAV}$ = 35ns<br>$t_{AVAV}$ = 45ns<br>Dependent on output loading and cycle<br>rate. Values obtained without output loads.                                                                                    |

| I <sub>CC2</sub> | Average $V_{cc}$ Current during STORE                                  |                | 2                     |                | 2                     | mA             | All Inputs Don't Care, $V_{CC}$ = max<br>Average current for duration of STORE<br>cycle ( $t_{STORE}$ ).                                                                                                                               |

|                  | Average $V_{CC}$ Current at $t_{AVAV}$ = 200ns                         |                |                       |                |                       |                | $\overline{W} \ge (V_{CC} - 0.2V)$                                                                                                                                                                                                     |

| I <sub>CC3</sub> | 3V, 25°C, Typical                                                      |                | 10                    |                | 10                    | mA             | All Others Inputs Cycling, at CMOS Levels.<br>Dependent on output loading and cycle<br>rate. Values obtained without output loads.                                                                                                     |

| I <sub>CC4</sub> | Average V <sub>CAP</sub> Current during<br><i>AutoStore</i> ™ Cycle    |                | 2                     |                | 2                     | mA             | All Inputs Don't Care<br>Average current for duration of STORE<br>cycle (t <sub>STORE</sub> ).                                                                                                                                         |

| I <sub>SB</sub>  | V <sub>CC</sub> Standby Current<br>(Standby, Stable CMOS Input Levels) |                | 3                     |                | 3                     | mA             | $\label{eq:constraint} \begin{array}{ c c } \overline{E} \geq (V_{CC}-0.2V) \\ \mbox{All Others $V_{IN} \leq 0.2V$ or $\geq (V_{CC}-0.2V)$ \\ \mbox{Standby current level after nonvolatile} \\ \mbox{cycle is complete.} \end{array}$ |

| I <sub>ILK</sub> | Input Leakage Current                                                  |                | ±1                    |                | ±1                    | μA             | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                                                                        |

| I <sub>olk</sub> | Off-State Output Leakage Current                                       |                | ±1                    |                | ±1                    | μA             | $\begin{array}{c} V_{\text{IN}} = V_{\text{SS}} \text{ to } V_{\text{CC}} \\ \hline V_{\text{CC}} = \max \\ V_{\text{IN}} = V_{\text{SS}} \text{ to } V_{\text{CC}},  \hline E  \text{or }  \hline G  \ge V_{\text{IH}} \end{array}$   |

| VIH              | Input Logic "1" Voltage                                                | 2.0            | V <sub>CC</sub> + 0.3 | 2.0            | V <sub>CC</sub> + 0.3 | V              | All Inputs                                                                                                                                                                                                                             |

| VIL              | Input Logic "0" Voltage                                                | $V_{SS} - 0.5$ | 0.8                   | $V_{SS} - 0.5$ | 0.8                   | V              | All Inputs                                                                                                                                                                                                                             |

| V <sub>OH</sub>  | Output Logic "1" Voltage                                               | 2.4            |                       | 2.4            |                       | V              | $I_{OUT} = -2mA$                                                                                                                                                                                                                       |

| V <sub>OL</sub>  | Output Logic "0" Voltage                                               |                | 0.4                   |                | 0.4                   | V              | I <sub>OUT</sub> = 4mA                                                                                                                                                                                                                 |

| T <sub>A</sub>   | Operating Temperature                                                  | 0              | 70                    | -40            | 85                    | °C             |                                                                                                                                                                                                                                        |

| V <sub>cc</sub>  | Operating Voltage                                                      | 2.7            | 3.6                   | 2.7            | 3.6                   | V              | 3.0V +20%, -10%                                                                                                                                                                                                                        |

| VCAP             | Storage Capacitor                                                      | 44             | 100                   | 44             | 100                   | μF             | Between Vcap pin and Vss, 5V rated.                                                                                                                                                                                                    |

### STK14CB16

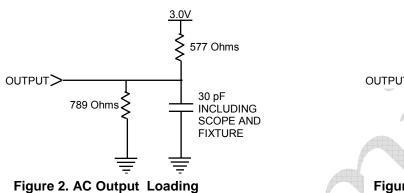

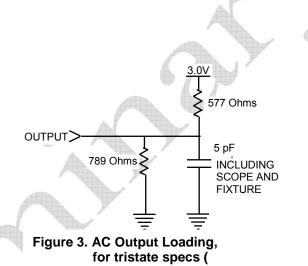

#### AC TEST CONDITIONS

| Inp | ut Pulse Levels                                  |                  | 0V to 3V     |

|-----|--------------------------------------------------|------------------|--------------|

| Inp | ut Rise and Fall Times<br>ut and Output Timing R |                  | ≤ 5ns        |

| Inp | ut and Output Timing F                           | Reference Levels | 1.5V         |

| Ou  | tput Load                                        | See Figure 2     | and Figure 3 |

###

000

| l | SYMBOL | PARAMETER          | MAX | UNITS | CONDITIONS             |

|---|--------|--------------------|-----|-------|------------------------|

|   | CIN    | Input Capacitance  | 7   | pF    | $\Delta V = 0$ to $3V$ |

|   | COUT   | Output Capacitance | 7   | pF    | $\Delta V = 0$ to $3V$ |

Notes

b: These parameters are guaranteed but not tested

-igure 3. AC Output Loading, for tristate specs ( t<sub>HZ</sub>, t<sub>LZ</sub>, t<sub>WLQZ</sub>, t<sub>WHQZ</sub>, t<sub>GLQX</sub>, t<sub>GHQZ</sub>)

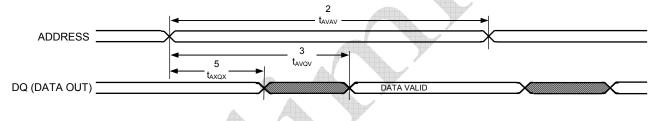

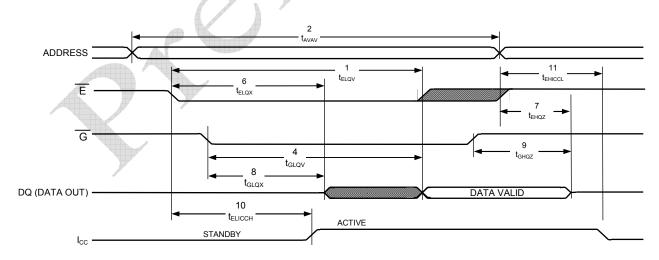

#### SRAM READ CYCLES #1 & #2

| NO. | SYMBOLS                        |                                 | SYMBOLS PARAMETER |                                   |  |  |     | STK140 | UNITS |        |

|-----|--------------------------------|---------------------------------|-------------------|-----------------------------------|--|--|-----|--------|-------|--------|

|     | #1                             | #2                              | Alt.              |                                   |  |  |     | MIN    | MAX   | •••••• |

| 1   |                                | t <sub>ELQV</sub>               | t <sub>ACS</sub>  | Chip Enable Access Time           |  |  |     |        | 25    | ns     |

| 2   | t <sub>avav</sub> c            | t <sub>AVAV</sub> c             | t <sub>RC</sub>   | Read Cycle Time                   |  |  |     | 25     |       | ns     |

| 3   | $t_{\text{AVQV}}{}^{\text{d}}$ |                                 | t <sub>AA</sub>   | Address Access Time               |  |  |     |        | 25    | ns     |

| 4   |                                | t <sub>GLQV</sub>               | t <sub>OE</sub>   | Output Enable to Data Valid       |  |  |     |        | 12    | ns     |

| 5   | t <sub>AXQX</sub> <sup>d</sup> |                                 | t <sub>он</sub>   | Output Hold after Address Change  |  |  |     | 3      |       | ns     |

| 6   |                                | t <sub>ELQX</sub>               | t <sub>LZ</sub>   | Chip Enable to Output Active      |  |  |     | 3      |       | ns     |

| 7   |                                | t <sub>EHQZ</sub> e             | t <sub>HZ</sub>   | Chip Disable to Output Inactive   |  |  |     |        | 10    | ns     |

| 8   |                                | t <sub>GLQX</sub>               | t <sub>OLZ</sub>  | Output Enable to Output Active    |  |  |     | 0      |       | ns     |

| 9   |                                | t <sub>GHQZ</sub> e             | t <sub>OHZ</sub>  | Output Disable to Output Inactive |  |  | ll. | ŧ      | 10    | ns     |

| 10  |                                | t <sub>ELICC</sub> <sup>b</sup> | t <sub>PA</sub>   | Chip Enable to Power Active       |  |  |     | 0      |       | ns     |

| 11  |                                | t <sub>EHICC</sub> <sup>b</sup> | t <sub>PS</sub>   | Chip Disable to Power Standby     |  |  |     | Ŋſ     | 25    | ns     |

#### Notes

c: W must be high during SRAM READ cycles

d: Device is continuously selected with  $\overline{E}$  and  $\overline{G}$  both low

e: Measured  $\pm$  200mV from steady state output voltage

f: HSB must remain high during READ and WRITE cycles.

## SRAM READ CYCLE #1: Address Controlled<sup>c,d,f</sup>

### SRAM READ CYCLE #2: E Controlled<sup>c,f</sup>

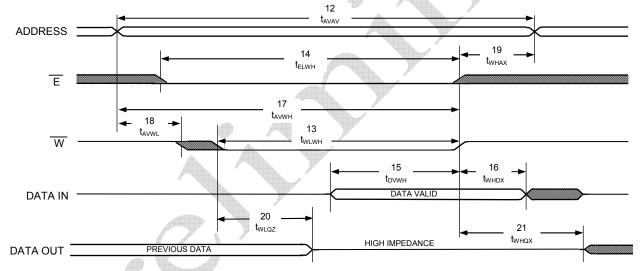

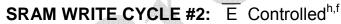

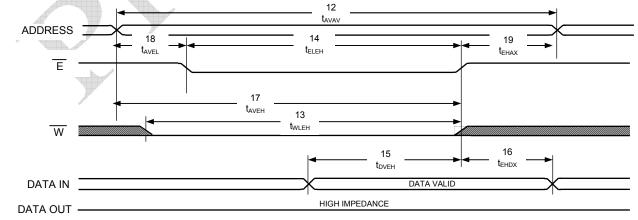

#### SRAM WRITE CYCLES #1 & #2

| NO. |                                  | SYMBOLS           |                 | DADAMETED                        | PARAMETER |  |  | STK14C | B16-25 | UNITS |

|-----|----------------------------------|-------------------|-----------------|----------------------------------|-----------|--|--|--------|--------|-------|

| NU. | #1                               | #2                | Alt.            |                                  |           |  |  | MIN    | MAX    |       |

| 12  | t <sub>AVAV</sub>                | t <sub>AVAV</sub> | t <sub>wc</sub> | Write Cycle Time                 |           |  |  | 25     |        | ns    |

| 13  | t <sub>wLWH</sub>                | t <sub>WLEH</sub> | t <sub>WP</sub> | Write Pulse Width                |           |  |  | 20     |        | ns    |

| 14  | t <sub>ELWH</sub>                | t <sub>ELEH</sub> | t <sub>cw</sub> | Chip Enable to End of Write      |           |  |  | 20     |        | ns    |

| 15  | t <sub>DVWH</sub>                | $t_{DVEH}$        | t <sub>DW</sub> | Data Set-up to End of Write      |           |  |  | 10     |        | ns    |

| 16  | t <sub>WHDX</sub>                | $t_{\text{EHDX}}$ | t <sub>DH</sub> | Data Hold after End of Write     |           |  |  | 0      |        | ns    |

| 17  | t <sub>AVWH</sub>                | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write   |           |  |  | 20     |        | ns    |

| 18  | t <sub>AVWL</sub>                | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Start of Write |           |  |  | 0      |        | ns    |

| 19  | t <sub>WHAX</sub>                | t <sub>EHAX</sub> | t <sub>WR</sub> | Address Hold after End of Write  |           |  |  | 0      |        | ns    |

| 20  | t <sub>WLQZ</sub> <sup>e,g</sup> |                   | t <sub>wz</sub> | Write Enable to Output Disable   |           |  |  |        | 10     | ns    |

| 21  | t <sub>WHQX</sub>                |                   | t <sub>ow</sub> | Output Active after End of Write |           |  |  | 3      |        | ns    |

Notes

g: If  $\overline{W}$  is low when  $\overline{E}$  goes low, the outputs remain in the high-impedance state. h:  $\overline{E}$  or  $\overline{W}$  must be  $\ge V_{IH}$  during address transitions.

### SRAM WRITE CYCLE #1: W Controlled<sup>h,f</sup>

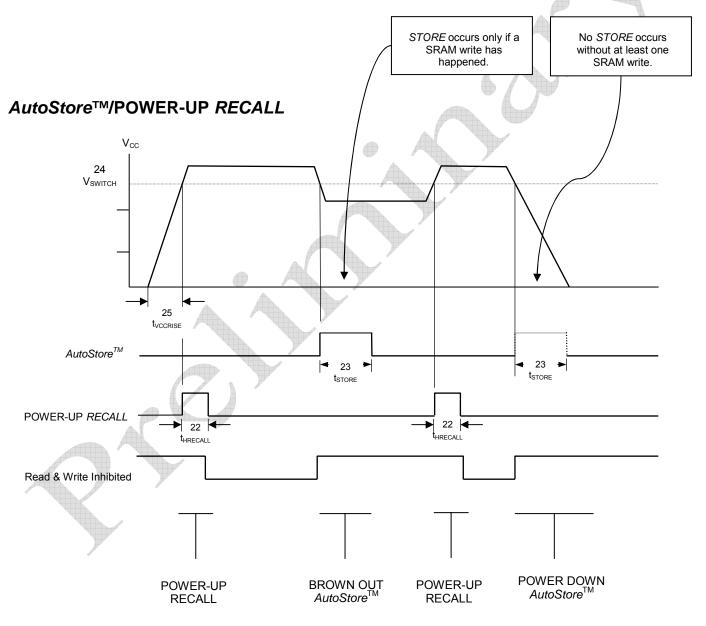

#### AutoStore<sup>™</sup> /POWER-UP RECALL

| NO    | SYMBOLS              |                   | PARAMETER                 | STK14 | CB16 | UNITS | NOTES |

|-------|----------------------|-------------------|---------------------------|-------|------|-------|-------|

| NO.   | Standard             | Alternate         |                           | MIN   | МАХ  | UNITS | NUTES |

| 22    | t <sub>HRECALL</sub> |                   | Power-up RECALL Duration  |       | 10   | ms    | i     |

| 23    | t <sub>STORE</sub>   | t <sub>HLHZ</sub> | STORE Cycle Duration      |       | 15   | ms    | j     |

| 24    | V <sub>SWITCH</sub>  |                   | Low Voltage Trigger Level | 2.55  | 2.65 | V     |       |

| 25    | t <sub>VCCRISE</sub> |                   | V <sub>CC</sub> Rise Time | 150   |      | μs    |       |

| lotes |                      |                   |                           |       |      |       |       |

is t<sub>HRECALL</sub> starts from the time V<sub>CC</sub> rises above V<sub>SWITCH</sub>

j: If an SRAM WRITE has not taken place since the last nonvolatile cycle, no STORE will take place

Note: Read and Write cycles will be ignored during STORE, RECALL and while  $V_{CC}$  is below  $V_{SWITCH}$

7

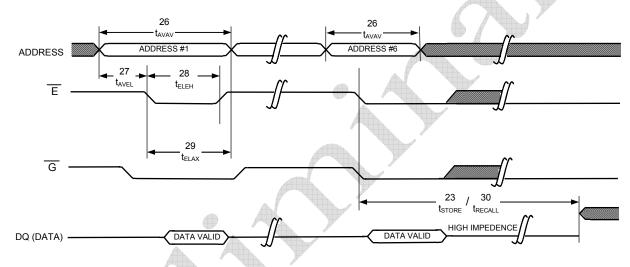

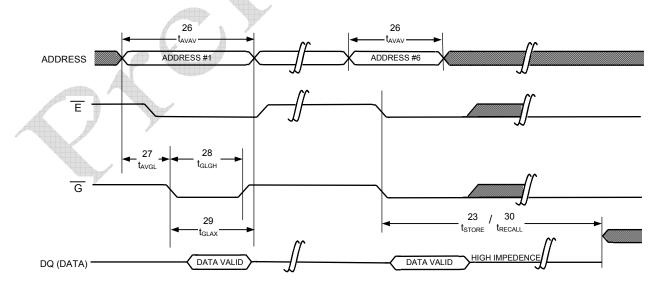

### SOFTWARE-CONTROLLED STORE/RECALL CYCLE<sup>k,I</sup>

|     | SYMBOLS             |                     | 6               |                                    |  | STK14CB16-25 |     |       |       |

|-----|---------------------|---------------------|-----------------|------------------------------------|--|--------------|-----|-------|-------|

| NO. | E<br>cont           | G<br>cont           | Alt.            | PARAMETER                          |  | MIN          | МАХ | UNITS | NOTES |

| 26  | t <sub>AVAV</sub>   | t <sub>AVAV</sub>   | t <sub>RC</sub> | STORE/RECALL Initiation Cycle Time |  | 25           |     | ns    | I     |

| 27  | t <sub>AVEL</sub>   | t <sub>AVGL</sub>   | t <sub>AS</sub> | Address Set-up Time                |  | 0            |     | ns    |       |

| 28  | t <sub>ELEH</sub>   | t <sub>GLGH</sub>   | t <sub>CW</sub> | Clock Pulse Width                  |  | 20           |     | ns    |       |

| 29  | t <sub>ELAX</sub>   | t <sub>GLAX</sub>   |                 | Address Hold Time                  |  | 20           | 4   | ns    |       |

| 30  | t <sub>RECALL</sub> | t <sub>RECALL</sub> |                 | RECALL Duration                    |  |              | 50  | μs    |       |

Notes

k: The software sequence is clocked with  $\overline{E}$  controlled READs or  $\overline{G}$  controlled READs.

I: The six consecutive addresses must be read in the order listed in the Mode Selection Table. W must be high during all six consecutive cycles.

### SOFTWARE STORE/RECALL CYCLE: E Controlled

SOFTWARE STORE/RECALL CYCLE: G Controlled<sup>I</sup>

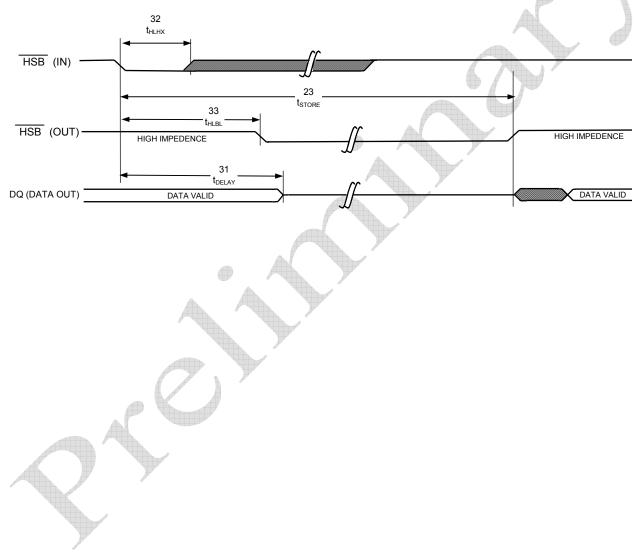

#### HARDWARE STORE CYCLE

| NO. | SYMBOLS            |                   | PARAMETER                           | STK1 | 4CB16 | UNITS | NOTES |

|-----|--------------------|-------------------|-------------------------------------|------|-------|-------|-------|

| NO. | Standard           | Alternate         | FARAMETER                           | MIN  | МАХ   | UNITS | NOTES |

| 31  | t <sub>DELAY</sub> | t <sub>HLQZ</sub> | Time Allowed to Complete SRAM Cycle | 1    |       | μs    | р     |

| 32  | t <sub>HLHX</sub>  |                   | Hardware STORE Pulse Width          | 15   |       | ns    |       |

| 33  | t <sub>HLBL</sub>  |                   | Hardware STORE Low to STORE Busy    |      | 300   | ns    |       |

Notes

m: Read and Write cycles in progress before HSB is asserted are given this amount of time to complete.

#### HARDWARE STORE CYCLE

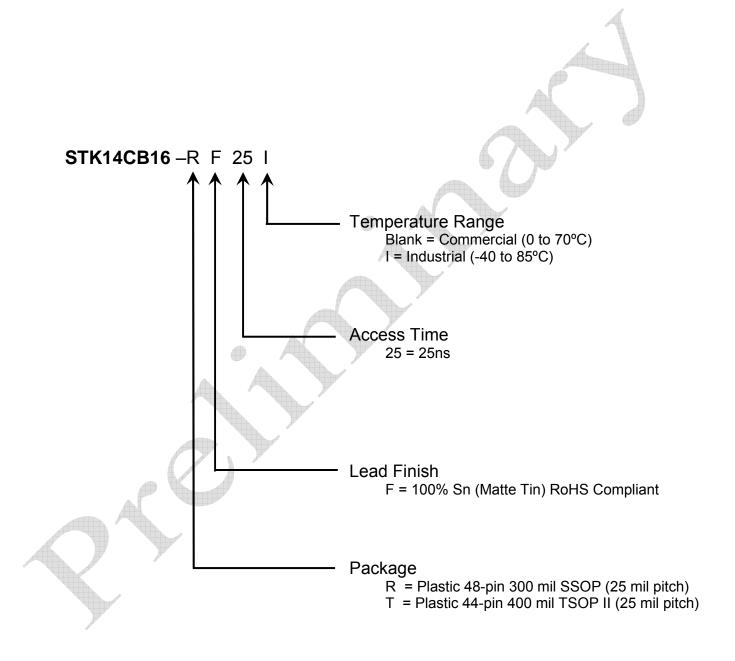

#### **ORDERING INFORMATION**

#### **Document Revision History**

| Revision | Date         | Summary              |

|----------|--------------|----------------------|

| 0.0      | October 2005 | Advanced Information |

SIMTEK STK14CB16 Data Sheet, October 2005

Copyright 2005, Simtek Corporation. All rights reserved.

This datasheet may only be printed for the express use of Simtek Customers. No part of this datasheet may be reproduced in any other form or means without express written permission from Simtek Corporation. The information contained in this publication is believed to be accurate, but changes may be made without notice. Simtek does not assume responsibility for, or grant or imply any warranty, including MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE regarding this information, the product or its use. Nothing herein constitutes a license, grant or transfer of any rights to any Simtek patent, copyright, trademark or other proprietary right.