#### DEVICE PERFORMANCE SPECIFICATION

Revision 5.0 MTD/PS-0205 January 29, 2007

# KODAK KAI-1020 IMAGE SENSOR

1000 (H) X 1000 (V) INTERLINE TRANSFER PROGRESSIVE SCAN CCD

# CONTENTS Summary Specification

| Summary Specification                  |    |

|----------------------------------------|----|

| Description                            |    |

| Features                               |    |

| Applications                           | 5  |

| Ordering Information                   |    |

| Device Description                     | 7  |

| Architecture                           |    |

| Physical Description                   | 8  |

| Pin Description and Device Orientation | 8  |

| Imaging Performance                    | 11 |

| Optical Specification                  | 11 |

| CCD Specifications                     | 11 |

| CDS Output Specification               | 11 |

| General – Monochrome                   | 11 |

| General Color                          | 11 |

| Power                                  | 12 |

| Typical Performance Curves             | 13 |

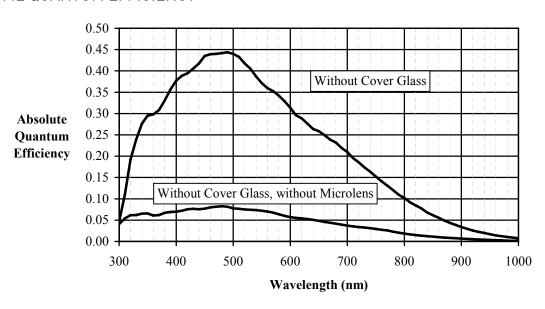

| Monochrome Quantum Efficiency          | 13 |

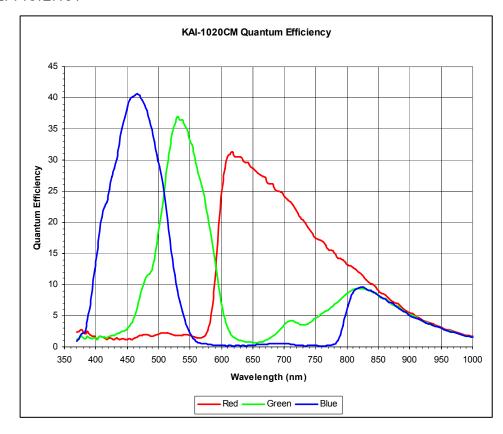

| Color Quantum Efficiency               | 13 |

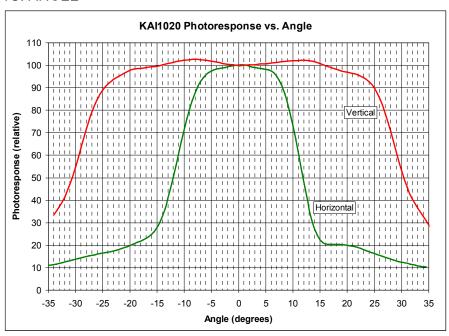

| Photoresponse vs. Angle                | 14 |

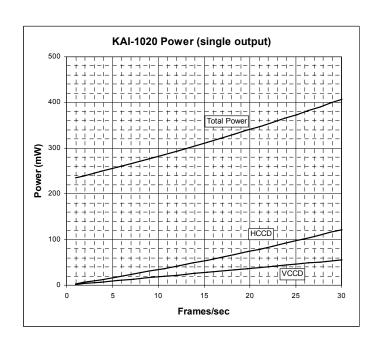

| Sensor Power                           | 14 |

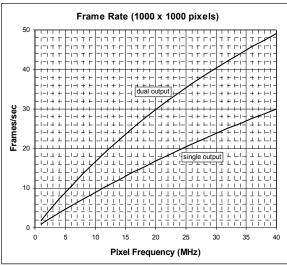

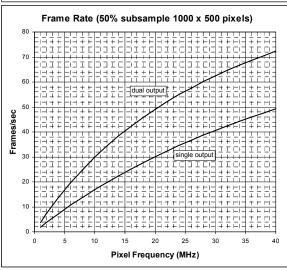

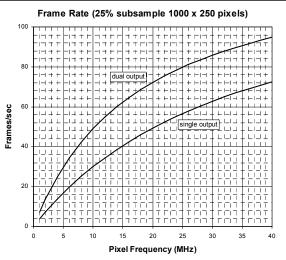

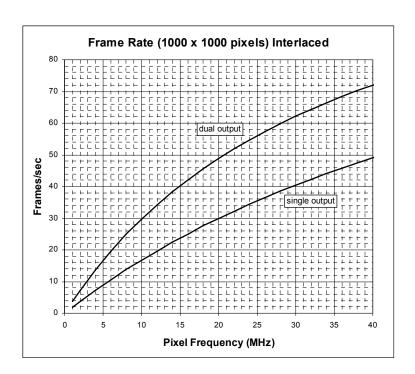

| Frame Rate                             | 15 |

| Defect Definitions                     | 17 |

| Specifications                         | 17 |

| Test Definitions                       | 18 |

| Test Conditions                        | 18 |

| Tests                                  | 18 |

| Test Regions of Interest               | 21 |

| Operation                              | 25 |

| Single or Dual output                  |    |

| The KAI-1020 Pixel                     |    |

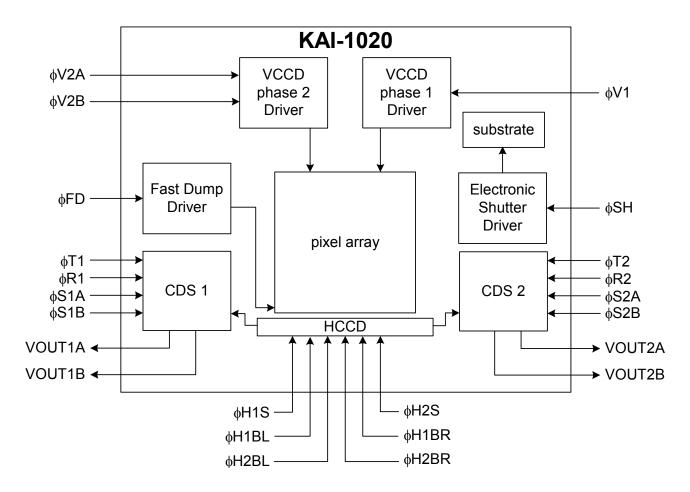

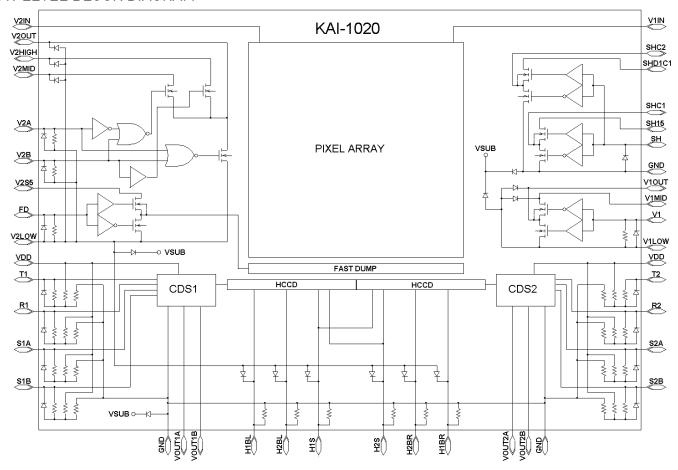

| High Level Black Diagram               | 27 |

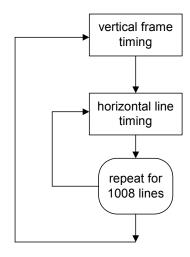

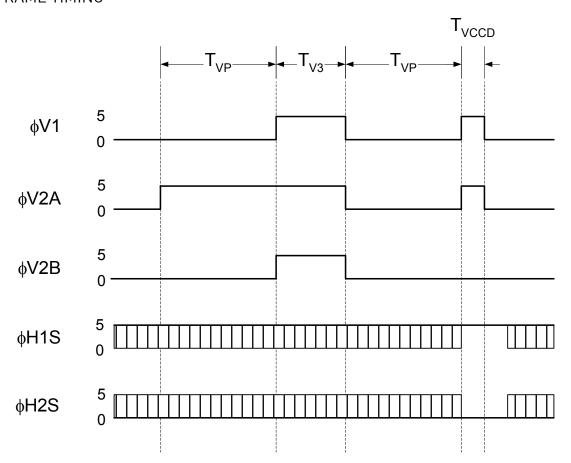

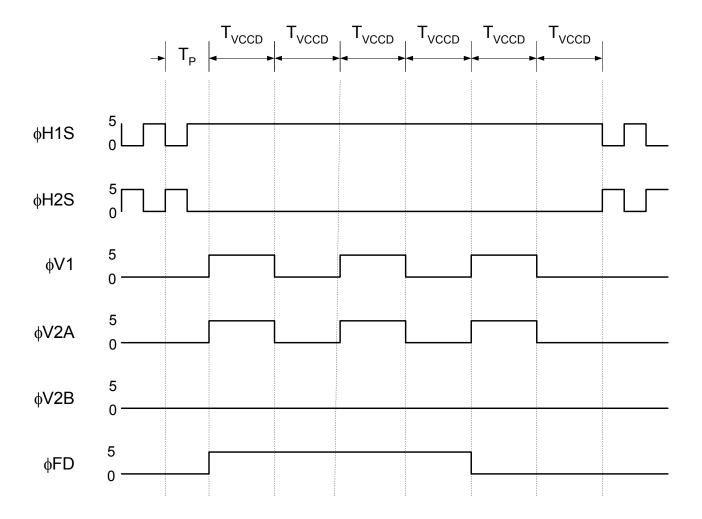

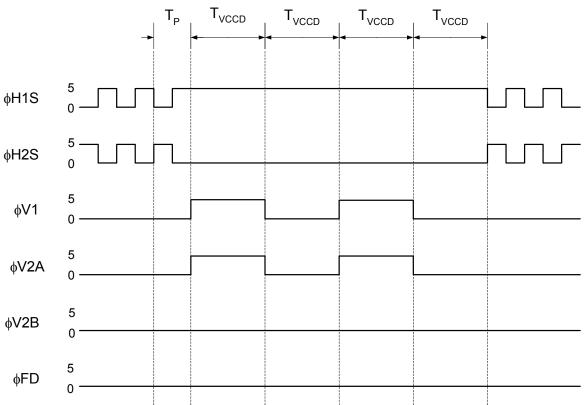

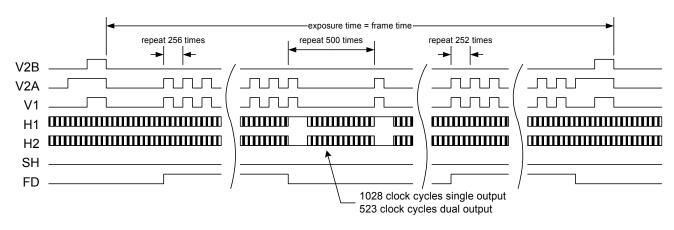

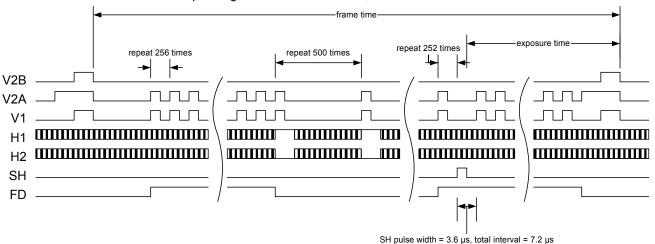

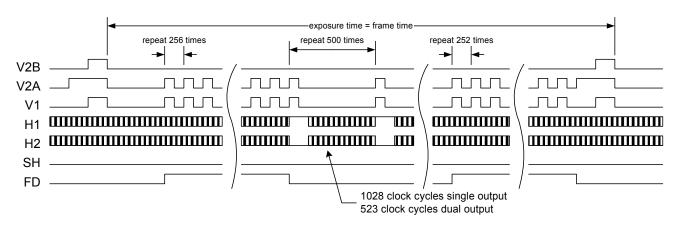

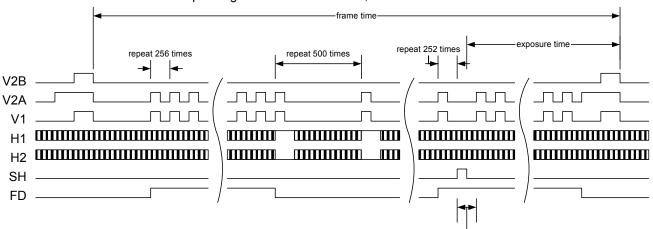

| Main Timing                            |    |

| Vertical Frame Timing                  |    |

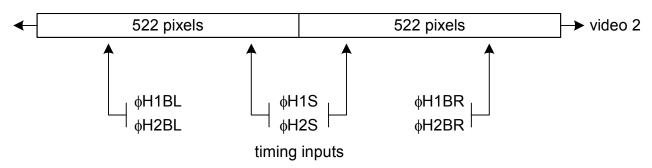

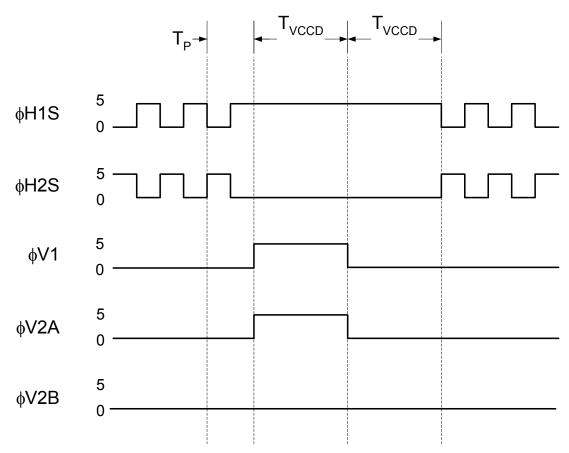

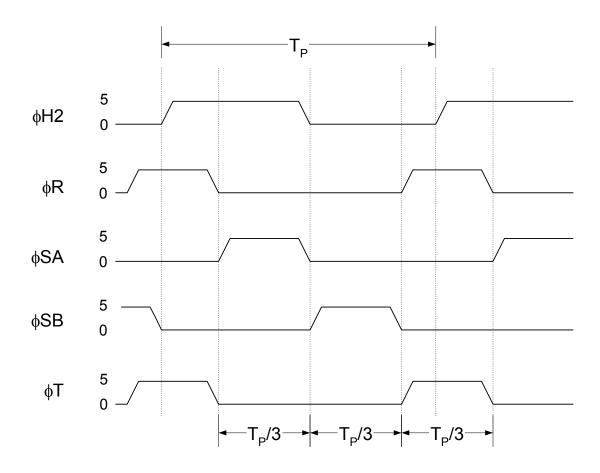

| Horizontal Line Timing                 |    |

| Single Output                          | 31 |

| Dual Output                            | 31 |

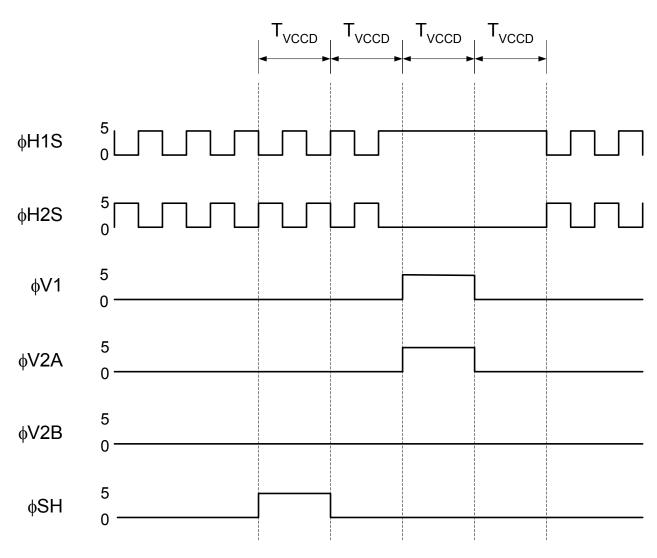

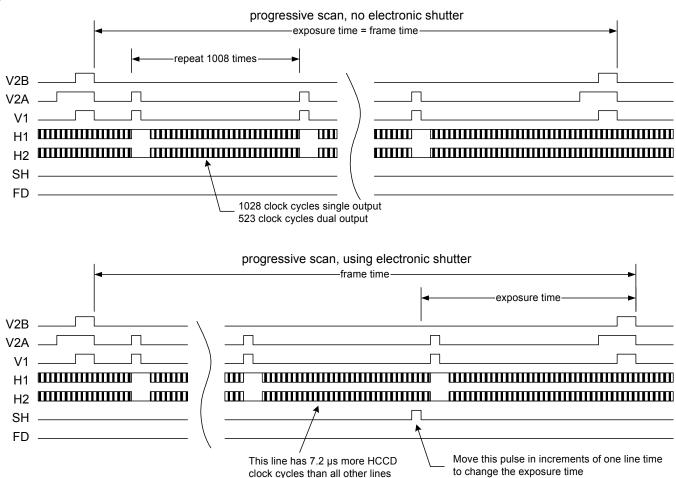

| Electronic Shutter                     | 32 |

| Substrate Voltage                      | 32 |

| Substrate Voltage and Antiblooming     |    |

| Electronic Shutter Timing              |    |

| Fast Dump                              |    |

| Binning and Interlaced Modes           |    |

| Correlated Double Sampling (CDS)       |    |

| CDS Timing Edge Alignment              |    |

| Disabling the CDS                      |    |

| Timing and Voltage Specifications      | 38 |

| Absolute Maximum Ratings               |    |

| Timing                               |    |

|--------------------------------------|----|

| Bias Voltages                        |    |

| Power Up Sequence                    | 38 |

| Pulse Amplitudes                     | 39 |

| Timing Examples                      | 40 |

| Progressive Scan                     | 40 |

| Fast Line Dump                       | 41 |

| Interlaced – Field Integration       | 42 |

| Camera Design                        | 43 |

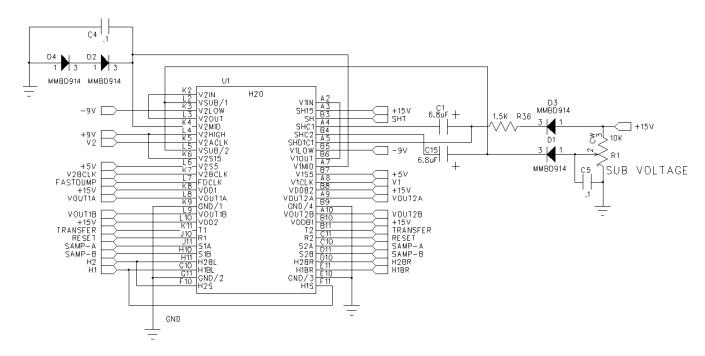

| Low level block diagram              | 43 |

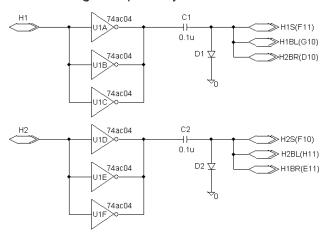

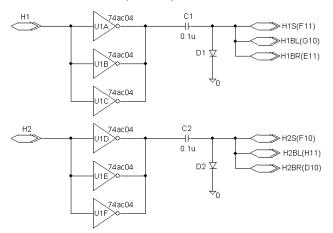

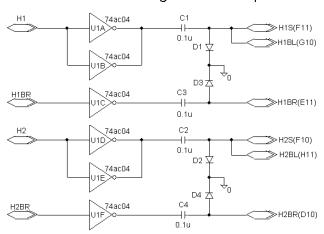

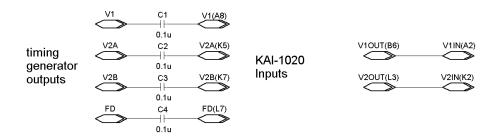

| Horizontal CCD Drive Circuit         | 44 |

| Vertical CCD                         | 45 |

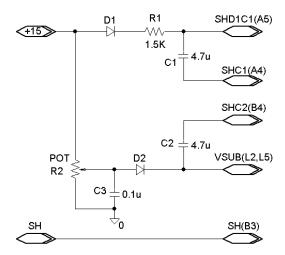

| Electronic Shutter                   |    |

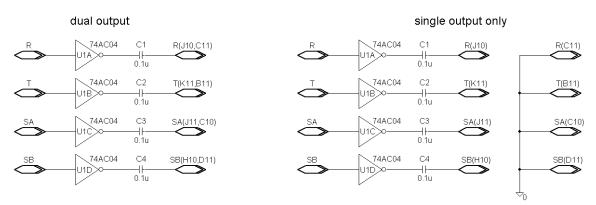

| CDS Timing Inputs                    |    |

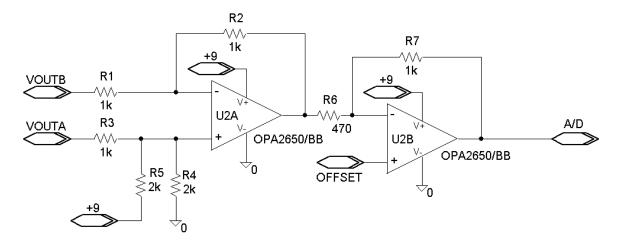

| CDS output circuit                   |    |

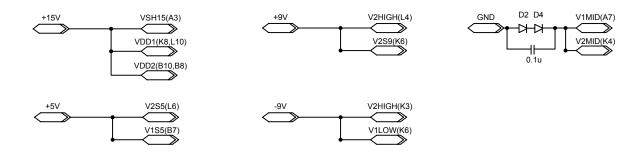

| Power Supplies                       | 48 |

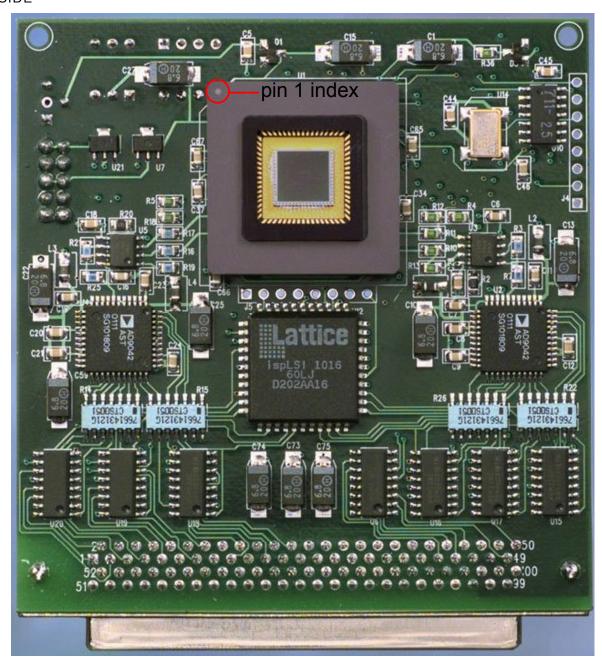

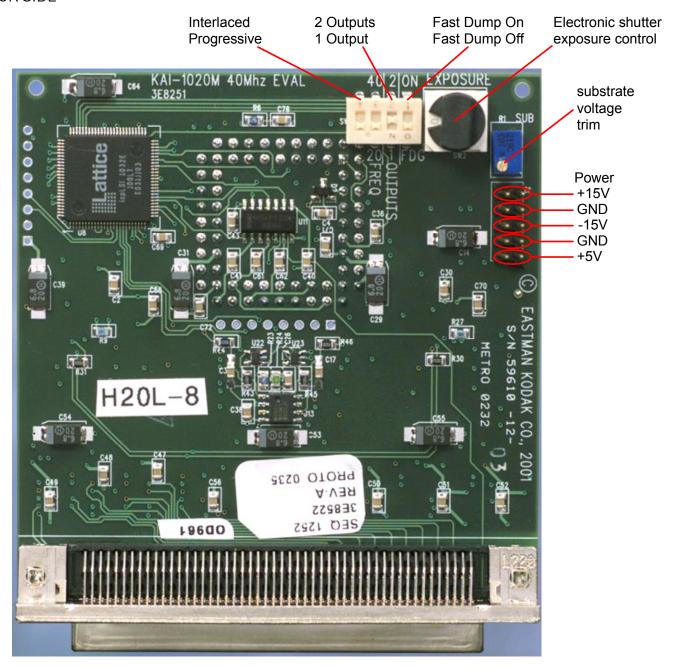

| KAI-1020 Evaluation Board            |    |

| Front side                           |    |

| Back side                            |    |

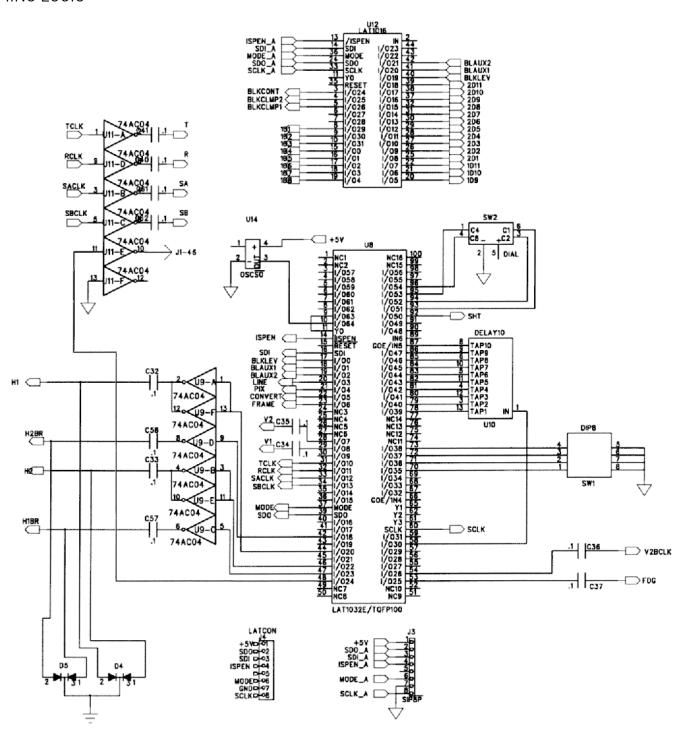

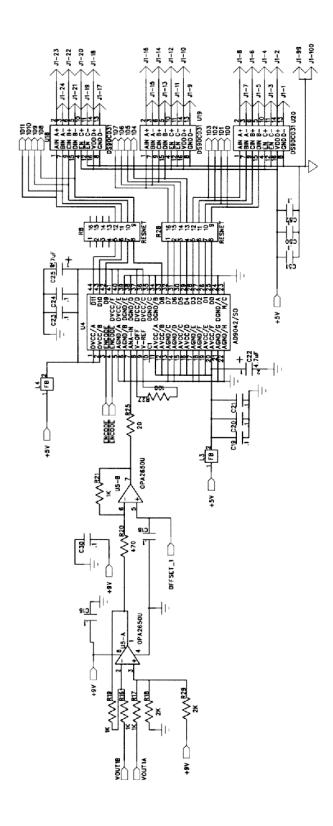

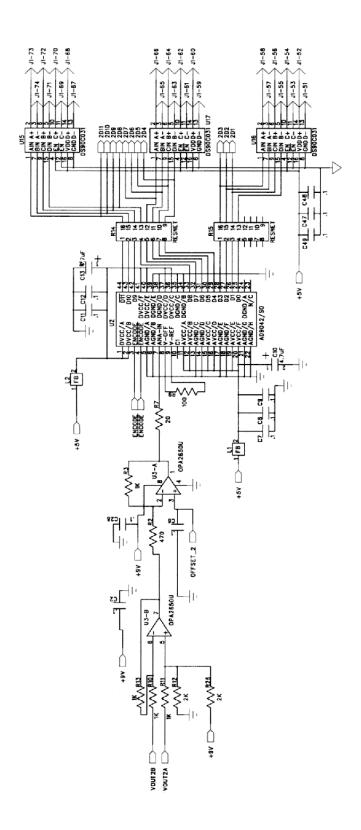

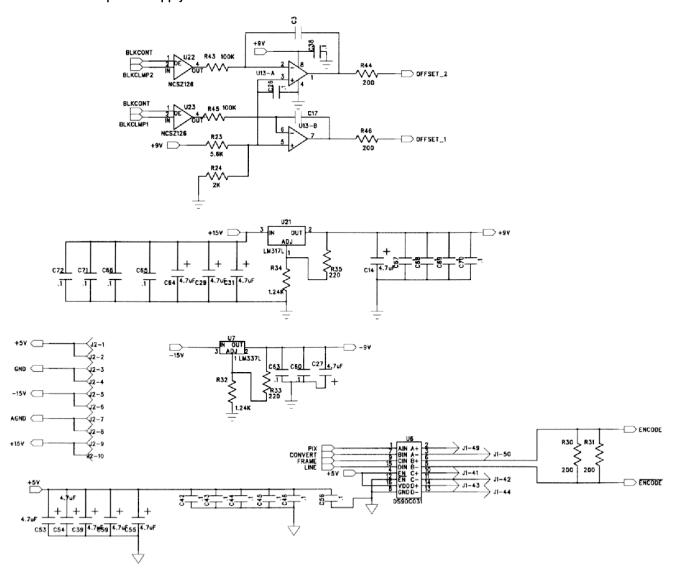

| Schematics                           |    |

| KAI-1020                             |    |

| Timing Logic                         |    |

| Output 1                             |    |

| Output 2                             |    |

| Automatic offset and power supply    |    |

| Parts List                           |    |

| Digital output connector             |    |

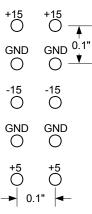

| Power Connector                      |    |

| Mode Switch                          |    |

| Exposure Switch                      |    |

| Substrate Voltage Trim               |    |

| Evaluation Board Notes               |    |

| Timing                               |    |

| Output channel                       |    |

| Automatic offset                     |    |

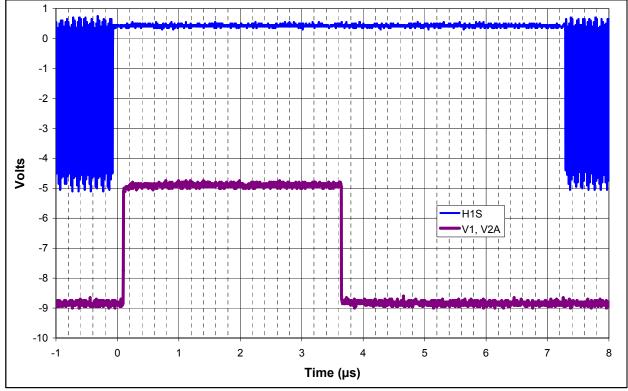

| Oscilloscope Traces                  |    |

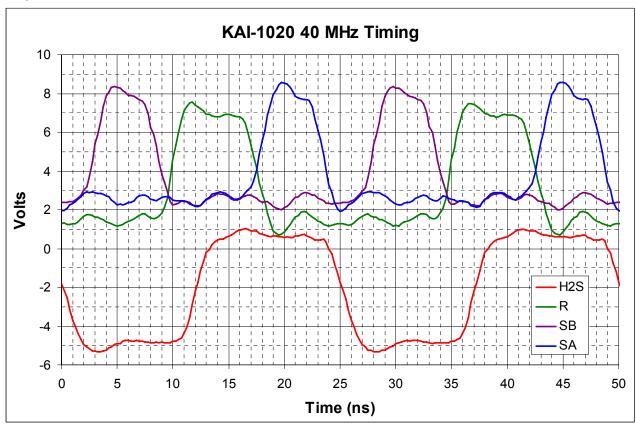

| CDS Timing                           |    |

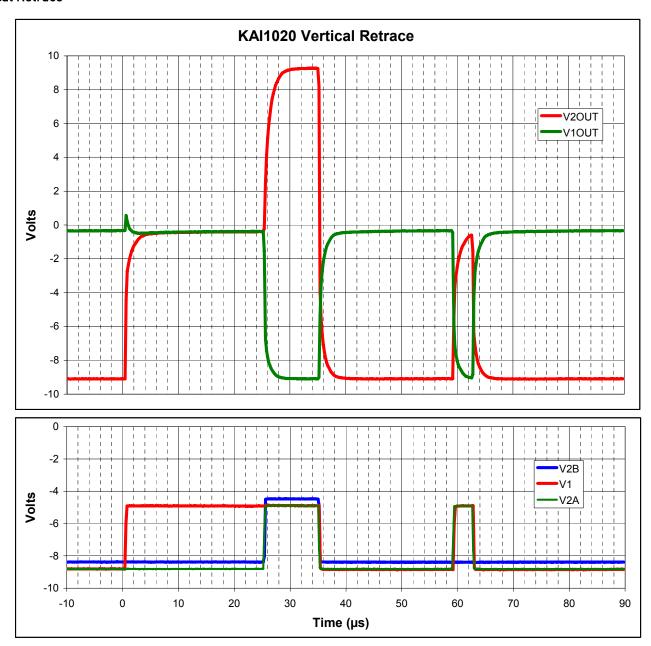

| Vertical Retrace                     |    |

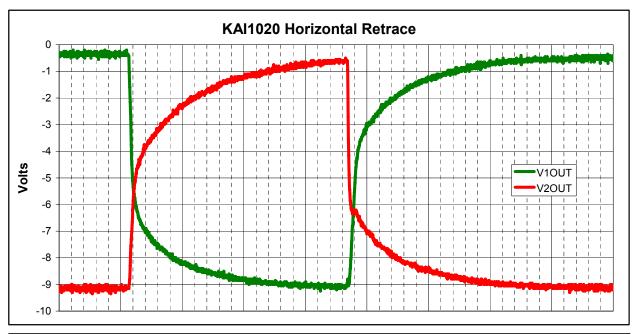

| Horizontal Retrace                   |    |

| Storage and Handling                 |    |

| ESD Cover Glass Care and Cleanliness |    |

| Environmental Exposure               |    |

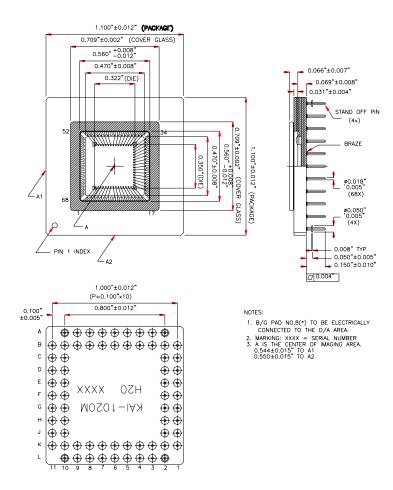

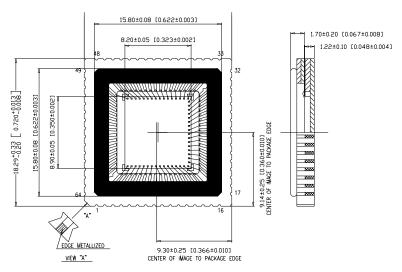

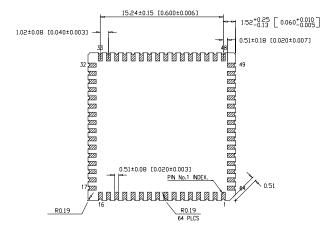

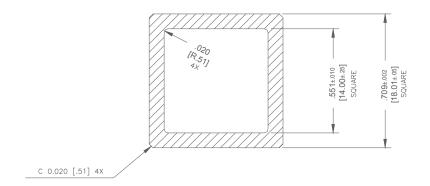

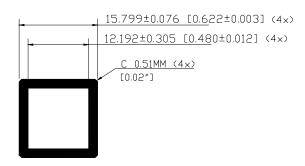

| Mechanical Drawings                  |    |

| Completed Assembly                   |    |

| Pin Grid Array                       |    |

| Leadless Chip Carrier                |    |

| Leadless Chip Carrier and Soldering  |    |

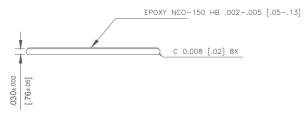

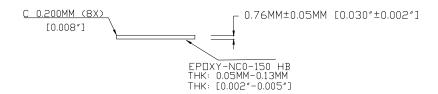

| Cover Glass                          | 47 |

| Pin Grid Array Cover Glass                | 67 |

|-------------------------------------------|----|

| Leadless Chip Carrier Cover Glass         | 68 |

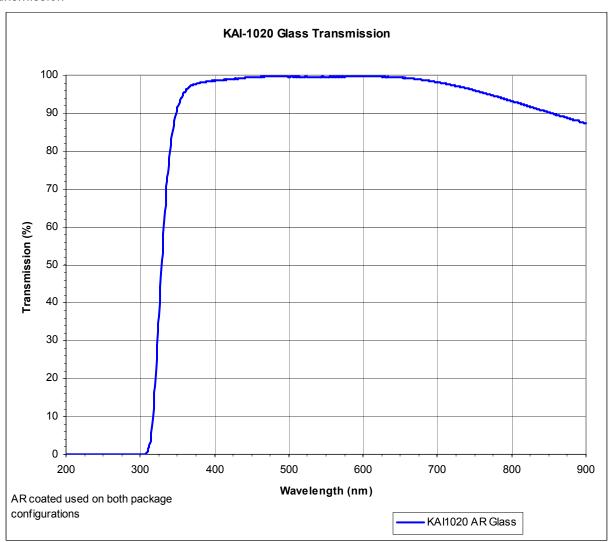

| Glass Transmission                        | 69 |

| Quality Assurance and Reliability         | 70 |

| Quality Strategy                          | 70 |

| Replacement                               | 70 |

| Liability of the Supplier:                |    |

| Liability of the Customer                 | 70 |

| Reliability                               | 70 |

| Test Data Retention                       | 70 |

| Mechanical                                | 70 |

| Warning: Life Support Applications Policy |    |

| Revision Changes                          | 71 |

|                                           |    |

| TABLE OF FIGURES                          |    |

| Figure 1: Test Sub Regions of Interest    | 21 |

| Figure 2: Regions of Interest             | 22 |

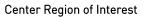

| Figure 3: Center Region of Interest       | 23 |

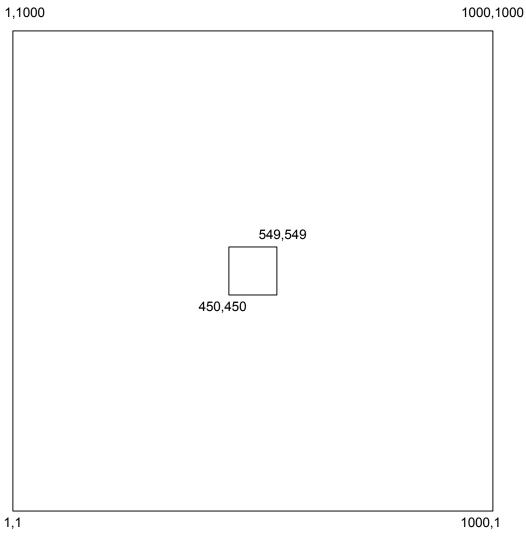

| Figure 4: Zones 1 and 2                   |    |

## SUMMARY SPECIFICATION

#### **KODAK** KAI-1020 IMAGE SENSOR

## 1000 (H) X 1000 (V) PROGRESSIVE SCAN INTERLINE CCD IMAGE SENSOR

#### DESCRIPTION

The KODAK KAI-1020 Image Sensor is a one megapixel interline CCD with integrated clock drivers and on-chip correlated double sampling. The progressive scan architecture and global electronic shutter provide excellent image quality for full motion video and still image capture.

The integrated clock drivers allow for easy integration with CMOS logic timing generators. The sensor features a fast line dump for high-speed sub-window readout and single (30 fps) or dual (48 fps) output operation.

#### **FEATURES**

- 10 bits dynamic range at 40 MHz

- Large 7.4 µm square pixels for high sensitivity

- Progressive scan (non-interlaced)

- Integrated vertical clock drivers

- Integrated correlated double sampling (CDS) up to 40 MHz

- Integrated electronic shutter driver

- Reversible HCCD capable of 40MHz operation All timing inputs 0 to 5 Volts

- Single or dual video output operation

- Progressive scan or interlaced

- Fast dump gate for high speed sub-window readout

- Antiblooming protection

#### **APPLICATIONS**

- Industrial Imaging

- Medical Imaging

| Parameter  Architecture  Architecture  Architecture  Total Number of Pixels  Number of Effective Pixels  Number of Active Pixels  Active Image Size  Active Image Size  Aspect Ratio  Number of Outputs  Saturation Signal  Output Sensitivity  Quantum Efficiency KAI-1020-CBA R[620nm], G[540nm], B[460nm]  Dark Noise  Dark Current [Typical]  Dynamic Range  Blooming Suppression  Image Lag  Amaximum Data Rate  Progressive Scan, One Output Progressive Scan, One Output Progressive Scan, One Output Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package  Are 1020 [N x 1008 (V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            | T                           |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|--|--|--|--|

| Total Number of Pixels 1028 (H) x 1008 (V)  Number of Effective Pixels 1004 (H) x 1000 (V)  Number of Active Pixels 1000 (H) x 1000 (V)  Pixel Size 7.4 µm (H) x 7.4 µm (V)  Active Image Size 7.4 µm (H) x 7.4 µm (V)  Aspect Ratio 1:1  Number of Outputs 1 or 2  Saturation Signal 40,000 electrons  Output Sensitivity 12 µV/electron  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise 50 electrons rms  Dark Current (Typical) <0.5 nA/cm²  Dynamic Range 58 dB  Blooming Suppression 100 X  Image Lag <10 electrons  Smear <0.03%  Maximum Data Rate 40 MHz/Channel (2 channels)  Frame Rate Progressive Scan, One Output Ag fps  Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Parameter                  | Typical Value               |  |  |  |  |

| Total Number of Pixels 1028 (H) x 1008 (V)  Number of Effective Pixels 1004 (H) x 1000 (V)  Pixel Size 7.4 µm (H) x 7.4 µm (V)  Active Image Size 7.4 µm (H) x 7.4 µm (V)  Aspect Ratio 1:1  Number of Outputs 1 or 2  Saturation Signal 40,000 electrons  Output Sensitivity 12 µV/electron  Quantum Efficiency KAI-1020-ABA (500nm) 44%  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm) 50 electrons rms  Dark Noise 50 electrons rms  Dark Current (Typical) <0.5 nA/cm²  Dynamic Range 58 dB  Blooming Suppression 100 X  Image Lag <10 electrons  Smear <0.03%  Maximum Data Rate 40 MHz/Channel (2 channels)  Frame Rate Progressive Scan, One Output Prog | Architecture               | Interline CCD,              |  |  |  |  |

| Number of Effective Pixels  Number of Active Pixels  Pixel Size  Active Image Size  Aspect Ratio  Number of Outputs  Saturation Signal  Output Sensitivity  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Avairum Data Rate  Progressive Scan, One Output Progressive Scan, One Output Progressive Scan, One Output Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  1000 (H) x 1000 (V) 1000 (H) x 100 (V) 1000 (H) x 1000 (V) 1000 (H) x 1000 (H) 1000 (H) x  | Architecture               | Progressive Scan            |  |  |  |  |

| Number of Active Pixels  Pixel Size  7.4 µm (H) x 7.4 µm (V)  7.4 mm (H) x 7.4 mm (V)  10.5 mm (diagonal)  Aspect Ratio  1:1  Number of Outputs  1 or 2  Saturation Signal  Output Sensitivity  12 µV/electron  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Smear  Progressive Scan, One Output  Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  7.4 µm (H) x 7.4 µm (V)  10.5 mm (diagonal)  44%  44%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  40 All Sections  40 All Sections | Total Number of Pixels     | 1028 (H) x 1008 (V)         |  |  |  |  |

| Pixel Size  Active Image Size  Active Image Size  Aspect Ratio  Aspect Ratio  Number of Outputs  Saturation Signal  Output Sensitivity  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Algebra Signal  Algebra Si  | Number of Effective Pixels | 1004 (H) x 1004 (V)         |  |  |  |  |

| Active Image Size  Aspect Ratio  Aspect Ratio  Number of Outputs  Saturation Signal  Output Sensitivity  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Smear  All Oelectrons  Maximum Data Rate  Progressive Scan, One Output Progressive Scan, One Output Progressive Scan, One Output Progressive Scan, One Output Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  7.4 mm [H] x 7.4 mm [V] 10.5 mm (diagonal) 12 µV/electrons 44%  40,000 electrons 44%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  40 NHz/channel (2 channels) 40 MHz/Channel (2 channels) 40 MHz/Channel (2 channels) 41 pps  All pps | Number of Active Pixels    | 1000 (H) x 1000 (V)         |  |  |  |  |

| Aspect Ratio Aspect Ratio Number of Outputs Saturation Signal Output Sensitivity 12 µV/electron Quantum Efficiency KAI-1020-ABA (500nm) Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm) Dark Noise Dark Current (Typical) Dynamic Range Blooming Suppression Image Lag Smear  Progressive Scan, One Output Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package  10 of 2  40,000 electrons 44%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  40 MHz/Channel (2 channels) 40 MHz/Channel (2 channels) 40 MHz/Channel (2 channels) 48 fps 49 fps  Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pixel Size                 | 7.4 μm (H) x 7.4 μm (V)     |  |  |  |  |

| Aspect Ratio 1:1  Number of Outputs 1 or 2  Saturation Signal 40,000 electrons  Output Sensitivity 12 µV/electron  Quantum Efficiency KAI-1020-ABA (500nm)  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise 50 electrons rms  Dark Current (Typical) <0.5 nA/cm²  Dynamic Range 58 dB  Blooming Suppression 100 X  Image Lag <10 electrons  Smear <0.03%  Maximum Data Rate 40 MHz/Channel (2 channels)  Frame Rate Progressive Scan, One Output Progressive Scan, Dual Outputs Interlaced Scan, One Output 49 fps  Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Active Image Size          |                             |  |  |  |  |

| Number of Outputs       1 or 2         Saturation Signal       40,000 electrons         Output Sensitivity       12 μV/electron         Quantum Efficiency KAI-1020-ABA (500nm)       44%         Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)       31%, 36%, 41%         Dark Noise       50 electrons rms         Dark Current (Typical)       <0.5 nA/cm²                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Aspect Ratio               |                             |  |  |  |  |

| Output Sensitivity  Quantum Efficiency KAI-1020-ABA [500nm]  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Smear  Volume  Progressive Scan, One Output Affice Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  12 µV/electron  44%  44%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  40. S dB  All Selectrons rms  40. S dB  All Selectrons  40 MHz/Channel (2 channels)  48 fps 48 fps 49 fps  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -                          | 1 or 2                      |  |  |  |  |

| Output Sensitivity  Quantum Efficiency KAI-1020-ABA [500nm]  Quantum Efficiency KAI-1020-CBA R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Smear  Volume  Progressive Scan, One Output Affice Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  12 µV/electron  44%  44%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  31%, 36%, 41%  40. S dB  All Selectrons rms  40. S dB  All Selectrons  40 MHz/Channel (2 channels)  48 fps 48 fps 49 fps  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |                             |  |  |  |  |

| Soonm   Cuantum Efficiency KAI-1020-CBA   R(620nm), G(540nm), B(460nm)   Soon electrons rms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | 12 μV/electron              |  |  |  |  |

| R(620nm), G(540nm), B(460nm)  Dark Noise  Dark Current (Typical)  Dynamic Range  Blooming Suppression  Image Lag  Smear  Auximum Data Rate  Progressive Scan, One Output Progressive Scan, Dual Outputs Integrated Vertical Clock Drivers  Integrated Electronic Shutter Driver  Package  50 electrons  50 electrons  40 MB  40 MB  40 MHz/Channel (2 channels)  40 MHz/Channel (2 channels)  48 fps  49 fps  68 pin PGA or  64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            | 44%                         |  |  |  |  |

| Dark Current [Typical] <0.5 nA/cm²  Dynamic Range 58 dB  Blooming Suppression 100 X  Image Lag <10 electrons  Smear <0.03%  Maximum Data Rate 40 MHz/Channel [2 channels]  Frame Rate  Progressive Scan, One Output Progressive Scan, Dual Outputs 48 fps Interlaced Scan, One Output 49 fps  Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling [CDS]  Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            | 31%, 36%, 41%               |  |  |  |  |

| Dynamic Range 58 dB Blooming Suppression 100 X Image Lag <10 electrons Smear <0.03% Maximum Data Rate 40 MHz/Channel (2 channels) Frame Rate Progressive Scan, One Output Progressive Scan, Dual Outputs Interlaced Scan, One Output 49 fps Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | =                          | 50 electrons rms            |  |  |  |  |

| Dynamic Range 58 dB Blooming Suppression 100 X Image Lag <10 electrons Smear <0.03% Maximum Data Rate 40 MHz/Channel (2 channels) Frame Rate Progressive Scan, One Output Progressive Scan, Dual Outputs Interlaced Scan, One Output 49 fps Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Dark Current (Typical)     | <0.5 nA/cm <sup>2</sup>     |  |  |  |  |

| Image Lag <10 electrons  Smear <0.03%  Maximum Data Rate 40 MHz/Channel (2 channels)  Frame Rate Progressive Scan, One Output Progressive Scan, Dual Outputs 48 fps Interlaced Scan, One Output 49 fps  Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | 58 dB                       |  |  |  |  |

| Smear < 0.03%  Maximum Data Rate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Blooming Suppression       | 100 X                       |  |  |  |  |

| Maximum Data Rate 40 MHz/Channel (2 channels)  Frame Rate Progressive Scan, One Output 30 fps Progressive Scan, Dual Outputs 48 fps Interlaced Scan, One Output 49 fps Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Image Lag                  | <10 electrons               |  |  |  |  |

| Frame Rate Progressive Scan, One Output 30 fps Progressive Scan, Dual Outputs 48 fps Interlaced Scan, One Output 49 fps Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Smear                      | <0.03%                      |  |  |  |  |

| Progressive Scan, One Output Progressive Scan, Dual Outputs Interlaced Scan, One Output Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package  68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Maximum Data Rate          | 40 MHz/Channel (2 channels) |  |  |  |  |

| Progressive Scan, Dual Outputs Interlaced Scan, One Output Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package  68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Frame Rate                 |                             |  |  |  |  |

| Interlaced Scan, One Output 49 fps Integrated Vertical Clock Drivers Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver  Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |                             |  |  |  |  |

| Integrated Vertical Clock Drivers  Integrated Correlated Double Sampling (CDS)  Integrated Electronic Shutter Driver  Package  68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |                             |  |  |  |  |

| Integrated Correlated Double Sampling (CDS) Integrated Electronic Shutter Driver Package  68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            | 49 fps                      |  |  |  |  |

| Package  68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                            |                             |  |  |  |  |

| Package 68 pin PGA or 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |                             |  |  |  |  |

| Package 64 pin CLCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |                             |  |  |  |  |

| Cover Glass AR coated, 2 sides                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Package                    |                             |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Cover Glass                | AR coated, 2 sides          |  |  |  |  |

All parameters above are specified at T = 40°C

## **ORDERING INFORMATION**

| Catalog<br>Number | Product Name                  | Description                                                        | Marking Code  |

|-------------------|-------------------------------|--------------------------------------------------------------------|---------------|

|                   |                               | Monochrome, No Microlens, PGA Package,                             | KAI-1020      |

| 2H4889            | KAI- 1020-AAA-JP-BA           | Taped Clear Cover Glass, no coatings, Standard Grade               | Serial Number |

| 4H0934            | KAI- 1020-ABB-FD-AE           | Monochrome, Telecentric Microlens, CLCC Package,                   |               |

| 4HU934            | NAI- 1020-ABB-FD-AE           | Clear Cover Glass with AR coating (both sides), Engineering Sample |               |

| 4H0933            | KAI- 1020-ABB-FD-BA           | Monochrome, Telecentric Microlens, CLCC Package,                   |               |

| 4110700           | TAL TOZO ADD TO DA            | Clear Cover Glass with AR coating (both sides), Standard Grade     |               |

| 4H0932            | KAI- 1020-ABB-JB-AF           | Monochrome, Telecentric Microlens, PGA Package,                    |               |

|                   | 1011 1020 7.00 00 7.0         | Clear Cover Glass (no coatings), Engineering Sample                | KAI-1020-ABB  |

| 4H0931            | KAI- 1020-ABB-JB-BA           | Monochrome, Telecentric Microlens, PGA Package,                    | Serial Number |

|                   |                               | Clear Cover Glass (no coatings), Standard Grade                    | _             |

| 4H0910            | KAI- 1020-ABB-JD-AF           | Monochrome, Telecentric Microlens, PGA Package,                    |               |

|                   |                               | Clear Cover Glass with AR coating (both sides), Engineering Sample | _             |

| 4H0935            | KAI- 1020-ABB-JD-BA           | Monochrome, Telecentric Microlens, PGA Package,                    |               |

| 1110700           | 1011 1020 7.00 00 07.         | Clear Cover Glass with AR coating (both sides), Standard Grade     |               |

| 2H4996            | KAI- 1020-CBA-FD-AF           | Color (Bayer RGB), Telecentric Microlens, CLCC Package,            |               |

| 2111776           | 1011 1020 03/113 /12          | Clear Cover Glass with AR coating (both sides), Engineering Sample | 4             |

| 4H0131            | KAI- 1020-CBA-FD-BA           | Color (Bayer RGB), Telecentric Microlens, CLCC Package,            |               |

| 4110101           | 1011 1020 08/118 8/1          | Clear Cover Glass with AR coating (both sides), Standard Grade     | KAI-1020CM    |

| 4H0194            | KAI- 1020-CBA-JD-AF           | Color (Bayer RGB), Telecentric Microlens, PGA Package,             | Serial Number |

| 4110174           | 1011 1020 08/1 38 712         | Clear Cover Glass with AR coating (both sides), Engineering Sample | _             |

| 4H0193            | KAI- 1020-CBA-JD-BA           | Color (Bayer RGB), Telecentric Microlens, PGA Package,             |               |

| 5176              |                               | Clear Cover Glass with AR coating (both sides), Standard Grade     |               |

| 1E9790            | KEK-1E9790-KAI-1020-<br>12-40 | Evaluation Board (Complete Kit)                                    | n/a           |

Please see ISS Application Note "Product Naming Convention" (MTD/PS-0892) for a full description of naming convention used for KODAK image sensors.

## Address all inquiries and purchase orders to:

Image Sensor Solutions Eastman Kodak Company Rochester, New York 14650-2010

Phone: (585) 722-4385 Fax: (585) 477-4947

E-mail: imagers@kodak.com

Kodak reserves the right to change any information contained herein without notice. All information furnished by Kodak is believed to be accurate.

#### **DEVICE DESCRIPTION**

#### **ARCHITECTURE**

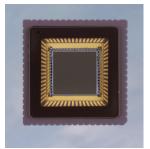

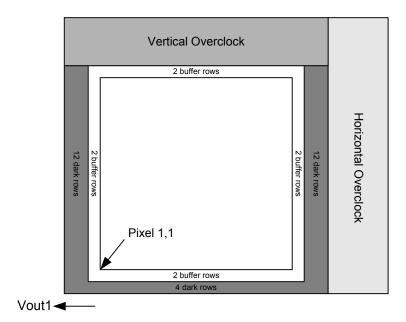

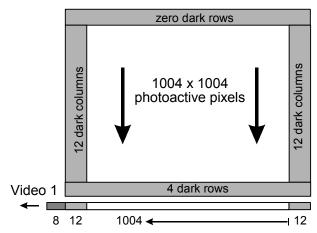

There are 4 light shielded rows followed 1004 photoactive rows. The first 2 and the last 2 photoactive rows are buffer rows giving a total of 1000 lines of image data.

In the single output mode all pixels are clocked out of the Video 1 output in the lower left corner of the sensor. The first 8 empty pixels of each line do not receive charge from the vertical shift register. The next 12 pixels receive charge from the left light-shielded edge followed by 1004 photo-sensitive pixels and finally 12 more light shielded pixels from the right edge of the sensor. The first and

last 2 photosensitive pixels are buffer pixels giving a total of 1000 pixels of image data.

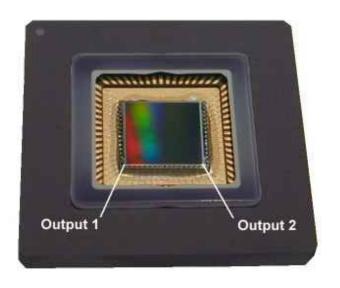

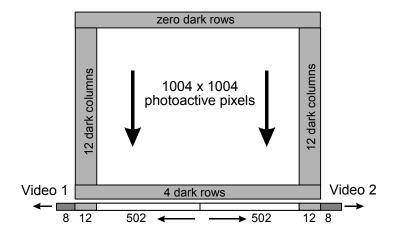

In the dual output mode the clocking of the right half of the horizontal CCD is reversed. The left half of the image is clocked out Video 1 and the right half of the image is clocked out Video 2. Each row consists of 8 empty pixels followed by 12 light shielded pixels followed by 502 photosensitive pixels. When reconstructing the image, data from Video 2 will have to be reversed in a line buffer and appended to the Video 1 data.

#### PHYSICAL DESCRIPTION

#### Pin Description and Device Orientation

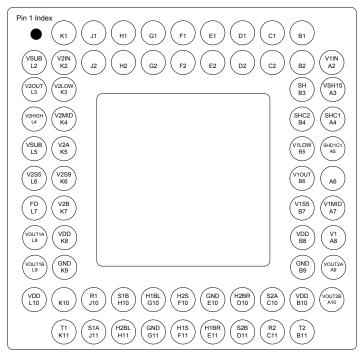

#### Pin Grid Array

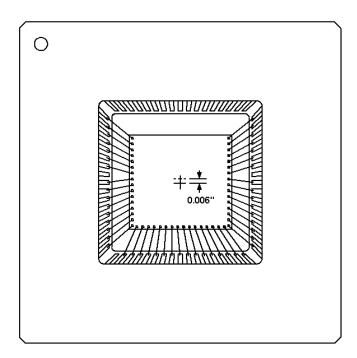

When viewed from the top with the pin 1 index to the upper left, the center of the photoactive pixel array is offset 0.006" above the physical center of the package. The pin 1 index is located in the corner of the package above pins L2 and K1. When operated in single output mode the first pixel out of the sensor will be in the corner closest to VOUT1B (pin L9). The HCCD is parallel to the row of pins A10 to L10. In the pictures below, the VCCD transfers charge down.

## Pin Grid Array Pin Description

Top View

| Label  | Pin | Function                              |

|--------|-----|---------------------------------------|

| V2IN   | K2  | VCCD gate phase 2 input               |

| VSUB   | L2  | substrate voltage input               |

| V2LOW  | K3  | VCCD phase 2 clock driver low         |

| V20UT  | L3  | VCCD phase 2 clock driver output      |

| V2MID  | K4  | VCCD phase 2 clock driver mid         |

| V2HIGH | L4  | VCCD phase 2 clock driver high        |

| φV2A   | K5  | VCCD phase 2 clock driver input A     |

| VSUB   | L5  | substrate voltage input               |

| V2S9   | K6  | VCCD phase 2 clock driver +9V         |

| V2S5   | L6  | VCCD phase 2 clock driver +5V         |

|        | LO  | fast dump clock driver +5V            |

| φV2B   | K7  | VCCD phase 2 clock driver input B     |

| φFD    | L7  | fast dump clock driver input          |

| VDD1   | K8  | Video 1 CDS +15V                      |

| VOUT1A | L8  | Video 1 CDS output A                  |

| GND    | K9  | Ground (0V)                           |

| VOUT1B | L9  | Video 1 CDS output B                  |

| VDD1   | L10 | Video 1 CDS +15V supply               |

| φT1    | K11 | Video 1 CDS transfer clock input      |

| φR1    | J10 | Video 1 CDS reset clock input         |

| φS1A   | J11 | Video 1 CDS sample A clock input      |

| φS1B   | H10 | Video 1 CDS sample B clock input      |

| φH2BL  | H11 | HCCD left phase 2 barrier clock input |

| φH1BL  | G10 | HCCD left phase 1 barrier clock input |

| GND    | G11 | Ground (0V)                           |

| φH2S   | F10 | HCCD storage phase 2 clock input      |

| All pins not list | ed must be | unconnected. |

|-------------------|------------|--------------|

|-------------------|------------|--------------|

| Label  | Pin | Function                               |

|--------|-----|----------------------------------------|

| φH1S   | F11 | HCCD storage phase 1 clock input       |

| GND    | E10 | Ground (0V)                            |

| φH1BR  | E11 | HCCD right phase 1 barrier clock input |

| φH2BR  | D10 | HCCD right phase 2 barrier clock input |

| φS2B   | D11 | Video 2 CDS sample B clock input       |

| φS2A   | C10 | Video 2 CDS sample A clock input       |

| φR2    | C11 | Video 2 CDS reset clock input          |

| φT2    | B11 | Video 2 CDS transfer clock input       |

| VDD2   | B10 | Video 2 CDS +15V                       |

| VOUT2B | A10 | Video 2 CDS output B                   |

| GND    | B9  | Ground (0V)                            |

| VOUT2A | Α9  | Video 2 CDS output A                   |

| VDD2   | B8  | Video 2 CDS +15V                       |

| φV1    | A8  | VCCD phase 1 clock driver input        |

| V1S5   | В7  | VCCD phase 1 clock driver +5V          |

| V1MID  | Α7  | VCCD phase 1 clock driver mid          |

| V10UT  | B6  | VCCD phase 1 clock driver output       |

| V1L0W  | B5  | VCCD phase 1 clock driver low          |

| SHD1C1 | A5  | shutter driver connection              |

| SHC2   | B4  | shutter driver connection              |

| SHC1   | A4  | shutter driver connection              |

| φSH    | B3  | shutter driver clock input             |

| VSH15  | А3  | shutter driver +15V                    |

| V1IN   | A2  | VCCD gate phase 1 input                |

|        |     |                                        |

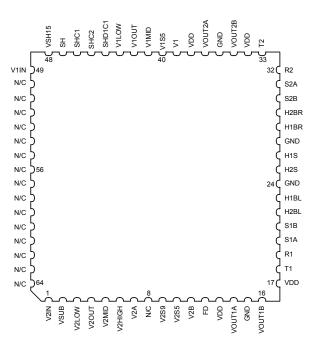

## Leadless Chip Carrier

Top View

| Pin                             | Description |  |  |

|---------------------------------|-------------|--|--|

| 1                               | V2IN        |  |  |

| 2                               | VSUB        |  |  |

| 3                               | V2LOW       |  |  |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | V20UT       |  |  |

| 5                               | V2MID       |  |  |

| 6                               | V2HIGH      |  |  |

| 7                               | V2A         |  |  |

| 8                               | No Connect  |  |  |

| 9                               | V2S9        |  |  |

| 10                              | V2S5        |  |  |

| 11                              | V2B         |  |  |

| 12                              | FD          |  |  |

| 13                              | VDD         |  |  |

| 14                              | VOUT1A      |  |  |

| 15                              | GND         |  |  |

| 16                              | VOUT1B      |  |  |

| 17                              | VDD         |  |  |

| 18                              | T1          |  |  |

| 19                              | R1          |  |  |

| 20                              | S1A         |  |  |

| 21                              | S1B         |  |  |

| 22                              | H2BL        |  |  |

| 23                              | H1BL        |  |  |

| 24                              | GND         |  |  |

| 50-64                           | No Connect  |  |  |

| Pin | Description |