### INTEL OverDrive™ PROCESSORS

- Powerful Performance Boosters for Intel486™ Microprocessor-Based Systems

- Improve Overall System

Performance by up to 70%

- Increase Both Integer and Floating-Point Performance

- Provides Next Level of CPU

Performance

- Intel486 DX2 OverDrive Processors Upgrade Systems Based on

- Intel486™ SX CPUs

- Intel486™ DX CPUs

- Binary Compatible with Large Installed Software Base

- -- MS-DOS\*, OS/2\*, Windows\*

- UNIX\* System V/386

- iRMX®, iRMK Kernals

290436-20

Intel OverDrive processors are powerful, single-chip upgrades for Intel486 microprocessor-based systems. The Intel486 DX2 OverDrive processor upgrades Intel486 SX and DX CPU-based systems with Intel486 DX2's "speed doubling" technology. OverDrive processors accelerate integer and math performance, delivering an overall performance boost of up to 70 percent. Users see a performance boost for all DOS, Windows, OS/2 and UNIX applications from AutoCAD\* to WordPerfect\*.

<sup>\*</sup>Other brands and names are the property of their respective owners.

### Intel OverDrive™ Processors

| CONTENTS                                               | PAGE             | CONTENTS                                              | PAGE    |

|--------------------------------------------------------|------------------|-------------------------------------------------------|---------|

| 1.0 INTRODUCTION                                       | 3-3              | 5.0 ELECTRICAL DATA                                   | 3-26    |

| 1.1 Product Overview                                   | 3-3              | 5.1 Power and Grounding                               | 3-26    |

| 1.2 Intel486 DX2 OverDrive Pr                          |                  | 5.2 Maximum Ratings                                   | 3-26    |

| for Intel486 SX and DX CPU                             |                  | 5.3 D.C. Specifications                               | 3-27    |

| Systems                                                |                  | 5.4 A.C. Specifications                               | 3-27    |

| for Replacement in PGA Into<br>CPU-Based Systems       | el486 DX         | 6.0 MECHANICAL DATA                                   | 3-36    |

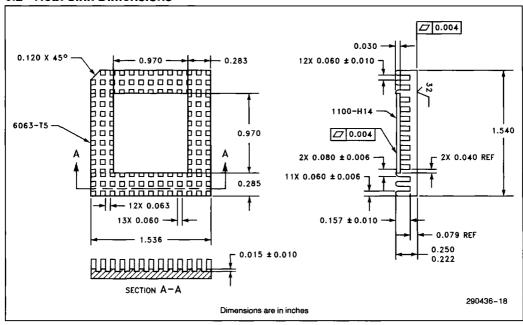

| 1.4 Pin Descriptions                                   |                  | 6.1 Package Dimensions                                |         |

| 1.5 Intel486 DX2 OverDrive Pr                          |                  | 6.2 Heat Sink Dimensions .                            | 3-37    |

| Block Diagram                                          |                  | 7.0 THERMAL MANAGEMENT                                | 3-38    |

| 2.0 DIFFERENCES FROM INTER<br>AND INTEL486 DX CPU      |                  | 7.1 The Intel OverDrive™ Pr with Attached Heat Sink . |         |

| FUNCTIONALITY                                          |                  | 7.2 The Intel OverDrive™ Pr                           | ocessor |

| 2.1 Hardware Interface :                               |                  | without Heat Sink                                     |         |

| 2.2 Testability                                        | 3-20             | 7.3 Thermal Equations                                 | 3-39    |

| 2.3 Instruction Set Summary .                          | 3-20             | APPENDIX A:                                           |         |

| 3.0 Intel OverDrive™ PROCES:<br>CIRCUIT DESIGN         | 3-22             | "END USER EASY" UPGRADABILITY                         | 3-41    |

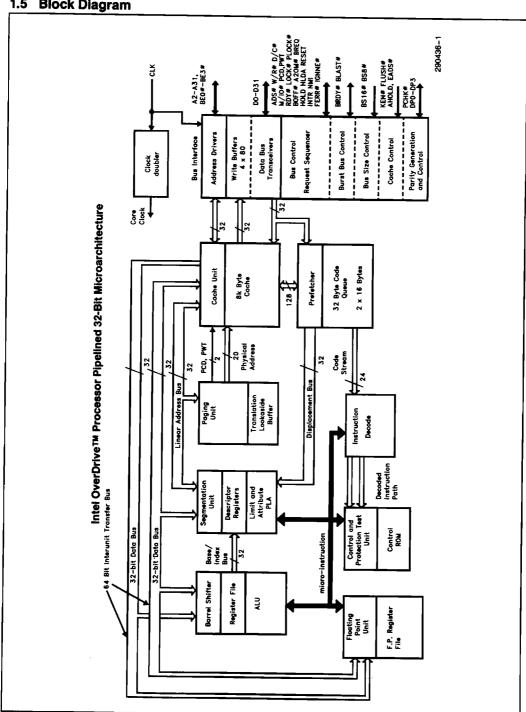

| 3.1 Upgrade Circuit for PGA In<br>DX CPU-Based Systems | itel486<br>3-22  | APPENDIX B:                                           |         |

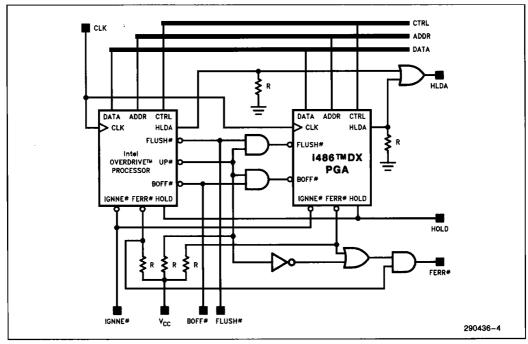

| 3.2 Upgrade Circuit for PGA In SX CPU-Based Systems    | itel486          | ZIF AND LIF SOCKET VENDO                              | PS 3-42 |

| 3.3 Upgrade Circuit for PQFP SX CPU-Based Systems      | intel486<br>3-24 |                                                       |         |

| 4.0 BIOS AND SOFTWARE                                  | 3-25             |                                                       |         |

| 4.1 Intel OverDrive™ Process<br>Detection              |                  |                                                       |         |

| 4.2 Timing Dependent Loops                             | 3-25             |                                                       |         |

#### 1.0 INTRODUCTION

This data sheet describes the Intel486 DX2 OverDrive processor. The Intel486 DX2 OverDrive processor is designed as an end-user upgrade for Intel486 SX and Intel486 DX CPU-based systems. This data sheet is intended to be used with the data sheet for the original CPU in the system-the Intel486 SX or Intel486 DX CPU-which describes the Intel486 Family Architecture and functionality. All enhancements or differences in the Intel486 DX2 OverDrive processor from the Intel486 SX or Intel486 DX CPU are described in this data sheet. Intel486 SX or Intel486 DX CPU-based systems that are compatible to the Intel OverDrive processor must be designed to both the original CPU specifications and the Intel OverDrive processor specifications.

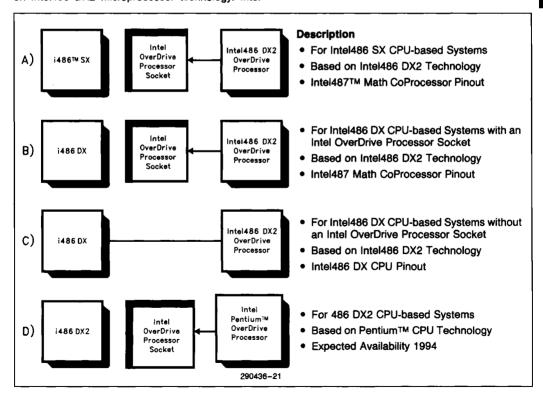

available in two basic product variants. The first product variant (ODP), shown in Figures 1A and 1B, is referred to as the OverDrive processor for Intel486 SX and DX CPU-based systems that have an OverDrive processor socket. This product, ODP, is described specifically in Section 1.2.

OverDrive processor are designed as a single-chip.

powerful performance booster for Intel486 Micro-

The Intel486 DX2 OverDrive processor is currently

processor-based systems.

The second i486 DX2 OverDrive processor variant (ODPR), shown in Figure 1C, is referred to as the OverDrive processor for Intel486 DX CPU-based systems that do not have an OverDrive processor socket. This product is designed to replace the Intel486 DX CPU in systems that do not have an "End-User Easy" OverDrive processor socket. Section 1.3 describes this product variant, ODPR.

#### 1.1 Product Overview

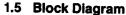

The Intel486 DX2 OverDrive processor is based on Intel486 DX2 Microprocessor technology, Intel

PRELIMINARY

- 1.2 Intel486 DX2 OverDrive™ Processor for Intel486™ SX and DX Microprocessor-Based Systems (with an OverDrive™ Processor Socket)

- Powerful Performance Booster for Intel486™ SX and DX CPU-Based Systems

- Improves Overall System

Performance by up to 70%

- Increases Both Integer and Floating-Point Performance

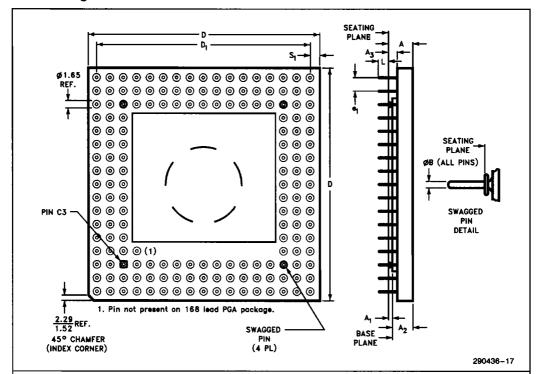

- 169-Lead Pin Grid Array Package

- Pin Compatible with Intel487™ SX Math CoProcessor

- "End-User Easy", Single-Chip Upgrade

- 169th Alignment Pin Ensures Proper Chip Orientation

- Math CoProcessor Included On-Chip

- High Integration Enables On-Chip

- 8 Kbyte Code and Data Cache

- Floating Point Unit

- Paged, Virtual Memory Management

- Utilizes Intel486™ DX2 Speed-Doubling Technology

- CPU Core Runs at Twice the Frequency of the System Bus

- Compatible with 33, 25, 20, and 16 MHz Systems

- Binary Compatible with Large Installed Software Base

- MS-DOS, OS/2, Windows

- UNIX System V/386

- iRMX®, iRMK Kernals

- **■** High Performance Design

- Core Clock Speed up to 66 MHz

- 106 Mbyte/sec Burst Bus

- CHMOS V Process Technology

- **■** Complete 32-Bit Architecture

- Address and Data Busses

- Registers

- -- 8-, 16-, 32-Bit Data Types

- Compatible with Intel SL Enhanced Features

The Intel486 DX2 OverDrive processor for Intel486 SX and DX microprocessor-based personal computers is a powerful, single-chip upgrade that is intrinsically cost effective and that offers excellent price/performance. Based on Intel486 DX2 technology, the Intel OverDrive processor integrates an integer unit, a floating point unit, a memory management unit, SL Enhanced features, and an 8 Kbyte cache on a single chip.

Using the Intel486 DX2's "speed doubling" technology, the Intel OverDrive processor operates internally at twice the speed of the system bus. This allows users of Intel486 SX and DX microprocessor-based systems to double the frequency of their computer's CPU by adding a single chip, without upgrading or modifying any other system components. For example, adding an Intel 486 DX2 OverDrive processor to an Intel486 DX 33 MHz system will double the CPUs internal operating speed to 66 MHz. Depending on the application, the OverDrive processor can provide an overall system performance boost of up to 70%.

The Intel486 DX2 OverDrive processor (ODP) is designed to be installed in the OverDrive processor socket of Intel486 microprocessor-based systems. In Intel486 SX systems, this is the same socket that was designed for the Intel487<sup>TM</sup> SX Math CoProcessor.

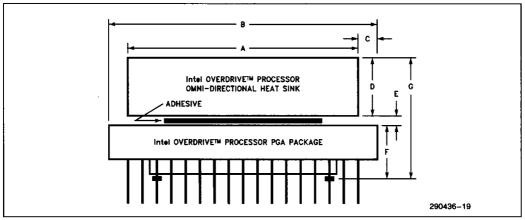

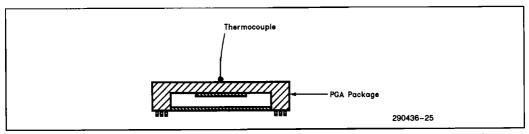

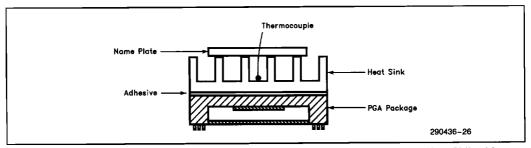

The Intel486 DX2 OverDrive processor is available in three product versions. The 20 MHz Intel OverDrive processor is designed to upgrade both 20 MHz and 16 MHz Intel486 SX Microprocessor-based systems. This product utilizes the standard 169-lead PGA package. The 25 MHz and 33 MHz

Intel OverDrive processor is designed to upgrade 25 MHz and 33 MHz Intel486 SX or DX Microprocessor-based systems. This product has a heat sink attached to the standard 169-lead PGA package to aid in the heat dissipation in 25 MHz and 33 MHz systems.

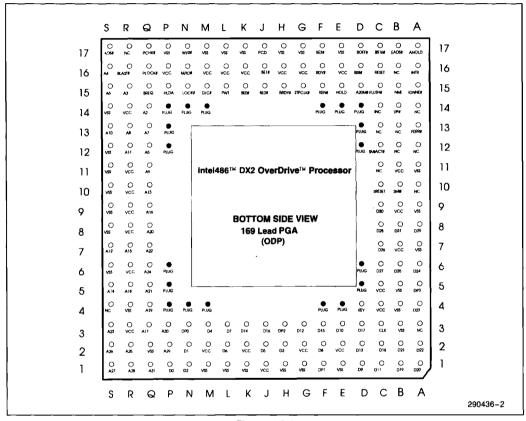

#### 1.2.1 Pinout

Figure 1.2.1

Figure 1.2.2

Table 1.2. Pin Cross Reference by Pin Name (ODP)

| Add                                                                                                                  | ress                                                                                                 | Da                                                                              | ıta                                                                                       | Contre                                                                                                                                                                    | ol                                                                                                                                                                                                       | N/C(1)                                                                                                | Vcc                                                                                                                                          | Vss                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Add  A2 A3 A4 A5 A6 A7 A8 A9 A10 A11 A12 A13 A14 A15 A16 A17 A18 A19 A20 A21 A22 A23 A24 A25 A26 A27 A28 A29 A30 A31 | Q14 R15 S16 Q12 S15 Q13 R13 Q11 S13 R12 S7 Q10 S5 R7 Q9 Q3 R5 Q4 Q8 Q5 Q7 S3 Q6 R2 S2 S1 R1 P2 P3 Q1 | Da  Do  Do  Do  Do  Do  Do  Do  Do  Do                                          | P1 N2 N1 H2 M3 J2 L3 F2 D1 E3 C1 G3 D2 K3 F3 J3 D3 C2 B1 A1 B2 A4 A6 B6 C7 C6 C8 A8 C9 B8 | A20M# ADS# AHOLD BE0# BE1# BE2# BE3# BLAST# BOFF# BRDY# BREQ# BS8# BS16# CLK D/C# DP0 DP1 DP2 DP3 EADS# FERR# FLUSH# HLDA HOLD IGNNE# INTR KEN# LOCK# M/IO# NMI PCD PCHK# | D15<br>S17<br>A17<br>K15<br>J16<br>J15<br>F17<br>R16<br>D17<br>C3<br>M15<br>D16<br>C17<br>C3<br>M15<br>N3<br>F1<br>H3<br>A5<br>B17<br>A13<br>C15<br>E15<br>A16<br>F15<br>N16<br>B17<br>N16<br>D17<br>D17 | A10 A12 A14 B12 B13 C13 R17 S4 A3 B16 C11  INC(2) C14  PLUG D5 D6 D12 D13 D14 E4 E14 F4 F14 M4 M14 N4 | Vcc<br>B7<br>B9<br>B11<br>C4<br>C5<br>E16<br>G16<br>H16<br>J1<br>K16<br>L16<br>M2<br>M16<br>P16<br>R3<br>R6<br>R8<br>R9<br>R10<br>R11<br>R14 | Vss A7 A9 A11 B3 B4 B5 E1 E17 G1 G17 H1 H17 K1 K17 L1 L17 M1 M17 P17 Q2 R4 S6 S8 S9 S10 S11 S12 S14 |

| A <sub>27</sub><br>A <sub>28</sub><br>A <sub>29</sub><br>A <sub>30</sub>                                             | R1<br>P2<br>P3                                                                                       | D <sub>26</sub> D <sub>27</sub> D <sub>28</sub> D <sub>29</sub> D <sub>30</sub> | C7<br>C6<br>C8<br>A8<br>C9                                                                | KEN#<br>LOCK#<br>M/IO#<br>NMI<br>PCD                                                                                                                                      | F15<br>N15<br>N16<br>B15<br>J17                                                                                                                                                                          | E4<br>E14<br>F4<br>F14<br>M4<br>M14                                                                   |                                                                                                                                              | S12                                                                                                 |

All NC pins must remain unconnected.

The INC pin is defined to be an internal no-connect. This means that the pin is not internally connected and may be used for the routing of external signals.

- 1.3 Intel486 DX2 OverDrive™ Processor for PGA Intel486™ DX Microprocessor-Based Systems (without an OverDrive™ Processor Socket)

- Powerful Performance Booster for PGA Intel486™ DX CPU-Based Systems

- improves Overall System Performance by up to 70%

- Increases Both Integer and Floating-Point Performance

- 168-Lead Pin Grid Array Package

- Pin Compatible with Intel486™ DX CPU

- Math CoProcessor Included On-Chip

- High Integration Enables On-Chip

- -8 Kbyte Code and Data Cache

- Floating Point Unit

- Paged, Virtual Memory Management

- Compatible with SL Enhanced Features

- Utilizes Intel486™ DX2 Speed-Doubling Technology

- CPU Core Runs at Twice the Frequency of the System Bus

- Compatible with 33 and 25 MHz Systems

- Binary Compatible with Large Installed Software Base

- MS-DOS, OS/2, Windows

- UNIX System V/386

- iRMX®, iRMK Kernals

- **■** High Performance Design

- -Core Clock Speed up to 66 MHz

- 106 Mbyte/sec Burst Bus

- CHMOS V Process Technology

- **Complete 32-Bit Architecture**

- Address and Data Busses

- Registers

- 8-, 16-, 32-Bit Data Types

The Intel486 DX2 OverDrive processor for Intel486 DX microprocessor-based personal computers is a powerful, single-chip upgrade that is intrinsically cost effective and that offers excellent price/performance. Based on Intel486 DX2 technology, the Intel OverDrive processor integrates an integer unit, a floating point unit, a memory management unit and an 8 Kbyte cache on a single chip.

Using the Intel486 DX2's "speed doubling" technology, the Intel OverDrive processor operates internally at twice the speed of the system bus. This allows users of Intel486 DX microprocessor-based systems to double the frequency of their computer's CPU by replacing a single chip, without upgrading or modifying any other system components. For example, adding an Intel486 DX2 OverDrive processor to an Intel486 DX 33 MHz system will double the CPUs internal operating speed to 66 MHz. Depending on the application, the OverDrive processor can provide an overall system performance boost of up to 70%.

The Intel486 DX2 OverDrive processor, ODPR, is designed to be installed in the Intel486 DX CPU socket after the Intel486 DX CPU has been removed.

Both the 25 MHz and 33 MHz versions of the OverDrive processor for Intel486 DX CPU-based Systems without an OverDrive processor socket have a heat sink attached to the standard 168-lead PGA package.

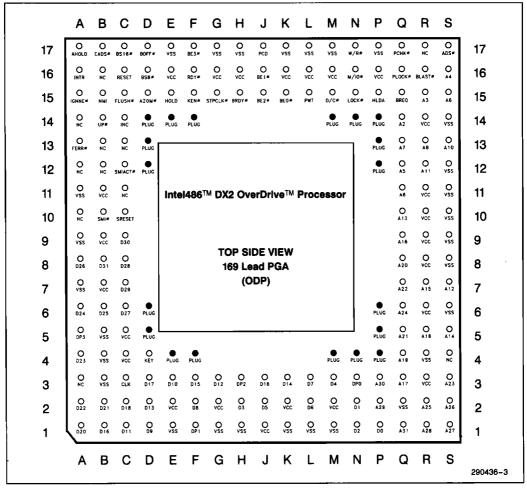

1.3.1 Pinout

|   | 1        | 2         | 3        | 4        | 5                 | 6        | 7        | 8        | 9             | 10                 | 11       | 12       | 13       | 14       | 15          | 16         | 17            |     |

|---|----------|-----------|----------|----------|-------------------|----------|----------|----------|---------------|--------------------|----------|----------|----------|----------|-------------|------------|---------------|-----|

| s | A27<br>O | A25<br>O  | A23<br>O | NC<br>O  | A14<br>O          | vss      | A12<br>O | vss      | vss           | vss                | vss<br>O | vss<br>O | A10<br>O | vss<br>O | A6<br>O     | A4<br>O    | ADS#          | s   |

| R | A28<br>O | A25<br>O  | vcc<br>O | vss<br>O | A18<br>O          | vcc<br>O | A15<br>O | vcc      | VCC<br>O      | vcc<br>O           | vcc<br>O | A11<br>O | A8<br>O  | vcc<br>O | A3<br>O     | BLAST#     |               | R   |

| Q | A31<br>O | vss<br>O  | A17<br>O | A19<br>O | A21<br>O          | A24<br>O | A22<br>O | A20<br>O | A 16<br>O     | A13                | A9<br>O  | A5<br>O  | A7<br>O  | A2<br>O  | BREQ<br>O   | PLOCK#     | PCHK#         | Q   |

| P | D0<br>O  | A29<br>O  | A30<br>O |          |                   |          |          |          |               |                    |          |          |          |          | HLDA<br>O   | vcc<br>O   | vss<br>O      | Р   |

| N | D2<br>O  | D1<br>O   | DP0<br>O |          |                   |          |          |          |               |                    |          |          |          |          | LOCK*       | M/10#<br>O | W/R#<br>O     | N   |

| М | vss<br>O | vcc<br>O  | D4<br>O  |          |                   |          |          |          |               |                    |          |          |          |          | D/C#<br>O   | vcc<br>O   | vss<br>O      | м   |

| L | vss<br>O | D6<br>O   | D7<br>O  |          |                   |          |          |          |               |                    |          |          |          |          | PWT<br>O    | vcc<br>O   | vss<br>O      | L   |

| K | vss<br>O | vcc<br>O  | D14<br>O |          | Int               | tel 48   | 6™       | DX2      | Over          | Drive <sup>1</sup> | M Pı     | rocess   | sor      |          | BEO#        | VCC<br>O   | vss<br>O      | к   |

| J | VCC<br>O | D5<br>O   | D16<br>O |          |                   |          | ,        |          |               | VIEW               |          |          |          |          | BE2#        | BE1#       | PCD<br>O      | J   |

| Н | vss<br>O | D3<br>O   | DP2<br>O |          |                   |          | (        |          | -LEA<br>(ODP) | D PGA<br>R)        | ()       |          |          |          | BRDY#       | vcc<br>O   | vss<br>O      | н   |

| G | vss<br>O | vcc<br>O  | D12<br>O |          |                   |          |          |          |               | •                  |          |          |          |          | STPCLK<br>O | # VCC      | O<br>VSS      | G   |

| F | DP1<br>O | 08<br>O   | D15<br>O |          |                   |          |          |          |               |                    |          |          |          |          | KEN#        | RDY#       | BE3#<br>O     | F   |

| E | vss<br>O | vcc<br>O  | OIO<br>O |          |                   |          |          |          |               |                    |          |          |          |          | HOLD        | VCC<br>O   | vss<br>O      | E   |

| ם | D9<br>O  | D13<br>O  | 017<br>O |          |                   |          |          |          |               |                    |          |          |          |          | 0           | BS8#       | BOFF#         | D   |

| С | D11<br>O | D18<br>O  | O CLK    | VCC<br>O | VCC               | 027<br>O | D26      | D28      | 030           | SRESET             | NC<br>O  | SMIACT#  | 0        | 0        | 0           | * RESET    | 0             | С   |

| В | D19<br>O | D2 1<br>O | vss<br>O | vss<br>O | v <b>s</b> s<br>O | D25<br>O | VCC<br>O | D31      | VCC<br>O      | SMI#               | VCC<br>O | NC<br>O  | NC<br>O  | NC<br>O  | O           | NC<br>O    | EADS#         | В   |

| A | D20<br>O | D22<br>O  | NC<br>O  | D23<br>O | DP3<br>O          | D24<br>O | vss<br>O | D29<br>O | vss<br>O      | NC<br>O            | vss<br>O | NC<br>O  | O        | NC<br>O  | IGNNE#      | O          | AHOLD<br>O    | Α   |

|   | 1        | 2         | 3        | 4        | 5                 | 6        | 7        | 8        | 9             | 10                 | 11       | 12       | 13       | 14       | 15          | 16         | 1 7<br>290436 | -22 |

Figure 1.3.1

|   | 17            | 16            | 15             | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2         | 1           |      |

|---|---------------|---------------|----------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|-----------|-------------|------|

| s | ADS#          | A4<br>O       | A6<br>O        | vss<br>O | A10<br>O | vss<br>O | vss      | vss<br>O | vss<br>O | vss      | A12<br>O | vss<br>O | A14<br>O | NC<br>O  | A23<br>O | A26<br>O  | A27<br>O    | s    |

| R | NC<br>O       | BLAST#        | A3<br>O        | vcc<br>O | A8<br>O  | A11<br>O | vcc      | vcc<br>O | vcc<br>O | vcc<br>O | A15<br>O | vcc<br>O | A18<br>O | vss<br>O | vcc<br>O | A25<br>O  | A28<br>O    | R    |

|   | PCHK#         | PLOCK#        | BREQ           | A2<br>O  | A7       | A5<br>O  | A9<br>O  | A13<br>O | A16<br>O | A20<br>O | A22<br>O | A24<br>O | A21<br>O | A19<br>O | A17<br>O | vss       | A31<br>O    | Q    |

| P | O<br>VSS<br>O | O<br>VCC<br>O | O<br>HLDA<br>O | U        | 0        | U        | U        | O        | Ü        | Ü        | Ü        | Ü        | O        | Ü        | A30<br>O | A29<br>O  | D0<br>O     | Р    |

| N | W/R#          | w/10#<br>O    | LOCK#          |          |          |          |          |          |          |          |          |          |          |          | DP0<br>O | D1<br>O   | D2<br>O     | N    |

| М | vss           | vcc<br>O      | D/C#           |          |          |          |          |          |          |          |          |          |          |          | D4<br>O  | VCC       | vss<br>O    | М    |

| L | vss           | vcc<br>O      | PWT<br>O       |          |          |          |          |          |          |          |          |          |          |          | 07<br>O  | D6        | vss<br>O    | L    |

| K | vss           | vcc<br>O      | BEO#           |          | In       | tel48    | 6™ !     | DX2 C    | )verl    | Drive    | ™ Pr     | oces     | sor      |          | D14<br>O | vcc<br>O  | vss<br>O    | Κ    |

| J | PCD<br>O      | BE1#          | BE2#           |          |          |          |          | TOP S    |          |          |          |          |          |          | D16<br>O | D5<br>O   | vcc<br>O    | J    |

| Н | vss           | vcc           | BRDY#          |          |          |          | (        | 168-     |          |          | A)       |          |          |          | DP2<br>O | D3<br>O   | vss         | н    |

| G | vss           |               | STPCLK#        |          |          |          |          | (        | ODPI     | ۲)       |          |          |          |          | D12<br>O | vcc       | vss         | G    |

| F | BE3#          | RDY#          | KEN#           |          |          |          |          |          |          |          |          |          |          |          | D15<br>O | D8<br>O   | DP1         | F    |

| E | vss           | VCC           | HOLD           |          |          |          |          |          |          |          |          |          |          |          | DIO      | VCC       | vss         | E    |

| D | BOFF#         | B\$8#         | A20M#          |          |          |          |          |          |          |          |          |          |          |          | D17<br>O | D13       | 09<br>O     | D    |

| c | O<br>BS16#    |               | O<br>FLUSH#    |          | NC       | SMIACT#  | NC<br>O  | SRESET   | D30<br>O | D28<br>O | D26<br>O | D27<br>O | vcc      | vcc      | CLK      | D18       | D11<br>O    | С    |

| В | EADS#         | O<br>NC       | O<br>NMI       | O<br>NC  | O<br>NC  | O<br>NC  | vcc      | SMI#     | vcc      | D31      | VCC      | D25      | VSS      | vss      | vss      | D2 1<br>O | D19<br>O    | В    |

| A | O<br>AHOLD    | O<br>INTR     | O<br>IGNNE#    | O<br>NC  | O        | O<br>NC  | O<br>vss | O<br>NC  | VSS      | O<br>D29 | vss      | O<br>D24 | DP3      | D23      | NC       | D22       | D20         | J ,  |

| ~ | ٥             | 0             | 0              |          | 0        | 0        | 0        | 0        | 0        | 0        |          | 0        |          | 0        | 0        | 0         |             |      |

|   | 17            | 16            | 15             | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2         | 1<br>290436 | 5-23 |

Figure 1.3.2

Table 1.3. Pin Cross Reference by Pin Name (ODPR)

|                 | lean       |                 |    | Contro  | · 1 | N/C <sup>(1)</sup> | V   | Van             |

|-----------------|------------|-----------------|----|---------|-----|--------------------|-----|-----------------|

| Add             | lress      | Da              |    | Contro  |     |                    | Vcc | V <sub>SS</sub> |

| A <sub>2</sub>  | Q14        | $D_0$           | P1 | A20M#   | D15 | A3                 | B7  | A7              |

| A <sub>3</sub>  | R15        | D <sub>1</sub>  | N2 | ADS#    | S17 | A10                | B9  | A9              |

| A <sub>4</sub>  | S16        | D <sub>2</sub>  | N1 | AHOLD   | A17 | A12                | B11 | A11             |

| A <sub>5</sub>  | Q12        | Dз              | H2 | BEO#    | K15 | A14                | C4  | B3              |

| A <sub>6</sub>  | S15        | D <sub>4</sub>  | М3 | BE1#    | J16 | B12                | C5  | B4              |

| A <sub>7</sub>  | Q13        | D <sub>5</sub>  | J2 | BE2#    | J15 | B13                | E2  | B5              |

| A <sub>8</sub>  | R13        | D <sub>6</sub>  | L2 | BE3#    | F17 | B14                | E16 | E1              |

| A <sub>9</sub>  | Q11        | D <sub>7</sub>  | L3 | BLAST#  | R16 | B16                | G2  | E17             |

| A <sub>10</sub> | S13        | Dg              | F2 | BOFF#   | D17 | C11                | G16 | G1              |

| A <sub>11</sub> | R12        | D <sub>9</sub>  | D1 | BRDY#   | H15 | C13                | H16 | G17             |

| A <sub>12</sub> | S7         | D <sub>10</sub> | E3 | BREQ#   | Q15 | R17                | J1  | H1              |

| A <sub>13</sub> | Q10        | D <sub>11</sub> | C1 | BS8#    | D16 | S4                 | K2  | H17             |

| A <sub>14</sub> | S5         | D <sub>12</sub> | G3 | BS16#   | C17 |                    | K16 | K1              |

| A <sub>15</sub> | R7         | D <sub>13</sub> | D2 | CLK     | C3  |                    | L16 | K17             |

| A <sub>16</sub> | Q9         | D <sub>14</sub> | K3 | D/C#    | M15 | INC(2)             | M2  | L1              |

| A <sub>17</sub> | Q3         | D <sub>15</sub> | F3 | DP0     | N3  |                    | M16 | L17             |

| A <sub>18</sub> | R5         | D <sub>16</sub> | J3 | DP1     | F1  | A13                | P16 | M1_             |

| A <sub>19</sub> | Q4         | D <sub>17</sub> | D3 | DP2     | НЗ  |                    | R3  | M17             |

| A <sub>20</sub> | Q8         | D <sub>18</sub> | C2 | DP3     | A5  |                    | R6  | P17             |

| A <sub>21</sub> | Q5         | D <sub>19</sub> | B1 | EADS#   | B17 |                    | R8  | Q2              |

| A <sub>22</sub> | Q7         | D <sub>20</sub> | A1 | FERR#   | C14 |                    | R9  | R4              |

| A <sub>23</sub> | <b>S</b> 3 | D <sub>21</sub> | B2 | FLUSH#  | C15 |                    | R10 | S6              |

| A <sub>24</sub> | Q6         | D <sub>22</sub> | A2 | HLDA    | P15 |                    | R11 | S8              |

| A <sub>25</sub> | R2         | D <sub>23</sub> | A4 | HOLD    | E15 |                    | R14 | S9              |

| A <sub>26</sub> | S2         | D <sub>24</sub> | A6 | IGNNE#  | A15 |                    | Į   | S1.0            |

| A <sub>27</sub> | S1         | D <sub>25</sub> | B6 | INTR    | A16 |                    |     | S11             |

| A <sub>28</sub> | R1         | D <sub>26</sub> | C7 | KEN#    | F15 |                    |     | S12             |

| A <sub>29</sub> | P2         | D <sub>27</sub> | C6 | LOCK#   | N15 | ļ                  |     | S14             |

| A <sub>30</sub> | P3         | D <sub>28</sub> | C8 | M/IO#   | N16 |                    |     |                 |

| A <sub>31</sub> | Q1         | D <sub>29</sub> | A8 | NMI     | B15 | ļ                  |     |                 |

|                 |            | D <sub>30</sub> | C9 | PCD     | J17 |                    |     | Į l             |

|                 |            | D <sub>31</sub> | B8 | PCHK#   | Q17 |                    |     |                 |

|                 |            |                 |    | PWT     | L15 |                    |     |                 |

|                 |            |                 |    | PLOCK#  | Q16 |                    |     |                 |

|                 |            |                 |    | RDY#    | F16 | <b>,</b>           |     |                 |

| 1               |            |                 |    | RESET   | C16 |                    |     |                 |

|                 |            |                 |    | SMI#    | B10 |                    |     |                 |

|                 |            |                 |    | SMIACT# | C12 |                    | ĺ   |                 |

|                 |            |                 |    | SRESET  | C10 | l                  |     | 1               |

|                 |            |                 |    | STPCLK# | G15 |                    |     |                 |

|                 |            |                 |    | W/R#    | N17 |                    | 1   |                 |

#### NOTES:

All NC pins must remain unconnected.

The INC pin is defined to be internal no-connect. This means that the pin is not internally connected and may be used for the routing of external signals.

#### INTEL OverDriveTM PROCESSORS

#### 1.4 PIN DESCRIPTIONS

What follows is a brief pin description.

| Symbol          | Туре     | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CLK             |          | Clock provides the fundamental timing for the bus interface unit and is multiplied by two (2x) to provide the internal frequency for the intel OverDrive processor. All external timing parameters are specified with respect to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| ADDRESS         | BUS      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| A31-A4<br>A2-A3 | 1/0<br>0 | A31-A2 are the address lines of the processor. A31-A2, together with the byte enables BE0#-BE3#, define the physical area of memory or input/output space accessed. Address lines A31-A4 are used to drive addresses into the processor to perform cache line invalidations. Input signals must meet setup and hold times t <sub>22</sub> and t <sub>23</sub> . A31-A2 are not driven during bus or address hold.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| BE0-3#          | 0        | The byte enable signals indicate active bytes during read and write cycles. During the first cycle of a cache fill, the external system should assume that all byte enables are active. BE3# applies to D24-D31, BE2# applies to D16-D23, BE1# applies to D8-D15 and BE0# applies to D0-D7. BE0#-BE3# are active LOW and are not driven during bus hold.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| DATA BUS        | DATA BUS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| D31-D0          | 1/0      | These are the data lines for the Intel OverDrive processor. Lines D0-D7 define the least significant byte of the data bus while lines D24-D31 define the most significant byte of the data bus. These signals must meet setup and hold times t22 and t23 for proper operation on reads. These pins are driven during the second and subsequent clocks of write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| DATA PAR        | ITY      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

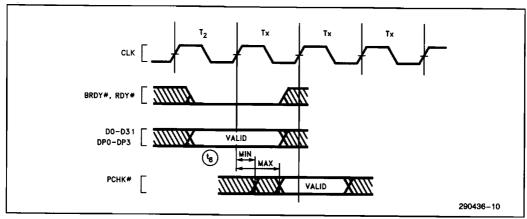

| DP0-DP3         | 1/0      | There is one <i>data parity</i> pin for each byte of the data bus. Data parity is generated on all write data cycles with the same timing as the data driven by the Intel OverDrive processor. Even parity information must be driven back into the microprocessor on the data parity pins with the same timing as read information to insure that the correct parity check status is indicated by the Intel OverDrive processor. The signals read on these pins do not affect program execution. Input signals must meet setup and hold times t <sub>22</sub> and t <sub>23</sub> . DP0-DP3 should be connected to V <sub>CC</sub> through a pullup resistor in systems which do not use parity. DP0-DP3 are active HIGH and are driven during the second and subsequent clocks of write cycles. |  |  |  |  |  |

| PCHK#           | 0        | Parity Status is driven on the PCHK# pin the clock after ready for read operations. The parity status is for data sampled at the end of the previous clock. A parity error is indicated by PCHK# being LOW. Parity status is only checked for enabled bytes as indicated by the byte enable and bus size signals. PCHK# is valid only in the clock immediately after read data is returned to the microprocessor. At all other times PCHK# is inactive (HIGH). PCHK# is never floated.                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Symbol        | Type    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               | Name and Function                                                                                                                                                 |  |  |  |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               | Туре    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               | Name and Function                                                                                                                                                 |  |  |  |

| BUS CYCL      | E DEFIN | ITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |               |                                                                                                                                                                   |  |  |  |

| M/IO#<br>D/C# | 0 0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               | ta/control and write/read lines are the primary bus als are driven valid as the ADS# signal is asserted.                                                          |  |  |  |

| W/R#          | 0       | M/IO#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | D/C#      | W/R#          | Bus Cycle Initiated                                                                                                                                               |  |  |  |

| ·             | ·       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0         | 0             | Interrupt Acknowledge                                                                                                                                             |  |  |  |

| 1             |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Q         | 1             | Halt/Special Cycle                                                                                                                                                |  |  |  |

|               |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1         | 0             | I/O Read                                                                                                                                                          |  |  |  |

|               |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1         | 1             | I/O Write                                                                                                                                                         |  |  |  |

|               |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0         | 0             | Code Read                                                                                                                                                         |  |  |  |

|               |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0         | 1             | Reserved                                                                                                                                                          |  |  |  |

|               |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1         | 0             | Memory Read                                                                                                                                                       |  |  |  |

|               |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1         | 1             | Memory Write                                                                                                                                                      |  |  |  |

|               |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               | not driven during bus hold and follow the timing of the 7.2.11 for a description of the special bus cycles.                                                       |  |  |  |

| LOCK#         | 0       | The bus lock pin indicates that the current bus cycle is locked. The Intel OverDrive processor will not allow a bus hold when LOCK# is asserted (but address holds are allowed). LOCK# goes active in the first clock of the first locked bus cycle and goes inactive after the last clock of the last locked bus cycle. The last locked cycle ends when RDY# is returned. LOCK# is active LOW and is not driven during bus hold. Locked read cycles will not be transformed into cache fill cycles if KEN# is returned active.                                                                                                                                                                                                                                                                              |           |               |                                                                                                                                                                   |  |  |  |

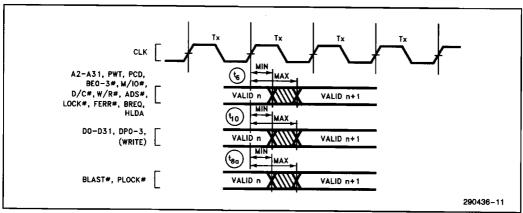

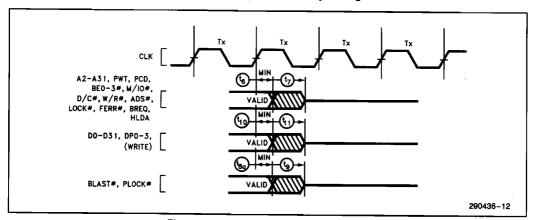

| PLOCK#        | 0       | The pseudo-lock pin indicates that the current bus transaction requires more than one bus cycle to complete. Examples of such operations are floating point long reads and writes (64 bits), segment table descriptor reads (64 bits), in addition to cache line fills (128 bits). The Intel OverDrive processor will drive PLOCK# active until the addresses for the last bus cycle of the transaction have been driven regardless of whether RDY# or BRDY# have been returned.  Normally PLOCK# and BLAST# are inverse of each other. However during the first bus cycle of a 64-bit floating point write, both PLOCK# and BLAST# will be asserted.  PLOCK# is a function of the BS8#, BS16# and KEN# inputs. PLOCK# should be sampled only in the clock RDY# is returned. PLOCK# is active LOW and is not |           |               |                                                                                                                                                                   |  |  |  |

| BUS CONT      | ROL     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |               |                                                                                                                                                                   |  |  |  |

| ADS#          | 0       | available                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | on the cy | cle definitio | licates that a valid bus cycle definition and address are on lines and address bus. ADS# is driven active in the are driven. ADS# is active LOW and is not driven |  |  |  |

| RDY#          | l       | The non-burst ready input indicates that the current bus cycle is complete. RDY # indicates that the external system has presented valid data on the data pins in response to a read or that the external system has accepted data from the Intel OverDrive processor in response to a write. RDY # is ignored when the bus is idle and at the end of the first clock of the bus cycle.  RDY # is active during address hold. Data can be returned to the processor while AHOLD is active.  RDY # is active LOW, and is not provided with an internal pullup resistor. RDY #                                                                                                                                                                                                                                 |           |               |                                                                                                                                                                   |  |  |  |

|               | L       | must sat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | sfy setup | and hold ti   | mes t <sub>16</sub> and t <sub>17</sub> for proper chip operation.                                                                                                |  |  |  |

PRELIMINARY 3-13

| Symbol   | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BURST CO | NTROL |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BRDY#    | 1     | The burst ready input performs the same function during a burst cycle that RDY # performs during a non-burst cycle. BRDY # indicates that the external system has presented valid data in response to a read or that the external system has accepted data in response to a write. BRDY # is ignored when the bus is idle and at the end of the first clock in a bus cycle.  BRDY # is sampled in the second and subsequent clocks of a burst cycle. The data presented on the data bus will be strobed into the microprocessor when BRDY # is sampled active. If RDY # is returned simultaneously with BRDY #, BRDY # is ignored and the burst cycle is prematurely interrupted  BRDY # is active LOW and is provided with a small pullup resistor. BRDY # must satisfy the setup and hold times t <sub>16</sub> and t <sub>17</sub> . |

| BLAST#   | 0     | The burst last signal indicates that the next time BRDY # is returned the burst bus cycle is complete. BLAST # is active for both burst and non-burst bus cycles. BLAST # is active LOW and is not driven during bus hold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| INTERRUP | TS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RESET .  | . 1   | The <b>RESET</b> input forces the CPU to begin execution at a known state. Reset is asynchronous, but must meet setup and hold times t20 and t21 for recognition in any specific clock. The CPU cannot begin execution of instructions until at least 1 ms after V <sub>CC</sub> and CLK have reached their proper AC and DC specifications. However, for soft resets, RESET should remain active for at least 15 CLK periods. The RESET pin should remain active during this time to ensure proper CPU operation. RESET is active HIGH.  RESET sets the SMBASE descriptor to a default address of 30000H. If the system uses SMBASE relocation, then the SRESET pin should be used for soft resets.                                                                                                                                    |

| SRESET   |       | The SRESET pin duplicates all the functionality of the RESET pin with the following two exceptions:  1. The SMBASE register will retain its previous value.  2. If UP # (I) is asserted, SRESET will not have an effect on the host microprocessor. For soft resets, SRESET should remain active for at least 15 CLK periods. SRESET is active HIGH. SRESET is asynchronous but must meet setup and hold times t <sub>20</sub> and t <sub>21</sub> for recognition in any specific clock.                                                                                                                                                                                                                                                                                                                                               |

| SMI#     | ţ     | The <b>System Management Interrupt</b> input is used to invoke the System Management Mode (SMM). SMI # is a falling edge triggered signal which forces the CPU into SMM at the completion of the current instruction. SMI # is recognized on an instruction boundary and at each iteration for repeat string instructions. SMI # does not break LOCKed bus cycles and cannot interrupt a currently executing SMM. The CPU will latch the falling edge of one pending SMI # signal while the CPU is executing an existing SMI. The nested SMI will not be recognized until after the execution of a Resume (RSM) instruction.                                                                                                                                                                                                            |

| SMIACT#  | 0     | The <b>System Management Interrupt ACTive</b> is an active low output, indicating that the processor is operating in SMM. It is asserted when the CPU begins to execute the SMI state save sequence and will remain active LOW until the processor executes the last state restore cycle out of SMRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| STPCLK#  | ł     | The STOP CLock request input signal indicates a request has been made to turn off the CLK input. When the CPU recognizes a STPCLK#, the processor will stop execution on the next instruction boundary, unless superseded by a higher priority interrupt, empty all internal pipelines and the write buffers and generate a Stop Grant acknowledge bus cycle. STPCLK# is active LOW and is provided with an internal pull-up resistor. STPCLK# is asynchronous but setup and hold times t <sub>20</sub> and t <sub>21</sub> must be met to ensure recognition in any specific clock.                                                                                                                                                                                                                                                    |

| Symbol  | Туре    | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTERRU | JPTS (C | ontinued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| INTR    | ı       | The maskable interrupt indicates that an external interrupt has been generated. If the internal interrupt flag is set in EFLAGS, active interrupt processing will be initiated. The Intel OverDrive processor will generate two locked interrupt acknowledge bus cycles in response to the INTR pin going active. INTR must remain active until the interrupt acknowledges have been performed to assure that the interrupt is recognized. INTR is active HIGH and is not provided with an internal pulldown resistor. INTR is asynchronous, but must meet setup and hold times t <sub>20</sub> and t <sub>21</sub> for recognition in any specific clock. |

| NMI     | ı       | The non-maskable interrupt request signal indicates that an external non-maskable interrupt has been generated. NMI is rising edge sensitive. NMI must be beld LOW for at least four CLK periods before this rising edge. NMI is not provided with an internal pulldown resistor. NMI is asynchronous, but must meet setup and hold times t <sub>20</sub> and t <sub>21</sub> for recognition in any specific clock.                                                                                                                                                                                                                                       |

| BUS ARI | BITRAT  | ION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BREQ    | 0       | The internal cycle pending signal indicates that the Intel OverDrive processor has internally generated a bus request. BREQ is generated whether or not the Intel OverDrive processor is driving the bus. BREQ is active HIGH and is never floated.                                                                                                                                                                                                                                                                                                                                                                                                        |

| HOLD    | l       | The bus hold request allows another bus master complete control of the Intel OverDrive processor bus. In response to HOLD going active the Intel OverDrive processor will float most of its output and input/output pins. HLDA will be asserted after completing the current bus cycle, burst cycle or sequence of locked cycles. The Intel OverDrive processor will remain in this state until HOLD is deasserted. HOLD is active high and is not provided with an internal pulldown resistor. HOLD must satisfy setup and hold times t <sub>18</sub> and t <sub>19</sub> for proper operation.                                                           |

| HLDA    | 0       | Hold acknowledge goes active in response to a hold request presented on the HOLD pin. HLDA indicates that the Intel OverDrive processor has given the bus to another local bus master. HLDA is driven active in the same clock that the Intel OverDrive processor floats its bus. HLDA is driven inactive when leaving bus hold. HLDA is active HIGH and remains driven during bus hold.                                                                                                                                                                                                                                                                   |

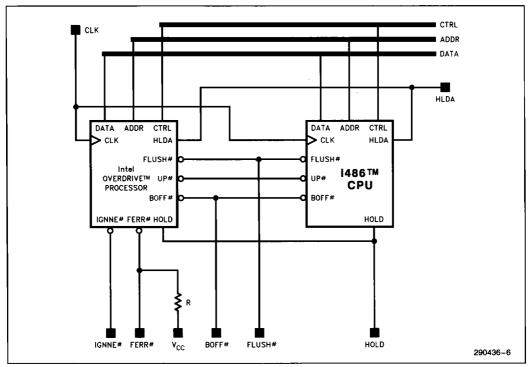

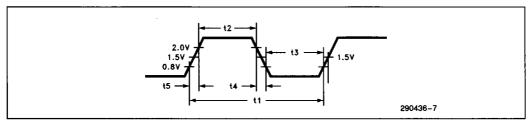

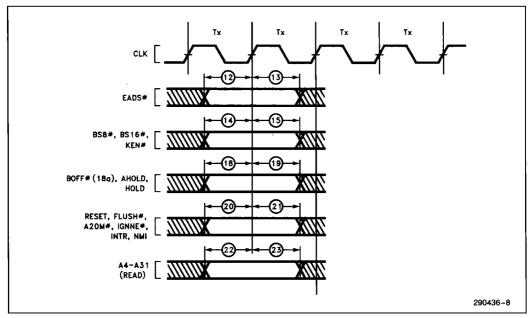

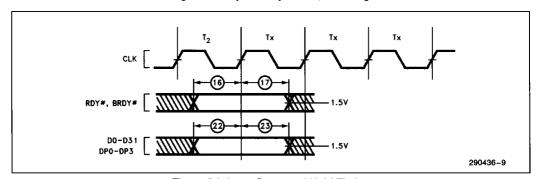

| Symbol     | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |