### 1. DESCRIPTION

S1D17508 is a 160 output segment (column) LCD driver suitable for driving of colored STN dot-matrix LCD panels of a larger capacity, for use in combination with S1D17043.

Contributing to making clearer LCD picture quality, this IC employs the high speed enable chain method and is slim-chip configuration which is more advantageous for miniaturization of the LCD panel. S1D17508 is also capable of low-voltage and high-speed logic operations and fits to a wide range of applications.

### 2. FEATURES

- Number of LCD drive output segments: 160

- Low voltage operation: 2.7V min.

- High duty drive: 1/500 (an example)

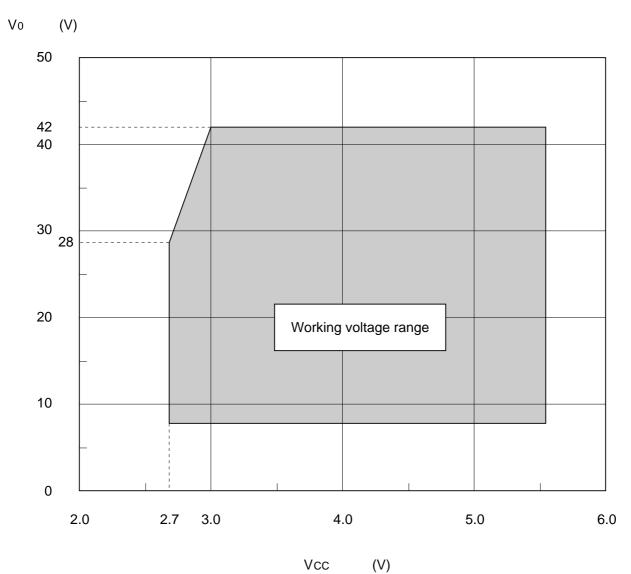

- Wide LCD drive voltage range: +8 to +42 V(VDD = 3 to 5.5V)

- High speed and low power consumption data transfer is possible by adoption of the 8-bit bus enable chain method:

Shift clock frequencies: 18.0 MHz

$(5V \pm 10\%)$ 10.0 MHz (2.7V)

- Slim-chip configuration

- Non-bias display off function

- Pin-selection of the output shift direction is available

- Offset bias regulation of LCD power for respective VDDH and GND levels is possible

- Logic operation power supply: 2.7 to 5.5V

- Shipped status: CHIP S1D17508D00B\*

TCP S1D17508T\*\*\*\*

• This IC is not radiation resistant

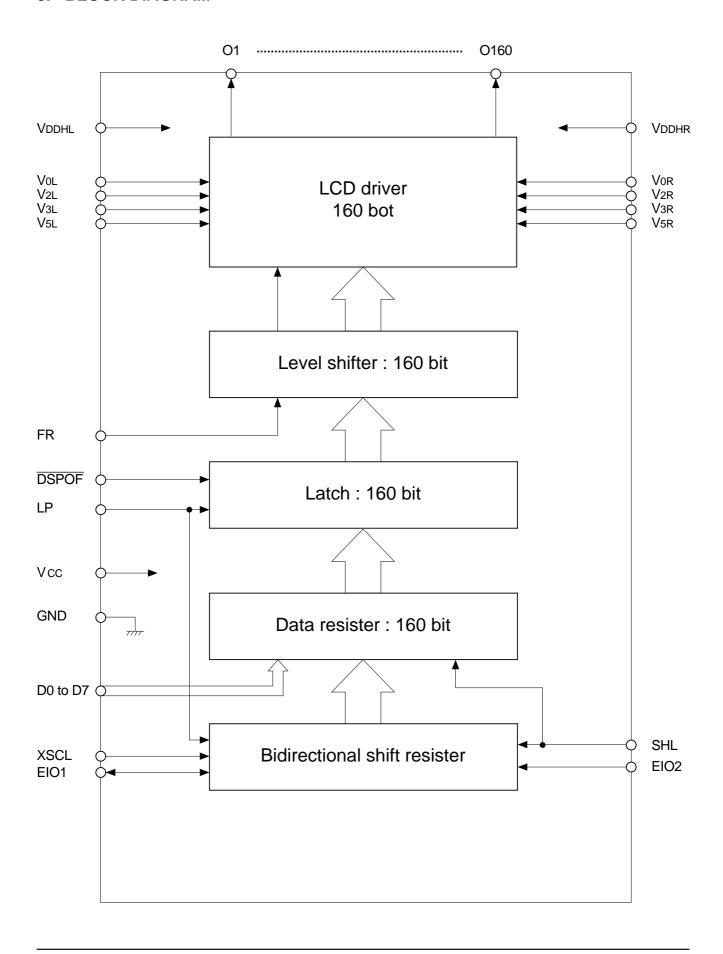

### 3. BLOCK DIAGRAM

8-2 EPSON

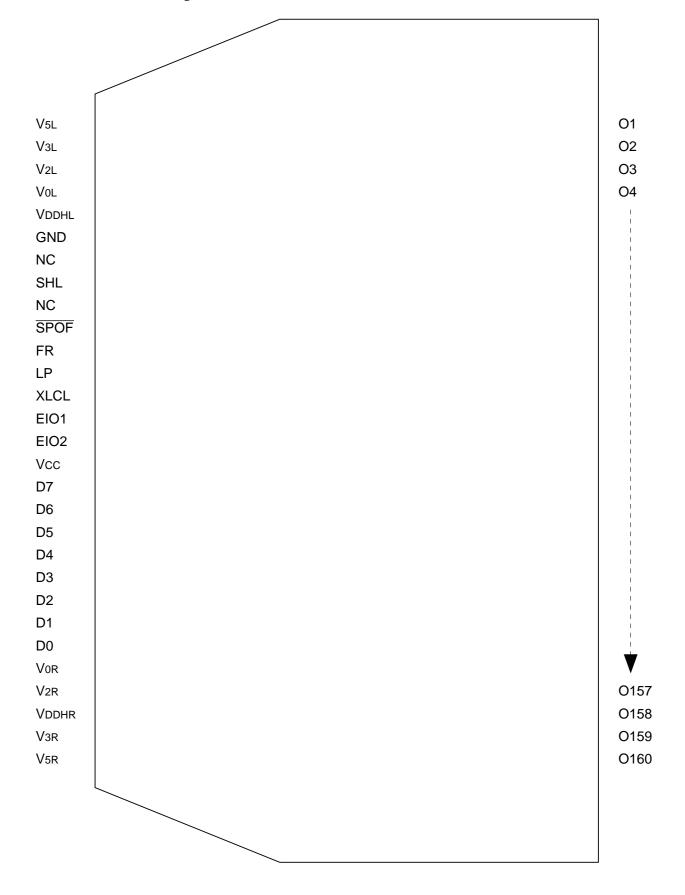

# 4. PIN DESCRIPTION

| Pin name            | I/O          | Description                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        | Numbers of pins |   |

|---------------------|--------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------|-------|----------------------|---------|------|--------|-----------------|---|

| O1 to O160          | 0            |                                                                                                                           | LCD driving segment (column) output. The output varies at the falling edge of LP.                                                                                                                                                                                                                                                                                                                                                            |           |                   |       |                      |         |      |        |                 |   |

| D0 to D7            | 1            | Display data input terminals                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 | 8 |

| XSCL                | I            |                                                                                                                           | For input of the shift clock signals of the display data (falling edge trigger)                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| LP                  | I            |                                                                                                                           | For input of the latch pulse signals of the display data (falling edge trigger)                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| EIO1<br>EIO2        | I/O          | Setting<br>The ou                                                                                                         | Enable I/O. Setting to I or O is determined by the SHL input level. The output is reset by the LP input and when 160 bit equivalent data are received, it falls to LOW automatically.                                                                                                                                                                                                                                                        |           |                   |       |                      |         |      |        |                 | 2 |

| SHL                 | I            | When (a0, a1                                                                                                              | Shift direction selection and EIO terminal I/O control signal input. When data are input to terminals (D <sub>0</sub> , D <sub>1</sub> D <sub>7</sub> ) in the order of (a <sub>0</sub> , a <sub>1</sub> a <sub>6</sub> and a <sub>7</sub> ), (b <sub>0</sub> b <sub>6</sub> and b <sub>7</sub> )(t <sub>0</sub> , t <sub>1</sub> t <sub>6</sub> and t <sub>7</sub> ), the relations between the data and segment outputs become as follows: |           |                   |       |                      |         |      |        | 1               |   |

|                     |              | SHL                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           | C                 | Outpu | ıt                   |         |      | E      | 10              |   |

|                     |              | SHL                                                                                                                       | 01                                                                                                                                                                                                                                                                                                                                                                                                                                           | O2        | О3                |       | O158                 | O159    | O160 | EIO1   | EIO2            |   |

|                     |              | LOW                                                                                                                       | а7                                                                                                                                                                                                                                                                                                                                                                                                                                           | a6        | а5                |       | t2                   | t1      | t0   | Input  | Output          |   |

|                     |              | HIGH                                                                                                                      | t0                                                                                                                                                                                                                                                                                                                                                                                                                                           | t1        | t2                |       | a5                   | a6      | a7   | Output | Input           |   |

|                     |              | (Note) The relations between the data and segment outputs are determined independent from the number of the shift clocks. |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| FR                  | 1            | For inp                                                                                                                   | ut of alt                                                                                                                                                                                                                                                                                                                                                                                                                                    | ernatin   | g curre           | nt L  | CD driv              | e signa | ls.  |        |                 | 1 |

| Vcc, GND            | Power supply |                                                                                                                           | Logic operation power supply: GND: 0V Vcc: +3.3, +5V                                                                                                                                                                                                                                                                                                                                                                                         |           |                   |       |                      |         |      |        | 2               |   |

| VDDHL, VDDHR        |              | LCD drive power supply VDDH GND: 0V VDDH:14 to 42V                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        | 10              |   |

| Vol,Vor<br>V2L, V2R | Power        | " V <sub>0</sub> V <sub>DDH≥</sub> V <sub>0≥</sub> V <sub>2</sub> ≥7/9V <sub>0</sub>                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| V3L, V3R            | supply       | " V2 2/9 V₀≥V₅≥Vss V3                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| V5L, V5R            |              | " V5                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                   |       |                      |         |      |        |                 |   |

| DSPOF               | I            | LOW I                                                                                                                     | n using                                                                                                                                                                                                                                                                                                                                                                                                                                      | put is fo | orcefull <u>y</u> |       | ade to \<br>oined us |         |      |        | ot              | 1 |

Total 187

### 5. FUNCTION OF EACH BLOCK

### 5-1 Enable shift resister

The enable shift register is a bidirectional shift register of which the shift direction is being selected by the SHL input and the shift register output is used to store data bus signals into the data register.

When the enable signal is in disabled state, the internal clock signal and the data bus are fixed to LOW, thus going into a power saving mode.

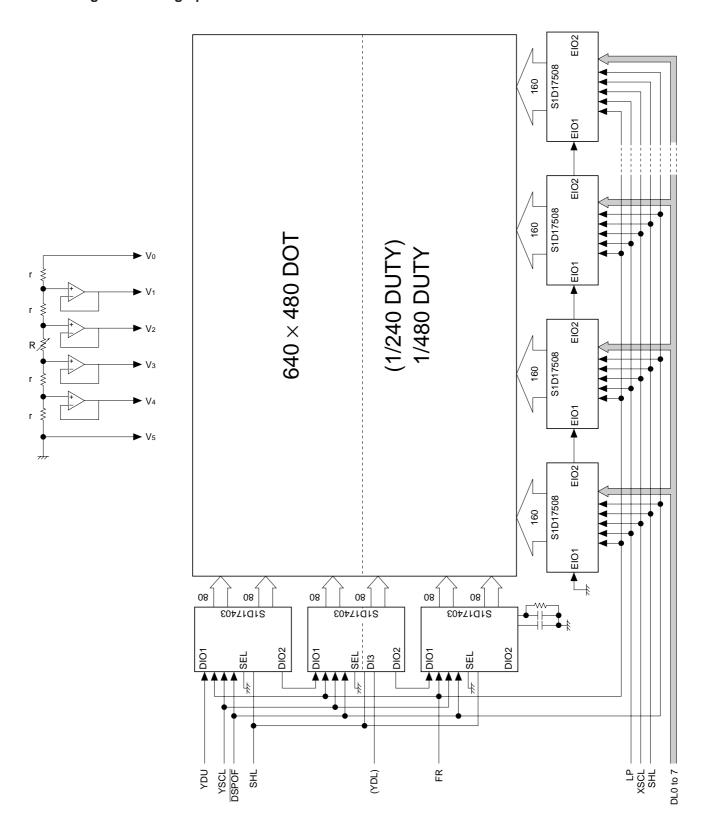

When using multiple number of segment drivers, make cascade connection of EIO terminals of respective drivers to connect the EIO terminal of the top driver to "GND". (Refer to Clause 10. Connection examples)

Since the enable control circuit automatically senses completion of receiving 160 bit equivalent data to transfer the enable signal automatically, control signal of a separate control LSI is not needed.

### 5-2 Data register

This register works to make series or parallel conversion of data bus signals according to the enable shift register output. Consequently, the relations between the serial display data and segment outputs are determined independent from the number of the shift clock inputs.

### 5-3 Latch

It takes in the content of the data register at the falling edge trigger to transfer the output to the level shifter.

### 5-4 Level shifter

This is a level interface circuit to convert the voltage level of signals from the logic operation level to LCD drive level.

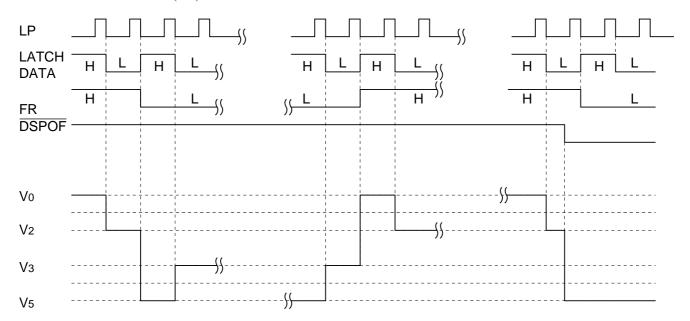

### 5-5 LCD driver

It outputs the LCD driving voltage.

Given below are the relations between data bus signals, alternating current signal FR levels and segment output voltages.

| DSPOF | Data bus<br>signals | FR   | Voltage<br>outputs of<br>the driver |

|-------|---------------------|------|-------------------------------------|

| HIGH  | HIGH                | HIGH | V <sub>0</sub>                      |

|       | 111011              | LOW  | V5                                  |

|       | LOW                 | HIGH | V <sub>2</sub>                      |

|       | LOVV                | LOW  | Vз                                  |

| LOW   | -                   | -    | V5                                  |

8-4 EPSON

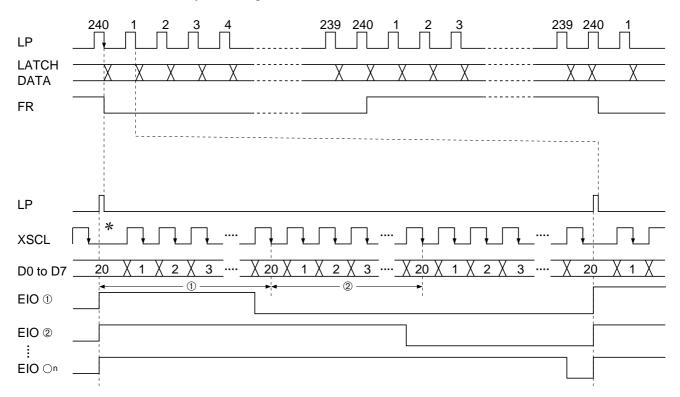

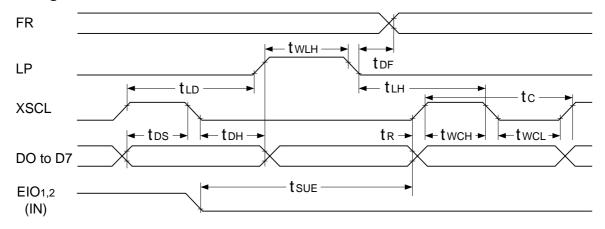

# 5-6 Timing diagram

### **Timing diagram**

In case of 1/240 Duty (an example)

- 1) to 1) stands for the cascade numbers of the driver.

- \* When making high speed data transfer, it becomes necessary to secure a longer XSCL cycle when determining the LP pulse insertion timing in order to maintain the specified value of LP → XSCL (tLH).

### 6. ABSOLUTE MAXIMUM RATINGS

| Items                 | Codes          | Ratings            | Units |

|-----------------------|----------------|--------------------|-------|

| Supply voltage (1)    | Vcc            | -0.3 to +7.0       | V     |

| Supply voltage (2)    | VDDH           | -0.3 to +45.0      | V     |

| Supply voltage (3)    | V0, V2, V3, V5 | -0.3 to VDDH + 0.3 | V     |

| Input voltage         | Vı             | -0.3 to Vcc + 0.3  | V     |

| Output voltage        | Vo             | -0.3 to Vcc + 0.3  | V     |

| EIO output current    | l01            | 20                 | mA    |

| Working temperature   | Topr           | −30 to +85         | °C    |

| Storage temperature 1 | Tstg1          | -65 to +150        | °C    |

| Storage temperature 2 | Tstg2          | -55 to +100        | °C    |

- (Note 1) All the voltage ratings are based on GND = 0V.

- (Note 2) The storage temperature 1 is applicable to independent chips and the storage temperature 2 is applicable to the TCP modular state.

- (Note 3) V<sub>0</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>5</sub> should always be in the order of V<sub>DDH</sub>≥V<sub>0</sub>≥V<sub>2</sub>≥V<sub>3</sub>≥V<sub>5</sub>≥GND.

(Note 4) If the logic operation power goes into a floating state or if VCC drops to 2.6V or below while the LCD driving power is being applied, the LSI may be damaged. Therefore, keep from occurrence of the aforementioned status.

Specifically, pay close attention to the power supply sequence at times of turning the system power on and off.

8-6 EPSON

# 7. ELECTRICAL CHARACTERISTICS

# 7-1 DC characteristics

Unless otherwise specified, GND = 0V,  $VCC = +5.0 \text{ V} \pm 10\%$ ,  $Ta = -30 \text{ to } 85^{\circ}\text{C}$

| Item                                   | Symbol         | ol Condition                                                                                                                                      |                                              | Applicable pin                           | Min.    | Тур. | Max.   | Unit |

|----------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|------------------------------------------|---------|------|--------|------|

| Supply voltage (1)                     | Vcc            |                                                                                                                                                   |                                              | Vcc                                      | 2.7     |      | 5.5    | V    |

| Recommended operating voltage          | Vo             |                                                                                                                                                   |                                              | Vol, VDDHL                               | 14.0    |      | 40.0   | V    |

| Operating voltage                      | Vo             |                                                                                                                                                   | Function only                                | Vor, VDDHL                               | 8.0     |      | 42.0   | V    |

| Supply voltage (2)                     | V <sub>2</sub> |                                                                                                                                                   | Recommended value                            | V2L, V2R                                 | 7/9 Vo  |      | Vo     | V    |

| Supply voltage (3)                     | V3             |                                                                                                                                                   | Recommended value                            | V3L, V3R                                 | GND     |      | 2/9 Vo | V    |

| High level input voltage               | ViH            |                                                                                                                                                   | V <sub>DD</sub> = 2.7 to 5.5V                | EIO1,EIO2,FR                             | 0.8Vcc  |      |        | V    |

| Low level input voltage                | VIL            | 1                                                                                                                                                 | VDD = 2.7 (0 5.5 V                           | D0 to D7,XSCL<br>SHL,LP,DSPOF            |         |      | 0.2Vcc | V    |

| High level output voltage              | Voн            | Vcc=                                                                                                                                              | Iон = −0.6mA                                 |                                          | Vcc-0.4 |      |        | V    |

| Low level output voltage               | Vol            | 2.7 to<br>5.5V                                                                                                                                    | IoL = 0.6mA                                  | EIO1, EIO2                               |         |      | 0.4    | V    |

| Input leak current                     | lu             | GND≤V                                                                                                                                             | 'IN ≤ Vcc                                    | D0 to D7,LP,FR<br>XSCL, SHL<br>DSPOF     |         |      | 2.0    | μА   |

| I/O leak current                       | Ili/O          | GND ≤ V                                                                                                                                           | 'IN ≤ VCC                                    | EIO1, EIO2                               |         |      | 5.0    | μΑ   |

| Rest current                           | IGND           | V <sub>0</sub> = 14.0 to 42.0V<br>V <sub>IH</sub> = V <sub>CC</sub> , V <sub>IL</sub> =GND                                                        |                                              | GND                                      |         |      | 25     | μА   |

| Output resistance                      | Rseg           | △Von<br>=0.5V                                                                                                                                     | Vo =+36.0V, 1/24                             | O1 to O160                               |         | 0.85 | 2.6    | kΩ   |

|                                        |                | Recom-<br>mended<br>condition                                                                                                                     | Vo =+26.0V, 1/20                             |                                          |         | 0.90 | 2.6    |      |

| In-chip deviation of output resistance | △Rseg          | △Von=0.<br>Vo = +36                                                                                                                               | 5V<br>5.0V, 1/24                             | O1 to O160                               |         |      | 90     | Ω    |

| Mean working current consumption (1)   | lcc            | Vcc = +5.0V, ViH = Vcc ViL = GND, fXSCL = 5.38MHz fLP = 33.6kHz, fFR = 70Hz Input data: Checkered indication, no-load                             |                                              | Vcc                                      |         | 0.5  | 1.1    | mA   |

|                                        |                |                                                                                                                                                   | 3.0V inditions are the same as nen Vcc = 5V. |                                          | 0.2     |      | 0.6    |      |

| Mean working current consumption (2)   | lo             | $V_0 = +30.0V$<br>$V_{CC} = +5.0V$ , $V_3 = +4.0V$<br>$V_2 = +26.0V$ , $V_5 = +0.0V$<br>Other conditions are the same as those in the IDD column. |                                              | VOL, VOR                                 |         | 0.15 | 0.9    | mA   |

| Input terminal capacity                | Сı             | Freq. = 1 MHz Ta = 25°C Independent chips                                                                                                         |                                              | D0 to D7, LP,<br>FR, XSCL, SHL,<br>DSPOF |         |      | 8      | pF   |

| I/O terminal capacity                  | Ci/O           | 1                                                                                                                                                 |                                              | EIO1, EIO2                               |         |      | 15     | pF   |

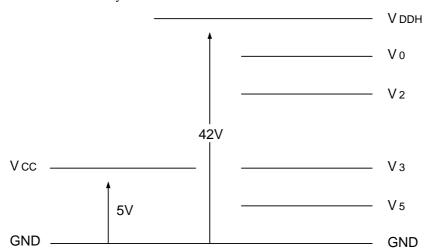

# Working voltage range Vcc - Vo

The  $V_0$  voltage should be set up within the  $V_{CC}$  -  $V_0$  working voltage range given below.

8-8 EPSON

### 7-2 AC characteristics

### Input timing characteristics

$V_{CC} = 5.0V \pm 10\%$ ,  $T_{a} = -30$  to  $85^{\circ}C$

| It a see a                     | 0         | 0 11(11        | N4:  | NA   | 1111  |

|--------------------------------|-----------|----------------|------|------|-------|

| Items                          | Symbol    | Conditions     | Min. | Max. | Units |

| XSCL cycle                     | tc        | tr, tf≤11ns *3 | 62   |      | ns    |

| XSCL high level pulse duration | twch      |                | 20   |      | ns    |

| XSCL low level pulse duration  | twcL      |                | 20   |      | ns    |

| Data setup time                | tos       |                | 10   |      | ns    |

| Data hold time                 | tDH       |                | 10   |      | ns    |

| $XSCL \to LP$ rise time        | tLD       |                | -5   |      | ns    |

| LP 	o XSCL fall time           | tLH       |                | 30   |      | ns    |

| LD high level pulse duration   | <b>5.</b> | *1             | 40   |      | ns    |

| LP high level pulse duration   | twlH      | *2             | 35   |      | ns    |

| FR delay allowance             | tDF       |                | -300 | +300 | ns    |

| EIO setup time                 | tsue      |                | 30   |      | ns    |

| Input signal variation time    | tr, tf    | *4             |      | 50   | ns    |

$VCC = 2.7V \text{ to } 4.5V, Ta = -30 \text{ to } 85^{\circ}C$

| Items                           | Symbol           | Conditions     | Min. | Max. | Units |

|---------------------------------|------------------|----------------|------|------|-------|

| XSCL cycle                      | tc               | tr, tf≤15ns *3 | 100  |      | ns    |

| XSCL high level pulse duration  | twch             |                | 35   |      | ns    |

| XSCL low level pulse duration   | twcL             |                | 35   |      | ns    |

| Data setup time                 | tDS              |                | 15   |      | ns    |

| Data hold time                  | tDH              |                | 10   |      | ns    |

| $XSCL \to LP$ rise time         | tLD              |                | -10  |      | ns    |

| $LP \rightarrow XSCL$ fall time | tLH              |                | 60   |      | ns    |

| LD high lovel pulse duration    | <b>5 4 7 1 1</b> | *1             | 75   |      | ns    |

| LP high level pulse duration    | twlH             | *2             | 65   |      | ns    |

| FR delay allowance              | tDF              |                | -300 | +300 | ns    |

| EIO setup time                  | tsue             |                | 40   |      | ns    |

| Input signal variation time     | tr, tf           | *4             |      | 50   | ns    |

**Notes**: \*1 The "twlh" specifies the time when the LP is at HIGH and, at the same time, when XSCL is at LOW, when LP is being input while the XSCL is at LOW.

- \* 2 The "twlh" (its definition is same as \*1) when LP rises while XSCL is at HIGH.

- \* 3 High speed operation of the shift clocks (XSCL) should only be made under a condition of  $t_r + t_f \le (t_C t_{WCH})$ .

- \* 4 When making high speed data transfer using continuous shift clocks, tr + tf of the LP signals should be upto (tc + twch tld twlh tlh) at the maximum.

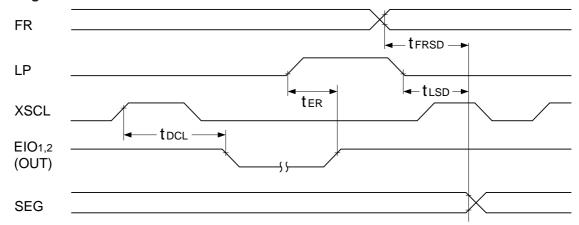

# **Output timing characteristics**

$V_{CC} = +5.0V \pm 10\%$ ,  $V_{0} = +14.0 \text{ to } +42.0V$

| Items                       | Symbol | Conditions  | Min. | Max. | Units |

|-----------------------------|--------|-------------|------|------|-------|

| EIO reset time              | ter    | CL = 15 pF  |      | 120  | ns    |

| EIO output delay time       | tDCL   | (EIO)       |      | 55   | ns    |

| LP 	o SEG output delay time | tLSD   | CL = 100 pF |      | 200  | ns    |

| FR 	o SEG output delay time | tFRSD  | (O n)       |      | 400  | ns    |

$V_{CC} = +2.7V$  to 4.5V,  $V_{0} = +14.0$  to +28.0V

| Items                          | Symbol | Conditions  | Min. | Max. | Units |

|--------------------------------|--------|-------------|------|------|-------|

| EIO reset time                 | tER    | CL = 15 pF  |      | 240  | ns    |

| EIO output delay time          | tDCL   | (EIO)       |      | 85   | ns    |

| LP 	o SEG output delay time    | tLSD   | CL = 100 pF |      | 400  | ns    |

| $FR \to SEG$ output delay time | tFRSD  | (O n)       |      | 800  | ns    |

8-10 **EPSON**

### 8. LCD DRIVING POWER SUPPLY

### 8-1 Setting up respective voltage levels

When setting up respective voltage levels for LCD drive, it is the best way to resistively divide the potential between V0 - GND to drive the LCD by means of voltage follower using an operation amplifier.

In consideration of the case of using an operation amplifier, the LCD driving minimum potential level V5 and GND are separated and independent terminals are used.

However, since the efficacy of the LCD driving output driver deteriorates when the potential of V5 goes up beyond the GND potential to enlarge the potential difference, always keep the potential difference of V5 - VSS at 0V to 2.5V. When a resistance exists in series in the power supply line of V0 (GND), Io at signal changes causes voltage drop at V0 (GND) of the supply terminals of the LSI disabling it to maintain the relations of the LCD with intermediate potentials

of (VDDH≥V0≥V2≥V3≥V5≥GND), thus leading to breakdown or destruction of the LSI.

When using a protective resistor, do not fail to stabilize the voltage using an appropriate capacitance.

### 8-2 Precautions when turning the power on and off

Since the LCD drive voltage of these LSIs is comparatively high, if a high voltage of 30V or more is applied to the LCD drive circuit with the logic operation power made floating or with the VCC lowered to 2.6V or less, or when LCD drive signals are output before applied voltage to the LCD drive circuits is stabilized, excess current flows through to possibly lead to breakdown or to destroy the LSI.

It is therefore suggested to maintain the potential of the LCD drive output to V5 level until the LCD drive circuit voltage is stabilized, using the display off function (DSPOF).

Maintain the following sequences when turning the power on and off:

When turning the power on: Turn on the logic operation power  $\rightarrow$  turn on the LCD drive power or turn them on simultaneously.

When turning the power off: Turn off the LCD drive power  $\rightarrow$  turn off the logic operation power or turn them off simultaneously.

For protection against excess current, insert a quick melting fuse in series in the LCD drive power line.

When using a protective resistor, select the optimum resistance value depending on the capacitance of the LCD cells.

# 9. A CONNECTION EXAMPLE

Block diagram of a large-plane LCD

8-12 **EPSON**

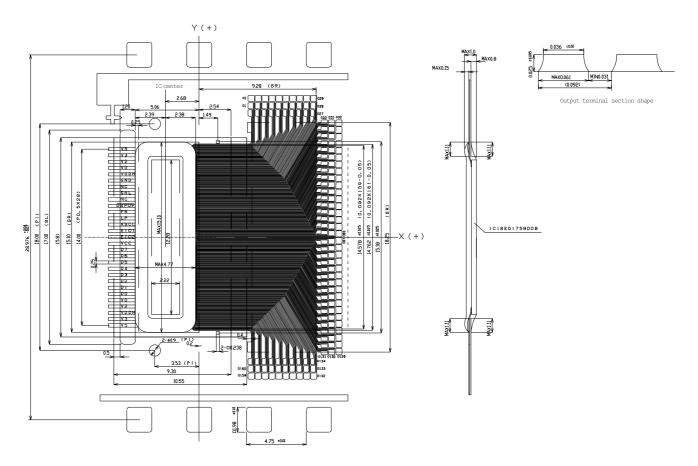

### 10. S1D17508T\* TCP PIN ARRANGEMENT EXAMPLE

For reference

Remark: This drawing is not meant to determine the contour of the TCP.

# 11. DIMENSIONAL OUTLINE DRAWING \$1D17508T00A\*

For reference

Unit: mm

8-14 **EPSON**

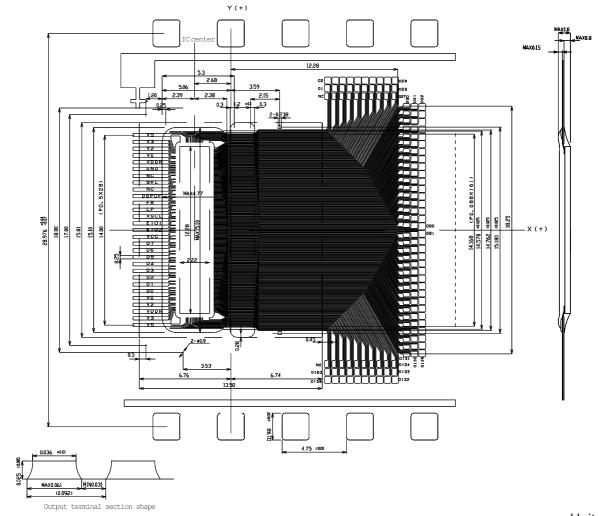

### S1D17508T00B\*

# For reference

Unit: mm

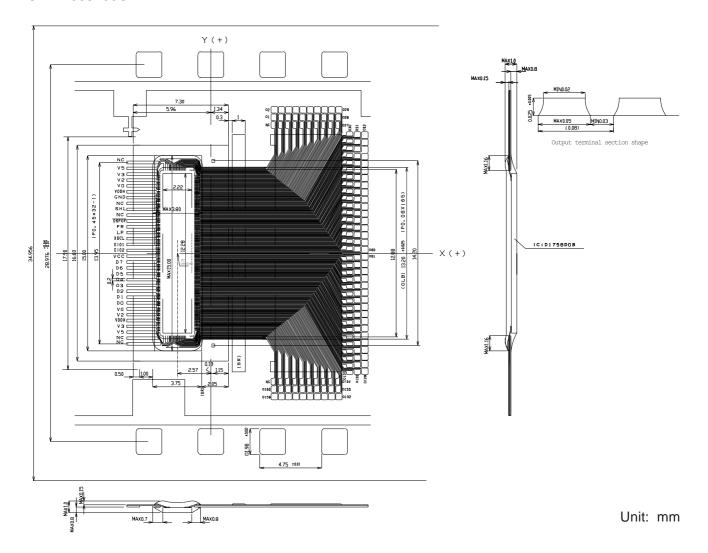

### S1D17508T00G\*

# For reference

8-16 **EPSON**