# **S73WS-P based MCP Products**

1.8 Volt-only x16 Simultaneous Read/Write, Burst Mode Flash Mobile SDRAM on Shared Bus

Data Sheet (Advance Information)

**Notice to Readers:** This document states the current technical specifications regarding the Spansion product(s) described herein. Each product described herein may be designated as Advance Information, Preliminary, or Full Production. See *Notice On Data Sheet Designations* for definitions.

## **Notice On Data Sheet Designations**

Spansion LLC issues data sheets with Advance Information or Preliminary designations to advise readers of product information or intended specifications throughout the product life cycle, including development, qualification, initial production, and full production. In all cases, however, readers are encouraged to verify that they have the latest information before finalizing their design. The following descriptions of Spansion data sheet designations are presented here to highlight their presence and definitions.

#### **Advance Information**

The Advance Information designation indicates that Spansion LLC is developing one or more specific products, but has not committed any design to production. Information presented in a document with this designation is likely to change, and in some cases, development on the product may discontinue. Spansion LLC therefore places the following conditions upon Advance Information content:

"This document contains information on one or more products under development at Spansion LLC. The information is intended to help you evaluate this product. Do not design in this product without contacting the factory. Spansion LLC reserves the right to change or discontinue work on this proposed product without notice."

#### **Preliminary**

The Preliminary designation indicates that the product development has progressed such that a commitment to production has taken place. This designation covers several aspects of the product life cycle, including product qualification, initial production, and the subsequent phases in the manufacturing process that occur before full production is achieved. Changes to the technical specifications presented in a Preliminary document should be expected while keeping these aspects of production under consideration. Spansion places the following conditions upon Preliminary content:

"This document states the current technical specifications regarding the Spansion product(s) described herein. The Preliminary status of this document indicates that product qualification has been completed, and that initial production has begun. Due to the phases of the manufacturing process that require maintaining efficiency and quality, this document may be revised by subsequent versions or modifications due to changes in technical specifications."

#### Combination

Some data sheets contain a combination of products with different designations (Advance Information, Preliminary, or Full Production). This type of document distinguishes these products and their designations wherever necessary, typically on the first page, the ordering information page, and pages with the DC Characteristics table and the AC Erase and Program table (in the table notes). The disclaimer on the first page refers the reader to the notice on this page.

#### Full Production (No Designation on Document)

When a product has been in production for a period of time such that no changes or only nominal changes are expected, the Preliminary designation is removed from the data sheet. Nominal changes may include those affecting the number of ordering part numbers available, such as the addition or deletion of a speed option, temperature range, package type, or V<sub>IO</sub> range. Changes may also include those needed to clarify a description or to correct a typographical error or incorrect specification. Spansion LLC applies the following conditions to documents in this category:

"This document states the current technical specifications regarding the Spansion product(s) described herein. Spansion LLC deems the products to have been in sufficient production volume such that subsequent versions of this document are not expected to change. However, typographical or specification corrections, or modifications to the valid combinations offered may occur."

Questions regarding these document designations may be directed to your local AMD or Fujitsu sales office.

# **S73WS-P based MCP Products**

1.8 Volt-only x16 Simultaneous Read/Write, Burst Mode Flash Mobile SDRAM on Shared Bus

Data Sheet (Advance Information)

### **Features**

■ Power supply voltage of 1.7 to 1.95V

■ Flash access time: 80 ns for NOR Flash

■ Flash burst frequencies: 66 MHz, 80 MHz, 108 MHz

■ Mobile SDRAM burst frequency: 104 MHz (SDR)

■ Package:

- 9.0 x 12.0 mm MCP

**■** Operating Temperature

- -25°C to +85°C (wireless)

The S73WS series is a product line of stacked packages and consists of:

- One NOR flash memory die

- One Mobile SDRAM die on shared bus

The products covered by this document are listed in the table below.

|           | DRAM Density            |  |  |

|-----------|-------------------------|--|--|

| Device    | 128Mb                   |  |  |

| S29WS256P | S73WS256PD0 (MCP) (SDR) |  |  |

#### Note:

For a full list of OPNs, please contact the local sales representative or refer to the Ordering Information valid combinations tables.

For detailed specifications, please refer to the individual data sheets.

| Document                      | Publication Identification Number (PID) |

|-------------------------------|-----------------------------------------|

| S29WS-P                       | S29WS-P_00                              |

| 128 Mb Mobile SDR-DRAM Type 5 | SDRAM_08                                |

## 1. Product Selector Guide

| Device           | NOR Flash<br>Density | NOR Flash<br>Speed | DRAM<br>Density | DRAM Speed    | DRAM Supplier | Package          |

|------------------|----------------------|--------------------|-----------------|---------------|---------------|------------------|

| S73WS512PD0HF64V | 512 Mb               | 66 MHz             | 128 Mb          | 104 MHz (SDR) | Type 5        | MCP<br>9 x 12 mm |

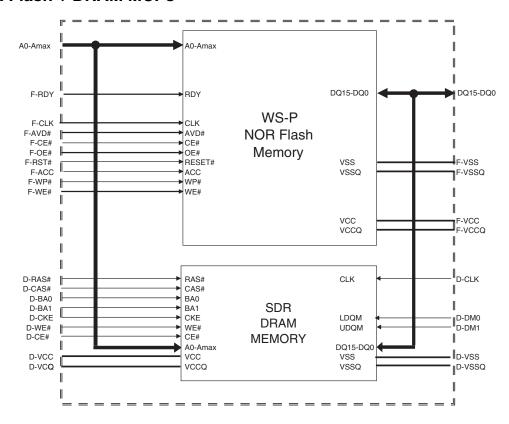

# 2. MCP Block Diagram

### 2.1 NOR Flash + DRAM MCPs

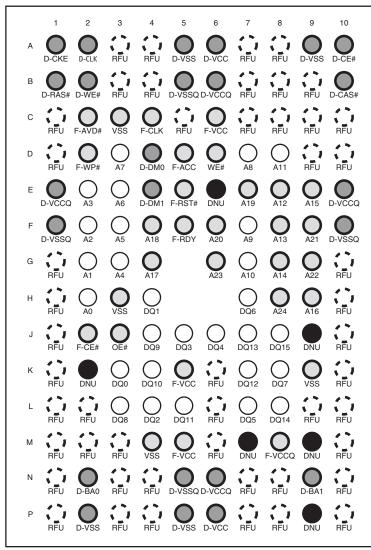

# 3. Connection Diagrams

### 3.1 512 Mb NOR Flash with 128 Mb SDR-DRAM

137-ball Fine-Pitch Ball Grid Array (Top View, Balls Facing Down)

Note: DDR-only signals are RFUs in the case of the SDR DRAM-based solutions.

### 3.1.0.1 Special Handling Instructions For FBGA Package

Special handling is required for Flash Memory products in FBGA packages.

Flash memory devices in FBGA packages may be damaged if exposed to ultrasonic cleaning methods. The package and/or data integrity may be compromised if the package body is exposed to temperatures above 150×C for prolonged periods of time.

# 3.2 NOR Flash and DRAM Input/Output Descriptions

| Amax-A0            | = | Address inputs, shared between NOR Flash and DRAM                                                                                                                                                                                                                                                   |

|--------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ15-DQ0           | = | Data input/output, shared between NOR Flash and DRAM                                                                                                                                                                                                                                                |

| F-CE#              | = | NOR Flash Chip-enable input. Asynchronous relative to CLK for Burst Mode.                                                                                                                                                                                                                           |

| F-OE#              | = | NOR Flash Output Enable input. Asynchronous relative to CLK for Burst mode.                                                                                                                                                                                                                         |

| F-WE#              | = | NOR Flash Write Enable input.                                                                                                                                                                                                                                                                       |

| F-V <sub>CC</sub>  | = | NOR Flash device power supply (1.7 V - 1.95V).                                                                                                                                                                                                                                                      |

| F-V <sub>CCQ</sub> | = | Input/Output Buffer power supply.                                                                                                                                                                                                                                                                   |

| $V_{SS}$           | = | Ground                                                                                                                                                                                                                                                                                              |

| RFU                | = | Reserved for Future Use                                                                                                                                                                                                                                                                             |

| F-RDY              | = | Flash ready output. Indicates the status of the Burst read. VOL = data valid.                                                                                                                                                                                                                       |

| F-CLK              | = | NOR Flash Clock. The first rising edge of CLK in conjunction with AVD# low latches the address input and activates burst mode operation. After the initial word is output, subsequent rising edges of CLK increment the internal address counter. CLK should remain low during asynchronous access. |

| F-AVD#             | = | NOR Flash Address Valid input. Indicates to device that the valid address is present on the address inputs.  VIL = for asynchronous mode, indicates valid address; for burst mode, causes starting address to be latched on rising edge of CLK.  VIH= device ignores address inputs                 |

| F-RST#             | = | NOR Flash hardware reset input. VIL= device resets and returns to reading array data                                                                                                                                                                                                                |

| F-WP#              | = | NOR Flash hardware write protect input. VIL = disables program and erase functions in the four outermost sectors.                                                                                                                                                                                   |

| F-ACC              | = | NOR Flash accelerated input. At VHH, accelerates programming; automatically places device in unlock bypass mode. At VIL, disables all program and erase functions. Should be at VIH for all other conditions.                                                                                       |

| D-CE#              | = | SDRAM Chip Select                                                                                                                                                                                                                                                                                   |

| D-CKE              | = | SDRAM Clock Enable                                                                                                                                                                                                                                                                                  |

| D-BA1-BA0          | = | SDRAM Bank Select                                                                                                                                                                                                                                                                                   |

| D-RAS#             | = | SDRAM Row Address Strobe                                                                                                                                                                                                                                                                            |

| D-CAS#             | = | SDRAM Column Address Strobe                                                                                                                                                                                                                                                                         |

| D-DM1-D-DM0        | = | SDRAM Data Input/Output Mask                                                                                                                                                                                                                                                                        |

| D-WE#              | = | SDRAM Write Enable input                                                                                                                                                                                                                                                                            |

| D-V <sub>SS</sub>  | = | SDRAM Ground                                                                                                                                                                                                                                                                                        |

| D-V <sub>SSQ</sub> | = | SDRAM Input/Output Buffer ground                                                                                                                                                                                                                                                                    |

| D-V <sub>CCQ</sub> | = | SDRAM Input/Output Buffer power supply                                                                                                                                                                                                                                                              |

| D-V <sub>CC</sub>  | = | SDRAM device power supply                                                                                                                                                                                                                                                                           |

|                    |   |                                                                                                                                                                                                                                                                                                     |

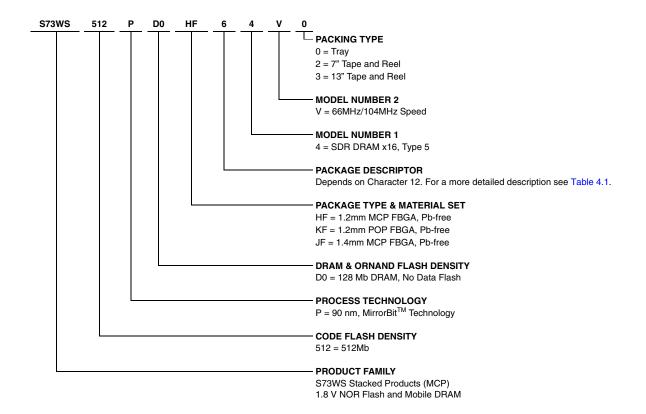

# 4. Ordering Information

The order number is formed by a valid combinations of the following:

Table 4.1 Character Position Descriptions (Sheet 1 of 2)

|              |              | Character 14 Description |                    |               |  |  |

|--------------|--------------|--------------------------|--------------------|---------------|--|--|

| Character 12 | Character 13 | Package Area             | Package Ball Count | Raw Ball Size |  |  |

|              | 0            | 7x9 mm                   | 56                 |               |  |  |

|              | 1            | 7x9 mm                   | 80                 |               |  |  |

|              | 2            | 8x11.6 mm                | 64                 |               |  |  |

| H, J, or G   | 3            | 8x11.6 mm                | 84                 |               |  |  |

|              | 4            | 9x12 mm                  | 84                 | 0.35 mm       |  |  |

|              | 5            | 9x12 mm                  | 115                | 0.35 11111    |  |  |

|              | 6            | 9x12 mm                  | 137                |               |  |  |

|              | 7            | 11x13 mm                 | 84                 |               |  |  |

|              | 8            | 11x13 mm                 | 115                |               |  |  |

|              | 9            | 11x13 mm                 | 137                |               |  |  |

Table 4.1 Character Position Descriptions (Sheet 2 of 2)

|              |              | Character 14 Description |                    |               |

|--------------|--------------|--------------------------|--------------------|---------------|

| Character 12 | Character 13 | Package Area             | Package Ball Count | Raw Ball Size |

|              | А            | 11x11 mm                 | 112                | 0.45 mm       |

|              | В            | 11x11 mm                 | 112                | 0.50 mm       |

|              | D            | 12x12 mm                 | 128                | 0.45 mm       |

|              | F            | 12x12 mm                 | 128                | 0.50 mm       |

| K            | G            | 14x14 mm                 | 152                | 0.45 mm       |

| N.           | Н            | 14x14 mm                 | 152                | 0.50 mm       |

|              | J            | 15x15 mm                 | 160                | 0.45 mm       |

|              | K            | 15x15 mm                 | 160                | 0.50 mm       |

| •            | L            | 17x17 mm                 | 192                | 0.45 mm       |

|              | M            | 17x17 mm                 | 192                | 0.50 mm       |

## 4.1 Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult your local sales office to confirm availability of specific valid combinations and to check on newly released combinations.

| S72WS-P Valid Combinations |                              |                       |                 |                  |                    |                  |            |                  |                     |

|----------------------------|------------------------------|-----------------------|-----------------|------------------|--------------------|------------------|------------|------------------|---------------------|

| Base Ordering<br>Number    | Package &<br>Material<br>Set | Package<br>Descriptor | Model<br>Number | Packing Type     | NOR Flash<br>Speed | DRAM<br>Supplier | DRAM Speed | Package Type     | Package<br>Markings |

| S73WS512PD0                | HF                           | 6                     | 4V              | 0, 2, 3 (Note 1) | 66 MHz             | Type 5           | 104 MHz    | 9x12 mm<br>(MCP) | (Note 2)            |

### Notes:

- 1. Packing Type 0 is standard. Specify other options as required.

- 2. BGA package marking omits leading S and packing type designator from ordering part number.

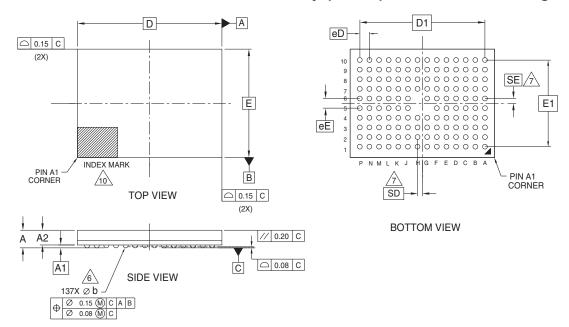

#### **Physical Dimensions** 5.

#### TLD137—137-ball Fine-Pitch Ball Grid Array (FBGA) 9 x 12.0 mm Package 5.1

| PACKAGE | TLD 137                       |            |      |                          |

|---------|-------------------------------|------------|------|--------------------------|

| JEDEC   | N/A                           |            |      |                          |

| DxE     | 12.00 mm x 9.00 mm<br>PACKAGE |            |      |                          |

| SYMBOL  | MIN                           | NOM        | MAX  | NOTE                     |

| Α       |                               |            | 1.20 | PROFILE                  |

| A1      | 0.17                          |            |      | BALL HEIGHT              |

| A2      | 0.81                          |            | 0.97 | BODY THICKNESS           |

| D       |                               | 12.00 BSC. |      | BODY SIZE                |

| E       |                               | 9.00 BSC.  |      | BODY SIZE                |

| D1      |                               | 10.40 BSC. |      | MATRIX FOOTPRINT         |

| E1      |                               | 7.20 BSC.  |      | MATRIX FOOTPRINT         |

| MD      |                               | 14         |      | MATRIX SIZE D DIRECTION  |

| ME      | 10                            |            |      | MATRIX SIZE E DIRECTION  |

| n       |                               | 137        |      | BALL COUNT               |

| φb      | 0.35 0.40 0.45                |            | 0.45 | BALL DIAMETER            |

| eЕ      | 0:80 BSC.                     |            |      | BALL PITCH               |

| eD      | 0.80 BSC                      |            |      | BALL PITCH               |

| SD / SE | 0.40 BSC.                     |            |      | SOLDER BALL PLACEMENT    |

|         | G5,H5,H6                      |            |      | DEPOPULATED SOLDER BALLS |

#### NOTES:

- DIMENSIONING AND TOLERANCING METHODS PER

- ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. BALL POSITION DESIGNATION PER JESD 95-1, SPP-010.

- 4. e REPRESENTS THE SOLDER BALL GRID PITCH.

- SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

n IS THE NUMBER OF POPULTED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

6 DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

7 SD AND SE ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW SD OR SE = 0.000.

WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, SD OR SE = e/2

"+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED BALLS.

A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK, METALLIZED MARK INDENTATION OR OTHER MEANS.

3393\ 16-038.22a

# 6. Revision History

## 6.1 Revision A (March 16, 2006)

Initial release.

### Colophon

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for any use that includes fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for any use where chance of failure is intolerable (i.e., submersible repeater and artificial satellite). Please note that Spansion will not be liable to you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products. Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the US Export Administration Regulations or the applicable laws of any other country, the prior authorization by the respective government entity will be required for export of those products.

#### Trademarks and Notice

The contents of this document are subject to change without notice. This document may contain information on a Spansion product under development by Spansion. Spansion reserves the right to change or discontinue work on any product without notice. The information in this document is provided as is without warranty or guarantee of any kind as to its accuracy, completeness, operability, fitness for particular purpose, merchantability, non-infringement of third-party rights, or any other warranty, express, implied, or statutory. Spansion assumes no liability for any damages of any kind arising out of the use of the information in this document.

Copyright © 2006 Spansion LLC. All Rights Reserved. Spansion, the Spansion logo, MirrorBit, ORNAND, and combinations thereof are trademarks of Spansion LLC. Other names are for informational purposes only and may be trademarks of their respective owners.