INTEGRATED CIRCUITS

Objective specification File under Integrated Circuits, ICXX 2001 September 19

### UAA3536

#### FEATURES

- · Multiple band application for GSM, DCS and PCS cellular phone systems

- Compliant to GPRS class 12 operation

- Compliant to EDGE RX operation

- · Low noise and wide dynamic range low IF receiver

- More than 35 dB on chip image rejection in receive

- More than 84 dB gain control range in receive

- Integrated channel filter

- Integrated TX filters

- High precision IQ modulator

- Multi-Band Tx modulation loop architecture including offset mixer and phase-frequency detector

- · Fully integrated fractional N RF synthesiser with AFC control possibility

- · Fully integrated RF VCO with integrated supply regulator

- Semi integrated reference oscillator with integrated coarse AFC possibility and with integrated supply regulator

- Two outputs to control RF frontend switches (pin diodes)

- Fully differential design minimizing cross-talk and spurs

- Functional down to 2.4 V and up to 3.3 V

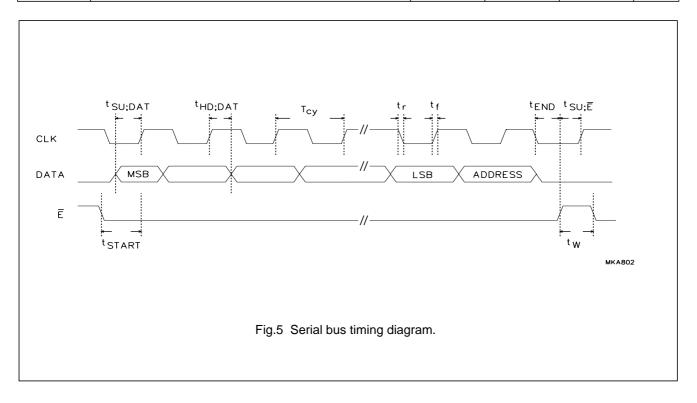

- 3-wire serial bus interface

- HVQFN40 package

#### APPLICATIONS

• GSM 900 MHz, DCS 1800 MHz and PCS 1900 MHz hand-held transceivers.

#### **GENERAL DESCRIPTION**

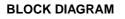

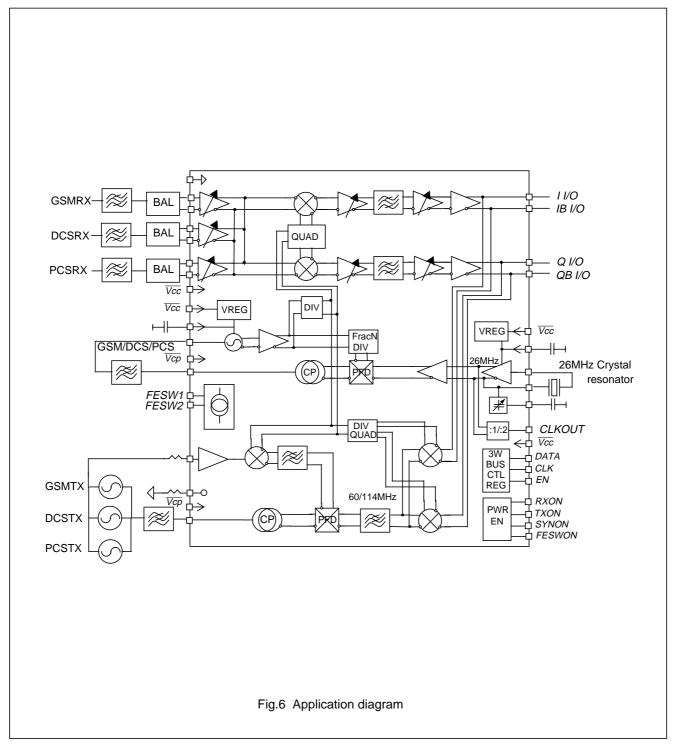

The UAA3536 integrates the receiver and most of the transmitter section of GSM, DCS and PCS hand-held transceiver.

The receiver consists of two distinct parts. First, the RF receiver front-end which amplifies the GSM, DCS or PCS aerial signal, converts the chosen channel down to a low IF of 100 kHz, and provides in addition more than 35 dB image suppression. The frontend gain is switchable by one 20dB gain step. Some selectivity is provided at this stage by an on-chip low-pass filter, and channel selectivity is provided by means of a high performance integrated band-pass filter. Then, the IF section further amplifies the wanted channel, performs gain control to tune the output level to the desired value and rejects DC. The IF gain can be varied over a range of 68 dB.

The transmitter consists of a closed loop modulation architecture. The down converted feedback RF transmit signal is mixed with the IQ modulation signals. In a phase frequency detector it is compared with the LO signal divided down to about 60 or 114 MHz and drives the charge pump for the external TX VCO.

The local oscillators (LO) signals required are provided by an on chip VCO for operation of the RF section. The frequencies of the RF VCO are set by an internal fractional N synthesiser PLL circuit, which are programmable via a 3-wire serial bus. Comparison frequency is 26 MHz (12 Hz step programmability) derived from the 26 MHz reference signal which is generated with the semi integrated reference oscillator. The quadrature phase RF LO signals required for IQ mixers in reception are generated internally. The reference oscillator can be without frequency control. In this case the precise receive and transmit frequencies have to be programmed via the fractional N synthesiser. A coarse AFC control is possible via programmable switched capacitors.

Two outputs are available to control external RF frontend switches, e.g. used for band selection.

**UAA3536**

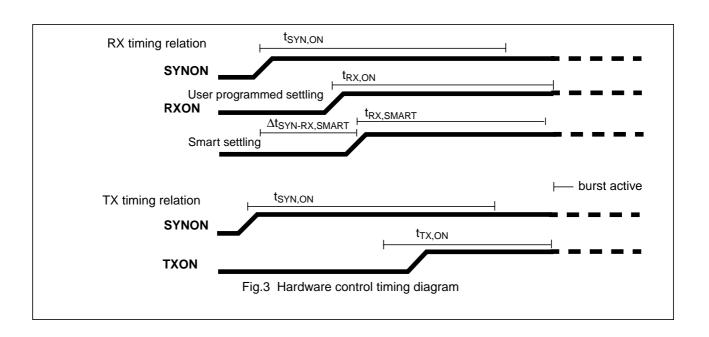

The circuit can be powered-up into four different modes, RX, TX, SYN or REF mode, depending on supply voltages applied, the logical level at pins RXON/TXON/SYNON and the 3-wire bus serial programming. In RX (TX) mode, all sections required for receive (transmit) are turned on. The SYN mode is used to power-up the synthesiser and the RF VCO prior to the RX or TX mode. In the SYN mode, some internal LO buffers are also powered-up such that VCO pulling is minimized when switching on the receiver or the transmitter. The reference oscillator (REF mode) is turned on by applying the supply voltage. Additionally band selection is done using the 3-wire bus serial programming allowing the proper enabling of the LNAs and TX charge-pump current programming.

#### **ORDERING INFORMATION**

| TYPE NUMBER |         | PACKAGE                                                                                  |          |

|-------------|---------|------------------------------------------------------------------------------------------|----------|

|             | NAME    | DESCRIPTION                                                                              | VERSION  |

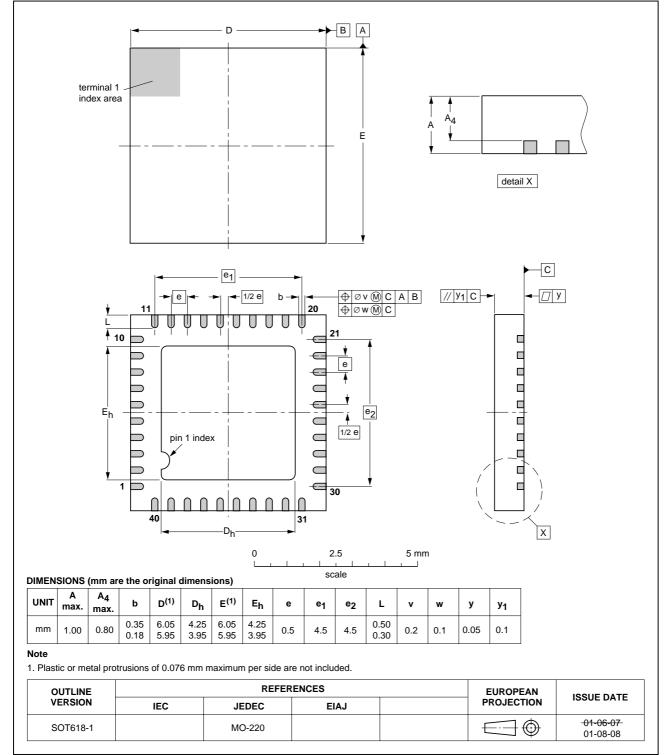

| UAA3536HN   | HVQFN40 | plastic, heatsink very thin quad flat package; 40 terminals; $6 \times 6 \times 0.85$ mm | SOT618-1 |

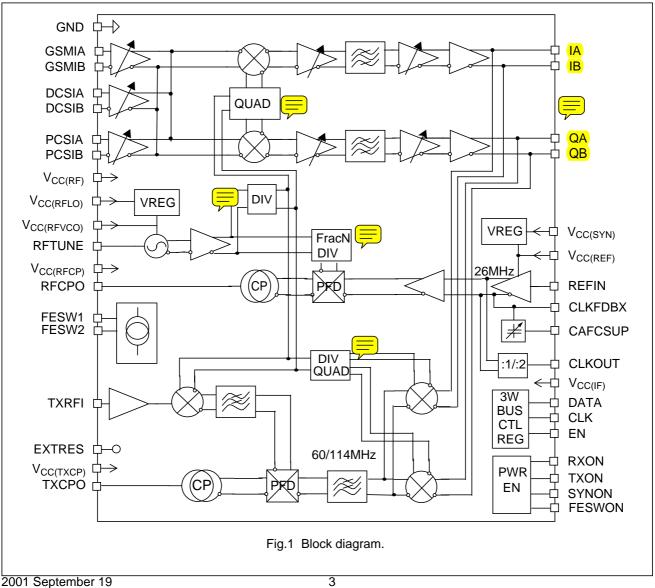

#### PINNING

| SYMBOL                 | PIN | DESCRIPTION                                      |

|------------------------|-----|--------------------------------------------------|

| TXRFI                  | 1   | Input from RF transmit VCOs                      |

| EXTRES                 | 2   | reference resistor for transmit modulation loop  |

| ТХСРО                  | 3   | transmit modulation loop                         |

|                        |     | charge-pump output                               |

| V <sub>CC(TXCP)</sub>  | 4   | transmit modulation loop<br>charge-pump supply   |

| TXON                   | 5   | TX mode control pin                              |

| IA                     | 6   | baseband input-output; I path                    |

| IB                     | 7   | baseband input-output; I path                    |

| QA                     | 8   | baseband input-output; Q path                    |

| QB                     | 9   | baseband input-output; Q path                    |

| V <sub>CC(IF)</sub>    | 10  | IF supply                                        |

| CLKOUT                 | 11  | reference oscillator output                      |

| CAFCSUP                | 12  | coarse AFC memory supply                         |

| CLKFDBX                | 13  | reference oscillator feedback                    |

| REFGND                 | 14  | Ground for reference oscillator                  |

| REFIN                  | 15  | reference oscillator input                       |

| V <sub>CC(REF)</sub>   | 16  | reference oscillator supply                      |

| DATA                   | 17  | 3-wire bus; DATA input                           |

| CLK                    | 18  | 3-wire bus; CLOCK input                          |

| EN                     | 19  | 3-wire bus; ENABLE control pin                   |

| V <sub>CC(RFCP)</sub>  | 20  | RF charge-pump supply                            |

| RFCPO                  | 21  | RF charge-pump output                            |

| V <sub>CC(SYN)</sub>   | 22  | synthesizer supply                               |

| RXON                   | 23  | RX mode control pin                              |

| SYNON                  | 24  | SYN mode control pin                             |

| V <sub>CC(RFVCO)</sub> | 25  | RF VCO supply                                    |

| RFTUNE                 | 26  | tuning input of RF VCO                           |

| GNDTUNE                | 27  | Ground for RF VCO tuning                         |

| V <sub>CC(RFLO)</sub>  | 28  | RF LO supply                                     |

| FESW1                  | 29  | frontend switch control output                   |

| FESW2                  | 30  | frontend switch control output                   |

| V <sub>CC(RF)</sub>    | 31  | RF front-end and transmit modulation loop supply |

| GSMIA                  | 32  | receiver GSM RF input                            |

| GSMIB                  | 33  | receiver GSM RF input                            |

| RFGND1                 | 34  | Ground for RF frontend                           |

| PCSIA                  | 35  | receiver PCS RF input                            |

| PCSIB                  | 36  | receiver PCS RF input                            |

UAA3536

## Low power GSM/DCS/PCS multi-band transceiver

| SYMBOL | PIN | DESCRIPTION                   |

|--------|-----|-------------------------------|

| RFGND2 | 37  | Ground for RF frontend        |

| DCSIA  | 38  | receiver DCS RF input         |

| DCSIB  | 39  | receiver DCS RF input         |

| FESWON | 40  | frontend switch control input |

UAA3536

#### FUNCTIONAL DESCRIPTION

#### **RF Receiver**

The receiver front-end converts the aerial RF signal from EGSM (925 - 960 MHz), DCS (1805 - 1880 MHz) or PCS (1930 - 1990 MHz) bands down to a low intermediate frequency (IF) of 100 kHz. The first stages are symmetrical low noise amplifiers (LNAs) with one 20dB gain step. They are matched to 50 W using external baluns. The LNAs are followed by an I, Q down-mixer. It consists of two mixers in parallel but driven by quadrature out of phase LO signals. The In phase (I) and Quadrature phase (Q) IF signals are low pass filtered to provide protection from high frequency offset interferers. The low IF I and Q signals are then fed into the channel filter.

#### Channel filter and AGC

The front-end low IF I and Q outputs enter the integrated bandpass channel filter with provision for five 8 dB gain steps in front of the filter. The filter is a self-calibrated fifth order band-pass filter centred around 100 kHz and has a bandwidth of 240 kHz for GSM mode, 300kHz for EDGE mode. Being filtered the low IF I and Q are further amplified with provision for ten 4 dB gain steps and fully integrated DC offset compensation. Realised with an active high pass circuit this compensation either operates continuously or keeps the acquired offset correction during the bursts depending on the programming. The low IF output buffer provides close to rail-to-rail output signals.

#### **IQ** modulator

I and Q baseband signals are applied to the IQ modulator that shifts the modulation spectrum up to the transmit IF. It is designed for low harmonic distortion, low carrier leakage and high image rejection to keep the phase error as small as possible. The modulator is loaded at its IF output by an integrated low pass filter that supress unwanted spurs prior to get into the phase detector. The clock drive is generated by division of the RFLO signal provided for the transmit offset mixer.

#### **Transmit modulation loop**

The analog transmit modulation loop is composed by an on-chip offset mixer with spur filter and by a phase/frequency detector with charge pump. The loop is closed off-chip by a loop filter and transmit VCO. The analog PLL copies the modulation to the off-chip transmit VCO and acts as a tracking filter. A PLL of at least third order is required to meet noise requirements at 20 MHz offset from carrier. The PLL bandwidth must be greater than 700 kHz in order to keep a low dynamic phase error and to minimize the acquisition time. The IF frequencies used are about 60 MHz for GSM/PCS and about 114 MHz for DCS.

#### **RF VCO**

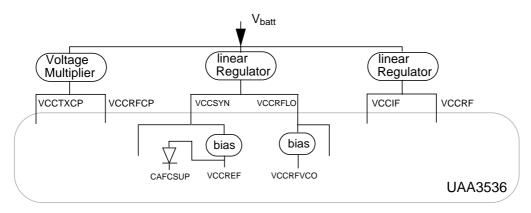

The RF VCO is fully integrated and self calibrating on manufacturing tolerances. It consists of 20 different frequency ranges that are selected internally depending on the frequency programming. It covers the necessary bandwidth of 1804 to 1991MHz and is tuned via the RF charge pump and the external loop filter. An internal supply voltage regulator using  $V_{CC(RFLO)}$  as input supplies the RF VCO and minimises parasitic couplings and pushing. This regulator and the RF VCO are turned on by the SYNON signal. The 20 different frequency ranges are realised by switching of varactors' cathodes between GND and an internal supply that is generated dynamically. Due to slow discharge of this supply burst mode operation is possible only. For test purpose a fixed supply can be chosen.

#### **RF LO section**

The RF LO section covering the 1804 to 1991 MHz bandwidth is driven by the internal RF VCO module. It includes the LO buffering for the RF PLL, a divider by two or one for GSM and DCS/PCS respectively which drives a quadrature generation network to supply the RX IQ down-mixer or it drives the transmit modulation loop offset mixer and the clock divider driving the IQ modulator.

UAA3536

#### **RF FracN Synthesiser PLL**

A high performance RF fractional N synthesiser PLL is included on chip which allows to synthesise the frequencies of the RF VCO. Very low close-in phase noise is achieved which allows to widen the PLL loop bandwidth for shorter settling time. The programmable 'main' dividers are controlled by a second order SD modulus controller. They divide the RF VCO signal down to frequencies of 26 MHz (12 Hz step programmability). Their phase is then compared in a digital phase/frequency detector (PFD) to that of the 26 MHz reference clock signal. The phase error information is fed back to the VCO via the charge pump circuit that 'sources' into or 'sinks' current from the loop filter capacitor, changing the VCO frequency such that the loop gets finally 'phase locked'. The charge pump output current is adapted internally to compensate for changes of RF VCO gain so that the tolerance of the PLL bandwidth is minimised.

#### **Reference Oscillator**

An amplifier is integrated to build a crystal oscillator. Externally only a quartz and few passive components are needed. 26 MHz is the reference frequency. It is turned on when the supply voltage  $V_{CC(SYN)}$  is applied. After division by two a reference clock of 13MHz is supplied to the other parts of the system through the pin CLKOUT. On request 26MHz can be made available on this pin. An internal supply voltage regulator using  $V_{CC(SYN)}$  as input supplies the reference oscillator and minimises parasitic couplings and pushing. AFC can be done by the FracN synthesiser programming or pia an external varactor. Additionally a coarse AFC control with a resolution of 8 bit is integrated via switchable capacitors. The programming of the coarse AFC capacitors is maintained during sleep mode through supplying the register via pin CAFCSUP. An off chip capacitor is connected to CAFCSUP and is charged via an internal diode from pin  $V_{CC(REF)}$ . Furthermore instead of realising this semi-integrated oscillator a reference clock coming from an external module can be applied to pin REFIN. This module can be supplied through  $V_{CC(REF)}$  pin.

#### **Control of frontend switches**

Two outputs are provided to drive RF switches of the phone, e.g. for switching between bands.

#### **Power-up reset**

A power-up reset generates a reset pulse at power supply ramp-up to initialise digital functions.

### UAA3536

#### LIMITING VALUES

| SYMBOL            | DESCRIPTION                                | MIN. | MAX. | UNIT |

|-------------------|--------------------------------------------|------|------|------|

| T <sub>amb</sub>  | operating ambient temperature              | -30  | +70  | °C   |

| T <sub>stg</sub>  | storage temperature                        | -40  | +150 | °C   |

| V <sub>CC</sub>   | supply voltages                            | -0.3 | 3.6  | V    |

| V <sub>CCCP</sub> | supply voltages for RX and TX charge pumps | -0.3 | 4.25 | V    |

| P <sub>MAX</sub>  | maximum power dissipation                  | -    | 1    | W    |

#### THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                | VALUE | UNIT |

|---------------------|------------------------------------------|-------|------|

| R <sub>th j-c</sub> | thermal resistance from junction to case | 25    | K/W  |

#### **DC CHARACTERISTICS**

$V_{CC}$  = 2.6V;  $V_{CC}CP$  = 4.0 V;  $T_{amb}$  = 25 °C; unless otherwise stated.

| SYMBOL                  | PARAMETER                                                                | CONDITIONS                                                                                                         | MIN.              | TYP.              | MAX.             | UNIT |

|-------------------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|------------------|------|

| Pins VCC(F              | RF), VCC(IF), VCC(RFLO) and                                              | VCC(SYN)                                                                                                           | •                 |                   |                  | -    |

| V <sub>CC</sub>         | supply voltage                                                           | note 1                                                                                                             | <mark>2.4</mark>  | -                 | <mark>3.3</mark> | V    |

| Pin VCC(R               | FVCO)                                                                    |                                                                                                                    |                   |                   |                  |      |

| V <sub>CC(RFVCO</sub> ) | internal supply voltage of RF VCO                                        | output only                                                                                                        | <mark>1.75</mark> | <mark>1.87</mark> | 2                | V    |

| Pin VCC(R               | EF)                                                                      |                                                                                                                    | •                 | •                 | ł                | •    |

| V <sub>CC(REF)</sub>    | internal supply voltage of reference oscillator                          | output only;<br>VCC(SYN)>=2.6V;<br>-30°C<=T <sub>amb</sub> <=70°C                                                  | 2.3               | -                 | 2.5              | V    |

| IOUTREF                 | source current to external                                               | VCC(SYN) turned on                                                                                                 | 2                 | -                 | -                | mA   |

| Pin VCC(R               | FCP)                                                                     |                                                                                                                    |                   |                   |                  |      |

| V <sub>CC(RFCP)</sub>   | supply voltage of phase detector and charge pump                         |                                                                                                                    | 3.8               | -                 | 4.25             | V    |

| Pin VCC(T               | KCP)                                                                     |                                                                                                                    | •                 | •                 |                  | •    |

| V <sub>CC(TXCP)</sub>   | supply voltage of phase detector and charge pump                         |                                                                                                                    | 2.6               | -                 | 4.25             | V    |

| Pins VCC(F              | RF), VCC(IF), VCC(RFLO), VC                                              | C(SYN), VCC(TXCP) and VCC                                                                                          | (RFCP)            | •                 |                  | 1    |

| I <sub>CCPD</sub>       | supply current ( $V_{CC} = 2.6 V$ ;<br>$V_{CC}CP = 4.0 V$ ); normal mode | power-down (total);<br>VCC(SYN)=0V;<br>RXON, TXON, SYNON and<br>FESWON = Hi<br>Z; pins EN, DATA,<br>and CLK = Hi Z | -                 | 10                | 30               | μΑ   |

| I <sub>CCPD</sub> Pres  | supply current ( $V_{CC} = 2.6V$ , $V_{CC}CP = 4.0V$ ); preset mode      | power-down (total);<br>VCC(SYN)=0V;<br>RXON, TXON, SYNON and<br>FESWON = 0; pins EN,<br>DATA and CLK = 1           | -                 | 100               | 200              | μΑ   |

| SYMBOL             | PARAMETER                                                              | CONDITIONS                                                                       | MIN. | TYP. | MAX. | UNIT |

|--------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|------|------|------|

| I <sub>CCREF</sub> | supply current REF mode                                                | reference oscillator active<br>(SYNVCC=2.6V)                                     | -    | 4.6  | 5.3  | mA   |

| I <sub>CCRX</sub>  | supply current RX mode                                                 | RX and SYN mode active;<br>FESW off                                              | -    | 69   | 82   | mA   |

| І <sub>сстх</sub>  | supply current TX mode                                                 | TX and SYN mode active;<br>FESW off                                              | -    | 69   | 87   | mA   |

| ICCTXFESW          | supply current TX mode,<br>FESW active                                 | TX and SYN mode active;<br>I <sub>FESW1</sub> = 2mA;<br>I <sub>FESW2</sub> = 2mA | -    | 73   | 91   | mA   |

| I <sub>CCSYN</sub> | supply current SYN mode                                                | SYN mode active                                                                  | -    | 40   | 46   | mA   |

| Pin VCC(R          | F)                                                                     |                                                                                  |      |      |      | •    |

| I <sub>CCRX</sub>  | supply current of RF receiver<br>and RFQUAD (one LNA only)             | RX mode active                                                                   | -    | 18   | -    | mA   |

| I <sub>CCLNA</sub> | supply current of one LNA only                                         | RX mode active                                                                   | -    | 7.5  | -    | mA   |

| I <sub>ССТХ</sub>  | supply current of transmit<br>modulation loop (without<br>charge pump) | TX mode active                                                                   | -    | 14   | -    | mA   |

| Pin VCC(IF         | ·<br>·)                                                                |                                                                                  | •    |      |      |      |

| I <sub>CCRX</sub>  | supply current for IQ low IF bandpass filter                           | RX mode active                                                                   | -    | 4    | -    | mA   |

| I <sub>CCRX</sub>  | supply current IQ AGC and buffer                                       | RX mode active                                                                   | -    | 3    | -    | mA   |

| I <sub>CCTX</sub>  | supply current IQ Modulator path                                       | TX mode active                                                                   | -    | 10.5 | -    | mA   |

| Pin VCC(R          | FLO)                                                                   |                                                                                  |      |      |      | •    |

| I <sub>CCRX</sub>  | supply current of RF VCO,<br>RF LO buffer and divider<br>section       | SYN mode active;<br>RX mode active                                               | -    | 24   | -    | mA   |

| I <sub>CCTX</sub>  | supply current of RF VCO,<br>RF LO buffer and divider<br>section       | SYN mode active;<br>TX mode active                                               | -    | 28   | -    | mA   |

| I <sub>CCSYN</sub> | supply current of RF VCO<br>and RF LO buffer                           | SYN mode active                                                                  | -    | 19   | -    | mA   |

| Pin VCC(S          | YN)                                                                    |                                                                                  |      |      |      |      |

| I <sub>CCREF</sub> | supply current of reference oscillator                                 |                                                                                  | -    | 4.6  | -    | mA   |

| I <sub>CCSYN</sub> | supply current of reference oscillator and RF synthesizer              | SYN mode active                                                                  | -    | 17   | -    | mA   |

### UAA3536

| SYMBOL              | PARAMETER                                    | CONDITIONS                                                                                                                                                                                        | MIN. | TYP.     | MAX.              | UNIT |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------------------|------|

| Pin VCC(R           | FCP)                                         |                                                                                                                                                                                                   | 1    | -!       |                   |      |

| I <sub>CPRF</sub>   | supply current RFLO charge pump              | SYN mode active;<br>ext. resistor = 22.6 k $\Omega$ (1%);<br>programmed to 0.52mA;<br>in lock:<br>during freq. acquisition:<br>during precharge (for 32.5 $\mu$ s<br>after synth. turnon); note 2 | -    | -        | 0.32<br>0.87<br>6 | mA   |

| Pin VCC(T           | XCP)                                         |                                                                                                                                                                                                   |      |          |                   |      |

| I <sub>CPTX</sub>   | supply current TX charge<br>pump             | TX mode active;<br>ext. resistor = 22.6 k $\Omega$ (1%);<br>TXI1=1; TXI2=1;<br>in lock;<br>during freq. acquisition;<br>note 2                                                                    | -    | -        | 0.9<br>2.45       | mA   |

| Pins IA, IB         | , QA and QB                                  |                                                                                                                                                                                                   |      |          |                   |      |

| V <sub>IQ</sub>     | common mode input-output<br>IQ voltage range | (Via + Vib) / 2 or<br>(Vqa + Vqb) / 2; note 3                                                                                                                                                     | 1.15 | 1.25     | 1.35              | V    |

| Pin EXTRE           | ES                                           |                                                                                                                                                                                                   |      |          |                   |      |

| V <sub>EXTRES</sub> | reference voltage for I <sub>CP</sub>        | R <sub>ext</sub> =22.6kΩ (1%)                                                                                                                                                                     | 0.95 | 1.0      | 1.05              | V    |

| Pin CAFC            | SUP                                          |                                                                                                                                                                                                   |      | ·        |                   | •    |

| VCAFCSUP            | internal supply voltage                      | SYNON=1                                                                                                                                                                                           | -    | VCC(REF) | -                 |      |

| Pins FESV           | V1, FESW2 (4)                                |                                                                                                                                                                                                   | ·    | ·        |                   |      |

| V <sub>FESW</sub>   | output voltage                               | I <sub>source</sub> =10mA                                                                                                                                                                         | 2.3  | -        | 2.5               | V    |

| V <sub>FESW</sub>   | output voltage                               | outputs in tri-state                                                                                                                                                                              | 0    | -        | VCC(RF)           |      |

| Logical in          | put levels: pins EN, DATA, CL                | K, RXON, TXON, SYNON, FES                                                                                                                                                                         | SWON |          |                   |      |

| V <sub>IH</sub>     | logical HIGH level                           |                                                                                                                                                                                                   | 0.9  | -        | VCC(SYN)<br>+ 0.3 | V    |

| V <sub>IL</sub>     | logical LOW level                            |                                                                                                                                                                                                   | -0.3 | -        | 0.3               | V    |

Notes:

1. For VCC < 2.6V only functionality is guaranteed, AC characteristics are not guaranteed

2. These performances are measured and guaranteed on evaluation board.

3. RX mode: DC supplied from the IC TX mode: DC supplied from external

4. Currents are supplied from open drain PMOS transistors.

UAA3536

## Low power GSM/DCS/PCS multi-band transceiver

#### AC CHARACTERISTICS

$V_{CC}$  = 2.6V;  $V_{CC}CP$  = 4.0 V;  $T_{amb}$  = -30 to +70 C; unless otherwise stated

#### **RF** receiver section

Measured in a 50  $\Omega$  impedance system, including external input baluns and matching networks to 50  $\Omega$ .

| SYMBOL           | PARAMETER                                   | CONDITIONS              | MIN. | TYP. | MAX. | UNIT |

|------------------|---------------------------------------------|-------------------------|------|------|------|------|

| Pins GSMI        | A and GSMIB                                 |                         |      |      |      | •    |

| f <sub>RF</sub>  | RF input frequency range                    |                         | 925  | -    | 960  | MHz  |

| R <sub>IN</sub>  | differential input resistance               | parallel RC input model | -    | 110  | -    | Ω    |

| C <sub>IN</sub>  | differential input capacitance              | parallel RC input model | -    | 1.0  | -    | pF   |

| NF               | noise figure; max AGC gain                  | notes 1, 1              | -    | 3.7  | 4.2  | dB   |

| $NF_{LG}$        | noise figure; max AGC gain;<br>low LNA gain | HGLG = 0; notes 1, 2    | -    | 23   | -    | dB   |

| $\Delta G_{LNA}$ | LNA gain step                               | HGLG = 0 <-> 1          | 16   | 20   | 24   | dB   |

| G <sub>OFF</sub> | LNA off-state gain difference               | LNA = 1 <-> 0; note 1   | 45   | -    | -    | dB   |

| P <sub>OFF</sub> | LNA off-state power handling                | LNA = 0; note 1, 3      | 3    | -    | -    | dBm  |

| Pins DCSI        | A and DCSIB                                 |                         |      | •    | ·    |      |

| f <sub>RF</sub>  | RF input frequency range                    |                         | 1805 | -    | 1880 | MHz  |

| R <sub>IN</sub>  | differential input resistance               | parallel RC input model | -    | 170  | -    | Ω    |

| C <sub>IN</sub>  | differential input capacitance              | parallel RC input model | -    | 0.8  | -    | pF   |

| NF               | Noise figure, max AGC gain                  | notes 1, 2              | -    | 4.2  | 4.7  | dB   |

| $NF_{LG}$        | noise figure; max AGC gain;<br>low LNA gain | HGLG = 0; notes 1, 2    | -    | 23   | -    | dB   |

| $\Delta G_{LNA}$ | LNA gain step                               | HGLG = 0 <-> 1          | 16   | 20   | 24   | dB   |

| G <sub>OFF</sub> | LNA off-state gain difference               | LNA = 1 <-> 0; note 1   | 45   | -    | -    | dB   |

| P <sub>OFF</sub> | LNA off-state power handling                | LNA = 0; notes 1, 3     | 6    | -    | -    | dBm  |

| Pins PCSI/       | A and PCSIB                                 |                         | ·    |      |      |      |

| f <sub>RF</sub>  | RF input frequency range                    |                         | 1930 | -    | 1990 | MHz  |

| R <sub>IN</sub>  | differential input resistance               | parallel RC input model | -    | 170  | -    | Ω    |

| C <sub>IN</sub>  | differential input capacitance              | parallel RC input model | -    | 0.7  | -    | pF   |

| NF               | Noise figure, max AGC gain                  | notes 1, 2              | -    | 4.4  | 4.9  | dB   |

| $NF_{LG}$        | noise figure; max AGC gain;<br>low LNA gain | HGLG = 0; notes 1, 2    | -    | 23   | -    | dB   |

| $\Delta G_{LNA}$ | LNA gain step                               | HGLG = 0 <-> 1          | 16   | 20   | 24   | dB   |

| G <sub>OFF</sub> | LNA off-state gain difference               | LNA = 1 <-> 0; note 1   | 45   | -    | -    | dB   |

| P <sub>OFF</sub> | LNA off-state power handling                | LNA = 0; note 1, 3      | 6    | -    | -    | dBm  |

| SYMBOL             | PARAMETER                                                  | CONDITIONS                                                                                                                           | MIN.       | TYP. | MAX.     | UNIT     |

|--------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------|------|----------|----------|

| Pins GSMI          | A, GSMIB, DCSIA, DCSIB, PC                                 | SIA and PCSIB                                                                                                                        | 1          |      |          |          |

| S11                | input power matching                                       | note 1                                                                                                                               | -          | -15  | -10      | dB       |

| SPURIN             | spurious power level at RF input                           | in 900 to 1000 MHz band,<br>note1                                                                                                    | -          | -    | -57      | dBm      |

|                    |                                                            | in 1800 to 2000 MHz band, note 1                                                                                                     | -          | -    | -47      | dBm      |

|                    |                                                            | out of preceding bands, note 1                                                                                                       | -          | -    | -45      | dBm      |

| CP1                | 1 dB input compression point; minimum AGC gain             | T <sub>amb</sub> = 25 °C; HGLG=1;<br>note 1                                                                                          | -25        | -    | -        | dBm      |

| CP1 <sub>LG</sub>  | 1 dB input compression point; minimum AGC gain             | T <sub>amb</sub> = 25 °C; HGLG=0;<br>note 1                                                                                          | -7         | -    | -        | dBm      |

| IP3                | input referred 3rd order<br>intercept; maximum AGC<br>gain | T <sub>amb</sub> = 25 °C; HGLG=1;<br>notes 1, 4                                                                                      | -18        | -    | -        | dBm      |

| IP3 <sub>LG</sub>  | input referred 3rd order<br>intercept; maximum AGC<br>gain | T <sub>amb</sub> = 25 °C; HGLG=0;<br>notes 1, 4                                                                                      | 0          | -    | -        | dBm      |

| IP2                | input referred 2nd order<br>intercept; maximum AGC<br>gain | T <sub>amb</sub> = 25 °C; HGLG=1;<br>notes 1,5                                                                                       | 27         | -    | -        | dBm      |

| IP2 <sub>LG</sub>  | input referred 2nd order<br>intercept; maximum AGC<br>gain | T <sub>amb</sub> = 25 °C; HGLG=0;<br>notes1, 5                                                                                       | 40         | -    | -        | dBm      |

| Blocking           | C/N ratio at blocking                                      | $T_{amb} = 25 \text{ °C}; \Delta f = 3 \text{ MHz};$<br>GSM: $P_w = -101 \text{dBm};$<br>$P_{int} = -25 \text{dBm}; \text{ note } 1$ | 8          | -    | -        | dB       |

|                    |                                                            | $P_{int} = -28 dBm;$ note 1<br>DCS/PCS: $P_w = -101 dBm;$<br>$P_{int} = -28 dBm;$ note 1                                             | 8          | -    | -        |          |

| IMrej              | image rejection                                            | $\Delta f_{IF} = 200 \text{ kHz}; T_{amb} = 25 \text{ °C};$<br>note 1                                                                | 35         | 38   | -        | dB       |

| ∆GvRF              | gain mismatch between operation of different bands         | note 1                                                                                                                               | -          | -    | 2        | dB       |

| Pins IA, IB        | , QA and QB (Rx mode)                                      |                                                                                                                                      |            |      |          |          |

| Gv <sub>MIN</sub>  | voltage conversion gain                                    | AGC gain set to min.;<br>HGLG=1; notes 1, 6                                                                                          | 20         | 26   | 32       | dB       |

| Gv <sub>MAX</sub>  | voltage conversion gain                                    | AGC gain set to max.;<br>HGLG=1; notes 1, 6                                                                                          | 90         | 94   | 98       | dB       |

| ∆GvBW              | gain difference between<br>GSM and EDGE mode               | RXBW = 0 <-> 1                                                                                                                       | -          | 1.7  | -        | dB       |

| ∆GvlQ              | gain mismatch I and Q paths                                |                                                                                                                                      | -          | -    | 0.5      | dB       |

| Gv <sub>STEP</sub> | voltage conversion gain step                               | note 6                                                                                                                               | -          | 4    | -        | dB       |

| AGC <sub>lin</sub> | gain control linearity                                     | T <sub>amb</sub> = 25 °C; note 6, 7<br>over any 20 dB gain range;<br>note 7                                                          | -2<br>-0.5 | -    | 2<br>0.5 | dB<br>dB |

### UAA3536

| SYMBOL               | PARAMETER                                                         | CONDITIONS                                                                                               | MIN.             | TYP.             | MAX.             | UNIT             |

|----------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|

| V <sub>OUT,lin</sub> | linear output voltage per pin                                     | $R_L = 100 \text{ k}\Omega \text{ differential;}$<br>$C_L=10\text{pF differential;}$<br>THD < 3%; note 8 | 0.75             | -                | -                | V <sub>pk</sub>  |

| V <sub>OUT,max</sub> | maximum output voltage per pin                                    | $R_L = 100 \ k\Omega$ differential;                                                                      | -                | -                | VCC(IF)<br>/ 2   | V <sub>pk</sub>  |

| I <sub>OUT</sub>     | maximum output current per pin                                    |                                                                                                          | -                | -                | 2000             | μA               |

| Voffset              | differential output offset voltage                                | in settled conditions                                                                                    | -300             | -                | +300             | mV               |

| f <sub>HP,-3dB</sub> | -3dB high pass corner<br>frequency (dc notch)                     | FASTSETL=0; STOPSETL=0                                                                                   | 4                | 6                | 8                | kHz              |

| BW <sub>GSM</sub>    | -3dB LOW IF filter bandwidth for GSm operation                    | 100 kHz center frequency<br>GSM mode; RXBW=0                                                             | 220              | 240              | 260              | kHz              |

| BW <sub>EDGE</sub>   | -3dB LOW IF filter bandwidth for EDGE operation                   | 100 kHz center frequency<br>EDGE mode; RXBW=1                                                            | <mark>275</mark> | <mark>300</mark> | <mark>325</mark> | <mark>kHz</mark> |

| $\Delta \tau_{gd}$   | group delay variation                                             | 30 kHz < f <sub>OUT</sub> < 170 kHz                                                                      | -                | 1.5              | 2                | μs               |

| Att <sub>GSM</sub>   | LOW IF filter attenuation<br>(5 <sup>th</sup> order) in GSM mode  | RXBW = 0<br>f <sub>OUT</sub> = 100 kHz ± 200 kHz                                                         | 17               | 31               | -                | dB               |

|                      |                                                                   | $f_{OUT}$ = 100 kHz ± 400 kHz                                                                            | 54               | 64               | -                | dB               |

|                      |                                                                   | $f_{OUT}$ = 100 kHz ± 600 kHz                                                                            | 73               | 82               | -                | dB               |

| Att <sub>EDGE</sub>  | LOW IF filter attenuation<br>(5 <sup>th</sup> order) in EDGE mode | $\begin{array}{l} RXBW = 1 \\ f_{OUT} = 100 \; kHz \pm 200 \; kHz \end{array}$                           | 10               | 19               | -                | dB               |

|                      |                                                                   | $f_{OUT}$ = 100 kHz ± 400 kHz                                                                            | 45               | 54               | -                | dB               |

|                      |                                                                   | $f_{OUT}$ = 100 kHz ± 600 kHz                                                                            | 64               | 73               | -                | dB               |

#### Notes:

- 1. Measured and guaranteed only on UAA3536 evaluation board.

- 2. This value excludes printed circuit board and balun losses.

- 3. No spurs are created as specified in SPUR<sub>IN</sub>.

- 4. IP3 related to an IM3 measurement with two tones at 800 and 1600kHz offset.

- 5. IP2 related to an IM2 measurement with two tones at 6 and 6.1MHz offset.

- 6. Voltage gain defined as the differential baseband RMS output voltage (either at pins IA and IB or pins QA and QB measured in standard load) divided by the RMS input voltage at the RF baluns.

- 7. Values are not applicable for HGLG=0.

- 8. Valid for following max. RF input power: HGLG=1: -31 dBm; HGLG=0: -15 dBm

#### Objective specification

## Low power GSM/DCS/PCS multi-band transceiver

#### Transmit modulation loop section

General conditions:  $V_{mod} = 0.5 V_{pk}$ ;  $f_{mod} = 67.7 kHz$ ; unless otherwise specified.

| SYMBOL                | PARAMETER                                     | CONDITIONS                                                                                                                                                                                                           | MIN.                         | TYP.                    | MAX.                         | UNIT  |

|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------|------------------------------|-------|

| Pins IA, IB           | , QA and QB (mode Tx)                         |                                                                                                                                                                                                                      | I                            | -                       |                              | 1     |

| f <sub>mod</sub>      | modulation frequency range                    | 3 dB low pass cutoff frequency                                                                                                                                                                                       | 1                            | -                       | -                            | MHz   |

| V <sub>mod</sub>      | modulation level                              | single ended; peak value                                                                                                                                                                                             | -                            | 0.5                     | 0.55                         | Vpk   |

| R <sub>IN</sub>       | dynamic input resistance                      | single ended                                                                                                                                                                                                         | -                            | 14.4                    | -                            | kΩ    |

| Offset mixe           | er: pin TXRFI                                 |                                                                                                                                                                                                                      |                              |                         |                              |       |

| f <sub>RF</sub>       | RF input frequency range                      | GSM<br>DCS<br>PCS                                                                                                                                                                                                    | 880<br>1710<br>1850          |                         | 915<br>1785<br>1910          | MHz   |

| R <sub>IN</sub>       | single ended input resistance                 | parallel RC input model<br>900MHz<br>1900MHz                                                                                                                                                                         | -                            | 65<br>35                | -                            | Ω     |

| C <sub>IN</sub>       | single ended input capacitance                | parallel RC input model<br>900MHz<br>1900MHz                                                                                                                                                                         | -                            | 3.4<br>2.0              | -                            | pF    |

| P <sub>IN</sub>       | input power                                   |                                                                                                                                                                                                                      | -22                          | -19                     | -16                          | dBm   |

| CP1                   | 1 dB input compression point                  | T <sub>amb</sub> = 25 °C                                                                                                                                                                                             | -                            | -22                     | -                            | dBm   |

| SPURIN                | spurious power level at RF                    | LO leakage                                                                                                                                                                                                           | -                            | -50                     | -45                          | dBm   |

|                       | input                                         | other                                                                                                                                                                                                                | -                            | -                       | -45                          | dBm   |

| V <sub>TXRFI</sub>    | range of applied voltage                      |                                                                                                                                                                                                                      | -0.3                         | -                       | VCC(RF)<br>+ 0.3             | V     |

| Phase dete            | ector: pin TXCPO                              |                                                                                                                                                                                                                      |                              | •                       |                              |       |

| I <sub>CP</sub>       | charge pump maximum sink<br>or source current | $\label{eq:Rext} \begin{split} & R_{ext} = 22.6 \ k\Omega \ (1\%); \\ & \text{over } V_{CP} \ range; \\ & TXI1 = 0; \ TXI2=0; \\ & TXI1 = 1; \ TXI2=0; \\ & TXI1 = 0; \ TXI2=1; \\ & TXI1 = 1; \ TXI2=1 \end{split}$ | 0.42<br>0.63<br>0.85<br>1.27 | 0.5<br>0.75<br>1<br>1.5 | 0.58<br>0.87<br>1.15<br>1.73 | mA    |

| f <sub>TXIF</sub>     | TXIF frequency                                | GSM/PCS<br>DCS                                                                                                                                                                                                       | -                            | <mark>60</mark><br>114  | -                            | MHz   |

| N <sub>TXIFDIV</sub>  | TXIF divider ratio                            | GSM/DCS;IFDIV=0<br>PCS; IFDIV=1                                                                                                                                                                                      | -                            | <mark>16</mark><br>32   | -                            | -     |

| KΦ                    | phase frequency detector gain                 |                                                                                                                                                                                                                      | -                            | I <sub>СР</sub> /2П     | -                            | A/rad |

| V <sub>CP</sub>       | charge pump output voltage                    |                                                                                                                                                                                                                      | 0.4                          | -                       | V <sub>CCCP</sub> -<br>0.4   | V     |

| R <sub>OUT</sub>      | output resistance                             | $V_{OUT} = V_{CCCP} / 2$                                                                                                                                                                                             | 100                          | -                       | -                            | kΩ    |

| R <sub>OUT(OFF)</sub> | output resistance to ground when powered down | TX mode disabled                                                                                                                                                                                                     | -                            | 500                     | -                            | Ω     |

### UAA3536

| SYMBOL                                             | PARAMETER                                                     | CONDITIONS                                                                           | MIN. | TYP.         | MAX.         | UNIT   |

|----------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------|------|--------------|--------------|--------|

| IQ Modulate                                        | pr; <mark>f<sub>mod</sub>=67.7kHz</mark>                      |                                                                                      |      |              |              |        |

| $\Phi_{ m NOISE}$ phase noise output power density |                                                               | $T_{amb} = 25 \text{ °C}; \Delta f = 400 \text{ kHz};$<br>note 1, 2; GSM<br>DCS, PCS | -    | -122<br>-118 | -120<br>-116 | dBc/Hz |

|                                                    |                                                               | $T_{amb}$ = 25 °C; $\Delta f$ = 1.8 MHz;<br>note 1, 2; GSM<br>DCS,PCS                | -    | -126<br>-122 | -123<br>-119 | dBc/Hz |

|                                                    |                                                               | $T_{amb}$ = 25 °C; $\Delta f$ = 20 MHz;<br>note 1, 2; GSM<br>DCS/PCS                 | -    | -            | -163<br>-157 | dBc/Hz |

| LO <sub>OUT</sub>                                  | local oscillator feedthrough                                  | $f = (F_c + f_{mod}) + - f_{mod};$<br>note 1, 2                                      | -    | -40          | -32          | dBc    |

| IM <sub>OUT</sub>                                  | image level                                                   | $f = (F_c + f_{mod}) + -2 * f_{mod};$<br>note 1, 2                                   | -    | -45          | -37          | dBc    |

| SPUR4f <sub>m</sub>                                | spurious level at 4 * f <sub>mod</sub><br>offset from wanted  | $f = (F_c + f_{mod}) + 4 * f_{mod};$<br>note 1, 2                                    | -    | -55          | -46          | dBc    |

| SPUR16f <sub>m</sub>                               | spurious level at 16 * f <sub>mod</sub><br>offset from wanted | $f = (F_c + f_{mod}) + - 16 * f_{mod};$<br>GSM, DCS; notes 1, 2, 3                   | -    | -            | -60          | dBc    |

| SPUR32fm                                           | spurious level at 32 * f <sub>mod</sub><br>offset from wanted | $f = (F_c + f_{mod}) + -32 * f_{mod};$<br>PCS; notes 1, 2, 3                         | -    | -            | -65          | dBc    |

| SPUR <sub>other</sub>                              | spurious level at other frequencies                           | abs(f-(F <sub>c</sub> +f <sub>mod</sub> ))>=400kHz<br>note1, 2                       | -    | -            | -70          | dBc    |

#### Notes

1. Measured and guaranteed only on UAA3536 evaluation board.

2. Measured at external transmit VCO output.

3. Spur is not critical for pseudo random and application modulation spectrum.

### UAA3536

#### Synthesizer and RF VCO

| SYMBOL                    | PARAMETER                                                          | CONDITIONS                                                                                                                                                                                                                                                                                                     | MIN.                                          | TYP.                                          | MAX.                                          | UNIT   |

|---------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|--------|

| RF synthes                | sizer; pin RFCPO                                                   | l                                                                                                                                                                                                                                                                                                              | I                                             |                                               | <b>!</b>                                      | ļ      |

| f <sub>RFLO</sub>         | synthesizer frequency range                                        |                                                                                                                                                                                                                                                                                                                | 1774.5                                        | -                                             | 2047.5                                        | MHz    |

| f <sub>compRF</sub>       | comparison frequency                                               |                                                                                                                                                                                                                                                                                                                | -                                             | 26                                            | -                                             | MHz    |

| f <sub>stepRF</sub>       | freq. step programmability                                         | f <sub>comp</sub> = 26 MHz                                                                                                                                                                                                                                                                                     | -                                             | 12.4                                          | -                                             | Hz     |

| Φ <sub>noise</sub>        | close-in phase noise                                               | $\Delta f = 2 \text{ kHz}; \text{ note } 1, 2$                                                                                                                                                                                                                                                                 | -                                             | -85                                           | -82                                           | dBc/Hz |

| P <sub>spur</sub>         | spur levels                                                        | ∆f > 400kHz                                                                                                                                                                                                                                                                                                    | -                                             | -                                             | -70                                           | dBc    |

| I <sub>CP</sub>           | Charge pump maximum sink<br>or source current                      | $R_{ext} = 22.6 kΩ (1\%);$<br>over V <sub>CP</sub> range;<br>currents set internally:<br>for I <sub>CP</sub> = 310μA<br>for I <sub>CP</sub> = 380μA<br>for I <sub>CP</sub> = 420μA<br>for I <sub>CP</sub> = 520μA<br>for I <sub>CP</sub> = 540μA<br>for I <sub>CP</sub> = 650μA<br>for I <sub>CP</sub> = 660μA | 260<br>320<br>350<br>440<br>450<br>540<br>550 | 310<br>380<br>420<br>520<br>540<br>650<br>660 | 360<br>440<br>490<br>600<br>630<br>760<br>770 | μΑ     |

|                           |                                                                    | for I <sub>CP</sub> = 800μA                                                                                                                                                                                                                                                                                    | 680                                           | 800                                           | 920                                           |        |

| KΦ                        | phase freq. detector gain                                          |                                                                                                                                                                                                                                                                                                                | -                                             | I <sub>CP</sub> /2П                           | -                                             | A/rad  |

| t <sub>prech</sub>        | loop filter precharge time                                         | after SYNON = 0 -> 1                                                                                                                                                                                                                                                                                           | -                                             | 32.5                                          | -                                             | μs     |

| l <sub>leak</sub>         | charge pump leakage current<br>in off state                        | over full V <sub>CP</sub> range                                                                                                                                                                                                                                                                                | -1                                            | -                                             | 1                                             | μA     |

| V <sub>CP</sub>           | charge pump output voltage                                         |                                                                                                                                                                                                                                                                                                                | 0.4                                           | -                                             | V <sub>CCCP</sub><br>- 0.4                    | V      |

| R <sub>OUT(OFF)</sub>     | output resistance to ground when powered down                      | SYN mode disabled                                                                                                                                                                                                                                                                                              | -                                             | 50                                            | -                                             | Ω      |

| Fractional N              | V Synthesiser                                                      |                                                                                                                                                                                                                                                                                                                | I                                             |                                               |                                               | 1      |

| N                         | integer divider ratio                                              | f <sub>comp</sub> =26MHz                                                                                                                                                                                                                                                                                       | 8                                             | -                                             | 28                                            |        |

| К                         | fractional divider<br>programming word                             | f <sub>comp</sub> =26MHz                                                                                                                                                                                                                                                                                       | 524,287                                       | -                                             | 1,572,864                                     |        |

| K <sub>frac</sub>         | fractional divider ratio                                           | f <sub>comp</sub> =26MHz                                                                                                                                                                                                                                                                                       | 0.25                                          | -                                             | 0.75                                          |        |

| Formulas fo               | or frequency calculation: f(VCC                                    | $D) = fcomp \times \left(\frac{N+128}{2} + K frac\right)$                                                                                                                                                                                                                                                      | ; Kfrac= $\left(\frac{K}{2^{21}}\right)$      | $+\frac{1}{2^{22}}$ ;                         |                                               |        |

| Integrated                | RF VCO: pin RFTUNE                                                 |                                                                                                                                                                                                                                                                                                                |                                               |                                               |                                               |        |

| f <sub>RF</sub>           | RF frequency range                                                 |                                                                                                                                                                                                                                                                                                                | 1804                                          | -                                             | 1991                                          | MHz    |

| G <sub>vco</sub>          | VCO gain                                                           | Vtune=2.0V                                                                                                                                                                                                                                                                                                     | 15                                            | 20                                            | 25                                            | MHz/V  |

| $\Delta G_{(VCO^*K\Phi)}$ | VCO gain times phase freq. detector gain variation                 | $\Delta G_{(VCO^*K\Phi)} / G_{(VCO^*K\Phi)}$                                                                                                                                                                                                                                                                   | -30                                           | -                                             | 30                                            | %      |

| R <sub>tune</sub>         | RFTUNE series resistor<br>inside the IC                            |                                                                                                                                                                                                                                                                                                                | -                                             | 50                                            | -                                             | Ω      |

| C <sub>tune</sub>         | parallel capacitor to ground inside the IC after R <sub>tune</sub> | freq = 400kHz; 0.4V;<br>freq = 400 kHz; 3.4V                                                                                                                                                                                                                                                                   | -                                             | 20<br>17                                      | -                                             | pF     |

### UAA3536

| SYMBOL                | PARAMETER            | CONDITIONS           | MIN. | TYP. | MAX.                      | UNIT  |

|-----------------------|----------------------|----------------------|------|------|---------------------------|-------|

| V <sub>tune</sub>     | tuning voltage range |                      | 0.4  | -    | V <sub>CCCP</sub><br>-0.4 | V     |

| $\Delta f_{VCC,RFLO}$ | pushing              |                      | -    | -    | 2                         | MHz/V |

| t <sub>VCO,cal</sub>  | VCO calibration time | after SYNON = 0 -> 1 | -    | 32.5 | -                         | μs    |

#### Notes

1. These performances are measured and guaranteed on evaluation board.

2. For measurement TX mode is activated and signal is taken from TX VCO output.

### UAA3536

#### Low noise crystal oscillator

| SYMBOL                   | PARAMETER                                     | CONDITIONS                                                | MIN.            | TYP.            | MAX.            | UNIT             |

|--------------------------|-----------------------------------------------|-----------------------------------------------------------|-----------------|-----------------|-----------------|------------------|

| Pins REFIN               | N, CLKFDBX                                    | 1                                                         | -!              |                 |                 | 1                |

| f <sub>REF</sub>         | reference frequency                           |                                                           | -               | 26              | -               | MHz              |

| R <sub>REFIN</sub>       | input resistance                              | f=26 MHz                                                  | -               | 2.6             | -               | kΩ               |

| C <sub>REFIN</sub>       | input capacitance                             | f=26 MHz                                                  | -               | 0.7             | -               | pF               |

| V <sub>REFIN</sub>       | intern. supplied DC input voltage             |                                                           | 1.0             | 1.1             | 1.15            | V                |

| R <sub>CLKFDBX</sub>     | output resistance                             | f=26 MHz; CAFC0//7=0;<br>f=26 MHz; CAFC0//7=1             | -               | 800<br>900      | -               | Ω                |

| V <sub>CLKFDBX</sub>     | DC output voltage                             |                                                           | 1.8             | 2.0             | 2.2             | V                |

| V <sub>IN(REFIN)</sub>   | input voltage level                           | note 1                                                    | 300             | -               | -               | mV <sub>pp</sub> |

| V <sub>CLKFDBX</sub>     | limiting output voltage swing                 | note 1                                                    | -               | 1700            | -               | mV <sub>pp</sub> |

| G <sub>V</sub>           | small signal voltage gain<br>(REFIN, CLKFDBX) | f=2.6MHz; CAFC0//7=0;<br>Pin < -42dBm; note 2             | -               | 26.0            | -               | dB               |

| SPUROUT                  | Spurious emission                             | f = 2 * f <sub>REF</sub> , note 1                         | -               | -32             | -20             | dBc              |

|                          | Spurious emission                             | non harmonics, note 1                                     | -               | -               | -70             | dBc              |

| $\Delta f_{VCC,REF}$     | pushing                                       | SYNVCC: 2.6V -> 3.3V                                      | -               | -               | 1               | ppm              |

| Coarse AF                |                                               | 1                                                         | -1              |                 |                 | •                |

| C <sub>CAFC,LO</sub>     | CLKFDBX output<br>capacitance LO              | CAFC0//7=0                                                | 17              | 19              | 21              | pF               |

| C <sub>CAFC,HI</sub>     | CLKFDBX output<br>capacitance HI              | CAFC0//7=1                                                | 32              | 38              | 44              | pF               |

| C <sub>CAFC,LSB</sub>    | LSB for coarse AFC capacitor                  | CAFC1//7 =0<br>CAFC0 = 0 <-> 1                            | 51              | 70              | 86              | fF               |

| Pin CAFCS                | SUP                                           |                                                           | •               |                 |                 |                  |

| ICAFCSUP                 | leakage current                               | V <sub>CCSYN</sub> =0V; V <sub>CAFCSUP</sub> =2.3V        | -               | -               | 100             | nA               |

| V <sub>store,CAFC</sub>  | CAFCSUP storage voltage                       | CAFC bits remain stored                                   | 0.6             | -               | -               | V                |