# Fast Settling, High Current Wideband Op Amps

61(6)203

## **APPLICATIONS:**

- coaxial line driving

- · DAC current to voltage amplifier

- · flash A to D driving

- baseband and video communications

- radar and IF processors

#### **DESCRIPTION:**

The CLC203 is a wideband, high-current operational amplifier which features a unique combination of high power and high precision. The amplifier's output current of 200mA and a full-power bandwidth of 60MHz (20V<sub>pp</sub>, 100 $\Omega$ ) ensure a quick design solution for the most demanding loads and signals. The solid 15ns settling time (to 0.2%) is reinforced by the CLC203's excellent DC performance; typically, the input offset voltage is only 0.5mV and is guaranteed to be less than 1mV at +25°C. The input offset voltage drift is typically only  $5\mu V/^{\circ}C$ .

The CLC203 is well suited to a wide range of applications. Specifically, the wide bandwidth, fast settling, linear phase, and very low harmonic distortion provide the designer with the signal fidelity needed in applications such as driving flash A to Ds or coaxial lines. The 60MHz full-power bandwidth and 200mA output current of the CLC203 eliminate the need for power buffers in most applications. Engineers desiring to improve the DC performance or settling precision of systems using the original CLC103 may replace it with a CLC203—in most cases with no design changes (they are pin compatible, however the CLC203 does not have a bias control pin).

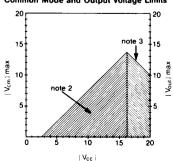

The dynamic performance of the CLC203 is based on Comlinear's proprietary op amp topology. This new design provides performance far beyond that available from conventional op amp designs; for example, the —3dB bandwidth remains nearly constant over a wide range of gains. (See the table below.) And since the amplifier is inherently stable, the user is saved the trouble and expense of designing external compensation networks. The result is shorter design time and the ability to accommodate design changes (in gain, for example) without loss of performance or a redesign of compensation circuits.

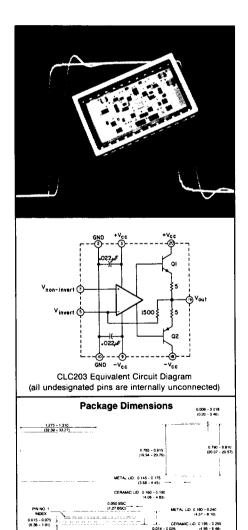

The CLC203 is constructed using thin film resistor/bipolar transistor technology. The CLC203AI is specified over a temperature range of -25°C to +85°C, while the CLC203AM is specified over a range of -55°C to +125°C and is screened to Comlinear's M Standard for high reliability applications. Both devices are packaged in 24-pin ceramic DIPs.

## **Typical Performance**

|                                | gain setting |          |          |          |          |          |           |

|--------------------------------|--------------|----------|----------|----------|----------|----------|-----------|

| parameter                      | +4           | +20      | +50      | -4       | -20      | -50      | units     |

| -3dB bandwidth rise time (20V) | 250<br>4     | 170<br>4 | 120<br>4 | 195<br>4 | 165<br>4 | 120<br>4 | MHz<br>ns |

| slew rate                      | 6            | 6        | 6        | 6        | 6        | 6        | V/ns      |

| settling time (0.2%)           | 15           | 15       | 18       | 15       | 15       | 18       | ns        |

## **FEATURES:**

- 60MHz full-power bandwidth (20V<sub>pp</sub>, 100Ω)

- 200mA output current

- 0.2% settling in 15ns

- 0.5mV input offset voltage, 5μV/°C drift

- 4ns rise and fall times (20V)

Comlinear Corporation • 4800 Wheaton Drive, Fort Collins, CO 80525 • (303) 226-0500 • FAX (303) 226-0564 WWW.DataSheet 4U.com

| PARAMETERS CONDITIONS                                                                                                                                                                                                                         |                                                                                            | TYP                                              | MAX & MIN RATINGS <sup>1</sup>                                 |                                                                |                                                                | UNITS                                              | SYMBOL                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------|

| Ambient Temperature                                                                                                                                                                                                                           | CLC203AM                                                                                   | +25°C                                            | −55°C                                                          | +25℃                                                           | +125℃                                                          |                                                    |                                                                  |

| Ambient Temperature                                                                                                                                                                                                                           | CLC203AI                                                                                   | +25°C                                            | −25°C                                                          | +25°C                                                          | + 85°C                                                         |                                                    | -                                                                |

| FREQUENCY DOMAIN RES                                                                                                                                                                                                                          | PONSE                                                                                      |                                                  |                                                                |                                                                |                                                                |                                                    |                                                                  |

| *-3dB bandwidth                                                                                                                                                                                                                               | $V_{out} < 4V_{pp}$<br>$V_{out} = 20V_{pp}$                                                | 160<br>60                                        | >140<br>>50                                                    | >140<br>>50                                                    | >110<br>>40                                                    | MHz<br>MHz                                         | SSBW<br>FPBW                                                     |

| gain flatness at  * peaking  * peaking  * rolloff                                                                                                                                                                                             | Vout = 20V <sub>pp</sub><br>Vout < 4V <sub>pp</sub><br>0.1 to 40MHz<br>> 40MHz<br>at 75MHz | 0.1<br>0.2<br>—                                  | <0.7<br><1.5<br><0.4                                           | <0.4<br><0.6<br><0.6                                           | <0.3<br><0.6<br><1.0                                           | dB<br>dB<br>dB                                     | GFPL<br>GFPH<br>GFR                                              |

| group delay<br>linear phase deviation<br>reverse isolation                                                                                                                                                                                    | to 75MHz<br>to 75MHz<br>to 150MHz                                                          | 3.3±0.3<br>1                                     | -<br><3.5                                                      | <2.5                                                           | ~2.5                                                           | ns                                                 | GD<br>LPD                                                        |

| non-inverting inverting                                                                                                                                                                                                                       |                                                                                            | 55<br>48                                         | >45<br>>40                                                     | >45<br>>40                                                     | >45<br>>40                                                     | dB<br>dB                                           | RINI<br>RII                                                      |

| TIME DOMAIN RESPONSE rise and fall time settling time to 0.2% overshoot slew rate (overdriven input) overload recovery                                                                                                                        | 5V step<br>20V step<br>10V step<br>5V step                                                 | 2.5<br>4.0<br>15<br>7<br>6                       | <2.9<br><5.0<br><25<br><20<br>>5                               | <2.9<br><5.0<br><20<br><15<br>>5                               | <3.3<br><5.0<br><25<br><15<br>>5                               | ns<br>ns<br>ns<br>%<br>V/ns                        | TRS<br>TRL<br>TSP<br>OS<br>SR                                    |

| <50ns pulse, 200% overdi                                                                                                                                                                                                                      | rive                                                                                       | 30                                               | _                                                              |                                                                | _                                                              | ns                                                 | OR                                                               |

| DISTORTION AND NOISE RE *2nd harmonic distortion *3rd harmonic distortion equivalent noise input                                                                                                                                              | E <b>SPONSE</b><br>2V <sub>pp</sub> , 20MHz<br>2V <sub>pp</sub> , 20MHz                    | -55<br>-55                                       | <-45<br><-45                                                   | <-45<br><-45                                                   | <-45<br><-45                                                   | dBc<br>dBc                                         | HD2<br>HD3                                                       |

| noise floor<br>integrated noise<br>noise floor<br>integrated noise                                                                                                                                                                            | >100kHz<br>1kHz to 100MHz<br>>5MHz<br>5MHz to 100MHz                                       | -158<br>28<br>-158<br>28                         | <-152<br><56<br><-152<br><56                                   | <-152<br><56<br><-152<br><56                                   | <-152<br><56<br><-152<br><56                                   | dBm(1Hz)<br>μV<br>dBm(1Hz)<br>μV                   | SNF<br>INV<br>SNF<br>INV                                         |

| **static DC PERFORMANCE *input offset voltage average temperature coeff *input bias current average temperature coeff *input bias current average temperature coeff *power supply rejection ratio common mode rejection ratio *supply current | icient<br>non-inverting<br>icient<br>inverting<br>icient                                   | 0.5<br>5<br>5<br>50<br>5<br>50<br>60<br>46<br>30 | <2.2<br><15<br><36<br><125<br><26<br><200<br>>45<br>>40<br><36 | <1.5<br><15<br><20<br><125<br><15<br><200<br>>45<br>>40<br><34 | <2.5<br><15<br><20<br><125<br><30<br><200<br>>45<br>>40<br><36 | mV<br>μV°C<br>μΑ<br>nA°C<br>μΑ°C<br>dB<br>dB<br>mA | VIO<br>DVIO<br>IBN<br>DIBN<br>IBI<br>DIBI<br>PSRR<br>CMRR<br>ICC |

| MISCELLANEOUS PERFORM non-inverting input                                                                                                                                                                                                     | MANCE<br>resistance<br>capacitance                                                         | 250<br>2.4                                       | >100<br><3                                                     | >100<br><3                                                     | >100<br><3                                                     | kΩ<br>pF                                           | RIN<br>CIN                                                       |

| output impedance                                                                                                                                                                                                                              | at DC<br>at 75MHz                                                                          | 2,45                                             | <0.1<br>—                                                      | <0.1<br>—                                                      | <0.1<br>—                                                      | $\Omega$<br>$\Omega$ , nH                          | RO<br>ZO                                                         |

| output voltage range                                                                                                                                                                                                                          | no load                                                                                    | -                                                | >±11                                                           | >±11                                                           | >±11                                                           | V                                                  | VO                                                               |

and polydistable proci

storage temperature -65°C to +150°C

lead temperature (soldering 10s) +300°C

\*note 1: Parameters preceded by an \* are the final electrical test parameters and are 100% tested. AM units are tested at -55°C, +25°C, and +125°C. All units are tested only at +25°C although their performance is guaranteed at -25°C and +85°C as indicated above.

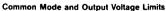

**note 2:** This rating protects against damage to the input stage caused by saturation of either the input or output stages. Under transient conditions not exceeding 1µs (duty cycle not exceeding 10%), maximum input voltage may be as large as twice the maximum.  $V_{cm}$  should never exceed  $V_{cc}$ : ( $V_{cm}$  is the voltage at the non-inverting input, pin 7.)

3 - 21

Frequency (Hz)

Figure 1: recommended non-inverting gain circuit

Figure 2: recommended inverting circuit

Test fixture layout artwork is available upon request.

## **CLC203 Operation**

The CLC203 is based on Comlinear's proprietary op amp topology, a unique design which uses current feedback instead of the usual voltage feedback. This design provides dynamic performance far beyond that previously available, yet it is used basically the same as the familiar voltage-feedback op amp (see the gain equations above). A complete discussion of current feedback is given in application note AN300-1.

# Increasing Bandwidth at High Gains

At high gains ( $|A_v| \ge 50$ ) the bandwidth of the CLC203 may be increased by lowering the value of feedback resistance. This is done by connecting an external resistor in parallel with the internal  $1500\Omega$  feedback resistor. The table below shows the recommended external resistor values for different gain settings.

## Increasing Bandwidth at High Gains

| A   | external resistor | 3dB bandwidth |

|-----|-------------------|---------------|

| 50  | 3kΩ               | 140MHz        |

| 100 | $750\Omega$       | 110MHz        |

### **Lavout Considerations**

To obtain optimum performance from any circuit operating at high frequencies, good PC layout is essential. Fortunately, the stable, well-behaved response of the CLC203 makes operation at high frequencies less sensitive to layout than is the case with other wideband op amps, even though the CLC203 has a much wider bandwidth.

In general, a good layout is one which minimizes the unwanted coupling of a signal between nodes in a circuit. A continuous ground plane from the signal input to output on the circuit side of the board is helpful. Traces should be kept short to minimize inductance. If long traces are needed, use microstrip transmission mes which are terminated in their characteristic impedance. At some high-impedance nodes, or in sensitive areas such as near pin 5 of the CLC203, stray capacitance should be kept small by keeping nodes small and removing ground plane directly around the node.

The  $\pm V_{cc}$  connections to the CLC203 are internally bypassed to ground with  $0.022\mu F$  capacitors to provide good high-frequency decoupling. It is recommended that  $1\mu F$  or larger tantalum capacitors be provided for

low-frequency decoupling. The  $0.01\mu F$  capacitors shown at pins 18 and 20 in figures 1 and 2 should be kept within 0.1" of those pins. A wide strip of ground plane should be provided for a signal return path between the load-resistor ground and these capacitors.

Since the layout of the PC board forms such an important part of the circuit, much time can be saved if prototype amplifier boards are tested early in the design stage. Encased/connectorized amplifiers are available from Comlinear.

# **Distortion and Noise**

The graphs of intercept point versus frequency on the preceding page make it easy to predict the distortion at any frequency, given the output voltage of the CLC203. First, convert the output voltage  $(V_{\rm O})$  to  $V_{\rm rms} = (V_{\rm pp}/2\sqrt{2})$  and then to  $P = (10log_{10}(20V_{\rm rms}^2))$  to get the output power in dBm. At the frequency of interest, its 2nd harmonic will be  $S_2 = (I_2 - P)dB$  below the level of P. Its third harmonic will be  $S_3 = 2(I_3 - P)dB$  below the level of P, as will the two-tone third order intermodulation products. These approximations are useful for  $P\!<\!-1dB$  compression levels.

Approximate noise figure can be determined for the CLC203 using the Equivalent Input Noise graph on the preceding page. The following equation can be used to determine noise figure (F) in dB.

$$F = 10log \left[ 1 + \frac{v_n^2 + \frac{i_n^2 R_F^2}{A_v^2}}{4kTR_s \Delta t} \right]$$

where  $v_n$  is the rms noise voltage and  $i_n$  is the rms noise current at the inverting node. Beyond the breakpoint of the curves (i.e., where they are flat), broadband noise figure equals spot noise, so  $\Delta f$  should equal one (1) and  $v_n$  and  $i_n$  should be read directly off the graph. Below the breakpoint, the noise must be integrated and  $\Delta f$  set to the appropriate bandwidth.

## **Application Notes and Assistance**

Application notes that address topics such as data conversion, fiber optics, and general high-frequency circuit design are available from Comlinear or your Comlinear sales engineer.

Comlinear maintains a staff of highly-qualified applications engineers to provide technical and design assistance.

www.DataSheet4U.com