- 900 MHz Frequency Hopping Spread Spectrum Transceiver

- Point-to-point, Point-to-multipoint, Peer-to-peer and

- Store & Forward Capabilities

- Transmitter Power Configurable to 40 or 158 mW

- Built-in 0 dBi Chip Antenna

- 100 kbps RF Data Rate

- 128-Bit AES Encryption

- Separate Serial Port for Diagnostics

- Analog and Digital I/O for Sensor Applications

- FCC and Canadian IC Certified for Unlicensed Operation

The DNT90CA/PA FHSS transceiver modules provides a low-cost, versatile solution for wireless data communications in the 900 MHz ISM band. The DNT90CA/PA RF output power can be set at 40 or 158 mW. The DNT90CA/PA receiver input is protected by low-loss SAW filter, providing an excellent combination of receiver sensitivity and out-of-band interference rejection. The DNT90CA/PA modules include analog, digital and serial I/O, providing the flexibility to serve applications ranging from cable replacements to sensor networks. The built-in chip antenna makes these modules very easy to integrate.

#### DNT90CA/PA Absolute Maximum Ratings

| Rating                                  | Value        | Units |

|-----------------------------------------|--------------|-------|

| Power Supply Input                      | -0.5 to +6.5 | V     |

| All Input/Output Pins                   | -0.5 to +3.3 | V     |

| Non-Operating Ambient Temperature Range | -40 to +85   | °C    |

# DNT90CA DNT90PA

Low Cost 900 MHz FHSS Transceiver Module with I/O

#### DNT90CA/PA Electrical Characteristics

| Characteristic                              |                                      | Notes | Minimum     | Typical           | Maximum | Units |

|---------------------------------------------|--------------------------------------|-------|-------------|-------------------|---------|-------|

| Operating Frequency Range                   |                                      |       | 902.76      |                   | 927.24  | MHz   |

| Hop Duration                                |                                      | 1     | 8           |                   | 100     | ms    |

| Number of RF Channels                       | Number of RF Channels 1 25, 26 or 52 |       |             |                   |         |       |

| Modulation                                  |                                      |       |             | FSK               |         |       |

| RF Data Transmission Rate                   |                                      |       |             | 100               |         | kbps  |

| Receiver Sensitivity @ 10 <sup>-5</sup> BER |                                      |       |             | -100              |         | dBm   |

| Transmitter RF Output Power                 |                                      | 1     |             | 40 or 158 mW      |         | mW    |

| Optimum Antenna Impedance                   |                                      |       |             | 50                |         | Ω     |

| Antenna                                     |                                      |       | 0 dBi l     | Dielectric Chip A | ntenna  |       |

| System Topologies                           |                                      |       |             | Point, Point-to-N |         |       |

|                                             |                                      |       | Peer-to-l   |                   |         |       |

| Access Scheme                               |                                      |       | Ad Hoc TDMA |                   |         |       |

#### **DNT90CA/PA Electrical Characteristics**

| Characteristic                                    | Sym                         | Notes | Minimum          | Typical                                 | Maximum | Units             |

|---------------------------------------------------|-----------------------------|-------|------------------|-----------------------------------------|---------|-------------------|

| ADC Input Range                                   |                             |       | 0                |                                         | 2.7     | V                 |

| ADC Input Resolution                              |                             |       |                  |                                         | 12      | bits              |

| ADC Sample Rate                                   |                             |       |                  | 100                                     |         | Hz                |

| Signal Source Impedance for ADC Reading           |                             |       |                  |                                         | 10      | KΩ                |

| ADC External Reference Voltage Range              |                             |       | 1.0              |                                         | 2.7     | V                 |

| DAC Output Range                                  |                             |       | 0                |                                         | 3.3     | V                 |

| DAC Output Resolution                             |                             |       |                  |                                         | 12      | bits              |

| Primary and Diagnostic Serial Port Baud Rates     |                             |       |                  | 4.8, 9.6, 14.4, 19<br>7.6, 115.2, 230.4 |         | kbps              |

| Serial Peripheral Interface Data Rate             |                             |       | 125              |                                         | 500     | kbps              |

| Digital I/O:                                      |                             |       |                  |                                         |         |                   |

| Logic Low Input Level                             |                             |       | -0.5             |                                         | 0.8     | V                 |

| Logic High Input Level                            |                             |       | 2.45             |                                         | 3.3     | V                 |

| Logic Input Internal Pull-up Resistor             |                             |       |                  | 20                                      |         | KΩ                |

| Power Supply Voltage Range                        | V <sub>cc</sub>             |       | +3.3             |                                         | +5.5    | Vdc               |

| Power Supply Voltage Ripple                       | er Supply Voltage Ripple 10 |       |                  |                                         | 10      | mV <sub>P-P</sub> |

| Peak Transmit Mode Current, 158 mW Output         |                             |       |                  |                                         | 170     | mA                |

| Average Operating Receive Current:                |                             |       |                  |                                         |         |                   |

| Base, Continuous Data Stream                      |                             |       |                  | 110                                     |         | mA                |

| Remote, Linked, No Data Transmission              |                             |       |                  | 15                                      |         | mA                |

| Remote, Continuous Data Stream                    |                             |       |                  | 25                                      |         | mA                |

| Sleep Current                                     |                             | 2     |                  | 3                                       | 6       | μA                |

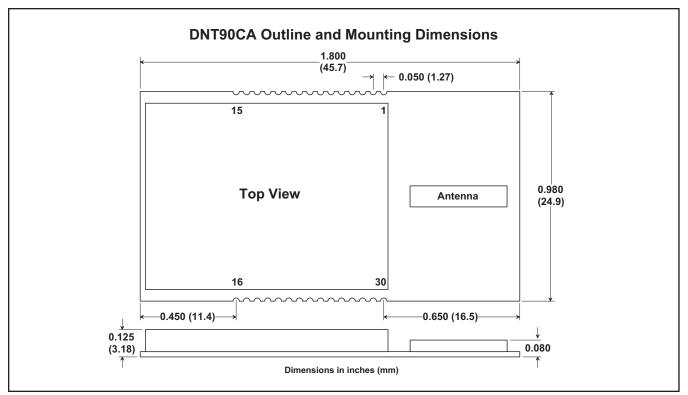

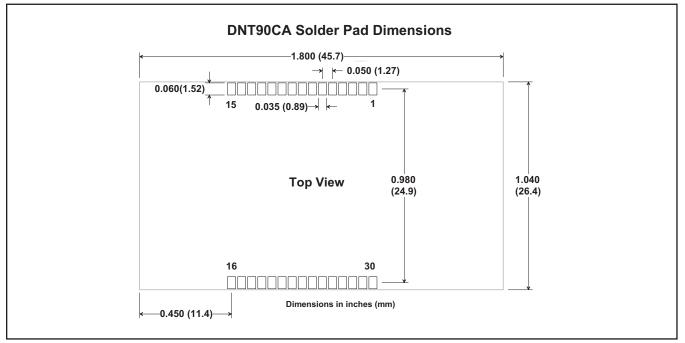

| DNT90CA Mounting                                  |                             |       | Reflow Soldering |                                         |         |                   |

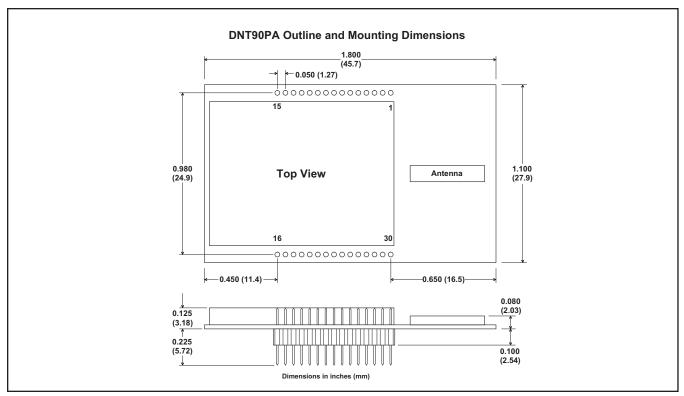

| DNT90PA Mounting                                  |                             |       | Socket           |                                         |         |                   |

| Operating Temperature Range                       |                             |       | -40              |                                         | 85      | °C                |

| Operating Relative Humidity Range, Non-condensing |                             |       | 10               |                                         | 90      | %                 |

Notes:

- 1. The DNT90CA/PA achieves regulatory certification under FHSS rules.

- 2. Maximum sleep current occurs at +85 °C.

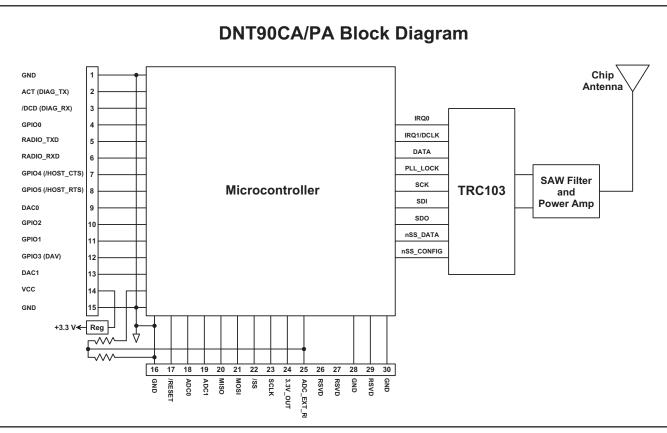

#### **DNT90A Hardware**

The major components of the DNT90A series radios include an RFM TRC103 900 MHz FHSS transceiver, and a low current 8-bit microcontroller. DNT90A radios operate in the 902 to 928 MHz ISM band. There are three selectable hopping patterns providing compatibility with frequency allocations in North America, South America and Australia. DNT90A radios also have two selectable output power levels: +16 dBm (40 mW) and +22 dBm (158 mW).

The DNT90A receiver is protected by a low-loss SAW filter, providing an excellent blend of receiver sensitivity and out-of-band interference rejection. All DNT90A configurations include a built-in chip antenna that simplifies integrating a DNT90A module into an application.

DNT90A radios provide a variety of hardware interfaces. There are two serial ports plus one SPI port. Either the primary serial port or the SPI port can be selected for data communications. The second serial port is dedicated to diagnostics. The primary and diagnostic serial ports support most standard baud rates up to 250 kbps. The SPI port supports data rates up to 500 kbps. DNT90A radios also include three ADC inputs, two DAC outputs, and six general-purpose digital I/O ports. Four of the digital I/O ports support an optional interrupt-from-sleep mode when configured as inputs. DNT90A radios are available in two mounting configurations. The DNT90CA is designed for solder reflow mounting. The DNT90PA is designed for plug-in connector mounting.

### **DNT90A Firmware**

DNT90A firmware operates using hybrid Ad Hoc TDMA channel access optimized for periodic burst transmissions. DNT90A firmware operates "out of the box" using point-topoint transparent serial mode, with point-to-multipoint, peer-to-peer and store & forward system topologies also supported.

DNT90A firmware provides the user with a rich set of configuration options including a choice of hopping patterns, hopping dwell times, serial and/or SPI data port operation, serial and SPI data rate selection, RF output power selection, plus configurable analog and digital I/O lines. Data integrity is protected by 24-bit error detection, with optional ACK and automatic transmission retries or redundant transmissions. 128-bit AES encryption provides a high level of data security for sensitive applications. Sensor networks can take advantage of timer or event-based data reporting and remote node sleep cycling for extended battery life.

## DNT90CA/PA I/O Descriptions

| Pin | Name                 | I/O        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-----|----------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | GND                  | -          | Power supply and signal ground. Connect to the host circuit board ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 2   | ACT<br>(DIAG_TX)     | 0<br>(0)   | This pin's default configuration is data activity output. On a base, this signal blinks when a valid packet is received. On a remote, this signal blinks when a packet is transmitted. On a router, this signal blinks when a valid upstream packet is received or a downstream packet is transmitted. Alternate pin function is the diagnostic serial port output.                                                                                                                                                                                                                                                                                                                             |  |

| 3   | /DCD<br>(DIAG_RX)    | 0<br>(I)   | This pin's default configuration is data carrier detect output. On a base, this signal is asserted when any valid packet is received, and is cleared if no packets are heard for the configured router/remote registration time-out interval. On a router or remote, this signal is asserted when the radio obtains hopping pattern synchronization, and remains asserted until no beacons are heard for 50 hops. Alternate pin function is the diagnostic serial port input.                                                                                                                                                                                                                   |  |

| 4   | GPIO0                | I/O        | Configurable digital I/O port 0. When configured as an input, an internal pull-up resistor can be selected and direct interrupt from sleep can be invoked. When configured as an output, the power-on state is configurable. In sleep mode the pin direction, input pull-up selection or output state are also separately configurable.                                                                                                                                                                                                                                                                                                                                                         |  |

| 5   | RADIO_TXD            | 0          | Serial data output from the radio.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 6   | RADIO_RXD            | Ι          | Serial data input to the radio.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 7   | GPOI4<br>(/HOST_CTS) | I/O<br>(O) | Default pin function is GPIO4 with the same configuration options as GPIO2. Alternate pin function is UART/SPI flow control output. The module sets this line low when it is ready to accept data from the host on the RADIO_RXD or MOSI input. When the line goes high, the host must stop sending data.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 8   | GPOI5<br>(/HOST_RTS) | I/O<br>(I) | Default pin function is GPIO5 with the same configuration options as GPIO2. Alternate pin function is UART/SPI flow control input. The host sets this line low to allow data to flow from the module on the RADIO_TXD pin. When the host sets this line high, the module will stop sending data to the host.                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 9   | DAC0                 | 0          | 12-bit DAC 0 output. Full scale output can be referenced to the voltage at pin 25 or the 3.3 V regulated module bus voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 10  | GPIO2                | I/O        | Configurable digital I/O port 2. Same configuration options as GPIO0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 11  | GPIO1                | I/O        | Configurable digital I/O port 1. Same configuration options as GPIO0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 12  | GPIO3<br>(DAV)       | I/O<br>(O) | Default pin function is GPIO3 with the same configuration options as GPIO0. When SPI slave mode oper-<br>ation is enabled, a logic high on this pin indicates when data is available to be clocked out by the SPI<br>master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 13  | DAC1                 | 0          | 12-bit DAC 1 output. Same specifications and configuration options as DAC0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 14  | VCC                  | I          | Power supply input, +3.3 to +5.5 Vdc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 15  | GND                  | -          | Power supply and signal ground. Connect to the host circuit board ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 16  | GND                  | -          | Power supply and signal ground. Connect to the host circuit board ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 17  | /RESET               | Ι          | Active low module hardware reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| 18  | ADC0                 | I          | ADC input 0. This pin is a direct ADC input when the ADC is operating in single-ended mode, or the differ-<br>ential negative input for positive inputs applied to ADC1 or ADC2 when the ADC is operating in differential<br>mode. Full-scale reading can be referenced to Pin 25 for ratiometric measurements. For absolute mea-<br>surements, the ADC can use the regulated supply voltage divided by 1.6 (about 2.06 V), or an external<br>voltage applied to Pin 25. In single-ended mode, ADC measurements are 11-bit unsigned values with full<br>scale nominally 2.7 V when referenced to a 2.7 V input on Pin 27. In differential mode, ADC measure-<br>ments are 12-bit signed values. |  |

| 19  | ADC1                 | I          | ADC input 1. Direct input when the ADC is operating in single-ended mode, positive differential input rela-<br>tive to ADC0 when the ADC is operating in differential mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 20  | MISO                 | I/O        | This pin is the SPI master mode input or slave mode output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 21  | MOSI                 | I/O        | This pin is the SPI master mode output or slave mode input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 22  | /SS                  | I/O        | SPI active low slave select. This pin is an output when the module is operating as a master, and an input when it is operating as a slave.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Pin | Name            | I/O | Description                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23  | SCLK            | I/O | SPI clock signal. This pin is an output when operating as a master, and an input when operating as a slave.                                                                                                                                                                                                                                                             |

| 24  | ADC2            | I   | ADC input 2. Direct input when the ADC is operating in single-ended mode, positive differential input rela-<br>tive to ADC0 when the ADC is operating in differential mode.                                                                                                                                                                                             |

| 25  | ADC_EXT_<br>REF | I/O | ADC external reference voltage pin. The voltage at this pin can be used by the ADCs as a reference for ratiometric measurements. With no external voltage or load applied, this pin presents a nominal 2.7 V output through a 2.126 K source resistance. A low impedance external reference voltage in the range of 1 to 2.7 V may be applied to this pin as an option. |

| 26  | RSVD            | -   | Reserved pin. Leave unconnected.                                                                                                                                                                                                                                                                                                                                        |

| 27  | RSVD            | -   | Reserved pin. Leave unconnected.                                                                                                                                                                                                                                                                                                                                        |

| 28  | GND             | -   | Connect to the host circuit board ground plane.                                                                                                                                                                                                                                                                                                                         |

| 29  | RSVD            | -   | Reserved pin. Leave unconnected.                                                                                                                                                                                                                                                                                                                                        |

| 30  | GND             | -   | Connect to the host circuit board ground plane.                                                                                                                                                                                                                                                                                                                         |

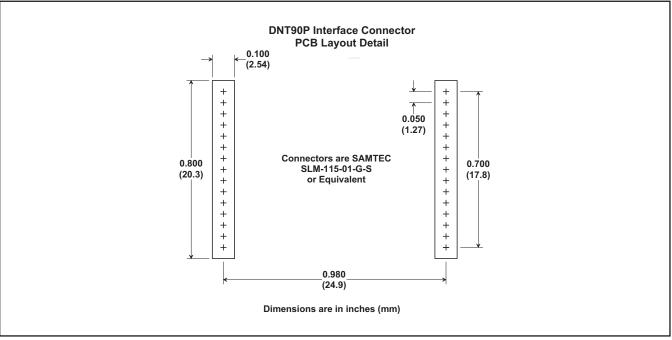

Figure 2

Figure 3

Figure 5

Note: Specifications subject to change without notice.

Part # M-0090-0000, Rev B