# **Power Factor Correction Controllers**

## ISL6730A, ISL6730B, ISL6730C, ISL6730D

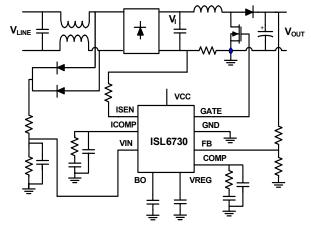

The ISL6730A, ISL6730B, ISL6730C, ISL6730D are active power factor correction (PFC) controller ICs that use a boost topology. (ISL6730B, ISL6730C, ISL6730D are Coming Soon.) The controllers are suitable for AC/DC power systems, up to 2kW and over the universal line input.

The ISL6730A, ISL6730B, ISL6730C, ISL6730D are operated in continuous current mode. Accurate input current shaping is achieved with a current error amplifier. A patent pending breakthrough negative capacitance technology minimizes zero crossing distortion and reduces the magnetic components size. The small external components result in a low cost design without sacrificing performance.

The internally clamped 12.5V gate driver delivers 1.5A peak current to the external power MOSFET. The ISL6730A, ISL6730B, ISL6730C, ISL6730D provide a highly reliable system that is fully protected. Protection features include cycle-by-cycle overcurrent, over power limit, over-temperature, input brownout, output overvoltage and undervoltage protection.

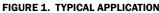

The ISL6730A, ISL6730B provide excellent power efficiency and transitions into a power saving skip mode during light load conditions, thus improving efficiency automatically. The ISL6730A, ISL6730B, ISL6730C, ISL6730D can be shut down by pulling the FB pin below 0.5V or grounding the BO pin. The ISL6730C, ISL6730D have no skip mode.

Two switching frequency options are provided. The ISL6730B, ISL6730D switch at 62kHz, and the ISL6730A, ISL6730C switch at 124kHz.

#### **Features**

- · Reduce component size requirements

- Enables smaller, thinner AC/DC adapters

- Choke and cap size can be reduced by 66%

- Lower cost of materials

- · Excellent power factor over line and load regulation

- Internal current compensation

- CCM Mode with Patent pending IP for smaller EMI filter

- · Better light load efficiency

- Automatic pulse skipping

- Programmable or automatic shutdown

- · High reliable design

- Cycle-by-cycle current limit

- Input average power limit

- OVP and OTP protection

- Input brownout protection

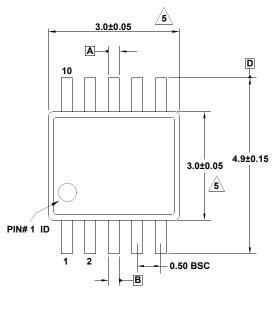

- Small 10 Ld MSOP package

### **Applications**

- Desktop computer AC/DC adaptor

- Laptop computer AC/DC adaptor

- TV AC/DC power supply

- · AC/DC brick converters

**TABLE 1. KEY DIFFERENCES IN FAMILY OF ISL6730**

| VERSION             | ISL6730A  | ISL6730B  | ISL6730C | ISL6730D |

|---------------------|-----------|-----------|----------|----------|

| Switching Frequency | 124kHz    | 62kHz     | 124kHz   | 62kHz    |

| Skip Mode           | Yes-Fixed | Yes-Fixed | No       | No       |

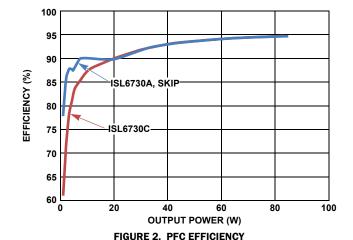

# **Pin Configuration**

ISL6730A, ISL6730B, ISL6730C, ISL6730D (10 LD MSOP) TOP VIEW

# **Pin Descriptions**

| PIN# | 1/0 | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | -   | GND    | Ground pin. All voltage levels refer to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2    | I   | ISEN   | Current sense pin. The current through this pin is proportional to the inductor current.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3    | I/O | ICOMP  | Current error amplifier output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4    | I   | VIN    | Input voltage sense. This pin provides the reference voltage to shape inductor current. Connect this pin to a resistor divider from the rectified input voltage. The resistor divider ratio is used to adjust the phase lag between input voltage and the input current. The phase lag is required to compensate the phase lead generated by the EMI filter.                                                                                                                                                                     |

| 5    | I/0 | во     | This pin should be decoupled to GND with a minimum $0.1\mu F$ ceramic capacitor. The BO pin is a voltage follower, which will follow the DC voltage of the VIN pin. The BO pin is internally tied to GND through a resistor $R_{IS}$ . The decoupling capacitor provides ripple filtering. When the voltage at the BO pin $(V_{BO})$ drops below brownout voltage threshold, the controller enters shutdown mode and the gate drive is disabled. The BO pin will be disabled when the FB pin drops below the enabling threshold. |

| 6    | I/O | COMP   | Output of the error amplifier. The voltage of the COMP pin sets the input power. During start-up, a small charge current will slowly ramp up the voltage of the COMP pin.                                                                                                                                                                                                                                                                                                                                                        |

| 7    | I   | FB     | Voltage feed back pin. Connect this pin to a resistor divider from the output. The resistor divider sets the output voltage. When the FB pin voltage exceeds 104% of the reference voltage, overvoltage-protection is triggered and gate drive is disabled. When the FB pin is below 10%, the device is put into shutdown mode. There is an internal pull-down current source for open loop protection.                                                                                                                          |

| 8    | -   | VREG   | Output of internal regulator. The voltage having a ±2% tolerance over line, load and operating temperature. Bypass to GND with a 47nF low ESR capacitor. VREG can source up to 10mA. This pin is not recommended for usage other than bypass.                                                                                                                                                                                                                                                                                    |

| 9    | I   | vcc    | Power supply pin. The VCC pin should be decoupled to GND with a minimum 0.1µF ceramic capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10   | 0   | GATE   | Push-pull gate drive for the external MOSFET. Output voltage is clamped at 12.5V. This pin provides typically 2A sink and 1.5A source capability.                                                                                                                                                                                                                                                                                                                                                                                |

# **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | TEMP.<br>RANGE (°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|--------------------------------|-----------------|---------------------|----------------------|----------------|

| ISL6730AFUZ                    | 6730A           | -40 to +125         | 10 Ld MSOP           | M10.118        |

| ISL6730BFUZ (Coming Soon)      | 6730B           | -40 to +125         | 10 Ld MSOP           | M10.118        |

| ISL6730CFUZ (Coming Soon)      | 6730C           | -40 to +125         | 10 Ld MSOP           | M10.118        |

| ISL6730DFUZ (Coming Soon)      | 6730D           | -40 to +125         | 10 Ld MSOP           | M10.118        |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL6730A. For more information on MSL please see techbrief TB363.

**EMI CHOKE**

⊸ v<sub>out</sub>

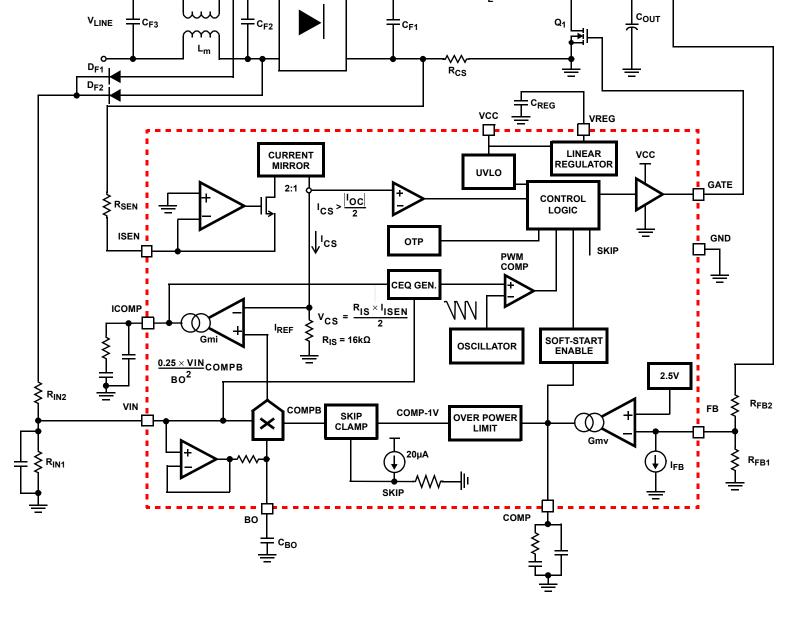

# **Application Schematics**

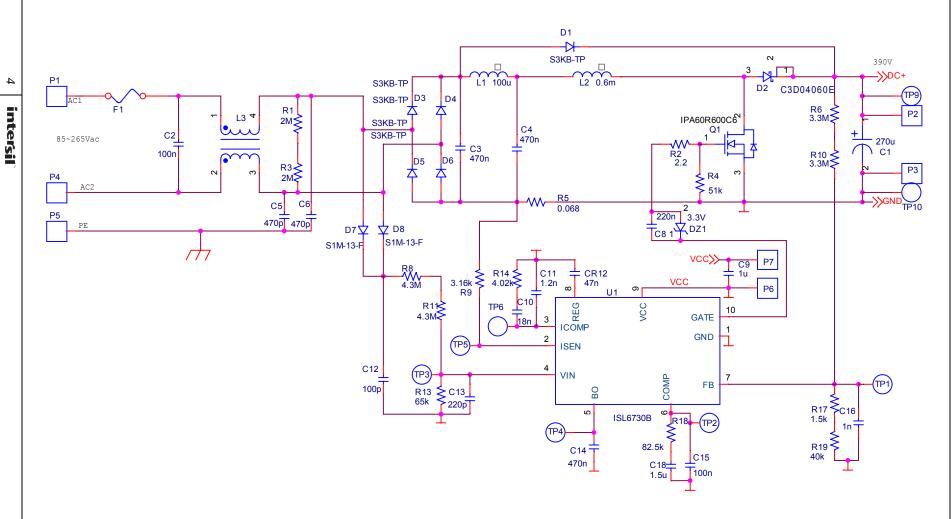

# **Typical 300W Application Schematic**

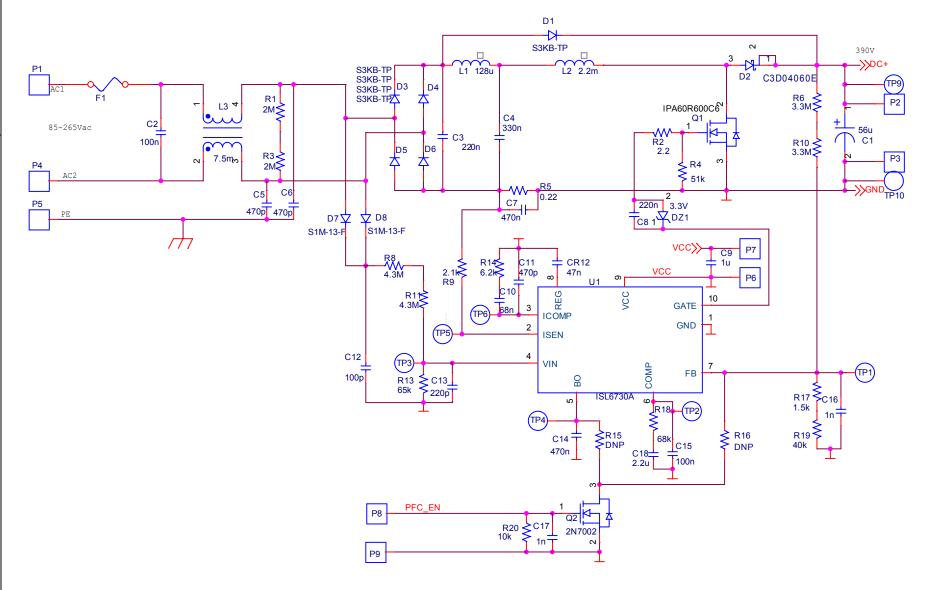

# Application Schematics (Continued)

# **Typical 85W Application Schematic**

$\Omega$

intersil

#### **Absolute Maximum Ratings**

| VCC to GND                                       | 0.3V to +28V  |

|--------------------------------------------------|---------------|

| GATE to GND                                      | 0.3V to +18V  |

| VIN, BO, ISEN, FB and COMP to GND                | 0.3V to +6.3V |

| ESD Rating                                       |               |

| Human Body Model (Tested per JESD22-A114)        | 2.5kV         |

| Machine Model (Tested per JESD22-A115)           | 200V          |

| Charged Device Model (Tested per JESD-C101E      | 1kV           |

| Latch Up (Tested per JESD-78B; Class 2, Level A) | 100mA         |

#### **Thermal Information**

| Thermal Resistance (Typical)              | $\theta_{JA}(^{\circ}C/W)$ | $\theta_{JC}$ (°C/W) |

|-------------------------------------------|----------------------------|----------------------|

| MSOP Package (Notes 4, 5)                 | 137                        | 39                   |

| Maximum Junction Temperature (Plastic Pac | kage)                      | +150°C               |

| Maximum Storage Temperature Range         | 6                          | 5°C to +150°C        |

| Ambient Temperature Range                 | 40                         | 0°C to +125°C        |

| Junction Temperature Range                | 40                         | 0°C to +125°C        |

| Pb-Free Reflow Profile                    |                            | see link below       |

| http://www.intersil.com/pbfree/Pb-FreeRe  | eflow.asp                  |                      |

#### **Recommended Operating Conditions**

| VCC to GND                |    | 15V to + 20V | ۷ |

|---------------------------|----|--------------|---|

| Ambient Temperature Range | 40 | °C to +125°0 | С |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 4. θ<sub>IA</sub> is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 5. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is taken at the package top center.

# **Electrical Specifications** Operating Conditions: V<sub>CC</sub> = 15V, T<sub>A</sub> = +25°C. Boldface limits apply over the operating temperature range, -40°C to +125°C.

| PARAMETER                                   | SYMBOL               | TEST CONDITIONS                                                             | MIN<br>(Note 8) | TYP  | MAX<br>(Note 8) | UNITS |

|---------------------------------------------|----------------------|-----------------------------------------------------------------------------|-----------------|------|-----------------|-------|

| V <sub>CC</sub> SUPPLY CURRENT              |                      |                                                                             | 1               | •    | 1               |       |

| Start Up Current                            | ISTART               | $V_{FB} = 1V$ , $V_{CC} < V_{CC}(ON)$                                       | 73              | 106  | 139             | μΑ    |

| Standby Current                             | I <sub>STDN</sub>    | $V_{FB} = GND, V_{CC} > V_{CC}(ON)$                                         | 179             | 237  | 295             | μΑ    |

| Skip Mode Current                           | ICCSKIP              | V <sub>FB</sub> = 2.5V, COMP = SKIP*0.25 +1V                                | 580             | 690  | 800             | μΑ    |

| Operating Current (Note 6)                  | Icc                  | GATE is floating                                                            | 3.2             | 3.7  | 4.2             | μΑ    |

| VCC UVLO                                    |                      |                                                                             |                 |      |                 |       |

| UVLO Rising Threshold                       | V <sub>CC(ON)</sub>  |                                                                             | 9               | 10   | 11              | V     |

| UVLO Falling Threshold                      | V <sub>CC(OFF)</sub> |                                                                             | 6.7             | 7.5  | 8.3             | V     |

| UVLO Threshold Hysteresis                   | V <sub>CC(HYS)</sub> |                                                                             | -               | 2.5  | -               | V     |

| REGULATOR VOLTAGE VREG                      |                      |                                                                             |                 |      |                 |       |

| Overall Accuracy                            |                      | I <sub>REF</sub> = 0 to -10mA, V <sub>CC</sub> = 15V, Load Capacitor = 47nF | 5.16            | 5.4  | 5.6             | V     |

| Current Limit                               |                      |                                                                             | 30              | 50   | 70              | mA    |

| PWM CONVERTERS                              |                      |                                                                             |                 |      | 1               |       |

| Minimum Duty Cycle, ISL6730A                |                      | f <sub>SW</sub> = 124kHz                                                    | -               | 2.57 | 4.66            | %     |

| Maximum Duty Cycle, ISL6730A                |                      | f <sub>SW</sub> = 124kHz                                                    | 94.8            | 96.5 | -               | %     |

| OSCILLATOR                                  |                      |                                                                             |                 |      |                 |       |

| Free Running Frequency, ISL6730A            |                      | T <sub>A</sub> = -40 °C to +125 °C, V <sub>IN</sub> = 0.6V                  | 98              | 107  | 116             | kHz   |

| Free Running Frequency, ISL6730A            |                      | T <sub>A</sub> = -40 °C to +125 °C, V <sub>IN</sub> = 2.5V                  | 114             | 125  | 136             | kHz   |

| PWM Ramp Amplitude                          | ٧ <sub>m</sub>       |                                                                             | 1.33            | 1.46 | 1.59            | V     |

| GATE DRIVER                                 |                      |                                                                             | -               | •    |                 | •     |

| Gate Drive Pull-Down Resistance             |                      | V <sub>CC</sub> = 15V, I <sub>GATE</sub> = 15mA                             | -               | 2.33 | 4.46            | Ω     |

| Gate Drive Pull-Up Voltage Drop             |                      | V <sub>CC</sub> = 9V, I <sub>GATE</sub> = 15mA                              | 0.15            | 0.3  | 0.45            | V     |

| Gate Drive Max. Sourcing/Sinking<br>Current |                      |                                                                             | -               | 1.5  | -               | Α     |

**Electrical Specifications** Operating Conditions: V<sub>CC</sub> = 15V, T<sub>A</sub> = +25°C. **Boldface limits apply over the operating temperature range,** -40°C to +125°C. (Continued)

| PARAMETER                              | SYMBOL                | TEST CONDITIONS                                                                   | MIN<br>(Note 8) | TYP   | MAX<br>(Note 8) | UNITS         |

|----------------------------------------|-----------------------|-----------------------------------------------------------------------------------|-----------------|-------|-----------------|---------------|

| Rise Time                              |                       | $C_0$ = 2.2nF, $V_{CC}$ = 15V, Gate Voltage Rise Time from 10% to 90% of $V_{GC}$ | -               | 34    | 62              | ns            |

| Fall Time                              |                       | $C_0$ = 2.2nF, $V_{CC}$ = 15V, Gate Voltage Fall Time from 10% to 90% of $V_{GC}$ | -               | 34    | 57              | ns            |

| Gate Clamp Voltage                     | V <sub>GC</sub>       |                                                                                   | 11              | 12    | 13              | V             |

| VOLTAGE REFERENCE                      | 1                     |                                                                                   | I               |       |                 | .1            |

| Reference Voltage                      | VREF                  |                                                                                   | 2.48            | 2.5   | 2.52            | V             |

| Feedback Pin Pull-Down Current         | I <sub>FB</sub>       |                                                                                   | -               | 65    | -               | nA            |

| Rising Threshold to Enable Converter   | FB_EN                 |                                                                                   | 280             | 300   | 320             | mV            |

| Falling Threshold to Disable Converter | FB_DIS                |                                                                                   | 190             | 202   | 214             | mV            |

| Enable Hysteresis                      | FB_Hys                |                                                                                   | -               | 100   | 1               | mV            |

| VOLTAGE ERROR AMPLIFIER                | 1                     |                                                                                   | I               |       |                 | .1            |

| DC Gain                                |                       |                                                                                   | -               | 92    | -               | dB            |

| Error Amp Transconductance             | gmv                   |                                                                                   | 50              | 77    | 104             | μ <b>A</b> /V |

| ISource/Sink                           |                       |                                                                                   | -               | 13    | 1               | μΑ            |

| COMP Offset Voltage                    | V <sub>COMP_OFF</sub> |                                                                                   | 0.95            | 1.01  | 1.07            | V             |

| COMP Soft-Start Enable Voltage         | V <sub>COMP_EN</sub>  |                                                                                   | 0.58            | 0.64  | 0.75            | ٧             |

| INPUT VOLTAGE SENSING                  | I                     |                                                                                   | 1               | •     |                 |               |

| VIN Leakage Current                    |                       |                                                                                   | -               | 9     | -               | nA            |

| MULTIPLIER GAIN                        | l                     |                                                                                   | I.              |       |                 |               |

| GMUL                                   |                       | COMP = 2.5V, V <sub>IN</sub> = 1.0V, BO = 1.0V, I <sub>SEN</sub> = 50µA           | 0.196           | 0.25  | 0.296           | V/V           |

| CURRENT ERROR AMPLIFIER                | <u>I</u>              |                                                                                   | 1.              |       |                 |               |

| Current DC Gain                        | A <sub>iDC</sub>      | $\Delta I_{\text{ICOMP}}/\Delta I_{\text{ISEN}}$                                  | 1.6             | 1.9   | 2.2             | A/A           |

| Error Amp Transconductance             | gmi                   | I <sub>ICOMP</sub> = ±20μA                                                        | 205             | 268   | 331             | μ <b>A</b> /V |

| ICOMP Source/Sink Current (Note 7)     |                       |                                                                                   | -               | 60    | 1               | μΑ            |

| Current Sensing Input Offset           |                       |                                                                                   | -3              | 2     | 7               | mV            |

| LIGHT LOAD EFFICIENCY ENHANCEM         | ENT AND OVE           | RPOWER PROTECTION                                                                 | I               |       |                 | .1            |

| Skip Mode COMP Threshold               | V <sub>SCMT</sub>     |                                                                                   | 1.32            | 1.36  | 1.4             | V             |

| COMP Upper Limit                       | V <sub>CUL</sub>      |                                                                                   | 3.53            | 3.85  | 4.17            | V             |

| COMP Valid Range                       | V <sub>CUL</sub> -1V  |                                                                                   | 2.5             | 2.83  | 3.16            | V             |

| FB Exit Threshold Voltage              | V <sub>FB_EXIT</sub>  | I <sub>ISEN</sub> = 0μA                                                           | 87              | 88    | 89              | %             |

| ISEN Exit Threshold Current            | I <sub>SEN_EXIT</sub> | V <sub>FB</sub> = 2.5V                                                            | -38             | -29   | -20             | μΑ            |

| BROWNOUT DETECTION                     |                       |                                                                                   | •               |       |                 | •             |

| Brownout Rising Threshold              | V <sub>BO_R</sub>     |                                                                                   | 478             | 494   | 510             | mV            |

| Brownout Falling Threshold             | V <sub>BO_F</sub>     |                                                                                   | 387             | 401   | 415             | V             |

| OVERVOLTAGE PROTECTION                 | •                     |                                                                                   | •               |       |                 |               |

| Overvoltage Protection                 | V <sub>OVP</sub>      | Fraction of the set point; ~1µs noise filter                                      | 102.9           | 104.1 | 105.3           | ٧             |

| OVERCURRENT PROTECTION                 |                       |                                                                                   | •               |       |                 | •             |

| Overcurrent Threshold                  | loc                   |                                                                                   | -197            | -177  | -159            | μΑ            |

# **Electrical Specifications** Operating Conditions: V<sub>CC</sub> = 15V, T<sub>A</sub> = +25°C. Boldface limits apply over the operating temperature range, -40°C to +125°C. (Continued)

| PARAMETER                            | SYMBOL | TEST CONDITIONS | MIN<br>(Note 8) | TYP | MAX<br>(Note 8) | UNITS |

|--------------------------------------|--------|-----------------|-----------------|-----|-----------------|-------|

| THERMAL SHUTDOWN                     |        |                 |                 |     |                 |       |

| Shutdown Temperature (Note 7)        |        |                 | -               | 160 | -               | °C    |

| Thermal Shutdown Hysteresis (Note 7) |        |                 | -               | 25  | -               | °C    |

#### NOTES:

- 6. This is the  $V_{CC}$  current consumed when the device is active but not switching. Does not include gate drive current.

- 7. Limits should be considered typical and are not production tested.

- 8. Parameters with MIN and/or MAX limits are 100% tested at  $+25\,^{\circ}$  C, unless otherwise specified.

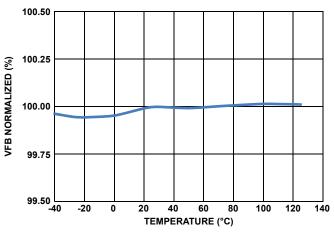

# **Typical Performance Curves**

FIGURE 3. FEEDBACK ACCURACY

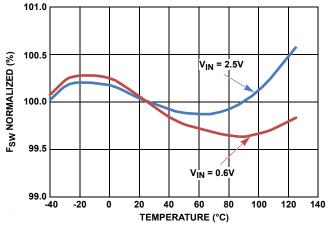

FIGURE 4.  $F_{SW}$  vs TEMPERATURE,  $V_{CC} = 15V$

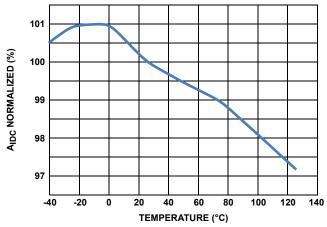

FIGURE 5. A<sub>IDC</sub> vs TEMPERATURE

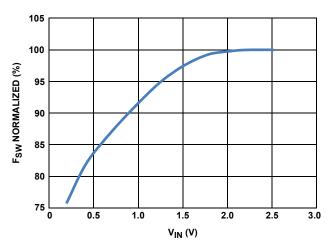

FIGURE 6. F<sub>SW</sub> vs V<sub>IN</sub>, T<sub>A</sub> = +25°C

# Typical Performance Curves (Continued)

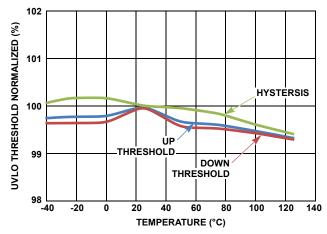

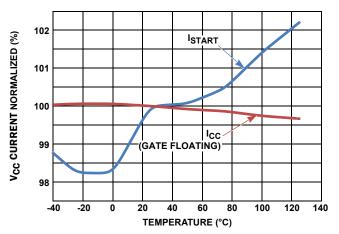

FIGURE 7. UVLO THRESHOLDS vs TEMPERATURE

FIGURE 8. V<sub>CC</sub> SUPPLY CURRENT vs TEMPERATURE

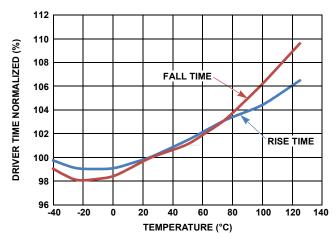

FIGURE 9. GATE DRIVER ABILITY vs TEMPERATURE (LOAD = 2.2nF)

# **Functional Description**

#### **VCC Undervoltage Lockout (UVLO)**

The ISL6730A, ISL6730B, ISL6730C, ISL6730D start automatically once the voltage at VCC exceeds the UVLO threshold.

#### **Shutdown**

When the VFB pin is below 0.2V, the controller is disabled and the PWM output driver is tri-stated. When disabled, the IC power will be reduced. During shutdown, the COMP pin is discharged to GND and the controller is disabled. The Over-Temperature Protection (OTP) is still alive to prevent the controller from starting up in a high temperature ambient condition.

In the event that the FB pin is disconnected from the feedback resistors, the FB pin is pulled to ground by an internal current source I<sub>FB</sub>. When the FB pin voltage drops below 0.2V, the gate driver is disabled. The ISL6730A, ISL6730B, ISL6730C, ISL6730D enters shutdown mode.

#### **Soft-Start**

The COMP pin is released once the soft-start operation begins. A  $13\mu A$  current sources out to the RC network connected from the COMP pin until the FB pin voltage reaches 90% of the reference voltage.

Switching is inhibited when the COMP pin voltage is below 1V. When the COMP pin reaches 1V, the current error amplifier and the gate driver are activated and the converter starts switching.

During UVLO, Brownout and Shutdown, the COMP is pulled to the ground.

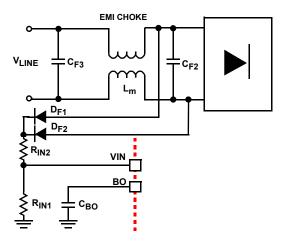

#### **Input Voltage Sensing**

The VIN pin is needed to sense the rectified input voltage. The sensed semi-sinusoidal waveform is needed to shape inductor current, which helps achieves unity power factor. At the same time, the voltage on the VIN pin is used to generate the negative capacitive element at the input. This will cancel the input filter capacitor,  $C_F$ . Canceling the effect of  $C_F$  will increase the displacement power factor and alleviate the zero crossing distortion, which is related to the distortion power factor.

10

FIGURE 10. INPUT VOLTAGE SENSING SCHEMATIC

The BO pin also utilizes the VIN resistor divider for voltage sensing. Set the resistor divider ratio to satisfy the brownout requirement.

First, calculate the resistor divider ratio, K<sub>BO</sub>.

$$K_{BO} = \frac{V_{BORMAX}}{V_{RMSmin} - 2V_F}$$

(EQ. 1)

Where  $V_F$  is the forward voltage drop of the bridge rectifier and the voltage drop of  $D_{F1}$ .  $D_{F2}$ .

Then, select the  $R_{IN2}$  based on the highest reasonable resistance value. Then select the  $R_{IN1}$  based upon the desirable minimum RMS value of the line voltage for the PFC operation.

$$R_{IN1} = \frac{K_{BO}}{1 - K_{BO}} \cdot R_{IN2}$$

(EQ. 2)

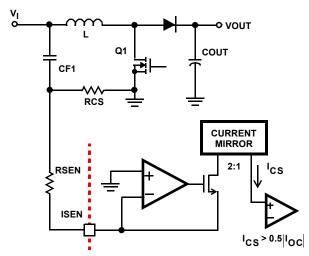

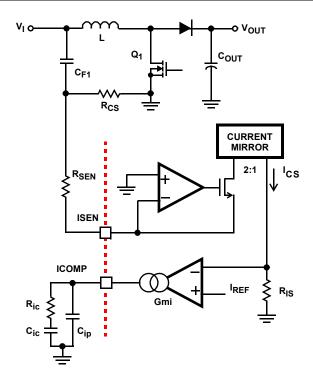

#### **Inductor Current Sensing**

The current sensing of the converter has two purposes. One is to force the inductor current to track the input semi-sinusoidal waveform. The other purpose is for overcurrent protection. Refer to Figure 11 for the current sensing scheme. The sensed current  $I_{CS}$  is in proportion to the inductor current,  $I_L$  as described in Equation 3.

$$I_{CS} = \frac{1}{2} \cdot \frac{R_{CS}}{R_{SFN}} \cdot I_{L}$$

(EQ. 3)

where:

$R_{CS}$  is the current sensing resistor with low value in the return path to the bridge rectifier.

$R_{\mbox{\footnotesize{SEN}}}$  is the current scaling resistor connected between ISEN to the  $R_{\mbox{\footnotesize{CS}}}.$

FIGURE 11. INDUCTOR CURRENT SENSING SCHEME

A high value  $R_{CS}$  renders more accurate current sensing. It is recommended to use the  $R_{CS}$  to render 120mV peak voltage at the maximum line voltage during full load condition.

$$R_{CS} > \frac{120 \text{mV} \cdot \text{V}_{RMSMAX} \cdot \eta}{\sqrt{2} \cdot \text{P}_{Omax}}$$

(EQ. 4)

Where  $\boldsymbol{\eta}$  is the efficiency of the converter at the maximum line input with full load.

Since the  $R_{CS}$  sees the average input current, high value  $R_{CS}$  generates high power dissipation on the  $R_{CS}$ . Use a reasonable  $R_{CS}$  according to the resistor power rating. The worst-case power dissipation occurs at the input low line when input current is at its maximum. Power dissipation by the resistor is:

$$P_{RCS} = (I_{RMSMAX})^2 \cdot R_{CS}$$

(EQ. 5)

where:

$I_{RMSMAX}$  is the maximum input RMS current at the minimum input line voltage,  $V_{RMSmin}. \\$

Select the  $R_{SEN}$  according to the peak current limit requirement. The resistor is sized for an overload current 25% more than the peak inductor peak current.

#### **Negative Input Capacitor Generation**

#### (Patent Pending)

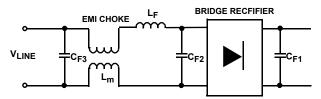

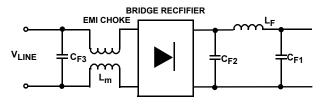

The patent pending negative capacitor generation capability of the ISL6730A, ISL6730B, ISL6730C, ISL6730D allows the capacitor  $C_{F2}$  to be moved from before the bridge rectifier (Figure 12) to after the bridge rectifier (Figure 13). Thus, a smaller lower cost  $C_{F2}$  can be used. The change in topology reduces the size of the EMI filter. Furthermore,  $C_{F1}$  can be increased thus decreasing the size of  $L_F$  (Figure 13).

FIGURE 12. TYPICAL PFC INPUT FILTER CIRCUIT

FIGURE 13. LOW COST PFC INPUT FILTER CIRCUIT

For applications where the output power is above 500W, the negative capacitance helps to improve the power factor dramatically. Please refer to Table 2 for the recommended filtering capacitor to be placed after the bridge rectifier, C<sub>F1</sub>.

TABLE 2.

| C <sub>F1</sub>       | Po < 100W | 100W < Po < 500W | Po > 500W |

|-----------------------|-----------|------------------|-----------|

| Typical<br>C(μF)/100W | 0.68      | 0.33             | 0.22      |

Additional C<sub>F1</sub> may be used to accommodate the use of small boost inductor or to eliminate the differential mode filter inductor as long as the equipment meets the power factor or goal.

The equivalent negative capacitor is a function of the input voltage divider ratio,  $K_{BO}$ , the current sensing gain and current compensation error integration gain.

Adjusting the negative Ceq can be achieved by adjusting the current compensation network.

#### **Frequency Modulation**

The ISL6730A, ISL6730B, ISL6730C, ISL6730D can further reduce EMI filter size by lowering the differential noise power density. The reduction is achieved by switching frequency modulation.

The frequency varies with the VIN pin. The switching frequency reaches the peak value when the VIN pin voltage is 2V as shown in Figure 6. The peak value of ISL6730A/C is 124kHz, and the ISL6730B/D is 62kHz.

#### **Output Voltage Regulation**

The output voltage is sensed through a resistor divider. The middle point of the resistor divider is fed to the FB pin. The resistor divider ratio sets the output voltage. The transconductance error amplifier generates a current in proportion to the difference between the FB pin and the 2.5V internal reference. The PFC is stabilized by the compensation network that is connected from the COMP pin to the ground.

The voltage of the COMP sets the input average power by determining the amplitude of the current reference. To keep the

harmonic distortion minimum, it is desirable to set the control bandwidth much lower than twice of the line frequency. The recommended voltage loop bandwidth is 10Hz.

During start-up, the compensation capacitors and the charging current from the error amplifier sets the input power increase rate. Thus, soft-start is achieved.

The COMP is discharged during shutdown and fault conditions.

#### **Light Load Efficiency Enhancement**

For PC, adaptor and TV applications, it is desirable to achieve high efficiency at light load conditions and low standby current. The ISL6730A, ISL6730B, ISL6730C, ISL6730D can enter light load efficiency mode automatically.

The voltage error amplifier output, COMP, is an indicator of the average input power level. The controller compares the V(COMP) and V(SKIP). If V(COMP)-1V is less than V(SKIP)\*0.25, the PFC controller stops gate switching and the COMP pin voltage is clamped to V(SKIP)+0.6V. ISL6730A/C use a fixed V(SKIP), which is 1.4V; for ISL6730B/D, the SKIP function are disabled.

The controller exits skip mode when  $V_{FB}$  drops to 88% (typical) of the reference voltage or when the sensed returned current exceeds 29µA.

### **Protection Circuits**

#### **Input Brownout, BO Protection**

Brownout occurs when there is a drop in the line voltage. The BO pin is a dual function pin. The BO pin detects the brownout condition and shuts down the gate driver and controller. During normal operation, the BO pin is used to compensate the effect of the input line voltage change on the voltage loop. To keep the harmonic distortion low, the corner frequency formed by the  $R_{BO}$  and  $C_{BO}$  should be lower than 6Hz.

The BO pin is the output of the average voltage of the rectified voltage. The PFC controller is turned off when the BO pin drops below 0.4V. This protects the PFC power stage to enable operation at or below brownout condition for long periods of time. The controller resumes operation when the BO pin returns to 0.5V.

The BO pin is usually connected to GND through a capacitor,  $C_{BO}$ . To avoid distortion on the VIN pin, select  $C_{BO}$  so that:

$$C_{BO} \gg 0.22 \mu F$$

(EQ. 6)

#### **Overcurrent Protection**

The peak current limiting function prevents the inductor from saturation. The gate driver turns off when the current goes above the current limit.

#### **Overpower Protection**

The overpower protection is implemented by limiting the COMP pin voltage higher than 3.85V (typical).

#### **Overvoltage Protection**

If the voltage on the FB pin exceeds the reference voltage by about 4%, the gate driver is turned off. The controller resumes normal operation after the FB pin drops below reference voltage.

#### **Over-Temperature Protection**

The ISL6730A, ISL6730B, ISL6730C, ISL6730D is protected against over-temperature conditions. When the junction temperature exceeds  $+160^{\circ}$ C, the PWM shuts down. Normal operation is resumed when the junction temperature decreases below  $+135^{\circ}$ C.

# **Application Guidelines**

#### **Layout Considerations**

As in any high frequency switching converter, layout is very important. Switching current from one power device to another can generate voltage transients across the impedances of the interconnecting bond wires and circuit traces. These interconnecting impedances should be minimized by using wide, short printed circuit traces. The critical components should be located as close together as possible using ground plane construction or single point grounding.

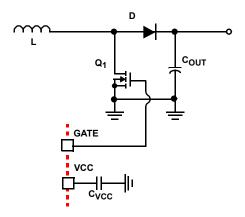

Figure 14 shows the critical power components;  $Q_1$ , D and  $C_{OUT}$ . To minimize the voltage overshoot, the interconnecting wires indicated by heavy lines should be part of the ground or the power plane in a printed circuit board. The components shown in Figure 14 should be located as close together as possible. Please note that the capacitors  $C_{VCC}$  and  $C_0$  each represent numerous physical capacitors. Locate the ISL6730A, ISL6730B, ISL6730C, ISL6730D within 2 inches of the MOSFET,  $Q_1$ . The circuit traces for the MOSFETs' gate and source connections from the ISL6730A, ISL6730B, ISL6730C, ISL6730D must be sized to handle up to 1.5A peak current.

FIGURE 14. CRITICAL CURRENT POWER COMPONENTS

#### **Component Selection Guidelines**

A 300W, universal input, PFC converter design is provided for demonstration. The design method is for a continuous current mode power factor correction boost converter with the ISL6730B/D. The switching frequency is 62kHz.

Table 3 shows the design parameters.

**TABLE 3. CONVERTER DESIGN PARAMETERS**

| PARAMETER         | CONDITIONS           | MIN | TYP | MAX | UNIT |

|-------------------|----------------------|-----|-----|-----|------|

| VLINE             |                      | 85  | 115 | 265 | VAC  |

| FLINE             |                      | 47  |     | 63  | Hz   |

| P <sub>OMAX</sub> | Maximum Output Power |     |     | 300 | W    |

| T <sub>HOLD</sub> | Hold Up Time         |     | 20  |     | ms   |

| Efficiency        | VLINE = 115VAC       | 92  |     |     | %    |

#### **BOOST INDUCTOR SELECTION**

First, calculate the maximum input RMS current, I<sub>INMAX</sub>.

$$I_{INMAX} = \frac{P_{OMAX}}{\eta \bullet V_{RMSmin}}$$

(EQ. 7)

Where  $\eta$  is the converter efficiency at  $\text{V}_{\mbox{RMSmin}}.$  PF is the power factor at  $\text{V}_{\mbox{RMSmin}}$

$$I_{\text{INMAX}} = \frac{300\text{W}}{0.92 \cdot 85\text{V}} = 3.84\text{A}$$

(EQ. 8)

Assuming the current is sinusoidal and the peak to peak ripple at line is 40%.

The boost inductor,  $L_{\mbox{\footnotesize{BST}}}$ , is given by the following equation:

$$L_{BST} \ge \frac{\sqrt{2} V_{RMSmin}}{0.4 \bullet F_{sw} \bullet \sqrt{2} \bullet I_{INM\Delta X}} \bullet \left(1 - \frac{\sqrt{2} \bullet V_{RMSmin}}{V_{OUT}}\right)$$

(EQ. 9)

$$L_{BST} \ge \frac{85 \text{V}}{0.4 \bullet 62 \text{kHz} \bullet 3.88 \text{A}} \bullet \left(1 - \frac{\sqrt{2} \bullet 85 \text{V}}{390 \text{V}}\right) = 617 \mu H \tag{EQ. 10}$$

The peak current of the inductor is the sum of the average peak inductor current and half of the peak to peak ripple current. Select and design the boost inductor as given by Equation 11. The ISL6730A, ISL6730B, ISL6730C, ISL6730D provides peak current limit function that can prevent the boost inductor saturation. Assuming 25% margin is given to the OCP threshold, select and design the boost inductor with saturation current given by Equation 11 with 25% more.

$$I_{LPeak} = \sqrt{2} \bullet I_{INMAX} \bullet \left(1 + \frac{0.4}{2}\right)$$

(EQ. 11)

$$I_{LPeak} = \sqrt{2} \cdot 3.88 A \cdot \left(1 + \frac{0.4}{2}\right) = 6.5 A$$

(EQ. 12)

#### **INPUT RECTIFIER**

The maximum average input current is calculated:

$$I_{\text{INAVE(max)}} = \frac{2 \bullet \sqrt{2} \bullet I_{\text{INMAX}}}{\pi}$$

(EQ. 13)

$$I_{\text{INAVE(max)}} = \frac{2 \cdot \sqrt{2} \cdot 3.88 \text{A}}{\pi} = 3.5 \text{A}$$

(EQ. 14)

13

Select the bridge diode using Equation 15 and sufficient reverse breakdown voltage. Assuming the forward voltage,  $V_{F,BR}$ , is 1V across each rectifier diode. The power loss of the rectifier bridge can be calculated:

$$P_{BR} = 2 \bullet V_{F, BR} \bullet I_{INAVE(MAX)}$$

(EQ. 15)

$$P_{BR} = 2 \cdot 1V \cdot 3.5A = 7W$$

(EQ. 16)

#### **INPUT CAPACITOR SELECTION**

Refer to Table 2 for the recommended input filter capacitor value.

$$C_{IN} = 300W \bullet \frac{0.33}{100} = 0.99 \mu F$$

(EQ. 17)

This is the recommended capacitor used after the diode bridge. For better power factor, less capacitance can be used. To lower the input filter inductor size, more capacitance can be used.

Two 0.47µF capacitors in parallel are used for C<sub>IN</sub>.

#### **BOOST DIODE SELECTION**

The boost diode loss is determined by the diode forward voltage drop,  $V_F$  and the output average current. The maximum output current is:

$$I_{OUT(max)} = \frac{P_{OMAX}}{V_{OUT}}$$

(EQ. 18)

$$I_{OUT(max)} = \frac{300W}{390V} = 0.77A$$

(EQ. 19)

The forward power loss on the diode is:

$$P_{FD} = I_{OUT(max)} \bullet V_{F}$$

(EQ. 20)

$$P_{FD} = 0.77A \cdot 1.85V = 1.42W$$

(EQ. 21)

The IDD03E60 part is selected.

The reverse recovery loss on the diode can be calculated. The  $Q_{RR}$  is found from the diode datasheet.  $Q_{RR}$  = 220nC when  $I_{\text{F}}$  = 3.5A.

The reverse recover loss on the diode can be estimated:

$$P_{RRD} = \frac{1}{4} \cdot Q_{RR} \cdot V_{OUT} \cdot F_{sw}$$

(EQ. 22)

$$P_{RRD} = \frac{1}{4} \cdot 220 \text{ nC} \cdot 390 \text{ V} \cdot 62 \text{ kHz} = 1.33 \text{ W}$$

(EQ. 23)

The total power loss on the diode is:

$$P_D = P_{FD} + P_{RRD} = (1.42 + 1.35)W = 2.75W$$

(EQ. 24)

#### **MOSFET POWER DISSIPATION**

The power dissipation on the MOSFET is from two different types of losses; the condition loss and the switching loss.

For the MOSFET, the worst case is at minimum line input voltage.

First, the drain to source RMS current is calculated:

$$I_{DS(max)} = I_{INMAX} \sqrt{1 - \frac{8\sqrt{2}}{3\pi}} \bullet \frac{V_{RMSmin}}{V_{OUT}}$$

(EQ. 25)

$$I_{DS(max)} = 3.88A \sqrt{1 - \frac{8\sqrt{2}}{3\pi} \cdot \frac{85V}{390V}} = 3.3A$$

(EQ. 26)

FN8258.0 February 26, 2013

The MOSFET, SPP20N60C3 is selected.

$$P_{COND} = I_{DS(max)}^{2} \bullet R_{DS(on)}$$

(EQ. 27)

$$P_{COND} = 3.3A^2 \bullet 0.3\Omega = 3.27W$$

(EQ. 28)

The switching loss of the MOSFET consists of three parts: the turn-on loss, the turn-off loss and the diode reverse recovery loss.

From the MOSFET datasheet, the typical switching losses curves are provided.

When  $R_G = 3.6\Omega$ ,  $I_D = 6A$ ,  $E_{ON} = 0.015$ mJ,  $E_{OFF} = 0.007$ mJ.

The switching loss due to transition is calculated:

$$P_{SW} = (E_{ON} + E_{OFF}) \bullet F_{sw}$$

(EQ. 29)

$$P_{SW} = (0.015 \text{mJ} + 0.007 \text{mJ}) \cdot 62 \text{kHz} = 1.36 \text{W}$$

(EQ. 30)

The diode reverse recovery incurs additional power loss on the MOSFET. This loss can be estimated as:

$$P_{RR} = Q_{RR} \bullet V_{OUT} \bullet F_{ew}$$

(EQ. 31)

This loss is also related the di/dt during the MOSFET turn-on. The di/dt can be found out from the MOSFET datasheet. At  $R_G=3.6\Omega,$  the turn-on di/dt is  $4000\text{A}/\mu\text{s}.$  From the Typical Reverse Recovery Charge curve at  $T_J=+125\,^{\circ}\text{C},$  the  $Q_{RR}=220\text{nC}$  when  $I_F=3.5\text{A}.$

$$P_{RR} = 220nC \cdot 390V \cdot 62kHz = 5.32W$$

(EQ. 32)

#### THE TOTAL LOSS ON THE MOSFET

$$P_{COND} + P_{SW} + P_{RR} = 3.27W + 1.36W + 5.32W = 9.95W$$

(EQ. 33)

#### **OUTPUT CAPACITOR SELECTION**

The output capacitor, C<sub>OUT</sub>, is required to hold the output above 300V during one line cycle. For capacitors with 20% tolerance, the tolerance should be taken into consideration. Thus, the output capacitance should be greater than:

$$C_{OUT} \ge \frac{2 \cdot T_{HOLD} \cdot P_{OMAX}}{V_{OUT}^2 - V_{HOLD}^2} \cdot (1 + 0.2)$$

(EQ. 34)

$$C_{OUT} \ge \frac{2 \cdot 20 \text{ms} \cdot 300 \text{W}}{(390)^2 - (300 \text{V})^2} \cdot (1 + 0.2) = 232 \mu\text{F}$$

(EQ. 35)

Calculate the ripple RMS current through the capacitor:

$$I_{CORMS(max)} = I_{OUT(max)} \sqrt{\frac{8\sqrt{2}}{3\pi}} \cdot \frac{V_{OUT}}{V_{RMSmin}} - 1$$

(EQ. 36)

$$I_{CORMS(max)} = 0.77A \sqrt{\frac{8\sqrt{2}}{3\pi}} \cdot \frac{390V}{85V} - 1 = 1.633A$$

(EQ. 37)

Select the proper capacitor according to the hold time and ripple RMS current requirement. The actual capacitance is  $270\mu F$ .

It is important to make sure the output peak-to-peak ripple is less than the minimum OVP threshold as specified in the "Electrical Specifications" table on page 6. The ESR at 2 times of the line frequency of the capacitor is found in the capacitor datasheet. The ESR of the output capacitor is  $770m\Omega$  at 100Hz.

14

$$V_{Opp} = I_{OUT(max)} \cdot \frac{\sqrt{(2\pi f_{line} \cdot C_{OUT} \cdot ESR)^2 + 1}}{(2\pi f_{line}) \cdot C_{OUT} \cdot 0.8}$$

(EQ. 38)

$$V_{Opp} = 0.77 \text{A} \cdot \frac{\sqrt{(2\pi \cdot 100 \text{Hz} \cdot 270 \mu \text{F} \cdot 0.77 \Omega)^2 + 1}}{(2\pi \cdot 100 \text{Hz}) \cdot 270 \mu \text{F} \cdot 0.8} = 6.6 \text{V} \tag{EQ. 39}$$

The minimum OVP threshold is 103% of the nominal output value. The maximum output peak to peak ripple should be less than 6% of the nominal value, which is 23.4V<sub>P-P</sub>.

#### **CURRENT SENSING RESISTORS**

Please refer to Equation 4 for calculation of the current sensing resistor  $R_{\mbox{\footnotesize{CS}}}.$

$$R_{CS} \ge \frac{120 \,\text{mV} \cdot 265 \,\text{V} \cdot 0.92}{\sqrt{2} \cdot 300 \,\text{W}} = 0.069 \,\Omega$$

(EQ. 40)

While a large  $R_{CS}$  renders better current sensing accuracy, larger  $R_{CS}$  also incurs higher power dissipation. Select  $R_{CS}$  from available standard value resistors to determine the sense resistor.

$$R_{CS} = 0.068\Omega \tag{EQ. 41}$$

The maximum power dissipation on the  $R_{CS}$  occurs at low line and full load condition. The maximum power dissipation is calculated:

$$P_{RCSMAX} = I_{INMAX}^{2} \cdot R_{CS}$$

(EQ. 42)

$$P_{RCSMAX} = 3.88A^2 \cdot 0.068\Omega = 1.023W$$

(EQ. 43)

The resistor, R<sub>SEN</sub> sets the overcurrent protection limit. From Equation 3, R<sub>SEN</sub> should be greater than:

$$R_{SEN} \ge \frac{R_{CS} \cdot I_{LPeak} \cdot (1 + 0.25)}{2 \cdot 0.5 |I_{OC}|}$$

(EQ. 44)

Where |x| stands for the ABS(x) function.

$$R_{SEN} \ge \frac{0.068\Omega \bullet 6.6A \bullet 1.25}{2 \bullet 0.18 \text{mA}} = 3.117 \text{k}\Omega$$

(EQ. 45)

Select RSEN from available standard value resistors, the selected RSEN is 3.16k $\Omega$ .

#### **CURRENT LOOP COMPENSATION**

The input current shaping is achieved by comparing the sensed current signal to the sensed input voltage signal. The current error amplifier (Gmi), together with the current compensation network, adjusts the duty cycle so that the inductor current traces the sensed rectified voltage. Thus, unity power factor is achieved.

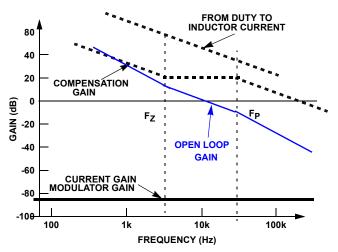

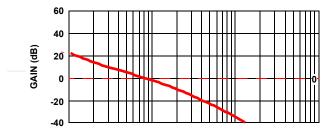

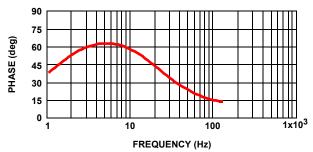

The compensation network consists of the Trans-Conductance error amplifier (Gmi) and the impedance network ( $Z_{ICOMP}$ ). The goal of the compensation network is to provide a closed loop transfer function with the sufficient OdB crossing frequency ( $f_{OdB}$ ) and adequate phase margin. Phase margin is the difference between the open loop phase at  $f_{OdB}$  and  $180\,^\circ$ . The following equations relate the compensation network's poles, zeros and gain to the components ( $R_{ic}$ ,  $C_{ic}$  and  $C_{ip}$ ) in Figure 15.

FIGURE 15. INDUCTOR CURRENT SENSING SCHEME

FIGURE 16. ASYMPTOTIC BODE PLOT OF CURRENT LOOP GAIN

$$F_{Z} = \frac{1}{2\pi \cdot R_{ic} \cdot C_{ic}}$$

(EQ. 46)

$$F_{p} = \frac{1}{2\pi \cdot R_{ic} \cdot \frac{C_{ip} \cdot C_{ic}}{C_{ip} + C_{ic}}}$$

(EQ. 47)

Use the following guidelines for locating the poles and zeros of the compensation network.

The cross over frequency of the current loop should be set between 2kHz to 100kHz. At cross over frequency, the transfer function from duty cycle to inductor current is well approximated by Equation 48:

$$G_{id}(s) = \frac{V_{OUT}}{L_{BST} \cdot s}$$

(EQ. 48)

It is recommended to set the cross over frequency from 1/10 to 1/6 of the switching frequency with phase margin of  $60^{\circ}$ . A high frequency pole is set at 1/2 of the switching frequency for ripple filtering. In this example, we set the cross over,  $F_C$  at 1/6 of the switching frequency.

$$F_{Z} = \frac{F_{C}}{\tan\left(\arctan\left(\frac{F_{C}}{F_{P}}\right) + \Phi_{M}\right)}$$

(EQ. 49)

Where F  $_{C}$  = F  $_{S}/6$  = 10.3kHz,  $\Phi_{M}$  is the phase margin, which is 60  $^{\circ}$  . F  $_{P}$  = F  $_{S}/2$  = 31kHz.

Thus, the current loop compensation zero is:

$$F_Z = \frac{(62KHz)/6}{\tan(\tan(\frac{2}{6}) + 60\deg)} = 2.12kHz$$

(EQ. 50)

The total compensation capacitance is calculated:

$$C_{ip} + C_{ic} = \left( \left( \frac{V_{OUT}}{L_{BST} \cdot (2\pi f_c)^2} \cdot \frac{A_{iDC}}{V_m} \cdot \frac{R_{CS}}{R_{SEN}} \right) \cdot \sqrt{\frac{1 + (f_c/f_z)^2}{1 + (f_c/f_p)^2}} \right)$$

(EQ. 51)

$$C_{ip} + C_{ic} = (19.8)nF$$

(EQ. 52)

$$C_{ip} = (C_{ip} + C_{iC}) \frac{f_z}{f_p}$$

(EQ. 53)

The value of the noise filtering capacitor is:

$$C_{ip} = 14.9 nF \cdot \frac{2.12 kHz}{31 kHz} = 1.35 nF$$

(EQ. 54)

The value of Cic is:

$$C_{ic} = 19.8nF - 1.35nF = 18.4nF$$

(EQ. 55)

The value of R<sub>ic</sub> is:

$$R_{ic} = \frac{1}{2\pi \cdot 2.12 \text{kHz} \cdot 18.4 \text{nF}} = 4.11 \text{k}\Omega$$

(EQ. 56)

Select the R<sub>C</sub> value from the standard value, we have:

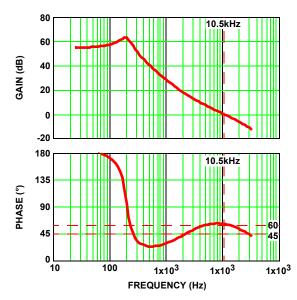

$\rm R_{ic}$  = 4.02k $\Omega,$   $\rm C_{ic}$  = 18nF,  $\rm C_{ip}$  = 1.2nF. Figure 17 shows the actual bode plot of current loop gain.

FIGURE 17. BODE PLOT OF THE ACTUAL CURRENT LOOP GAIN

#### **INPUT VOLTAGE SETTING**

First, set the BO resistor divider gain,  $K_{BO}$  according to Equation 1 and Equation 2.

Assuming the converter starts at  $V_{LINE}$  =  $80V_{RMS}$ , then the BO resistor divider gain,  $K_{BO}$  should be:

$$K_{BO} = \frac{0.5V}{80V - 2V} = 0.00641$$

(EQ. 57)

In this design, two 3.3M $\Omega$  resistors in series are used for R<sub>IN2</sub>. So, R<sub>IN1</sub> is calculated:

$$R_{IN1} = \frac{0.00641}{1 - 0.00641} \cdot (6.6M\Omega) = 42.6k\Omega$$

(EQ. 58)

Using resistor from the standard value,  $R_{IN1}$  = 43k $\Omega$ , the actual  $K_{BO}$  is calculated:

$$K_{BO} = \frac{R_{IN1}}{R_{IN1} + R_{IN2}} = 0.00647$$

(EQ. 59)

#### **NEGATIVE INPUT CAPACITOR GENERATION**

The ISL6730A, ISL6730B, ISL6730C, ISL6730D generates an equivalent negative capacitance at the input to cancel the input filter capacitance. Thus, more input capacitors can be used without reducing the power factor.

The input equivalent negative capacitance is a function of the current sensing gain, BO resistor divider gain and the compensation components.

$$C_{NEG} = \left(K_{BO} \cdot 0.8 - \frac{V_m}{V_{OUT}}\right) \frac{R_{SEN}}{R_{CS}A_{iDC}} (C_{ic} + C_{ip}) \tag{EQ. 60}$$

$$C_{NEG} = \left(0.00647 \cdot 0.8 - \frac{1.5}{390}\right) \frac{3.16k}{0.068 \cdot 1.9} (18nF + 1.2nF) = 0.62 \mu F \tag{EO. 61}$$

This equivalent negative capacitor cancels the input filter capacitor required for EMI filtering. Therefore, the displacement power factor significantly improves.

For example,  $C_{F1}$  = 0.68 $\mu$ F,  $C_{IN}$  = 0.94 $\mu$ F, using the low cost EMI filter shown in Figure 13. When  $V_{LINE}$  = 230VAC,  $f_{LINE}$  = 50Hz,  $P_0$  = 60W.

Assuming 95% efficiency under the above test condition, the resistive component, which is in phase to voltage:

$$I_a = \frac{P_o}{V_{LINE} \cdot 0.95} = 0.275A$$

(EQ. 62)

The reactive current through the input capacitors:

$$I_c = V_{LINF} \bullet (2\pi \cdot f_{LINF}) \bullet (C_{F1} + C_{IN}) = 0.117A$$

(EQ. 63)

Thus, the displacement power factor is:

$$PF_{DIS} = \frac{I_a}{\sqrt{(I_a)^2 + (I_c)^2}} = 0.92$$

(EQ. 64)

The reactive current generated by the equivalent negative capacitor is:

$$I_{cneg} = V_{LINE} \bullet (2\pi \cdot f_{LINE}) \bullet (C_{NEG}) = 0.045A$$

(EQ. 65)

With the equivalent negative capacitor, the total reactive current reduces to:

$$I_{c} - I_{cneq} = 0.072A$$

(EQ. 66)

The displacement power factor increases to:

$$PF_{DIS} = \frac{I_a}{\sqrt{(I_a)^2 + (I_c - I_{cneg})^2}} = 0.967$$

(EQ. 67)

#### **VOLTAGE LOOP COMPENSATION**

The average diode forward current can be approximated by:

$$I_{D(ave)} = \frac{P_{in}}{V_{OUT}}$$

(EQ. 68)

Assuming the input current traces the input voltage perfectly. The input power is in proportion to  $(V_{\mbox{COMP}}$  - 1V).

$$I_{D(ave)} = \frac{R_{SEN}}{R_{CS} \cdot 0.5 \cdot R_{IS}} \bullet \frac{1}{V_{OUT}} \bullet \left(\frac{0.25}{\left((2\sqrt{2})/\pi\right)^2 \cdot K_{BO}}\right) \bullet \Delta_{COMP}$$

(EQ. 69)

Where  $\triangle_{COMP}$  is the V<sub>COMP</sub> - 1V. 1V is the offset voltage.

$R_{IS}$  is the internal current scaling resistor.  $R_{IS}$  = 16k $\Omega$ .

$$I_{D(ave)} = 0.598 \frac{A}{V} \bullet \Delta_{COMP}$$

(EQ. 70)

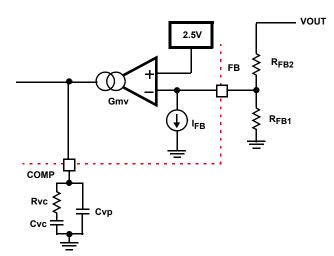

FIGURE 18. OUTPUT VOLTAGE SENSING AND COMPENSATION

Thus, the transfer function from  $\overline{V}_{COMP}$  to  $\overline{V}_{OUT}$  is:

$$G_{PS}(s) = \frac{V_{OUT}(s)}{\Delta_{COMP}} = \frac{1}{C_O \cdot s} \cdot \frac{I_{D(ave)}}{\Delta_{COMP}} \tag{EQ. 71}$$

$$G_{PS}(s) = \left(\frac{I_{D(ave)}}{C_{O} \cdot s} \cdot \frac{1}{\Delta_{COMP}}\right) = \frac{0.598}{C_{O} \cdot s}$$

(EQ. 72)

As shown in Figure 18, the voltage loop gain is:

$$G_{VLOOP}(s) = G_{PS}(s) \cdot G_{DIV} \cdot gmv \cdot Z_{COMP}(s)$$

(EQ. 73)

The output feedback resistor divider gain, GDIV is:

$$G_{DIV} = \frac{V_{REF}}{V_{OUT}}$$

(EQ. 74)

The compensation gain uses external impedance networks as shown in Figure 18, Z<sub>COMP</sub>(s) is given by:

$$Z_{COMP}(s) = \frac{1}{(C_{vc} + C_{vp}) \cdot s} \bullet \frac{R_{vc} \bullet C_{vc} \bullet s + 1}{R_{vc} \bullet C_{vc} \bullet C_{vp}} \bullet s + 1$$

(EQ. 75)

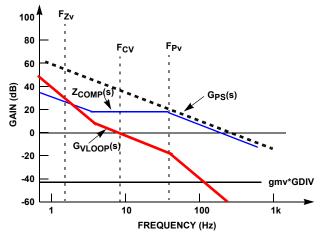

The targeted cross over frequency,  $F_{CV}$  is 8Hz. The high frequency pole,  $F_{PV}$  is required in order to reject the 2 time line frequency component.  $F_{PV}$  = 20Hz. The targeted phase margin is 60°.

FIGURE 19. ASYMPTOTIC BODE PLOT OF CURRENT LOOP GAIN

The zero,  $F_{Zv}$  is calculated:

$$F_{Zv} = \frac{F_{CV}}{\tan(\Phi_{m} + \tan(F_{CV}/(F_{Pv})))}$$

(EQ. 76)

$$F_{Zv} = \frac{8Hz}{tan(60deg + atan((8Hz)/(20Hz)))} = 1.15Hz$$

(EQ. 77)

Then the total capacitance used for compensation is calculated:

$$C_{vc} + C_{vp} = \frac{\left|G_{PS}(i \bullet (2\pi F_{CV}))\right| \bullet G_{DIV} \bullet Gmv}{(2\pi F_{CV})} \bullet \sqrt{\frac{\left(F_{CV}/F_{ZV}\right)^2 + 1}{\left(F_{CV}/F_{PV}\right)^2 + 1}}$$

(Eq. 78)

Thus, the total compensation capacitance is:

$$C_{vc} + C_{vp} = 1829nF$$

(EQ. 79)

$$C_{vp} = 1829 nF \cdot \frac{F_{ZV}}{F_{ZP}} = 105 nF$$

(EQ. 80)

$$C_{VC} = 1829 nF - 105 nF = 1724 nF$$

(EQ. 81)

$$R_{VC} = \frac{1}{2 \cdot \pi \cdot F_{ZV} \cdot C_{VC}} = 81.2 \text{k}\Omega$$

(EQ. 82)

Choose components from the standard values. We have  $C_{VP}$  = 100nF,  $C_{VC}$  = 1500nF,  $R_{VC}$  = 82.5k $\Omega$ . The actual bode plot is shown in Figure 20.

FIGURE 20. BODE PLOT OF THE ACTUAL VOLTAGE LOOP GAIN

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE              | REVISION | CHANGE          |

|-------------------|----------|-----------------|

| February 26, 2013 | FN8258.0 | Initial Release |

### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the fastest growing markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil or to find out how to become a member of our winning team, visit our website and career page at <a href="https://www.intersil.com">www.intersil.com</a>.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective product information page. Also, please check the product information page to ensure that you have the most updated datasheet: <u>ISL6730A</u>.

To report errors or suggestions for this datasheet, please go to: www.intersil.com/askourstaff

Reliability reports are available from our website at: http://rel.intersil.com/reports/search.php

For additional products, see <a href="www.intersil.com/en/products.html">www.intersil.com/en/products.html</a>

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/en/support/qualandreliability.html

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

intersil

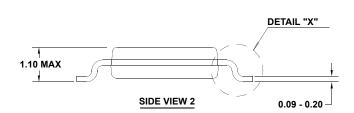

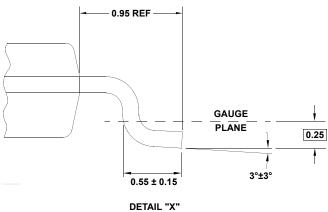

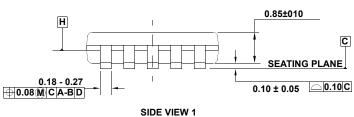

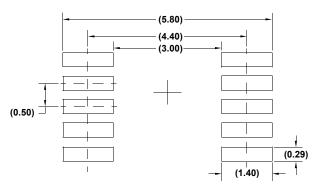

# Package Outline Drawing M10.118

#### 10 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

Rev 1, 4/12

**TOP VIEW**

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- Dimensioning and tolerancing conform to JEDEC MO-187-BA and AMSEY14.5m-1994.

- 3. Plastic or metal protrusions of 0.15mm max per side are not included.

- Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.