**Features**

# Step-Up Converter for Handheld Applications

### **General Description**

The MAX8969 is a simple 1A step-up converter in a small package that can be used in any single-cell Li-ion application. This IC provides protection features such as input undervoltage lockout, short circuit, and overtemperature shutdown.

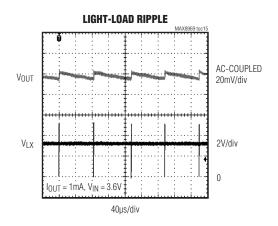

The IC transitions to skip mode seamlessly under lightload conditions to improve efficiency. Under these conditions, switching occurs only as needed, reducing switching frequency and supply current to maintain high efficiency.

When the input voltage is sufficient to drive the load, the IC can be operated in track mode or automatic track mode (ATM). In track mode, the p-channel MOSFET acts as a current-limited load switch and quiescent current is as low as 30µA under a no-load condition. In ATM mode, the p-channel MOSFET acts as a current-limited load switch and quiescent current is as low as 60µA under a no-load condition. In ATM mode, the internal boost circuitry is enabled, allowing for fast transitions into boost mode.

The IC is available in a small, 1.25mm x 1.25mm, 9-bump WLP (0.4mm pitch) package.

### **Applications**

Cell Phones Smartphones Mobile Internet Devices GPS, PND eBooks

♦ Compact Lavout Small, 1.25mm x 1.25mm WLP Package 3MHz PWM Switching Frequency **Small External Components**

♦ Safe and Efficient Step-Up Mode **Up to 1A Output Current** 2.5V to 5.5V Input Voltage Range 3.3V to 5V Ouput Voltage Range Over 90% Efficiency with Internal Synchronous Rectifier Low 45µA No-Load Quiescent Current **Soft-Start Controls Inrush Current**

**♦ Track Mode**

True Shutdown™

Low 1µA Shutdown Current

- **1A Current Limited** 130mΩ On-Resistance Low 30µA No Load Quiescent Current

- **♦ Automatic Track Mode** 130m $\Omega$  On-Resistance Low 60µA No-Load Quiescent Current **Boost Circuitry Enabled for Fast Transition into Boost**

### **Typical Operating Circuit**

| INPUT<br>2.5V T0 5.5V<br>C <sub>IN</sub> 4.7μF — | IN LX_ OUT_  MAX8969  EN  TREN | OUTPUT<br>3.7V, 1A<br>Cout<br>22µF |

|--------------------------------------------------|--------------------------------|------------------------------------|

|                                                  | GND_<br>                       |                                    |

True Shutdown is a trademark of Maxim Integrated Products, Inc.

### **Ordering Information**

| PART          | Vout<br>(V) | TEMP RANGE     | PIN-<br>PACKAGE |

|---------------|-------------|----------------|-----------------|

| MAX8969EWL33+ | 3.3         | -40°C to +85°C | 9 WLP           |

| MAX8969EWL35+ | 3.5         | -40°C to +85°C | 9 WLP           |

| MAX8969EWL37+ | 3.7         | -40°C to +85°C | 9 WLP           |

| MAX8969EWL42+ | 4.25        | -40°C to +85°C | 9 WLP           |

| MAX8969EWL50+ | 5.0         | -40°C to +85°C | 9 WLP           |

**Note:** The output voltage range is from 3.3V to 5V. Contact the factory for output options and availability.

+Denotes a lead(Pb)-free/RoHS-compliant package.

/U/IXI/U

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, OUT_ to GND                                       | 0.3V to +6.0V      |

|-------------------------------------------------------|--------------------|

| EN, TREN to GND0.3V to lower of                       | (VIN + 0.3V) or 6V |

| Total LX_ Current                                     | 3.2ARMS            |

| OUT_ Short Circuit to GND                             | Continuous         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                    |

| WLP (derate 12mW/°C above +70°C)                      | 960mW              |

| Operating Temperature Range             | 40°C to +85°C  |

|-----------------------------------------|----------------|

| Junction Temperature                    | +150°C         |

| Storage Temperature Range               | 65°C to +150°C |

| Soldering Temperature (reflow) (Note 1) | +260°C         |

**Note 1:** This device is constructed using a unique set of packaging techniques that impose a limit on the thermal profile that the device can be exposed to during board level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 2)

WLP

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......83°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......50°C/W

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maxim-ic.com/thermal-tutorial**.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 2.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted. Typical values are } T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER                             | CONDITIONS                         |                   |                        | MIN  | TYP  | MAX  | UNITS |  |

|---------------------------------------|------------------------------------|-------------------|------------------------|------|------|------|-------|--|

| Operating Input Voltage Range         |                                    |                   |                        | 2.5  |      | 5.5  | V     |  |

| Minimum Startup Voltage               |                                    |                   |                        |      | 2.3  |      | V     |  |

| Undervoltage Lockout Threshold (UVLO) | V <sub>IN</sub> falling, 75mV hyst | teresis           |                        | 2.1  | 2.2  | 2.3  | V     |  |

| Chutdown Cupply Current               | VEN = VTREN = VOUT                 | = 0V,             | T <sub>A</sub> = +25°C |      | 0.8  | 5    | ^     |  |

| Shutdown Supply Current               | $V_{IN} = 4.8V$                    |                   | T <sub>A</sub> = +85°C |      | 1    |      | μA    |  |

| Thermal Shutdown                      | T <sub>A</sub> rising, 20°C hyster | esis              | •                      |      | +165 |      | °C    |  |

| BOOST MODE                            |                                    |                   |                        |      |      |      |       |  |

| Continuous Output Current             | V <sub>IN</sub> > 2.5V (Note 4)    |                   |                        | 1    |      |      | А     |  |

|                                       |                                    | V <sub>OU</sub> - | T = 3.3V               | 0.9  |      |      |       |  |

|                                       | V <sub>IN</sub> > 2.5V, pulse load | Vou               | Γ = 3.5V               | 0.8  |      |      |       |  |

| Pook Output Current                   |                                    | V <sub>OU</sub> - | r = 3.7V               | 0.7  |      |      | A     |  |

| Peak Output Current                   |                                    | V <sub>OU</sub> - | T = 4.25V              | 0.7  |      |      |       |  |

|                                       |                                    | V <sub>OU</sub> - | T = 4.7V               | 0.7  |      |      |       |  |

|                                       | V                                  |                   | T = 5.0V               | 0.7  |      |      |       |  |

| Switching Frequency                   | (Note 4)                           |                   |                        |      | 3    |      | MHz   |  |

|                                       | No load, VOUT_TARGET = 3.3V        |                   | 3.175                  | 3.30 | 3.40 |      |       |  |

|                                       | No load, Vout_target = 3.5V        |                   | 3.40                   | 3.50 | 3.60 | V    |       |  |

| Output Voltage Accuracy               | No load, Vout_target = 3.7V        |                   | 3.64                   | 3.75 | 3.85 |      |       |  |

|                                       | No load, Vout_TARGE                | ET = 4.25         | 5V                     | 4.10 | 4.25 | 4.35 | 1     |  |

|                                       | No load, Vout_target = 5V          |                   | 4.85                   | 5.00 | 5.10 | 1    |       |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.6V, T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are  $T_A = +25$ °C.) (Note 3)

| PARAMETER                                                | CON                                                                                                                                                             | DITIONS                 | <b>;</b>               | MIN  | TYP | MAX  | UNITS        |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------|------|-----|------|--------------|--|

|                                                          | $2.5V < V_{IN} < V_{ATMRT}$ , conditions emulating 0 < $I_{OUT} < 1A$ , $C_{OUT} = 22\mu F$ , $L = 1\mu H$ , $V_{OUT\_TARGET} = 3.3V$                           |                         |                        | 3.00 |     | 3.45 |              |  |

|                                                          | 2.5V < V <sub>IN</sub> < V <sub>ATMRT</sub> , conditions emulating 0 < I <sub>OUT</sub> < 1A, C <sub>OUT</sub> = 22μF, L = 1μH, V <sub>OUT</sub> _TARGET = 3.5V |                         |                        | 3.15 |     | 3.65 |              |  |

| Steady-State Output Voltage (Notes 5, 6)                 | 2.5V < V <sub>IN</sub> < V <sub>ATMRT</sub> ,<br>I <sub>OUT</sub> < 1A, C <sub>OUT</sub> = 22<br>V <sub>OUT</sub> _TARGET = 3.7V                                |                         |                        | 3.35 |     | 3.85 | V            |  |

|                                                          | 2.5V < VIN < VATMRT,<br>IOUT < 600mA, COUT<br>VOUT_TARGET = 4.25V                                                                                               | $= 22 \mu F$ ,          |                        | 3.95 |     | 4.35 |              |  |

|                                                          | 2.5V < VIN < VATMRT,<br>IOUT < 500mA, COUT<br>VOUT_TARGET = 5V                                                                                                  |                         |                        | 4.50 |     | 5.10 |              |  |

| LX_ Leakage Current                                      | V <sub>L</sub> X = 0V, 4.8V                                                                                                                                     |                         | T <sub>A</sub> = +25°C |      | 0.1 | 5    | μA           |  |

| EX_ Edukago darront                                      | $T_{A} = +85^{\circ}C$                                                                                                                                          |                         |                        | 0.2  |     | μπ   |              |  |

| Skip-Mode Supply Current                                 | EN = high, I <sub>OUT</sub> = 0A, 1µH inductor (TREN is low, not switching)                                                                                     |                         |                        |      | 45  |      | μA           |  |

| pMOS Turn-Off Current (Zero-Cross Current)               |                                                                                                                                                                 |                         |                        |      | 10  |      | mA           |  |

| LX_ nMOS Current Limit                                   |                                                                                                                                                                 |                         |                        |      | 2.6 | 3.2  | А            |  |

| Maximum Duty Cycle                                       |                                                                                                                                                                 |                         |                        |      | 83  |      | %            |  |

| Minimum Duty Cycle                                       |                                                                                                                                                                 |                         |                        | 0    |     |      | %            |  |

|                                                          | Vout = 3.3V                                                                                                                                                     |                         |                        |      | 120 |      |              |  |

|                                                          | V <sub>OUT</sub> = 3.5V                                                                                                                                         |                         |                        | 115  |     |      | -            |  |

| pMOS On-Resistance                                       | V <sub>OUT</sub> = 3.7V                                                                                                                                         | V <sub>OUT</sub> = 3.7V |                        |      | 110 |      | mΩ           |  |

|                                                          | V <sub>OUT</sub> = 4.25V                                                                                                                                        |                         |                        |      | 100 |      |              |  |

|                                                          | V <sub>OUT</sub> = 5V                                                                                                                                           |                         |                        |      | 91  |      |              |  |

|                                                          | VOUT = 3.3V                                                                                                                                                     |                         |                        |      | 65  |      |              |  |

|                                                          | V <sub>OUT</sub> = 3.5V                                                                                                                                         |                         |                        |      | 63  |      |              |  |

| nMOS On-Resistance                                       | V <sub>OUT</sub> = 3.7V                                                                                                                                         |                         |                        |      | 60  |      | mΩ           |  |

|                                                          | Vout = 4.25V                                                                                                                                                    |                         |                        | 55   |     |      |              |  |

|                                                          | V <sub>OUT</sub> = 5V                                                                                                                                           |                         |                        |      | 51  |      |              |  |

| Minimum Output Capacitance for Stable Operation (Actual) |                                                                                                                                                                 |                         |                        |      | 8   |      | μF           |  |

|                                                          |                                                                                                                                                                 | Vout                    | = 3.3V                 |      | 70  |      |              |  |

|                                                          |                                                                                                                                                                 | Vout                    | = 3.5V                 |      | 55  |      | -<br>-<br>μF |  |

| Maximum Output Capacitance (Actual)                      | 0 < IOUT < 0.3A                                                                                                                                                 | Vout                    | = 3.7V                 |      | 45  |      |              |  |

|                                                          | during startup                                                                                                                                                  |                         | = 4.25V                |      | 30  |      |              |  |

|                                                          | Vout = 5V                                                                                                                                                       |                         |                        |      | 20  | ,    |              |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 2.6V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are  $T_A = +25^{\circ}C.)$  (Note 3)

| PARAMETER                          | CONDITION                                                       | CONDITIONS                                                     |      | TYP  | MAX  | UNITS             |  |

|------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|------|------|------|-------------------|--|

| Output Voltage Ripple              | IOUT = 150mA, circuit of Figu                                   | I <sub>OUT</sub> = 150mA, circuit of Figure 1                  |      |      |      | mV <sub>P-P</sub> |  |

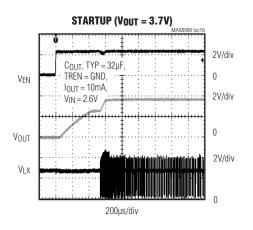

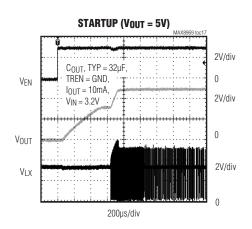

| Soft-Start Interval                | I <sub>OUT</sub> = 10mA, see the <i>Outpu</i> Selection section | IOUT = 10mA, see the <i>Output Capacitor</i> Selection section |      |      |      | μs                |  |

| TRACK MODE                         |                                                                 |                                                                |      |      |      |                   |  |

| pMOSFET On-Resistance              | I <sub>OUT</sub> = 500mA, V <sub>IN</sub> = 2.7V                |                                                                |      | 130  |      | mΩ                |  |

| piviospet on-nesistance            | IOUT = 500mA, VIN = 3.2V                                        |                                                                |      | 110  |      | 11122             |  |

| Track Current Limit                | V <sub>OUT</sub> = 3.6V                                         |                                                                | 1    | 2    |      | А                 |  |

| Track Mode Quiescent Current       | EN = low, TREN = high                                           |                                                                |      | 30   |      | μΑ                |  |

| AUTOMATIC TRACK MODE (ATM)         |                                                                 |                                                                | •    |      |      | •                 |  |

| ATM Supply Current                 | V <sub>IN</sub> = 5.4V                                          |                                                                |      | 65   |      | μΑ                |  |

|                                    | VOUT_TARGET = 3.3V                                              |                                                                |      | 3.15 |      |                   |  |

| ATM VIN Rising Threshold (VATMRT)  | VOUT_TARGET = 3.5V                                              | 3.35<br>3.55                                                   |      |      | V    |                   |  |

|                                    | VOUT_TARGET = 3.7V                                              |                                                                |      |      |      |                   |  |

|                                    | VOUT_TARGET = 4.25V                                             |                                                                | 4.04 |      | ]    |                   |  |

|                                    | VOUT_TARGET = 5V                                                |                                                                |      | 4.74 |      | 7                 |  |

|                                    | VOUT_TARGET = 3.3V                                              |                                                                |      | 3.10 |      |                   |  |

|                                    | VOUT_TARGET = 3.5V                                              | VOUT_TARGET = 3.5V                                             |      |      | 3.29 |                   |  |

| ATM VIN Falling Threshold (VATMFT) | VOUT_TARGET = 3.7V                                              | VOUT_TARGET = 3.7V                                             |      |      |      | V                 |  |

|                                    | VOUT_TARGET = 4.25V                                             | VOUT_TARGET = 4.25V                                            |      |      |      | 1                 |  |

|                                    | VOUT_TARGET = 5V                                                |                                                                | 4.69 |      |      | 1                 |  |

| Boost to ATM Transition Time       | (Note 7)                                                        |                                                                | 1    | ,    | μs   |                   |  |

| ATM to Boost Transition Time       |                                                                 |                                                                |      | 1    |      | μs                |  |

| LOGIC CONTROL                      |                                                                 |                                                                |      |      |      |                   |  |

| EN, TREN Logic Input High Voltage  | 2.3V < V <sub>IN</sub> < 5.5V                                   |                                                                | 1.05 |      |      | V                 |  |

| EN, TREN Logic Input Low Voltage   | $2.3V < V_{IN} < 5.5V$                                          |                                                                |      | 0.4  | V    |                   |  |

| EN, TREN Leakage Current           | VEN = VTREN = 0V                                                | $T_A = +25^{\circ}C$ $T_A = +85^{\circ}C$                      | -1   | 0.01 | +1   | μΑ                |  |

- **Note 3:** Specifications are 100% production tested at T<sub>A</sub> = +25°C. Limits over the operating temperature range are guaranteed by design and characterization.

- **Note 4:** Continuous operation with 1A at elevated ambient temperature and low voltage is not guaranteed. Under worst-case conditions, die thermal protection cannot be activated after 100ms of 1A load application. See the continuous output current parameter for a conservative estimate of current that can be maintained at  $T_A = +85^{\circ}C$ .

- **Note 5:** Switching frequency decreases if input voltage is > 83% of the output voltage selected. This allows duty factor to drop to values necessary to boost output voltage less than 25% without the use of pulse widths less than 60ns.

- Note 6: Contact factory for other options.

- **Note 7:** The output voltage regulation is a direct function of the peak current in the nMOS power switch. The inductor current (ILX) described in the conditions of the steady-state output voltage specification corresponds to the peak inductor current.

- Note 8: Once ATM threshold is reached boost switching stops in 1μs (typ), but the transition to ATM does not occur until V<sub>OUT</sub> has fallen equal to V<sub>IN</sub>.

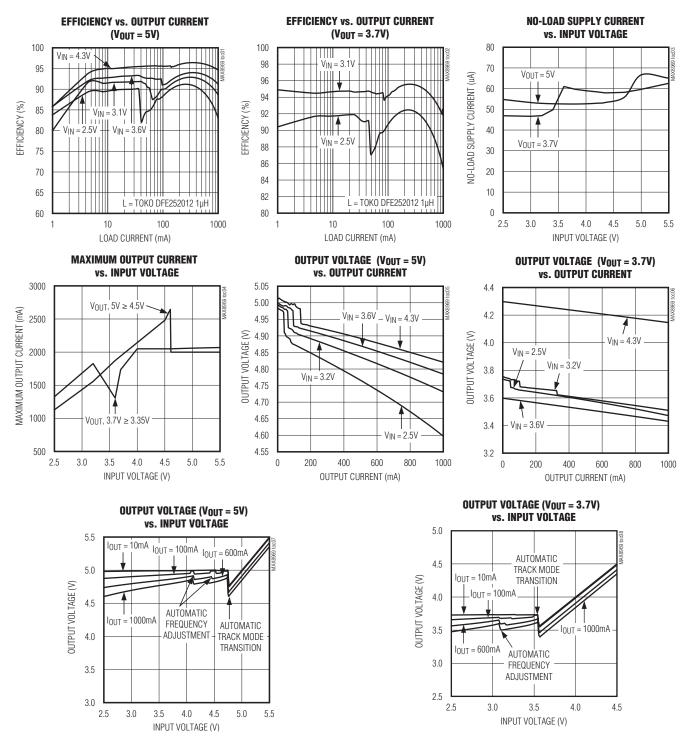

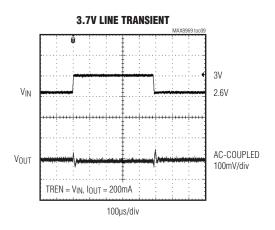

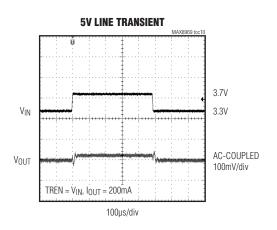

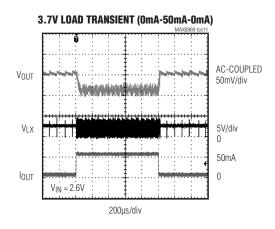

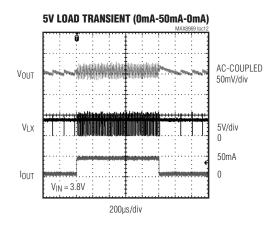

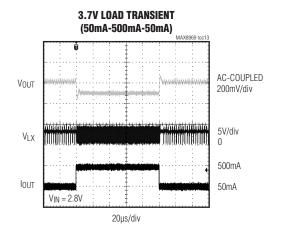

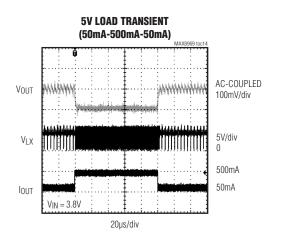

### **Typical Operating Characteristics**

$(V_{IN} = 3.6V, C_{OUT} = 22\mu F, X5R, 6.3V local and 10\mu F, X5R, 6.3V, 1\mu H inductor, circuit of Figure 1, TA = +25°C, unless otherwise noted.)$

### Typical Operating Characteristics (continued)

(VIN = 3.6V, COUT = 22μF, X5R, 6.3V local and 10μF, X5R, 6.3V, 1μH inductor, circuit of Figure 1, TA = +25°C, unless otherwise noted.)

### **Typical Operating Characteristics**

$(V_{IN} = 3.6V, C_{OUT} = 22\mu F, X5R, 6.3V local and 10\mu F, X5R, 6.3V, 1\mu H inductor, circuit of Figure 1, TA = +25°C, unless otherwise noted.)$

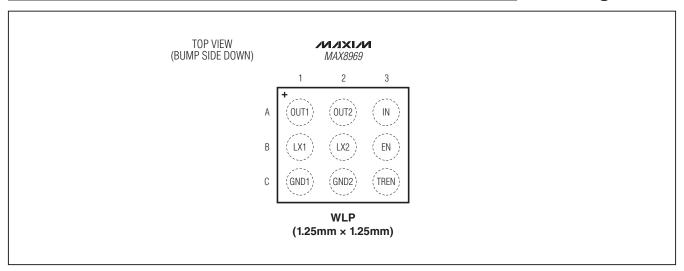

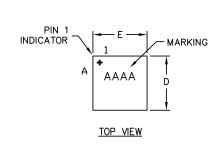

### Pin Configuration

## Pin Description

| PIN | NAME | FUNCTION                                                                                                                                                                                                        |

|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | OUT1 | Power Output. Bypass OUT_ to ground with a 22µF rated ceramic capacitor. For optimal performance place the ceramic capacitor as close as possible to OUT OUT1 and OUT2                                          |

| A2  | OUT2 | should be shorted together directly under the IC. In True Shutdown, the output voltage can fall to 0V, but OUT_ has a diode with its cathode connected to IN. See Figure 3.                                     |

| А3  | IN   | Input Supply Voltage. Bypass IN to GND_ with a 4.7µF ceramic capacitor. A larger capacitance may be required to reduce noise.                                                                                   |

| B1  | LX1  | Converter Switching Node. Connect a 1µH inductor from LX_ to IN. LX_ is high impedance in                                                                                                                       |

| B2  | LX2  | shutdown. LX1 and LX2 should be shorted together directly under the IC.                                                                                                                                         |

| В3  | EN   | Enable Input. Drive EN logic-high to enable boost mode, regardless of the logic level of TREN. Connect EN to ground or drive logic-low to allow TREN to select either True Shutdown or track mode. See Table 1. |

| C1  | GND1 | Ground. Connect GND_ to a large ground plane. GND1 and GND2 should be shorted together                                                                                                                          |

| C2  | GND2 | directly under the IC.                                                                                                                                                                                          |

| C3  | TREN | Track Enable Input. Drive TREN logic-high to enable track mode. Connect TREN to ground or drive logic-low to place the IC in True Shutdown. See Table 1.                                                        |

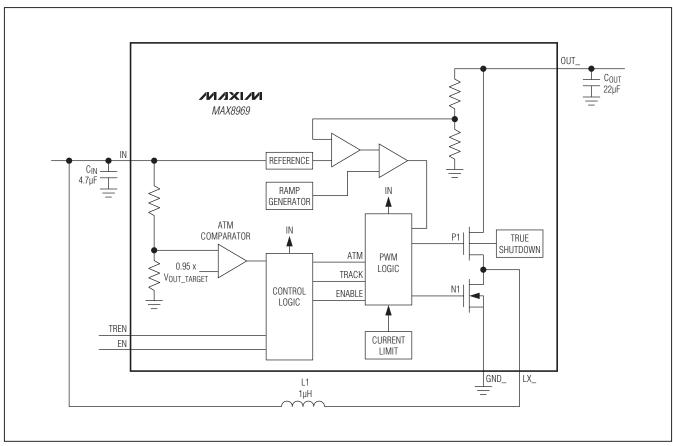

Figure 1. Functional Diagram

### **Detailed Description**

The MAX8969 is a step-up DC-DC switching converter that utilizes a fixed-frequency PWM architecture with True Shutdown. With an advanced voltage-positioning control scheme and high 3MHz switching frequency, the IC is inexpensive to implement and compact, using only a few small easily obtained external components. Under light-load conditions, the IC switches only when needed, consuming only 45µA (typ) of quiescent current. The IC is highly efficient with an internal switch and synchronous rectifier. Shutdown typically reduces the quiescent current to 1µA (typ). Low quiescent current and high efficiency make this device ideal for powering portable equipment.

Internal soft-start limits inrush current to less than 720mA (typ), while output voltage is less than input voltage. Once output voltage approaches input voltage approaches input voltage after a brief delay, output voltage is boosted to its final value at a rate of approximately 25mV/µs.

During this period, as well as being limited by the voltage, ramp rate current is limited by the normal 2.6A boost mode current limit.

In boost mode, the step-up converter boosts to VOUT\_TARGET from battery input voltages ranging from 2.5V to VOUT\_TARGET. When the input voltage ranges from 0.95 x VOUT\_TARGET to 5.5V, the IC enters ATM and the output voltage approximately follows the input voltage. During boost mode, the input current limit is set to 2.6A to guarantee delivery of the rated out current (e.g., 1A output current when boosting from a 2.5V input supply to a 3.7V output).

#### **Control Scheme**

The step-up converter uses a load/line control scheme. The load/line control scheme allows the output voltage to sag under load, but prevents overshoot when the load is suddenly removed. The load/line control scheme reduces the total range of voltages reached during transients at the expense of DC output impedance.

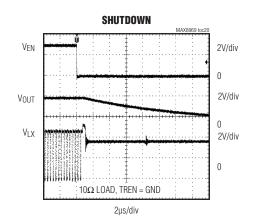

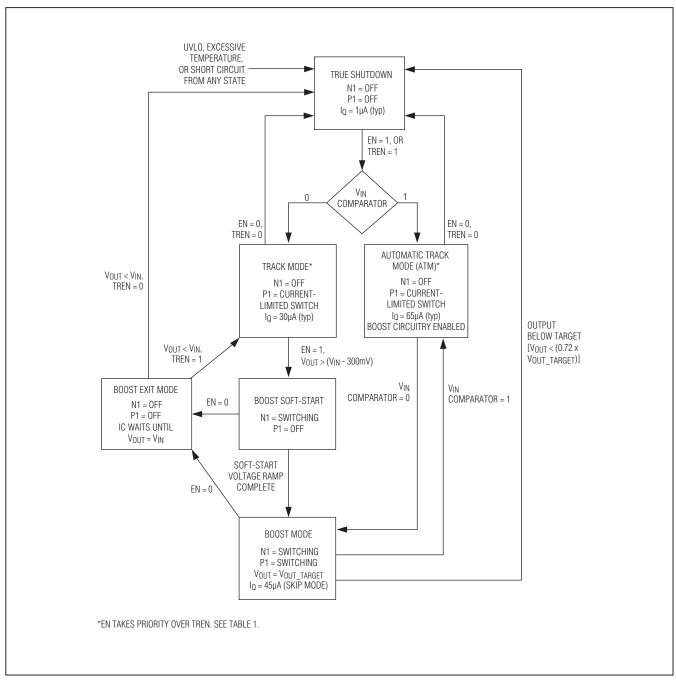

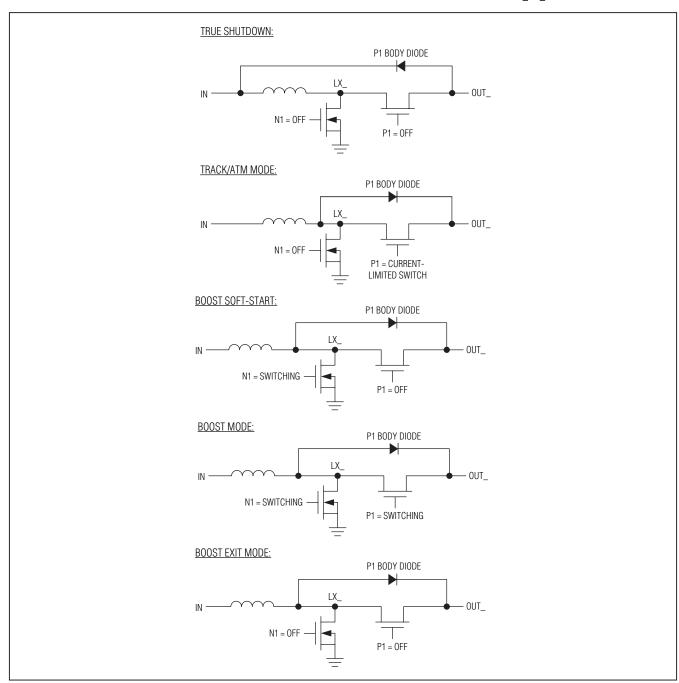

Figure 2. State Diagram

Figure 3. Modes of Operation

The IC is designed to operate with the input voltage range straddling its output voltage set point. Two techniques are used to accomplish this. The first technique is to activate ATM if the input voltage exceeds 95% of the output set point; see the *Automatic Track Mode (ATM)* section. The second technique is automatic frequency adjustment.

#### **Automatic Track Mode (ATM)**

ATM is entered when an internal comparator signals that the input voltage has exceeded the ATM threshold. The ATM threshold is 95% of the output voltage target. At this point, the IC enters ATM, with the pMOS switch turned on, regardless of the status of TREN. Note that EN must be high to enable ATM mode. This behavior is summarized in Table 1.

#### **Automatic Frequency Adjustment**

Automatic frequency adjustment is used to maintain stability if the input voltage is above 80% and below 95% of the output set point. Frequency adjustment is required because the n-channel has a minimum on-time of approximately 60ns. At 3MHz, this would lead to the p-channel having a maximum duty factor of 82%. With an input voltage more than 82% of the output set point, the p-channel's duty factor must be increased by reducing operating frequency either through cycle skipping or adjusting the clock's frequency. The IC adjusts its clock frequency rather than simply skipping cycles. This adjustment is done in two steps. The first step occurs if the input voltage exceeds approximately 83% of the output voltage and reduces clock speed to approximately 1.6MHz. The second step occurs if the input voltage is greater than output voltage less 460mV. If this condition is met, clock frequency is reduced to approximately 1MHz. Frequency adjustment allows the converter to operate at a known frequency under all conditions.

#### **Fault Protection**

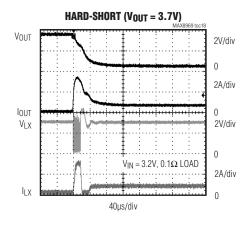

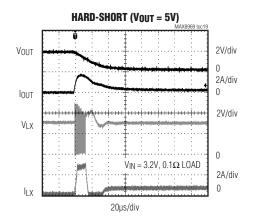

In track, ATM, and boost modes, the IC has protection against overload and overheating.

- In track and ATM, current is limited to prevent excessive inrush current during soft-start and to protect against overload conditions. If the die temperature exceeds +165°C in track/ATM, the switch turns off until the die temperature has cooled to +145°C.

- In boost mode, during each 3MHz switching cycle, if the inductor current exceeds 2.6A, the n-channel MOSFET is shut off and the p-channel MOSFET is switched on. The end result is that LX\_ current is regulated to 2.6A or less. A 2.6A inductor current is a large enough current to guarantee a 1A output load current under all intended operating conditions. The IC can operate indefinitely while regulating the inductor current to 2.6A or less.

However, if a short circuit or extremely heavy load is applied to the output, the output voltage decreases since the inductor current is limited to 2.6A.

If the output voltage decreases to less than 72% of the regulation voltage target (i.e., 2.8V with VOUT\_TARGET of 3.7V), a short circuit is assumed, and the IC returns to the shutdown state. The IC then attempts to start up if the output short is removed. Even if the output short persists indefinitely, the IC thermal protection ensures that the die is not damaged.

#### **True Shutdown**

During operation in boost mode, the p-channel MOSFET prevents current from flowing from OUT\_ to LX\_. In all other modes of operation, it is desirable to block current flowing from LX\_ to OUT\_. True Shutdown prevents current from flowing from LX\_ to OUT\_ while the IC is shut down by reversing the internal body diode of the p-channel MOSFET. This feature is also active during track/ATM to allow current limit to function as anticipated.

Upon leaving boost mode, the p-channel MOSFET continues to prevent current from flowing from OUT\_ to LX\_ until OUT\_ and IN are approximately the same voltage. After this condition has been met, track/ATM and shutdown operate normally.

**Table 1. Modes of Operation**

| V <sub>IN</sub> COMPARATOR | EN | TREN | MODE OF OPERATION |

|----------------------------|----|------|-------------------|

| X                          | 0  | 0    | True Shutdown     |

| X                          | 0  | 1    | Track             |

| 0                          | 1  | X    | Boost             |

| 1                          | 1  | X    | ATM               |

X = Don't care.

#### **Thermal Considerations**

In most applications, the IC does not dissipate much heat due to its high efficiency. But in applications where the IC runs at high ambient temperature with heavy loads, the heat dissipated may cause the temperature to exceed the maximum junction temperature of the part. If the junction temperature reaches approximately +165°C, the thermal overload protection is activated.

The maximum power dissipation depends on the thermal resistance of the IC package and circuit board. The power dissipated (PD) in the device is:

$$P_D = P_{OUT} \times (1/\eta - 1)$$

where  $\eta$  is the efficiency of the converter and POUT is the output power of the step-up converter. The maximum allowed power dissipation is:

$$PMAX = (TJMAX - TA)/\theta JA$$

where ( $T_{JMAX}$  -  $T_A$ ) is the temperature difference between the IC's maximum rated junction temperature and the surrounding air, and  $\theta_{JA}$  is the thermal resistance of the junction through the PCB, copper traces, and other materials to the surrounding air.

### \_Applications Information

#### **Step-Up Inductor Selection**

Due to the small size of the recommended capacitor, the inductor's value is limited to approximately 1 $\mu$ H. Inductors of approximately 1 $\mu$ H guarantee stable operation of the converter with capacitance as small as 8 $\mu$ F (actual) present on the converter's output. If the inductor's value is reduced significantly below 1 $\mu$ H, ripple can become excessive.

#### **Output Capacitor Selection**

An output capacitor (COUT) is required to keep the output-voltage ripple small and to ensure regulation loop stability. The output capacitor must have low impedance at the switching frequency. Ceramic capacitors are highly recommended due to their small size and low ESR. Ceramic capacitors with X5R or X7R temperature characteristics generally perform well. One  $22\mu\text{F}$  (with a minimum actual capacitance of  $6\mu\text{F}$  under operating conditions) is recommended. This capacitor along with an additional  $10\mu\text{F}$  of bypass capacitance, associated with the load, guarantee proper performance of the IC. The minimum combined capacitance is required to be  $8\mu\text{F}$  or larger. These capacitors can be found with case size 0603 or larger.

#### **Input Capacitor Selection**

The input capacitor ( $C_{IN}$ ) reduces the current peaks drawn from the battery or input power source. The impedance of  $C_{IN}$  at the switching frequency should be kept very low. Ceramic capacitors with X5R or X7R temperature characteristics are highly recommended due to their small size, low ESR, and small temperature coefficients. Note that some ceramic dielectrics exhibit large capacitance and ESR variation with temperature and DC bias. Ceramic capacitors with Z5U or Y5V temperature characteristics should be avoided. A  $4.7\mu F$  input capacitor is recommended for most applications. This assumes that the input power source has at least  $22\mu F$  of additional capacitance near the IC. For optimum noise immunity and low input-voltage ripple, the input capacitor value can be increased.

#### **Recommended PCB Layout and Routing**

Poor layout can affect the IC performance, causing electromagnetic interference (EMI) and electromagnetic compatibility (EMC) performance, ground bounce, and voltage losses. Poor layout can also affect regulation and stability.

A good layout is implemented using the following rules:

- Place the inductor, input capacitor, and output capacitor close to the IC using short traces. These components carry high switching frequencies and large traces act like antennas. The output capacitor placement is the most important in the PCB layout and should be placed directly next to the IC. The inductor and input capacitor placement are secondary to the output capacitor's placement but should remain close to the IC.

- Route the output voltage path away from the inductor and LX\_ switching node to minimize noise and magnetic interference.

- Maximize the size of the ground metal on the component side to help with thermal dissipation. Use a ground plane with several vias connecting to the component-side ground to further reduce noise interference on sensitive circuit nodes.

Refer to the MAX8969 Evaluation Kit for more details.

**Chip Information**

PROCESS: BICMOS

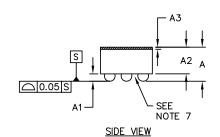

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to www.maxim-ic.com/packages. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | CKAGE TYPE PACKAGE CODE OUTLINE NO. |                | LAND PATTERN NO.               |  |

|--------------|-------------------------------------|----------------|--------------------------------|--|

| 9 WLP        | W91B1+7                             | <u>21-0459</u> | Refer to Application Note 1891 |  |

| C  | DMMON DIMENSIONS |

|----|------------------|

| Α  | 0.64±0.05        |

| A1 | 0.19±0.03        |

| A2 | 0.45 REF         |

| А3 | 0.025 BASIC      |

| b  | ø0.27±0.03       |

| D1 | 0.80 BASIC       |

| E1 | 0.80 BASIC       |

| е  | 0.40 BASIC       |

| SD | 0.00 BASIC       |

| SE | 0.00 BASIC       |

|           | Ę    |      |      | )    | DEPOPULATED |

|-----------|------|------|------|------|-------------|

| PKG. CODE | MIN  | MAX  | MIN  |      | BUMPS       |

| W91B1+7   | 1.22 | 1.30 | 1.22 | 1.30 | NONE        |

| W91C1+1   | 1.56 | 1.63 | 1.38 | 1.45 | NONE        |

# SD

BOTTOM VIEW

#### NOTES:

- Terminal pitch is defined by terminal center to center value.

Outer dimension is defined by center lines between scribe lines.

All dimensions in millimeters.

- 4. Marking shown is for package orientation reference only.

5. Tolerance is ± 0.02mm unless specified otherwise.

6. All dimensions apply to PbFree (+) package codes only.

7. Front—side finish can be either Black or Clear.

PACKAGE OUTLINE 9 BUMPS, WLP PKG. 0.4mm PITCH

IDOCUMENT CONTROL NO. ADDROVAL 21 - 0459

-DRAWING NOT TO SCALE-

В

### **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 9/11          | Initial release | _                |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.