# **5 VOLT CACHE DATA/LATC**

# **CACHE DATA** SRAM

## SINGLE 8K x 18 SRAM, DUAL 4K x 18 SRAM

CONFIGURABLE CACHE DATA SRAM

### **FEATURES**

- Operates as two 4K x 18 SRAMs with common addresses and data; also configurable as a single 8K x 18 SRAM

- Built-in input address latches (A0-A12)

- Separate upper and lower Byte Select

- Fast access times: 20, 25 and 35ns allow operation with 40, 33 and 25 MHz microprocessor systems

- Fast OE: 8ns

- Directly interfaces with the Intel 82385 cache controller as well as other 80386 and 80486 cache memory controllers

- Parity bits provided for large cache applications such as secondary cache for the 80486 microprocessors

| OPTIONS                                                            | MARKING    |

|--------------------------------------------------------------------|------------|

| • Timing 20ns access (40 MHz)                                      | -20        |

| 25ns access (33 MHz)<br>35ns access (25 MHz)                       | -25<br>-35 |

| <ul><li>Packages</li><li>52-pin PLCC</li><li>52-pin PQFP</li></ul> | EJ<br>LG   |

Part Number Example: MT56C3818EJ-25

### GENERAL DESCRIPTION

The MT56C3818 is one of a family of fast SRAM cache memories. It employs a high-speed, low-power design using a four-transistor memory cell. It is fabricated using double-layer polysilicon, double-layer metal CMOS technology.

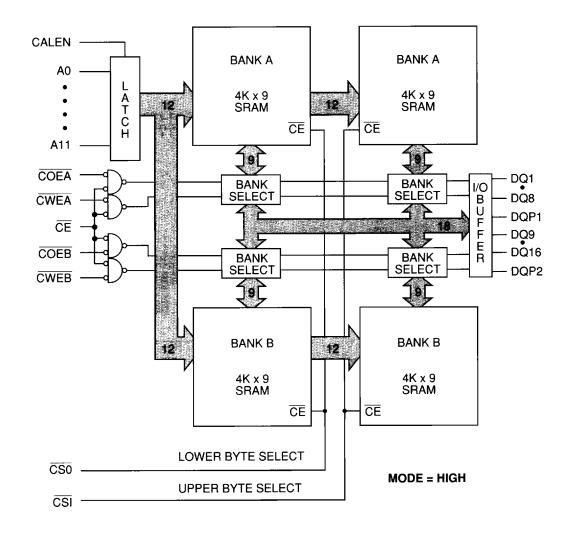

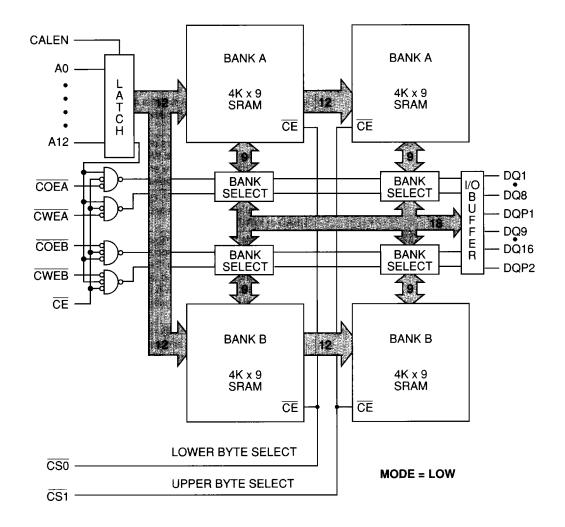

The MT56C3818 is a highly integrated cache data memory building block. It easily interfaces with cache controllers for the Intel 80386 in either the DIRECT MAPPED or TWO-WAY SET ASSOCIATIVE mode. A mode control pin (MODE) determines the configuration of the memory. When this pin is held LOW, the device functions as an 8Kword by 18-bit SRAM. When the mode pin is HIGH, the device is configured as a dual 4K-word by 18-bit SRAM.

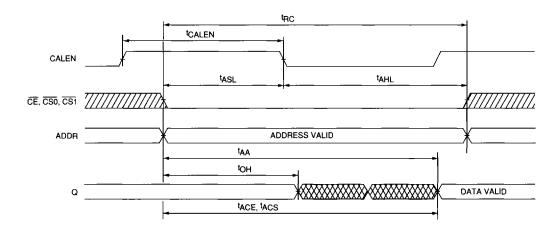

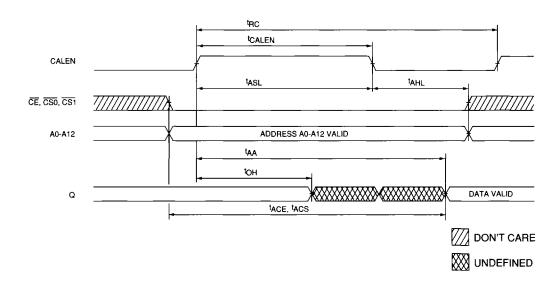

Input addresses are latched in the on-chip register on the negative edge of the CALEN signal. This register is functionally equivalent to a 74LS373.

The memory functions are controlled by the chip select  $(\overline{CE}, \overline{CSO})$  and  $\overline{CSI}$ , output enable  $(\overline{COEA})$  and  $\overline{COEB}$  and write enable ( $\overline{\text{CWEA}}$  and  $\overline{\text{CWEB}}$ ) signals.

In either DIRECT MAPPED (direct) or TWO-WAY SET ASSOCIATIVE (dual) operational modes,  $\overline{\text{CE}}$  is a global chip enable, while CSO and CSI control lower and upper byte selection for READ and WRITE operations.

Outputs are enabled on a HIGH-to-LOW transition of COEA or COEB. In the dual mode, bank "A" or bank "B" may be enabled. In the direct mode, COEA and COEB should be connected together externally and used as a single output enable. Alternately, <del>COEA</del> or <del>COEB</del> can be tied LOW externally, allowing the other signal to control the outputs.

Write enable is activated on a HIGH-to-LOW transition of CWEA or CWEB. In the dual mode, data may be written to bank "A" or bank "B". In the direct mode, TWEA and **CWEB** should be connected together externally and used as a single write enable. Alternately, CWEA or CWEB can be tied LOW externally, allowing the other signal to control the write function.

The MT56C3818 operates from a +5V power supply and all inputs and outputs are fully TTL compatible.

### **FUNCTIONAL BLOCK DIAGRAM**

# **DUAL 4K x 18** (TWO-WAY SET ASSOCIATIVE)

# 5 VOLT CACHE DATA/LATCHED SRAN

### **FUNCTIONAL BLOCK DIAGRAM**

8K x 18 (DIRECT MAP)

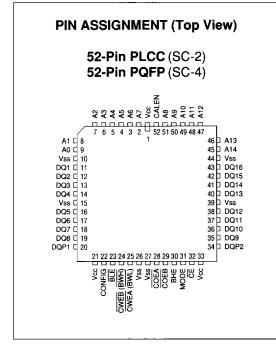

### **PIN DESCRIPTIONS**

|   | PLCC PIN<br>Number(s)                                                | SYMBOL       | TYPE             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|---|----------------------------------------------------------------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 8, 7, 6, 5, 4, 3, 2,<br>51, 50, 49, 48, 47                           | A0-A11       | Input            | Address Inputs: These inputs are clocked by CALEN and stored in a latch.                                                                                                                                                                                                                                                                                                                         |

|   | 46                                                                   | A12          | Input            | Address Input: This input is the high order-address bit in the direct 8K x 18 configuration. It is not used in the dual 4K x 18 configuration. This input is latched by the negative edge of CALEN.                                                                                                                                                                                              |

|   | 52                                                                   | CALEN        | Input            | Address Latch Enable: When CALEN is HIGH, the latch is transparent. The negative edge latches the current address inputs (A0-A12).                                                                                                                                                                                                                                                               |

| - | 31                                                                   | MODE         | Input            | Mode Select: This controls the device configuration. When this pin is tied HIGH, the device is in the dual 4K x 18 configuration. When the pin is tied LOW, the device is configured as an 8K x 18 SRAM.                                                                                                                                                                                         |

|   | 23, 30                                                               | CSO, CS1     | Input            | Chip Selects: These signals are used to select the upper and lower bytes for both READ and WRITE operations. When CS0 is LOW, DQ1-DQ8 and DQP1 are enabled. When CS1 is LOW, DQ9-DQ16 and DQP2 are enabled.                                                                                                                                                                                      |

|   | 45                                                                   | CE           | Input            | Chip Enable: When $\overline{\text{CE}}$ is LOW, the device is enabled. It is a global control signal that activates both bank A and bank B for READ or WRITE operations.                                                                                                                                                                                                                        |

|   | 28, 29                                                               | COEA, COEB   | Input            | Output Enable: In the dual configuration, the signal that is LOW enables bank A or B. Simultaneous LOW assertion will deselect both banks. In the direct mode, these signals should be externally connected and, when asserted LOW, allow A12 to determine which memory bank is enabled. Alternately, COEA or COEB can be tied LOW externally, allowing the other signal to control the outputs. |

|   | 25, 24                                                               | CWEA, CWEB   | Input            | Write Enable: In the dual configuration, the signal that is LOW enables a data write to the addressed memory location. In the direct mode, these signals should be externally connected and, when asserted LOW, allow A12 to determine which memory bank is written. Alternately, CWEA or CWEB can be tied LOW externally, allowing the other signal to control the write function.              |

|   | 11, 12, 13, 14, 16,<br>17, 18, 19, 35, 36, 37,<br>38, 40, 41, 42, 43 | DQ1-DQ16     | Input/<br>Output | SRAM Data I/O: lower byte is DQ1-DQ8; upper byte is DQ9-DQ16.                                                                                                                                                                                                                                                                                                                                    |

|   | 20, 34                                                               | DQP1<br>DQP2 | Input/<br>Output | Parity Data I/O: DQP1 is the parity bit for the lower byte. DQP2 is the parity bit for the upper byte.                                                                                                                                                                                                                                                                                           |

|   | 1, 21, 22, 32, 33                                                    | Vcc          | Supply           | Power Supply: +5V ±5%                                                                                                                                                                                                                                                                                                                                                                            |

| 9 | , 10, 15, 26, 27, 39, 44                                             | Vss          | Supply           | Ground: GND                                                                                                                                                                                                                                                                                                                                                                                      |

### **TRUTH TABLE**

DUAL 4K x 18 (MODE PIN = HIGH)

| OPERATION                              | CE | CSO | CS1 | COEA | COEB | CWEA | CWEB |

|----------------------------------------|----|-----|-----|------|------|------|------|

| Outputs High-Z, WRITE disabled         | Н  | Х   | Х   | Х    | Х    | Х    | X    |

| Outputs High-Z, WRITE disabled         | Х  | Н   | Н   | X    | Х    | X    | Х    |

| Outputs High-Z                         | Х  | Х   | Х   | Н    | Н    | Х    | X    |

| Outputs High-Z                         | Х  | Х   | Х   | L    | L    | X    | Х    |

| READ DQ1-DQ8,DQP1 bank A               | L  | L   | Н   | L    | Н    | Н    | Н    |

| READ DQ1-DQ8, DQP1 bank B              | L  | L   | Н   | Н    | L    | Н    | Н    |

| READ DQ9-DQ16, DQP2 bank A             | L  | Н   | L   | L    | Н    | Н    | Н    |

| READ DQ9-DQ16, DQP2 bank B             | L  | Н   | L   | Н    | L    | Н    | Н    |

| READ DQ1-DQ16, DQP1, DQP2 bank A       | L  | L   | L   | L    | Н    | Н    | Н    |

| READ DQ1-DQ16, DQP1, DQP2 bank B       | L  | L   | L   | Н    | L    | Н    | Н    |

| WRITE DQ1-DQ8, DQP1 bank A             | L  | L   | Н   | Х    | Х    | L    | Н    |

| WRITE DQ1-DQ8, DQP1 bank B             | L  | L   | Н   | Х    | Х    | Н    | L    |

| WRITE DQ9-DQ16, DQP2 bank A            | L  | Н   | L   | Х    | Х    | L    | Н    |

| WRITE DQ9-DQ16, DQP2 bank B            | L  | Н   | L   | Х    | Х    | н    | L    |

| WRITE DQ1-DQ16, DQP1, DQP2 bank A      | L  | L   | L   | Х    | Х    | L    | Н    |

| WRITE DQ1 -DQ16, DQP1, DQP2 bank B     | L  | L   | L   | Х    | Х    | Н    | L    |

| WRITE DQ1-DQ8, DQP1 banks A & B        | L  | L   | Н   | ×    | Х    | L    | L    |

| WRITE DQ9-DQ16, DQP2 banks A & B       | L  | Н   | L   | Х    | Х    | L    | L    |

| WRITE DQ1-DQ16, DQP1, DQP2 banks A & B | L  | L   | L   | Х    | Х    | L    | L    |

NOTE:  $\overline{\text{CE}}$ , when taken inactive while  $\overline{\text{CWEA}}$  or  $\overline{\text{CWEB}}$  remain active, allows a chip-enable-controlled WRITE to be

performed.

### TRUTH TABLE

8K x 18 (MODE PIN = LOW)

| OPERATION                      | CE | CSO | CS1 | COEA | COEB | CWEA | CWEB |

|--------------------------------|----|-----|-----|------|------|------|------|

| Outputs High-Z, WRITE disabled | Н  | X   | Х   | ×    | X    | ×    | ×    |

| Outputs High-Z, WRITE disabled | Х  | Н   | Н   | Х    | X    | X    | Х    |

| Outputs High-Z                 | X  | Х   | Х   | Н    | Н    | X    | Х    |

| READ DQ1-DQ8, DQP1             | L  | L   | Н   | L    | L    | Н    | Н    |

| READ DQ9-DQ16, DQP2            | L_ | Н   | L   | L    | L    | Н    | Н    |

| READ DQ1-DQ16, DQP1, DQP2      | L  | L   | L   | L    | L    | Н    | Н    |

| WRITE DQ1-DQ8, DQP1            | L  | L   | Н   | X    | X    | L    | L    |

| WRITE DQ9-DQ16, DQP2           | L  | Н   | L   | Х    | Х    | L    | L    |

| WRITE DQ1-DQ16, DQP1, DQP2     | L  | L   | L   | X    | Х    | L    | L    |

NOTE:

- 1. CE, when taken inactive while CWEA and CWEB remain active, allows a chip-enable-controlled WRITE to be

- 2. COEA and COEB must both be LOW to enable outputs. However, one signal can be tied LOW externally, allowing the other signal to control the outputs. Similarly CWEA and CWEB must both be LOW to enable a WRITE cycle. Either CWEA or CWEB can be tied LOW externally, allowing the other signal to control the WRITE function.

# ■ 5 VOLT CACHE DATA/LATCHED SRAN

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on VCC Supply Relative to Vss | 1V to +7V |

|---------------------------------------|-----------|

| Storage Temperature                   |           |

| Power Dissipation (PLCC)              |           |

| Power Dissipation (PQFP)              | 1.2W      |

| Short Circuit Output Current          |           |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED DC OPERATING CONDITIONS**

$(0^{\circ}C \le T_{A} \le 70^{\circ}C; Vcc = 5V \pm 5\%)$

| DESCRIPTION            | CONDITIONS                              | SYMBOL | MIN  | MAX      | UNITS | NOTES |

|------------------------|-----------------------------------------|--------|------|----------|-------|-------|

| Power Supply Voltage   |                                         | Vcc    | 4.75 | 5.25     | ٧     |       |

| Input High Voltage     |                                         | VIH    | 2.2  | Vcc +0.3 | V     | 1     |

| Input Low Voltage      |                                         | VIL    | -0.3 | 0.8      | V     | 1, 2  |

| Input Leakage Current  | Vin = GND to Vcc                        | ILı    | -5   | 5        | μA    |       |

| Output Leakage Current | Vi/o = GND to Vcc<br>Output(s) Disabled | ILo    | -5   | 5        | μA    |       |

| Output Low Voltage     | loL = 4.0mA                             | Vol    |      | 0.4      | V     | 1     |

| Output High Voltage    | Iон = -1.0mA                            | Vон    | 2.4  |          | V     | 1     |

| DESCRIPTION                                                    | CONDITIONS                          | SYMBOL | TYP | MAX | UNITS | NOTES |

|----------------------------------------------------------------|-------------------------------------|--------|-----|-----|-------|-------|

| Power Supply Current:<br>Average Operating Current             | 100% Duty Cycle<br>VIN = GND to Vcc | lcc1   | 130 | 220 | mA    |       |

| Power Supply Current:<br>Average Operating Current             | 50% Duty Cycle VIN = GND to Vcc     | Icc2   | 70  | 120 | mA    |       |

| Average Operating Current  Power Supply Current:  CMOS Standby |                                     | ISB    | 2.0 | 20  | mA    |       |

### CAPACITANCE

| DESCRIPTION        | CONDITIONS                       | SYMBOL | MAX | UNITS | NOTES |

|--------------------|----------------------------------|--------|-----|-------|-------|

| Input Capacitance  | T <sub>A</sub> = 25°C; f = 1 MHz | Cı     | 6   | pF    | 3     |

| Output Capacitance | Vcc = 5V                         | Cı/o   | 6   | рF    | 3     |

### PQFP THERMAL CONSIDERATIONS

| DESCRIPTION                                                  | CONDITIONS | SYMBOL | MAX | UNITS | NOTES |

|--------------------------------------------------------------|------------|--------|-----|-------|-------|

| Thermal resistance – Junction to Ambient<br>Suspended in Air | Still Air  | ۵JA    | 100 | °C/W  | _     |

| Thermal resistance – Junction to Case                        |            | ٥JC    | 45  | °C/W  |       |

| Thermal resistance mounted on 2" x 3" PC board               |            | ΑLo    | 70  | °C/W  |       |

| Maximum Case Temperature                                     |            | TC     | 110 | °C    |       |

# 5 VOLT CACHE DATA/LATCHED SRAN

### **ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS** $(0^{\circ}C \le T_A \le +70^{\circ}C, Vcc = 5V \pm 5\%)$

| BEGGRINTION                                          |                    | -:  | 20       | -25 |          | -35 |                                        |       |       |

|------------------------------------------------------|--------------------|-----|----------|-----|----------|-----|----------------------------------------|-------|-------|

| DESCRIPTION                                          | SYM                | MIN | MAX      | MIN | MAX      | MIN | MAX                                    | UNITS | NOTES |

| READ Cycle                                           |                    |     |          |     |          |     |                                        |       |       |

| READ cycle time                                      | <sup>t</sup> RC    | 20  |          | 25  |          | 35  |                                        | ns    | 4, 5  |

| Address access time (A0-A12)                         | †AA                |     | 20       |     | 25       |     | 35                                     | ns    |       |

| Chip Enable access time                              | <sup>t</sup> ACE   |     | 20       |     | 20       |     | 25                                     | ns    |       |

| Chip Select access time                              | tACS               |     | 20       |     | 25       |     | 35                                     | ns    |       |

| Output Enable access time                            | <sup>†</sup> AOE   |     | . 8      |     | 10       |     | 13                                     | ns    |       |

| Output hold from address change                      | tОН                | 3   |          | 3   | _        | 3   |                                        | ns    |       |

| Chip Select to output Low-Z                          | tLZCS              | 3   |          | 3   |          | 3   |                                        | ns    |       |

| Output Enable to output Low-Z                        | tLZOE              | 2   |          | 2   |          | 2   |                                        | ns    |       |

| Chip deselect to output High-Z                       | †HZCS              |     | 15       |     | 15       |     | 25                                     | ns    | 6     |

| Output disable to output High-Z                      | THZOE              |     | 10       |     | 10       |     | 14                                     | ns    | 6     |

| Address Latch Enable pulse width                     | <sup>1</sup> CALEN | 8   |          | 8_  |          | 10  |                                        | ns    |       |

| Address setup to latch LOW                           | †ASL               | 4   |          | 4   |          | 6_  |                                        | ns    |       |

| Address hold from latch LOW                          | tAHL.              | 5   |          | 5   |          | 5   | L                                      | ns    |       |

| WRITE Cycle                                          |                    |     |          |     |          |     |                                        | r     |       |

| WRITE cycle time                                     | †WC                | 20  |          | 25  |          | 35  | L                                      | ns    |       |

| Address valid to end of write                        | tAW                | 15  |          | 18  |          | 25  |                                        | ns    |       |

| Chip Select to end of write                          | ţCM.               | 15  |          | 18  |          | 25  | <u> </u>                               | ns    |       |

| Data valid to end of write                           | tDW                | 10  |          | 10  |          | 10  | ļ                                      | ns    |       |

| Data hold from end of write                          | tDH _              | 0   |          | 0   |          | 0   | _                                      | ns    |       |

| Write Enable output in High-Z                        | tHZWE              |     | 12       |     | 15_      |     | 15                                     | ns    | 6     |

| Write disable to output in Low-Z                     | tLZWE              | 3   |          | 3   |          | 3   | <u> </u>                               | ns    | ļ     |

| WRITE pulse width                                    | †WP                | 15  |          | 18  |          | 25  | ļ                                      | ns    |       |

| CE pulse width (during Chip Enable controlled write) | tCP_               | 15  |          | 18  | ļ        | 25  | L                                      | ns    |       |

| Address setup time                                   | tAS                | 0   |          | 0   | ļ        | 0_  | <b>↓</b>                               | ns    |       |

| WRITE recovery time                                  | †WR                | 0   | L        | 0   | L        | 0_  | ↓                                      | ns    | 1     |

| Address Latch Enable pulse width                     | <sup>t</sup> CALEN | 8   | <u> </u> | 8   |          | 10  | $oldsymbol{oldsymbol{oldsymbol{eta}}}$ | ns    |       |

| Address setup to latch LOW                           | †ASL_              | 4   | ļ        | 4   | <u> </u> | 6   |                                        | ns    |       |

| Address hold from latch LOW                          | <sup>t</sup> AHL   | 5   | L        | 5   | L        | 5   | L                                      | ns    |       |

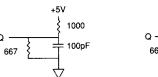

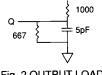

### **AC TEST CONDITIONS**

| Input pulse levelsVss to 3.0V |  |  |  |  |

|-------------------------------|--|--|--|--|

| Input rise and fall times     |  |  |  |  |

| Input timing reference levels |  |  |  |  |

| Output reference levels       |  |  |  |  |

| Output load                   |  |  |  |  |

Fig. 1 OUTPUT LOAD **EQUIVALENT**

+5٧

Fig. 2 OUTPUT LOAD **EQUIVALENT**

### NOTES

- All voltages referenced to Vss (GND).

- 2. -3V for pulse width < tRC/2.

- 3. This parameter is sampled.

- 4. **CWE** is HIGH for a READ cycle.

- 5. All READ cycle timings are referenced from the last valid address to the first transitioning address.

- tHZCS, tHZOE, and tHZWE are specified with CL = 5pF as in Fig. 2. Transition is measured ±500mV from steady state voltage.

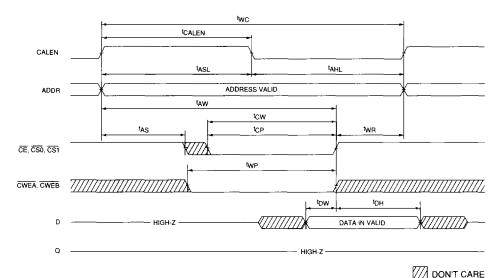

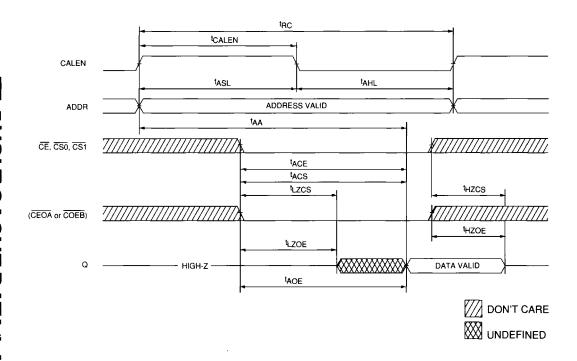

### **READ CYCLE NO. 1**

$\frac{\text{(Address Controlled)}}{\text{CWEA}} = \frac{\text{CWEB}}{\text{CWEB}} = \text{Viii}; \frac{\text{COEA}}{\text{COEA}} \text{ and/or } \frac{\text{COEB}}{\text{COEB}} = \text{Viii}$

### **READ CYCLE NO. 2**

(CALEN Controlled)

CWEA = CWEB = VIH; COEA and/or COEB = VIL

## READ CYCLE NO. 3 CWEA = CWEB = VIH

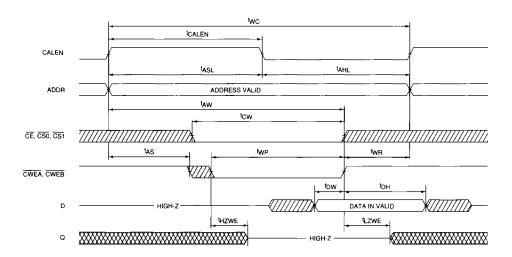

## WRITE CYCLE NO. 1 (Write Enable Controlled)

# WRITE CYCLE NO. 2 (Chip Select Controlled)