# **HIGH SPEED CMOS GATE ARRAYS**

#### **■ DESCRIPTION**

The S-MOS SLA10000 series is a channel-less gate array manufactured on S-MOS' state-of-the-art 0.8 micron double-metal SiCMOS process. The series consists of 11 arrays ranging from 9,000 to 101,800 usable gates and from 128 to 432 I/O. The SLA10000 series has been tailored for high performance designs with typical gate delays of .3 nanoseconds. Additionally, high-speed silicon efficient RAM functions are offered as customized cells. The series has a selectable output drive capability of 2, 6, 12 or 24 milliamps (two output buffers can be used in parallel to obtain 48 milliamps). The arrays are offered in a wide variety of packages including 64 – 256 pin quad flat packs. The SLA10000 series is supported by S-MOS' own design system with NavNet schematic editor, as well as most major CAD systems including Mentor, Valid, Viewlogic, FutureNet, Synopsys/ Verilog and OrCAD.

### **#** FEATURES

- .76 micron drawn channel length (N-channel)

- Very high speed: tpd (2-input power NAND)(typ, FO = 2 & 2mm AL) = 0.3 ns/gate

- High Drive

- 24mA for a single output

- 48 mA for parallel outputs

- Low gate—to—pads ratio for high pin count applications

- Megacells compatible

- Fully migratable to S-MOS standard cell families

## **■ PRODUCT CONFIGURATION**

| Array   | Raw    | Usable | Total  |           |

|---------|--------|--------|--------|-----------|

| Allay   | Gates  | Min    | Max    | # of Pads |

| SLA1020 | 20216  | 9097   | 11523  | 128       |

| SLA1024 | 24424  | 10746  | 13922  | 140       |

| SLA1029 | 29120  | 12521  | 16016  | 152       |

| SLA1034 | 34138  | 14338  | 18776  | 164       |

| SLA1039 | 39644  | 16650  | 21804  | 176       |

| SLA1049 | 49489  | 20290  | 26230  | 196       |

| SLA1060 | 60653  | 24868  | 32146  | 216       |

| SLA1073 | 73353  | 29342  | 39000  | 236       |

| SLA1081 | 81320  | 32528  | 41000  | 248       |

| SLA1152 | 152256 | 53290  | 68515  | 336       |

| SLA1255 | 254743 | 89160  | 101897 | 432       |

NOTE: All arrays have 4 power / GND pads included within total pad count.

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol | Limits              | Unit |

|---------------------|--------|---------------------|------|

| DC Supply Voltage   | VDD    | Vss -0.3 to 7.0     | V    |

| Input Voltage       | Vin    | Vss -0.3 to VDD+0.3 | V    |

| Output Voltage      | Vouт   | Vss-0.3 to VDD+0.3  | V    |

| Storage Temperature | Тѕтс   | -65 to +150         | °C   |

# ■ RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol | Min  | Тур | Max  | Unit |

|-----------------------|--------|------|-----|------|------|

| Supply Voltage        | VDD    | 4.50 | 5.0 | 5.50 | V    |

| Input Voltage         | Vin    | Vss  |     | VDD  | ٧    |

| Operating Temperature | Topr   | -20  |     | 85   | °C   |

# ■ PERFORMANCE CHARACTERISTICS (Under Recommended Operating Conditions)

| Symbol | Parameter                        | Conditions     | Min       | Тур | Max       | Units    |

|--------|----------------------------------|----------------|-----------|-----|-----------|----------|

|        | Low level input voltage          |                |           |     |           |          |

| VIL    | CMOS Level                       |                | }         |     | 1.0       | V        |

|        | TTL Level                        |                |           |     | 0.8       | ٧        |

|        | High level input voltage         |                |           |     |           |          |

| Vін    | CMOS Level                       |                | 3.5       |     |           | V        |

|        | TTL Level                        |                | 2.0       |     |           | V        |

|        | Positive going threshold voltage |                |           |     |           |          |

| VT+    | CMOS Schmitt Trigger             | VDD = 5.0      |           |     | 4.0       | V        |

|        | TTL Schmitt Trigger              | $V_{DD} = 5.0$ |           |     | 3.0       | ٧        |

|        | Negative going threshold voltage |                |           |     | 1         |          |

| VT-    | CMOS Schmitt Trigger             | VDD = 5.0      | 0.8       |     |           | ٧        |

|        | TTL Schmitt Trigger              | $V_{DD} = 5.0$ | 0.6       |     |           | V        |

|        | Hystereisis voltage              |                |           |     |           |          |

| Vн     | CMOS Schmitt Trigger             | $V_{DD} = 5.0$ | 0.3       |     |           | V        |

|        | TTL Schmitt Trigger              | $V_{DD} = 5.0$ | 0.1       |     |           | ٧        |

|        | Low level input current          | Vin = Vss      |           |     |           |          |

| Iι∟    | ·                                | No pull-up     |           |     | 1.0       | μA       |

|        | High level input current         | VIN = VDD      |           |     |           |          |

| hH     |                                  | No pull-up     |           |     | 1.0       | μΑ       |

|        | Low level output voltage         |                |           |     |           |          |

|        | LOT + OSC                        | Iol = 50μA     |           |     | Vss +0.4V | V        |

| Vol    | Type 1                           | lot = 2mA      |           |     | Vss +0.4V | V        |

|        | Type 2                           | IoL = 6mA      |           |     | Vss +0.4V | V        |

|        | Type 3                           | IoL = 12mA     |           |     | Vss +0.4V | V        |

|        | Type 4                           | IoL = 24mA     |           |     | Vss +0.4V | v        |

|        | High level output voltage        |                |           | •   | 1         |          |

|        | LOT + OSC                        | Іон = 50μΑ     | VDD -0.4V |     |           | V        |

| Vон    | Type 1                           | юн = 1mA       | VDD -0.4V |     |           | V        |

|        | Type 2                           | юн = 2mA       | VDD -0.4V |     |           | v        |

|        | Type 3                           | юн = 4mA       | VDD -0.4V |     |           | v        |

|        | Type 4                           | юн = 8mA       | VDD -0.4V |     |           | v        |

|        | Pull up resistor                 | VDD = 5.0      | 100 0111  |     |           | ΚΩ       |

| Reu    | Type 1                           | 100 = 0.0      | 25        |     | 100       |          |

| ᢏ      | Type 2                           |                | 50        |     | 200       |          |

|        | Type 3                           |                | 100       |     | 400       |          |

|        | Pull down resistor               | VDD = 5.0      |           |     | +00       | ΚΩ       |

| RPD    | Type 1                           | ¥50 = 5.0      | 25        |     | 100       | 1775     |

| 1,,,,  | Type 2                           |                | 50        |     | 200       |          |

|        | Type 3                           |                | 100       |     | 400       |          |

| loz    | Tri-state leakage current        |                | 100       |     | 1.0       | μ.Λ      |

| Cin    | Input Capacitance                |                | -         | 4   | 1.0       | μA<br>pF |

| COUT   | Output Capacitance               |                |           | 6   | +         | •        |

| CBID   | Bi-directional pad capacitance   |                |           | 10  | +         | pF<br>pF |

| ODID   | Di-directional pad capacitance   |                |           | 10  |           | þΓ       |

## **■ MACRO LIBRARY**

| Function                                                          | Coll Name            | Cotoo    |

|-------------------------------------------------------------------|----------------------|----------|

| SIMPLE GATES                                                      | Cell Name            | Gates    |

| 2-INPUT NAND GATE                                                 | NA2                  | 1        |

| 3-INPUT NAND GATE                                                 | NA3                  | 2        |

| 4-INPUT NAND GATE                                                 | NA4                  | 2        |

| 2-INPUT NOR GATE                                                  | NO2                  | 1        |

| 3-INPUT NOR GATE                                                  | NO3                  | 2        |

| 4-INPUT NOR GATE                                                  | NO4                  | 2        |

| 3-INPUT AND GATE                                                  | A3                   | 2        |

| 6-INPUT AND GATE                                                  | A6                   | 4        |

| 8-INPUT AND GATE                                                  | A8                   | 5        |

| 3-INPUT OR GATE                                                   | 03                   |          |

| 6-INPUT OR GATE                                                   | 06                   | 2<br>4   |

| 8-INPUT OR GATE                                                   |                      | -        |

| EXCLUSIVE OR GATE                                                 | O8<br>EXO            | <u>5</u> |

| EXCLUSIVE NOR GATE                                                |                      | 3        |

| COMPLEX GATES                                                     | EXN                  | <u> </u> |

| 2-AND 2-WIDE 3-INPUT NOR GATE                                     | ANIOO                |          |

| 3-AND 2-WIDE 4-INPUT NOR GATE                                     | AN23                 | 2        |

| 2-AND 2-WIDE 4-INPUT NOR GATE                                     | AN14                 | 2        |

| 2-AND 3-WIDE 4-INPUT NOR GATE                                     | AN24                 | 2 2      |

| 2-AND 3-WIDE 6-INPUT NOR GATE                                     | AN34                 |          |

| 2-AND 2-WIDE 3-INPUT OR GATE                                      | AN36                 | 5        |

| 3-AND 2-WIDE 6-INPUT OR GATE                                      | AO23                 | 2        |

| 4-AND 2-WIDE 8-INPUT OR GATE                                      | AO26                 | 4        |

| 2-AND 2-WIDE 3-INPUT NAND GATE                                    | AO28                 | 5        |

| 3-AND 2-WIDE 4-INPUT NAND GATE                                    | ON23                 | 2        |

| 2-AND 2-WIDE 4-INPUT NAND GATE                                    | ON14                 | 2        |

| 2-AND 3-WIDE 4-INPUT NAND GATE                                    | ON24                 | 2        |

|                                                                   | ON34                 | 2        |

| 2-AND 2-OR 2-WIDE 4-INPUT NAND GATE 2-OR 3-WIDE 6-INPUT NAND GATE | ON44                 | 2        |

| 2-OR 2-WIDE 3-INPUT AND GATE                                      | ON36                 | 5        |

| INVERTERS/BUFFERS                                                 | OA23                 | 2        |

| NORMAL INVERTER                                                   | <del> </del>         |          |

| POWER INVERTER                                                    | IN1                  |          |

| POWER INVERTER                                                    | IN2                  | 1        |

| NORMAL BUFFER                                                     | IN4                  | 2        |

| FLIP-FLOPS                                                        | BUF1                 | 1        |

| LATCH                                                             | <del>  - ; _  </del> |          |

| LATCH WITH RESET                                                  | LF<br>1.50           | 4        |

| LATCH WITH SET                                                    | LFR                  | 5        |

| D-FF                                                              | LFS                  | 5        |

| D-FF WITH RESET                                                   | DF                   | 6        |

| D-FF WITH RESET                                                   | DFR                  |          |

| D-FF WITH SET AND RESET                                           | DFS                  |          |

| JK-FF WITH RESET                                                  | DFSR                 | 8        |

|                                                                   | JKR                  | 10       |

| JK-FF WITH SET AND RESET                                          | JKSR                 | 11       |

| ADDERS                                                            | <del> </del>         |          |

| 1-BIT FULL ADDER COMPARATORS                                      | T183                 | 9        |

|                                                                   | <del>   </del>       |          |

| 4-BIT MAGNITUDE COMPARATOR WITH ENABLE                            | T085                 | 39       |

| 8-BIT MAGNITUDE COMPARATOR COUNTERS                               | T688                 | 26       |

|                                                                   | <u> </u>             |          |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER                               | A161                 | 57       |

| WITH RESET, LOAD AND ENABLE                                       | <u> </u>             |          |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH RESET AND LOAD           | T161E                | 51       |

| SYNCHRONOUS 2-BIT BINARY UP COUNTER WITH RESET, LOAD AND ENABLE   | A161H                | 29       |

# ■ MACRO LIBRARY (cont.)

| Function                                                      | Cell Name    | Gates    |

|---------------------------------------------------------------|--------------|----------|

| COUNTERS (cont.)                                              |              |          |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH RESET AND ENABLE     | A161L        | 46       |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH RESET                | A161LE       | 40       |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH LOAD AND ENABLE      | A161R        | 52       |

| SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH LOAD                 | T161RE       | 46       |

| FULLY SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH RESET, LOAD    | A163         | 54       |

| AND ENABLE                                                    |              |          |

| FULLY SYNCHRONOUS 4-BIT BINARY UP COUNTER WITH RESET AND LOAD | A163E        | 48       |

| RESETABLE R-BIT BINARY UP COUNTER/LATCH WITH RESET AND LOAD   | T177         | 39       |

| PRESETABLE 2-BIT BINARY UP COUNTER/LATCH WITH RESET AND LOAD  | T177H        | 21       |

| PRESETABLE 4-BIT BINARY UP COUNTER/LATCH WITH LOAD            | T177R        | 38       |

|                                                               |              |          |

| PRESETABLE 4-BIT BINARY UP COUNTER/LATCH WITH SET AND LOAD    | T177V        | 39       |

| PRESETABLE 2-BIT BINARY UP COUNTER/LATCH WITH SET AND LOAD    | T177HV       | 20       |

| SYNCHRONOUS 4-BIT UP/DOWN COUNTER WITH LOAD AND ENABLE        | A191         | 70       |

| SYNCHRONOUS 4-BIT UP/DOWN COUNTER WITH RESET                  | A191CE       | 47       |

| SYNCHRONOUS 4-BIT UP/DOWN COUNTER WITH LOAD                   | A191E        | 63       |

| SYNCHRONOUS 2-BIT UP/DOWN COUNTER WITH LOAD AND ENABLE        | A191H        | 35       |

| SYNCHRONOUS 4-BIT UP/DOWN COUNTER WITH RESET                  | A191LE       | 51       |

| SYNCHRONOUS 4-BIT DUAL CLOCK BINARY UP/DOWN COUNTER WITH      | A193         | 69       |

| RESET AND LOAD                                                | /./65        | •        |

| SYNCHRONOUS4-BIT DUAL CLOCK BINARY UP/DOWN COUNTER WITH       | A193L        | 53       |

| RESET                                                         | ^135L        | 33       |

| SYNCHRONOUS 2-BIT DUAL CLOCK BINARY UP/DOWN COUNTER WITH      | A193L        | 200      |

|                                                               | A193L        | 36       |

| RESET AND LOAD                                                | 1            |          |

| SYNCHRONOUS 2-BIT DUAL CLOCK BINARY UP/DOWN COUNTER WITH      | A193HL       | 27       |

| RESET                                                         |              |          |

| DECADE COUNTER WITH RESET                                     | A390         | 34       |

| 4-BIT BINARY UP COUNTER WITH RESET                            | T93V         | 25       |

| 4-BIT BINARY DOWN COUNTER WITH RESET                          | T393V        | 25       |

| DECODER/DEMULTIPLEXERS                                        |              |          |

| BCD-TO-DECIMAL DECODER                                        | T042         | 29       |

| 3-LINE TO 8-LINE DECODE/MULTIPLEXER WITH ENABLE G             | A138G2       | 18       |

| 2-LINE TO 4-LINE DECODER/MULTIPLEXER WITH ENABLE G            | A139         | 9        |

| 2-LINE TO 4-LINE DECODER/MULTIPLEXER                          | A139G        | 6        |

| DFFS/LATCHES                                                  | AISSG        | - 0      |

|                                                               | <del> </del> |          |

| 4-BIT LATCH WITH RESET                                        | T116         | 17       |

| QUADRUPLE DFF WITH RESET                                      | T175         | 27       |

| QUADRUPLE DFF WITH Q, XQ WITHOUT RESET                        | T175R        | 22       |

| QUADRUPLE DFF WITH Q ONLY                                     | T175RX       | 22       |

| OCTAL DFF WITH RESET                                          | T175W        | 54       |

| OCTAL OFF                                                     | T175WR       | 44       |

| OCTAL D-TYPE TRANSPARENT LATCH WITH ENABLE                    | T373T        | 26       |

| SELECTORS/MULTIPLEXERS                                        | 1 .0.0.      |          |

| 4-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER                    | T153         | 12       |

| WITH STROBE G                                                 | 1155         | 12       |

|                                                               | T1500        |          |

| 4-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER                    | T153G        | 10       |

| QUADRUPLE 2-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER          | T157WG       | 13       |

| WITH STROBE G                                                 | <u> </u>     |          |

| QUADRUPLE 2-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER          | T157G        | 11       |

| OCTAL 2-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER              | T157W        | 25       |

| WITH STROBE G                                                 |              |          |

| OCTAL 2-LINE TO 1-LINE DATA SELECTOR/MULTIPLEXER              | T157WG       | 21       |

| SHIFT REGISTERS                                               | 1,           | <u> </u> |

| 8-BIT PARALLEL-OUT SERIAL SHIFT REGISTER WITH RESET           | T164         | 55       |

| 8-BIT SHIFT REGISTER WITH RESET, LOAD AND ENABLE              |              |          |

| 4-BIT SHIFT REGISTER WITH RESET, LOAD AND ENABLE              | T166         | 65       |

| 4-DIT SHIFT REGISTER WITH RESET, LOAD AND ENABLE              | T166H        | 34       |

### **■ INTERNAL TRISTATES**

S-MOS supports the use of internal tristate busses with the following macro library:

| Name  | Function                        | Gates |  |  |

|-------|---------------------------------|-------|--|--|

| TSV   | Tristate Inverting Buffer       | 4     |  |  |

| TSB   | Tristate Buffer                 | 4     |  |  |

| T240  | Octal Inverting Tristate Buffer | 26    |  |  |

| T240H | Quad Inverting Tristate Buffer  | 13    |  |  |

| T244  | Octal Tristate Buffer           | 22    |  |  |

| Name  | Function                   | Gates |

|-------|----------------------------|-------|

| T244H | Quad Tristate Buffer       | 11    |

| T373  | Octal Latch With Tristates | 46    |

| T373H | Quad Latch With Tristates  | 23    |

| T374  | Octal DFF With Tristates   | 72    |

| T374H | Quad DFF With Tristates    | 36    |

NOTE: In order to ensure design quality, S-MOS Systems requires the use of certain design practices when using internal tristate cells. Please consult S-MOS Systems for more information.

### **■ PACKAGE MATRIX**

|                 | No.   | Device code   | 1020  | 1024       | 1029  | 1034  | 1039  | 1049  | 1060  | 1073  | 1081  | 1152   | 1255   |

|-----------------|-------|---------------|-------|------------|-------|-------|-------|-------|-------|-------|-------|--------|--------|

| Package<br>Type | C of  | Pads<br>Gross | 128   | 140        | 152   | 164   | 176   | 196   | 216   | 236   | 248   | 336    | 432    |

|                 | No. C | Gates         | 20216 | 24424      | 29120 | 34138 | 39644 | 49489 | 60653 | 73353 | 81320 | 152256 | 254743 |

| Plastic DIP     | 28    | S28           | Α     |            |       |       |       |       |       |       |       |        |        |

| Plastic DIP     | 40    | C40           | A     |            |       |       |       |       |       |       |       |        |        |

|                 | 64    | QFP-5         | Q     | Q          |       |       |       |       |       |       |       |        |        |

|                 | 64    | QFP-13        | A     | Α          | A     |       |       |       |       |       |       |        |        |

|                 | 80    | QFP-5         | A*    | A*         | Α*    | A*    | A*    | A*    | A*    | LQ    | LQ    |        |        |

|                 | 80    | QFP-14        | Α     | Α          | Α     | A     | Α     | Α     | Α     |       |       |        |        |

|                 | 100   | QFP-5         | A*    | A*         | A*    | A*    | A*    | A*    | Α*    | LQ    | LQ    |        |        |

|                 | 100   | QFP-15        | Α     | Α          | Α     | Α     | Α     | Α     | Α     |       |       |        |        |

|                 | 120   | QFP-8         | A*    | A*         | A*    | A*    | Α*    | A*    | A*    | A*    | A*    |        | LQ     |

| Plastic QFP     | 128   | QFP-5         | A*    | Α*         | A*    | L     | A*    | A*    | A*    | LQ    |       |        |        |

|                 | 128   | QFP-8         | Α     | A          | A*    | [      | LQ     |

|                 | 144   | QFP-8         | L     | L          | A*    | Α*    | A*    | A*    | A*    | A*    | A*    |        | LQ     |

|                 | 144   | QFP-17        |       | L          | Α     | Α     | Α     | Α     | Α     | Q     | A*    |        | LQ .   |

|                 | 160   | QFP-8         |       | L          | L     | Α*    | Α     | A*    | A*    | A*    |       |        |        |

|                 | 184   | QFP-16        |       |            |       |       |       | Q     | Α     | Α     | Α     |        | LQ     |

|                 | 196   | QFP-9         |       |            |       |       |       |       | A*    | Α     |       |        | LQ     |

|                 | 208   | QFP-8         |       |            |       |       |       |       | Α     | A*    | Α*    | Q      | LQ     |

|                 | 232   | QFP-10        |       |            |       |       |       |       |       |       |       |        | D      |

|                 | 256   | QFP-9         |       |            |       |       |       |       |       |       |       |        | Q      |

|                 | 44    | J44           | Q     |            |       |       |       |       |       |       |       |        |        |

| PLCC            | 68    | J68           | Α     |            |       |       |       |       |       |       |       |        |        |

|                 | 84    | J84           | A*    | <u>A</u> * | A*    | Α*    | A*    | A*    | A*    | A*    | A*    |        | LQ     |

| Ceramic PGA     | 132   | P132          |       |            |       | Α     |       |       |       |       |       |        |        |

A: Available \*: Pin-Pad t Pin-Pad table exist

L: Need Lead frame development (2.5 months for new lead frame development)

Q: Need Qualification (reliability test) (2.5 months for reliability test)

LQ: Need Lead frame and Qualification (reliability test)(2.5 months for new lead frame development and/or 2.5 months for reliability test)

### **■ PROCESS TECHNOLOGY**

The SLA10000 Series is fabricated on our highly automated 6" fabrication line located in Fujimi, Japan. The process is similar to that used for high-volume 1 Meg SRAM which has been in production since 1988.

N-Channel is .76 micron drawn (0.6 micron effective) and P-Channel length is 1.2 micron drawn (.8 micron effective).

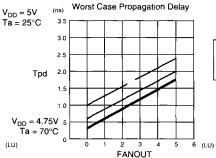

## **■ PROPAGATION DELAY TIMES**

The propagation delay values printed in our cell libraries and used in simulation are derived from actual measurements of silicon, not spice simulations. The measured coefficient parameters are:

## Delay Multiplier

|     | 5%   | 10%  |  |  |

|-----|------|------|--|--|

| Min | 0.65 | 0.60 |  |  |

| Max | 1.60 | 1.75 |  |  |

5% Factor

Voltage: 4.75 to 5.25 volts Temperature = 0 to 70°C

10% Factor

Voltage: 4.50 to 5.50 Volts Temperature = -20 to 85°C

| Name    | Function     | From   | То                  | Best | Case               | Wors  | Case  | Loads |

|---------|--------------|--------|---------------------|------|--------------------|-------|-------|-------|

| Ivallie | runction     | FIOIII | tplh (ns) tphl (ns) |      | tplh (ns) tphl (ns |       | Loads |       |

|         |              |        |                     | .07  | .05                | .15   | .11   | 0     |

| NA2     | 2-INPUT NAND | IN     | OUT                 | .12  | .09                | .28   | .20   | 1     |

|         |              |        |                     | .18  | .13                | .40   | .30   | 2     |

|         |              |        |                     | .09  | .03                | .23   | .06   | 0     |

| NO2     | 2-INPUT NOR  | iN     | OUT                 | .18  | .05                | .45   | .12   | 1     |

|         |              |        |                     | .27  | .08                | .66   | .17   | 2     |

|         |              |        |                     | .05  | .03                | .12   | .06   | 0     |

| IN1     | 1 x INVERTER | IN     | OUT                 | .10  | .05                | .25   | .12   | 1     |

|         |              |        |                     | .16  | .08                | .38   | .17   | 2     |

|         |              |        |                     | .03  | .02                | .08   | .04   | 0     |

| IN4     | 4 x INVERTER | IN     | OUT                 | .04  | .03                | .11   | .05   | 1     |

|         |              |        |                     | .06  | .04                | .15   | .07   | 2     |

|         |              |        |                     | .39  | .47                | .95   | 1.16  | Ō     |

| DF      | D FLIP-FLOP  | CLK    | Q                   | .44  | .49                | 1.08  | 1.22  | 1     |

|         |              |        |                     | .50  | .52                | 1.20  | 1.27  | 2     |

|         | TTL LEVEL    |        |                     | .41  | .39                | 1.00  | .95   | 0     |

| IBT     |              | IN .   | OUT                 | .43  | .42                | 1.05  | 1.01  | 1     |

|         | INPUT BUFFER |        |                     | .45  | .44                | 1.09  | 1.08  | 2     |

|         | 2mA OUTDUT   |        |                     | 1.20 | 1.89               | 2.95  | 4.64  | 10pF  |

| UO1     | 2mA OUTPUT   | IN     | PAD                 | 4.56 | 6.46               | 11.22 | 15.88 | 50pF  |

|         | DRIVER       |        |                     | 8.76 | 12.16              | 21.55 | 29.93 | 100pF |

|         | 6mA OUTDUT   |        |                     | .75  | 1.17               | 1.84  | 2.86  | 10pF  |

| UO2     | 6mA OUTPUT   | IN     | PAD                 | 2.77 | 3.55               | 6.79  | 8.46  | 50pF  |

| L       | DRIVER       |        |                     | 5.28 | 6.29               | 12.98 | 15.46 | 100pF |

| BEST CASE                 | WORST CASE                 |  |  |  |

|---------------------------|----------------------------|--|--|--|

| Temperature = 0°C Ambient | Temperature = 70°C Ambient |  |  |  |

| Supply Voltage = 5.25V    | Supply Voltage = 4.75V     |  |  |  |

| Process = Best case       | Process = Worst Case       |  |  |  |

## Workstation Support

Schematic capture, electrical rule checking, design rule checking, simulation and timing verification are supported on Daisy, Mentor, Valid, NavNet and Intergraph workstations. In addition, our proprietary LADS software, used with NavNet, ViewLogic, OrCad or FutureNet, is available for IBM PCs and compatibles. LADS is also available on Sun and Apollo platforms.

LADS includes ERC, DRC, logic simulation and timing verification up to 6,000 gates using PCs with 640K of memory or up to 20,000 gates in PCs equipped with 4 megabytes of extended memory.

## Standard Cell Migration

The SLA10000 Series can be easily migrated to the SSC5000 Series 0.8µm standard cells. This is made possible by the identical and compatible design tools shared by the two design methodologies. As such, the gate array macro library is a subset of the standard cell macro library.

### Megacells

Due to the design of the SLA10000 Series, fully routed and characterized megacells be implemented effectively alongside of random logic. Available:

| B8259   | B82288  |

|---------|---------|

| B8237   | B146818 |

| B82284  | B8250   |

| B8255   | B8251   |

| B16C550 | B8254   |

|         | B-80    |

### **■ PERFORMANCE CURVES**

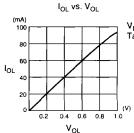

# Current (Type 4 Output Buffer)

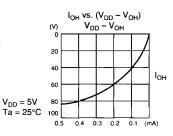

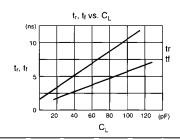

Type 2 Output Buffer Delay Characteristics

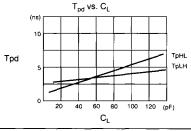

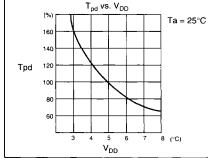

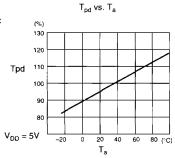

# **Propagation Delay Characteristics**

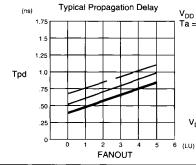

# **Propagation Delay Including Interconnect**

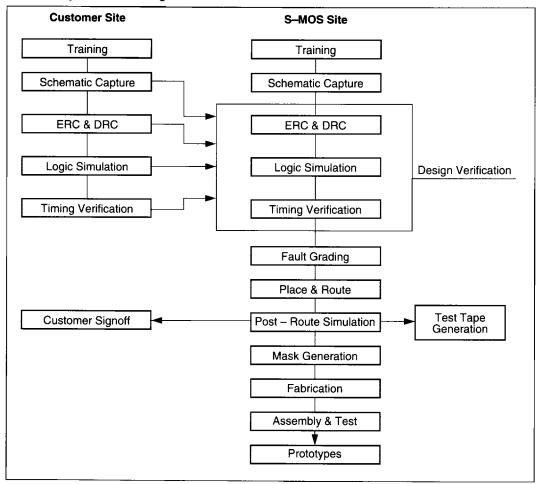

# ■ S-MOS Systems ASIC Design Flow