# **OKI Semiconductor**

**FEDL9092-01** Issue Date: Nov. 4, 2003

# ML9092-01/02/03/04

LCD Driver with Key Scanner and RAM

#### GENERAL DESCRIPTION

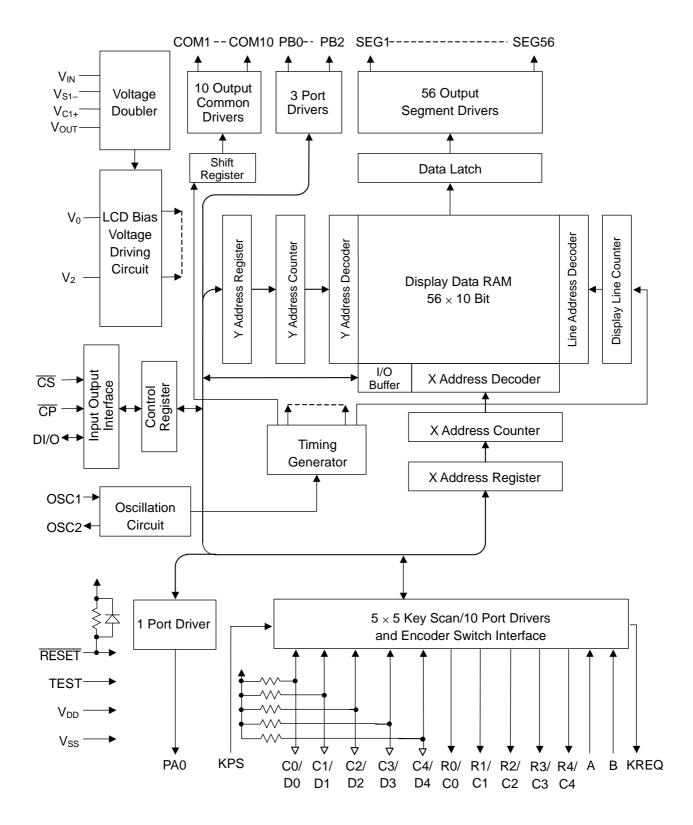

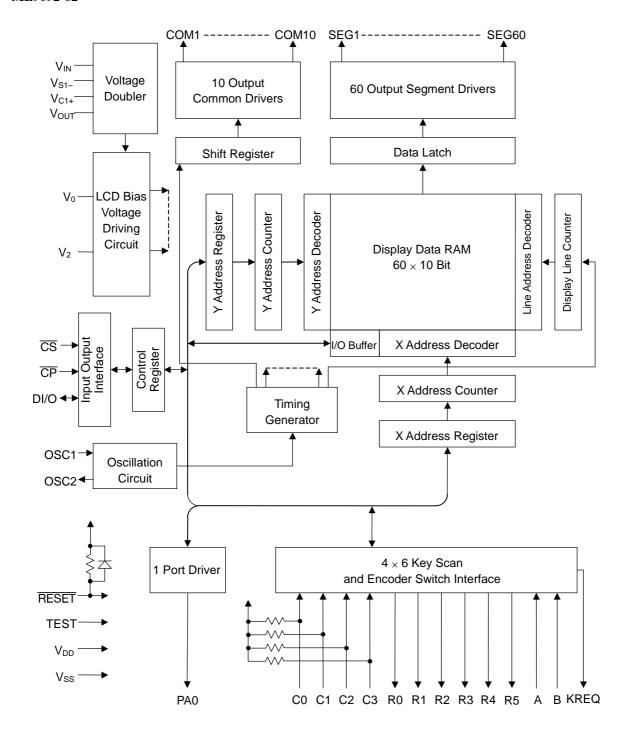

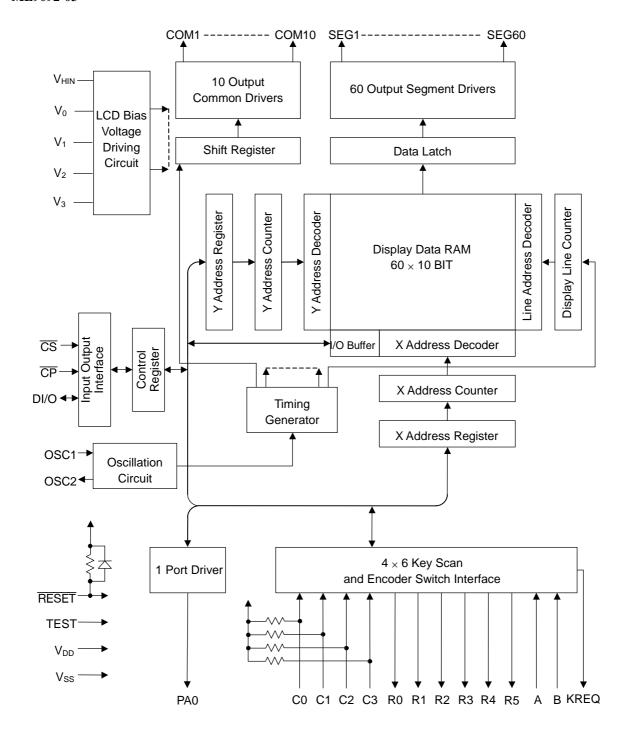

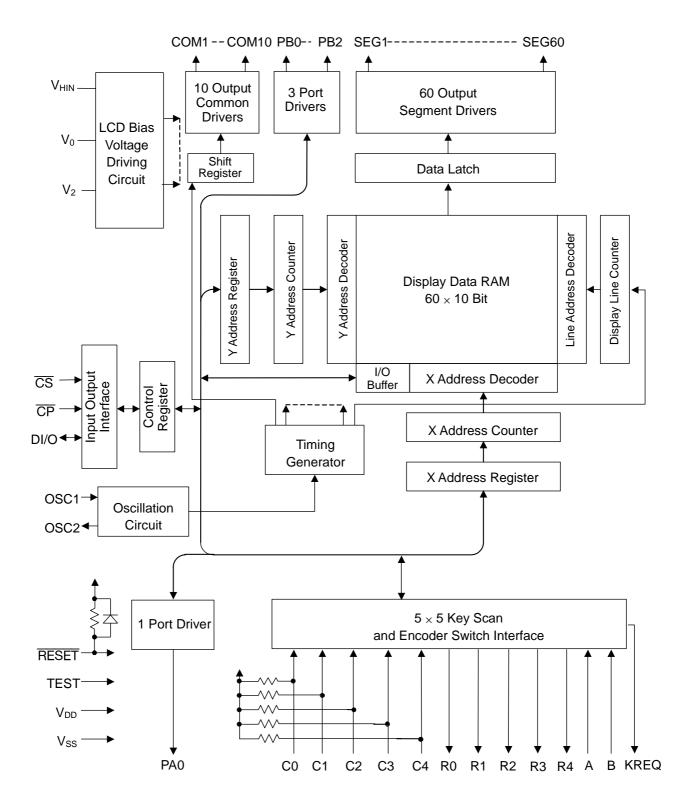

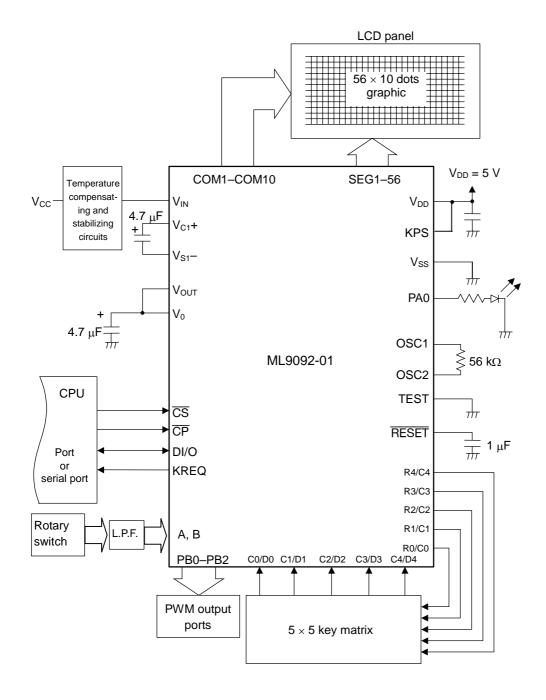

The ML9092-01/02/03/04 are LCD drivers that have internal RAM and a key scan function. They are best suited for car audio displays.

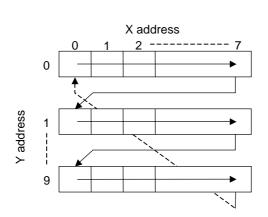

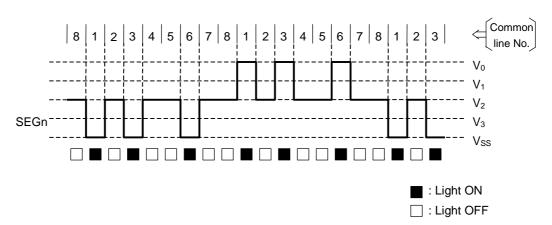

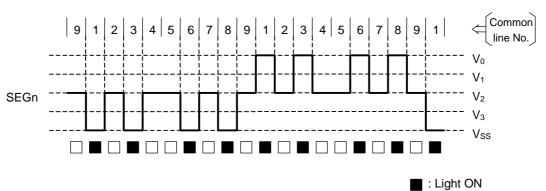

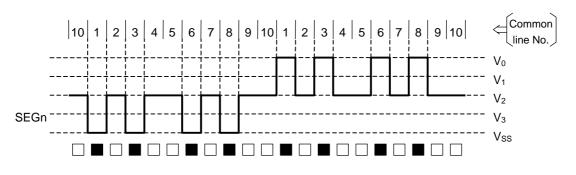

Since 1-bit data of the display data RAM corresponds to the light-on or light-off of 1-dot of the LCD panel (a bit map system), a flexible display is possible.

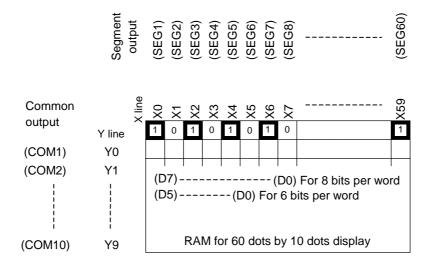

A graphic display system of a maximum of  $60 \times 10$  dots ( $56 \times 10$  dots for ML9092-01,  $60 \times 10$  dots for ML9092-02/03/04). can be implemented.

The ML9092-01/02 do not require any power supply circuit to drive the LCD, because they have internal voltage doublers. (If a large-sized panel is driven, use the ML9092-03, to which the LCD driving voltage is supplied externally.)

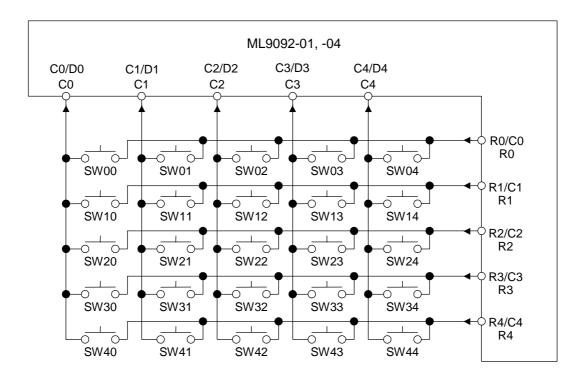

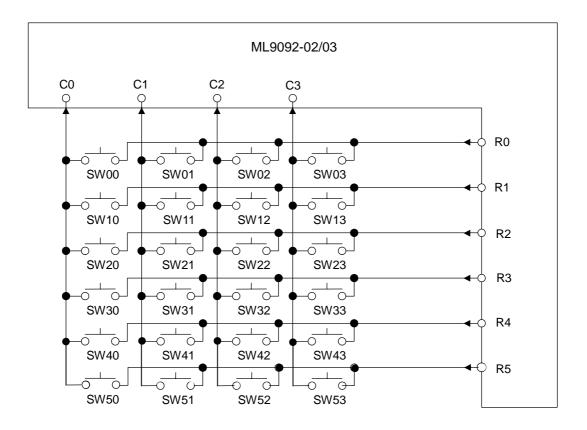

The internal key scan circuit ( $5 \times 5$  key scanning for ML9092-01/04,  $6 \times 4$  key scanning for ML9092-02/03) has eliminated the needs of key scanning by the CPU, thereby enabling the efficient use of the CPU ports.

#### **FEATURES**

• Logic voltage : 4.5 to 5.5 V

• LCD drive voltage : 4.5 to 16.5 V (positive voltage)

• Segment output : 56 outputs for ML9092-01; 60 outputs for ML9092-02/03/04

• Common output : 10 outputs

• Built-in bit-mapped RAM :  $60 \times 10 = 600$  bits (for ML9092-01 only:  $56 \times 10 = 560$  bits for the RAM

display area)

• 4-pin serial interface with CPU:  $\overline{CS}$ ,  $\overline{CP}$ , DI/O, KREQ

• Built-in LCD drive bias resistors

• Built-in voltage doubler circuit

• For the ML9092-01/04, the built-in 5 × 5 key scanner makes it possible to read the status of 25 key switches and 1-channel rotary encoder. In addition, the ML9092-01/04 have an 8-bit, 3-channel PWM circuit built in. For the ML9092-02/03, the built-in 6 × 4 key scanner makes it possible to read the status of 24 key switches and 1-channel rotary encoder.

• Port A output : 1 pin, output current = -15 mA : Can be used for LED driving

• Port B output : 3 pins, output current = -2 mA : Applies to ML9092-01/04 (capable of PWM

output)

Port C output

Port D output

2 pin, output current = -2 mA

3 pin, output current = -2 mA

4 Applies to ML9092-01 only

5 pins, output current = -2 mA

5 pins, output current = -2 mA

• Temperature range  $: -40 \text{ to } +85^{\circ}\text{C}$

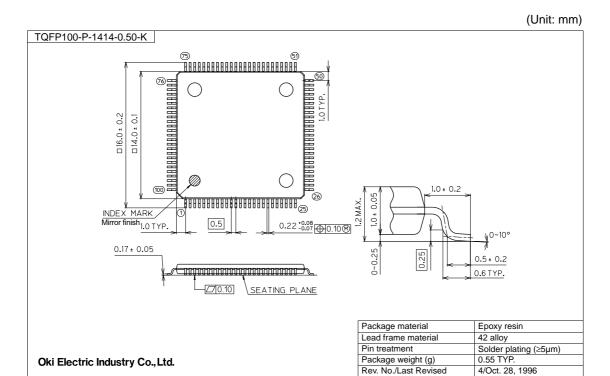

• Package: 100-pin plastic TOFP (TOFP100-P-1414-0.50-K)

(Product name: ML9092-01TB, ML9092-02TB, ML9092-03TB, ML9092-04TB)

# Comparison between the ML9092-01, ML9092-02, ML9092-03, and ML9092-04

| Item                                            | ML9092-01        | ML9092-02      | ML9092-03      | ML9092-04        |

|-------------------------------------------------|------------------|----------------|----------------|------------------|

| Number of common outputs                        | 10 Max.          | 10 Max.        | 10 Max.        | 10 Max.          |

| Number of dots on the LCD screen                | 8 × 56           | 8 × 60         | 8 × 60         | 8 × 60           |

|                                                 | 9 × 56           | 9 × 60         | 9 × 60         | 9 × 60           |

| (selectable by program)                         | 10 × 56          | 10 × 60        | 10 × 60        | 10 × 60          |

| Number of port A outputs                        | 1                | 1              | 1              | 1                |

| Number of port B outputs                        | 3                | 0              | 0              | 3                |

| Number of port C and D outputs (see note below) | 5 each           | 0              | 0              | 0                |

| Key scan (see note below)                       | 5 × 5 key scan   | 4 × 6 key scan | 4 × 6 key scan | 5 × 5 key scan   |

| Rotary encoder                                  | 1 channel        | 1 channel      | 1 channel      | 1 channel        |

| Voltage doubler                                 | Yes              | Yes            | No             | No               |

| PWM circuit                                     | 8-bit, 3-channel | No             | No             | 8-bit, 3-channel |

Note: The key scan function and port C/D cannot be used concurrently. Use either.

#### **BLOCK DIAGRAM**

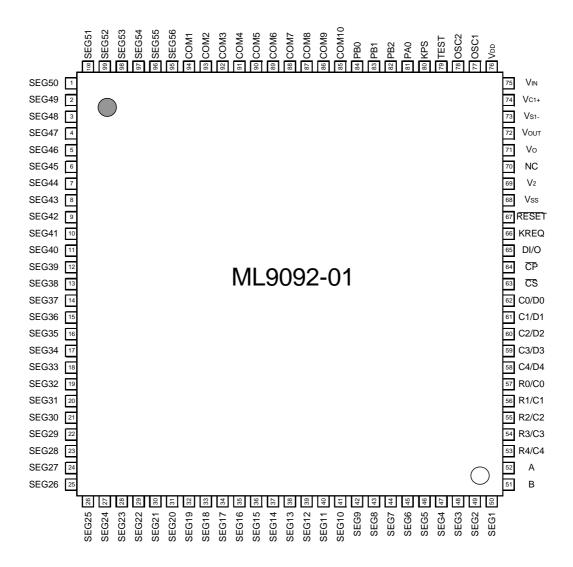

### **PIN CONFIGURATION (TOP VIEW)**

100-Pin Plastic TQFP

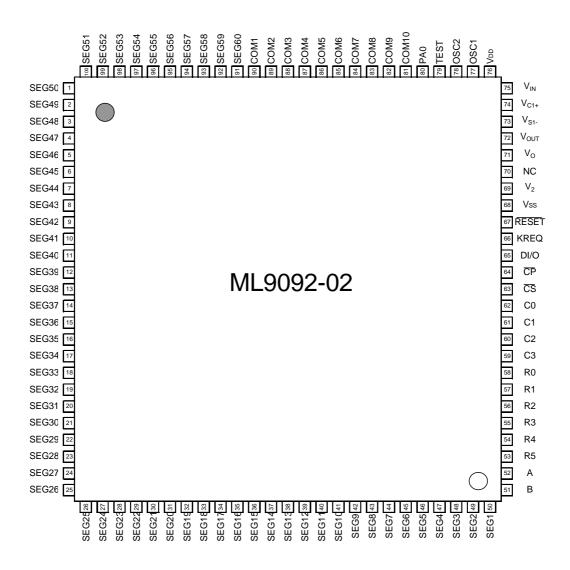

100-Pin Plastic TQFP

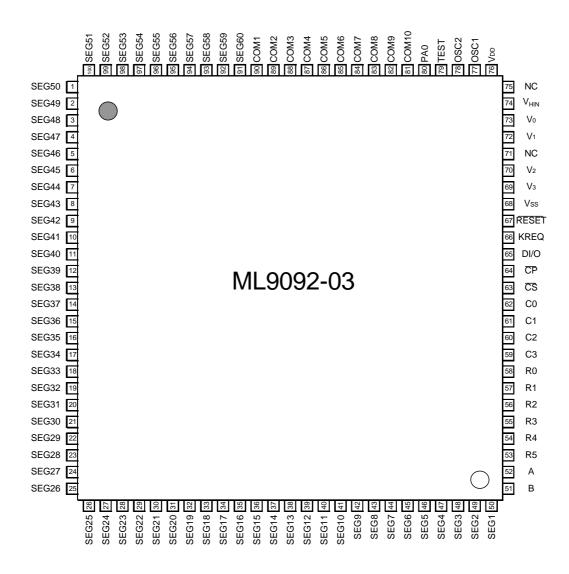

100-Pin Plastic TQFP

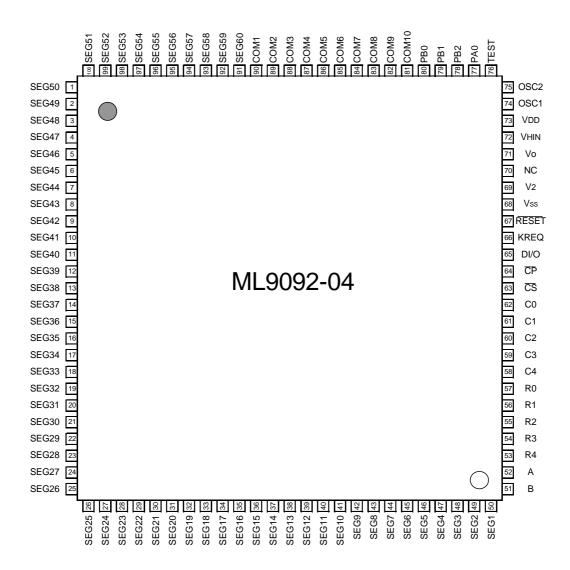

ML9092-01/02/03/04

100-Pin Plastic TQFP

# FUNCTIONAL DESCRIPTIONS

# **Pin Functional Descriptions**

| ML9092-01<br>Function | Pin            | Symbol                               | Туре | Description                                                                                                                                            |

|-----------------------|----------------|--------------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | 63             | <del>CS</del>                        | 1    | Chip select signal input pin                                                                                                                           |

|                       | 64             | СP                                   | I    | Shift clock signal input pin. This pin is connected to the Schmitt circuit internally.                                                                 |

| CPU interface         | 65             | DI/O                                 | I/O  | Serial data signal I/O pin. This pin is connected to the Schmitt circuit internally.                                                                   |

|                       | 66             | KREQ                                 | 0    | Key scan read and rotary encoder read READY signal output pin.                                                                                         |

|                       | 77             | OSC1                                 | 1    | Connect external resistors with this pin.                                                                                                              |

| Oscillation           | 78             | OSC2                                 | 0    | This pin is connected to the Schmitt circuit internally.  If using an external clock, input it from the OSC1 pin and leave the OSC2 pin open.          |

| Control size of       | 67             | RESET                                | I    | Reset input. Initial settings can be established by applying a "L" level to this pin. This pin is connected to the Schmitt circuit internally.         |

| Control signal        | 80             | KPS                                  | I    | Input pin for switching between key scanning and ports C and D                                                                                         |

|                       | 79             | TEST                                 | I    | Test input pin. This pin is connected to the $V_{\text{SS}}$ pin.                                                                                      |

|                       | 62–58          | C0/D0-C4/D4                          | I/O  | Input pins that detect status of key switches/port D output pins. When used as input pins, these pins are connected to the Schmitt circuit internally. |

| Switch signal         | 57–53          | R0/C0-R4/C4                          | 0    | Key switch scan signal output pins/port C output pins                                                                                                  |

|                       | 51, 52         | A, B                                 | I    | Rotary encoder signal input pins. These pins are connected to the Schmitt circuit internally.                                                          |

| Dowl accidenced       | 81             | PA0                                  | 0    | Port A output pin                                                                                                                                      |

| Port output           | 84–82          | PB0-PB2                              | 0    | Port B output pins                                                                                                                                     |

| LCD driver output     | 50–1<br>100–95 | SEG1-SEG56                           | 0    | LCD segment driver output pins                                                                                                                         |

|                       | 94–85          | COM1-COM10                           | 0    | LCD common driver output pins                                                                                                                          |

|                       | 76             | $V_{DD}$                             | _    | Logic power supply pin                                                                                                                                 |

|                       | 68             | V <sub>SS</sub>                      | _    | GND pin                                                                                                                                                |

| Power supply          | 75             | V <sub>IN</sub>                      | _    | Voltage doubler reference voltage input pin                                                                                                            |

|                       | 74, 73         | V <sub>C1</sub> +, V <sub>S1</sub> - | _    | Pins to connect a capacitor for voltage doubler                                                                                                        |

|                       | 72             | V <sub>OUT</sub>                     | _    | Voltage doubler output pin                                                                                                                             |

|                       | 71, 69         | V <sub>0</sub> , V <sub>2</sub>      | _    | LCD bias pins                                                                                                                                          |

|                       | 70             | NC                                   | _    | Should be left open.                                                                                                                                   |

| -                     |                |                                      |      | •                                                                                                                                                      |

| Function          | Pin            | Symbol                               | Type | Description                                                                                                                                    |  |  |  |

|-------------------|----------------|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | 63             | <u>cs</u>                            | I    | Chip select signal input pin                                                                                                                   |  |  |  |

|                   | 64             | CP                                   | I    | Shift clock signal input pin. This pin is connected to the Schmitt circuit internally.                                                         |  |  |  |

| CPU interface     | 65             | DI/O                                 | I/O  | Serial data signal I/O pin. This pin is connected to the Schmitt circuit internally.                                                           |  |  |  |

|                   | 66             | KREQ                                 | 0    | Key scan read and rotary encoder read READY signal output pin.                                                                                 |  |  |  |

|                   | 77             | OSC1                                 | I    | Connect external resistors with this pin.  This pin is connected to the Schmitt circuit                                                        |  |  |  |

| Oscillation       | 78             | OSC2                                 | Ο    | internally.  If using an external clock, input it from the OSC1 pin and leave the OSC2 pin open.                                               |  |  |  |

| Control signal    | 67             | RESET                                | I    | Reset input. Initial settings can be established by applying a "L" level to this pin. This pin is connected to the Schmitt circuit internally. |  |  |  |

|                   | 79             | TEST                                 | I    | Test input pin. This pin is connected to the $V_{\text{SS}}$ pin.                                                                              |  |  |  |

|                   | 62–59          | C0-C3                                | I    | Input pins that detect status of key switches. These pins are connected to the Schmitt circuit internally.                                     |  |  |  |

| Switch signal     | 58–53          | R0-R5                                | 0    | Key switch scan signal output pins                                                                                                             |  |  |  |

|                   | 51, 52         | A, B                                 | I    | Rotary encoder signal input pins. These pins are connected to the Schmitt circuit internally.                                                  |  |  |  |

| Port output       | 80             | PA0                                  | 0    | Port A output pin                                                                                                                              |  |  |  |

| LCD driver output | 50–1<br>100–91 | SEG1-SEG60                           | 0    | LCD segment driver output pins                                                                                                                 |  |  |  |

|                   | 90–81          | COM1-COM10                           | 0    | LCD common driver output pins                                                                                                                  |  |  |  |

|                   | 76             | $V_{DD}$                             |      | Logic power supply pin                                                                                                                         |  |  |  |

|                   | 68             | V <sub>SS</sub>                      |      | GND pin                                                                                                                                        |  |  |  |

| Power supply      | 75             | V <sub>IN</sub>                      | _    | Voltage doubler reference voltage input pin                                                                                                    |  |  |  |

|                   | 74, 73         | V <sub>C1</sub> +, V <sub>S1</sub> - | _    | Pins to connect a capacitor for voltage doubler                                                                                                |  |  |  |

|                   | 72             | V <sub>OUT</sub>                     | _    | Voltage doubler output pin                                                                                                                     |  |  |  |

|                   | 71, 69         | V <sub>0</sub> , V <sub>2</sub>      |      | LCD bias pins                                                                                                                                  |  |  |  |

|                   | 70             | NC                                   | _    | Should be left open.                                                                                                                           |  |  |  |

| Function          | Pin             | Symbol                                                            | Type | Description                                                                                                                                    |

|-------------------|-----------------|-------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | 63              | <del>CS</del>                                                     | I    | Chip select signal input pin                                                                                                                   |

|                   | 64              | CP                                                                | I    | Shift clock signal input pin. This pin is connected to the Schmitt circuit internally.                                                         |

| CPU interface     | 65              | DI/O                                                              | I/O  | Serial data signal I/O pin. This pin is connected to the Schmitt circuit internally.                                                           |

|                   | 66              | KREQ                                                              | 0    | Key scan read and rotary encoder read READY signal output pin.                                                                                 |

|                   | 77              | OSC1                                                              | 1    | Connect external resistors with this pin.                                                                                                      |

| Oscillation       | 78              | OSC2                                                              | 0    | This pin is connected to the Schmitt circuit internally.  If using an external clock, input it from the OSC1 pin and leave the OSC2 pin open.  |

| Control signal    | 67              | RESET                                                             | I    | Reset input. Initial settings can be established by applying a "L" level to this pin. This pin is connected to the Schmitt circuit internally. |

|                   | 79              | TEST                                                              | I    | Test input pin. This pin is connected to the $V_{\text{SS}}$ pin.                                                                              |

|                   | 62–59           | C0-C3                                                             | 1    | Input pins that detect status of key switches. These pins are connected to the Schmitt circuit internally.                                     |

| Switch signal     | 58–53           | R0–R5                                                             | 0    | Key switch scan signal output pins                                                                                                             |

|                   | 51, 52          | A, B                                                              | I    | Rotary encoder signal input pins. These pins are connected to the Schmitt circuit internally.                                                  |

| Port output       | 80              | PA0                                                               | 0    | Port A output pin                                                                                                                              |

| LCD driver output | 50–1,<br>100–91 | SEG1-SEG60                                                        | 0    | LCD segment driver output pins                                                                                                                 |

|                   | 90–81           | COM1-COM10                                                        | 0    | LCD common driver output pins                                                                                                                  |

|                   | 76              | $V_{DD}$                                                          |      | Logic power supply pin                                                                                                                         |

|                   | 68              | V <sub>SS</sub>                                                   |      | GND pin                                                                                                                                        |

| Power supply      | 74              | V <sub>HIN</sub>                                                  |      | High-voltage power supply pin                                                                                                                  |

|                   | 73, 72, 70, 69  | V <sub>0</sub> , V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> | _    | LCD bias pins                                                                                                                                  |

|                   | 75, 71          | NC                                                                |      | Should be left open.                                                                                                                           |

| ML9092-04         |                 | ·                               |      |                                                                                                                                                |

|-------------------|-----------------|---------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Function          | Pin             | Symbol                          | Type | Description                                                                                                                                    |

|                   | 63              | <del>CS</del>                   | I    | Chip select signal input pin                                                                                                                   |

|                   | 64              | СP                              | I    | Shift clock signal input pin. This pin is connected to the Schmitt circuit internally.                                                         |

| CPU interface     | 65              | DI/O                            | I/O  | Serial data signal I/O pin. This pin is connected to the Schmitt circuit internally.                                                           |

|                   | 66              | KREQ                            | 0    | Key scan read and rotary encoder read READY signal output pin.                                                                                 |

|                   | 74              | OSC1                            | 1    | Connect external resistors with this pin.                                                                                                      |

| Oscillation       | 75              | OSC2                            | 0    | This pin is connected to the Schmitt circuit internally.  If using an external clock, input it from the OSC1 pin and leave the OSC2 pin open.  |

| Control signal    | 67              | RESET                           | I    | Reset input. Initial settings can be established by applying a "L" level to this pin. This pin is connected to the Schmitt circuit internally. |

|                   | 76              | TEST                            | 1    | Test input pin. This pin is connected to the $V_{\text{SS}}$ pin.                                                                              |

|                   | 62–58           | C0-C4                           | I    | Input pins that detect status of key switches. These pins are connected to the Schmitt circuit internally.                                     |

| Switch signal     | 57–53           | R0-R4                           | 0    | Key switch scan signal output pins                                                                                                             |

|                   | 51, 52          | A, B                            | I    | Rotary encoder signal input pins. These pins are connected to the Schmitt circuit internally.                                                  |

| Port output       | 77<br>80–78     | PA0<br>PB0–PB2                  | 0    | Port A output pin Port B output pins                                                                                                           |

| LCD driver output | 50–1,<br>100–91 | SEG1-SEG60                      | 0    | LCD segment driver output pins                                                                                                                 |

|                   | 90–81           | COM1-COM10                      | 0    | LCD common driver output pins                                                                                                                  |

|                   | 73              | $V_{DD}$                        |      | Logic power supply pin                                                                                                                         |

|                   | 68              | V <sub>SS</sub>                 |      | GND pin                                                                                                                                        |

| Power supply      | 72              | V <sub>HIN</sub>                |      | High-voltage power supply pin                                                                                                                  |

|                   | 71, 69          | V <sub>0</sub> , V <sub>2</sub> |      | LCD bias pins                                                                                                                                  |

|                   | 70              | NC                              | _    | Should be left open.                                                                                                                           |

|                   |                 |                                 |      |                                                                                                                                                |

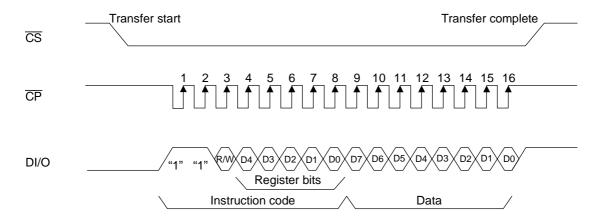

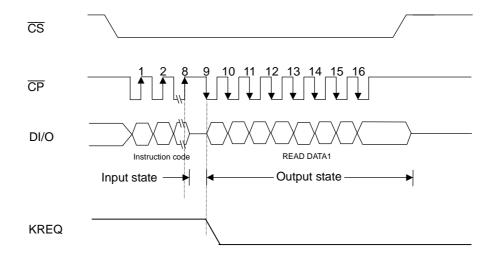

#### CS

Chip select input pin. A Schmitt circuit is internally connected to this pin. An "L" level selects the chip, and an "H" level does not select the chip. During the "L" level, internal registers can be accessed.

#### CP

Clock input pin for serial interface data I/O. A Schmitt circuit is internally connected to this pin. Data input to the DI/O pin is synchronized to the rising edge of the clock. Output from the DI/O pin is synchronized to the falling edge of the clock.

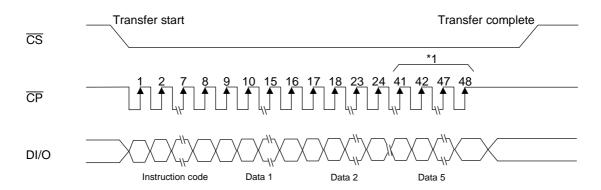

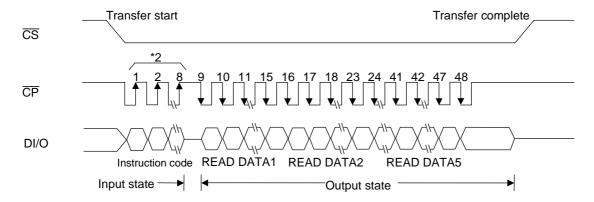

#### • DI/O

Serial interface data I/O pin. A Schmitt circuit is internally connected to this pin. This pin is in the output state only during the interval beginning when commands for key scan data read, RAM read or rotary encoder are written until the  $\overline{CS}$  signal rises. At all other times this pin is in the input state. (When reset, the input state is set.) The relation between data level of this pin and operation is listed below.

| Data level | LCD display | Key status | Rotary switch |  |  |

|------------|-------------|------------|---------------|--|--|

| "H"        | Light ON    | ON         | Count value   |  |  |

| "L"        | Light OFF   | OFF        | Count value   |  |  |

#### KREO

Key scan read and rotary encoder read READY signal output pin.

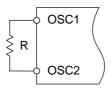

#### • OSC1

Input pin for RC oscillation. A Schmitt circuit is internally connected to this pin. An oscillation circuit is configured by connecting this pin and OSC2 with a resistor (R) placed across the connection (see figure below). Make the wiring between this pin and the resistor as short as possible. If an external master oscillation clock is to be input, input the master oscillation clock to this pin.

$$R = 56 \text{ k}\Omega$$

$$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V})$$

$$R$$

OSC1 OSC2

#### • OSC2

Output pin for RC oscillation. A Schmitt circuit is internally connected to this pin. An oscillation circuit is configured by connecting this pin and OSC1 with a resistor (R) placed across the connection (see figure above). Make the wiring between this pin and the resistor as short as possible. If an external master oscillation clock is to be input, leave this pin unconnected (open).

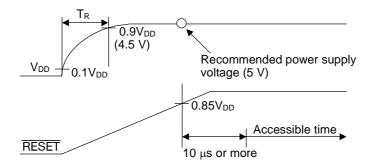

#### • RESET

Reset signal input pin. A Schmitt circuit is internally connected to this pin. The initial state can be set by pulling this pin to an "L" level. Refer to the "Output, I/O and Register States in Response to Reset Input" page for the initial states of each register and display.

An internal pull-up resistor is connected to this pin. Connecting an external capacitor enables power-on reset.

#### • TEST

Test signal input pin. Connect this pin to V<sub>SS</sub>.

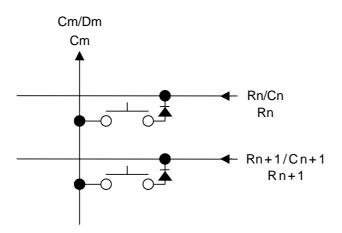

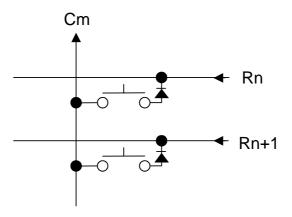

#### • R0/C0 to R4/C4 (ML9092-01), R0 to R5 (ML9092-02/03), R0 to R4 (ML9092-04)

Key switch scan signal output pins. During the scan operation, "L" level signals are output in the order of R0/C0, R1/C1, ..., R4/C4 (ML9092-01) or R0, R1, ..., R5 (ML9092-02/03) or R0, R1, ..., R4 (ML9092-04). (Refer to the description under the heading "Key scan" for details.) For the ML9092-01, R0 to R4 can be used as the output ports for the general-purpose port C depending on the input signal to the KPS pin.

#### • C0/D0 to C4/D4 (ML9092-01), C0 to C3 (ML9092-02/03), C0 to C4 (ML9092-04)

Input pins that detect the key switch status. Pull-up resistors and a Schmitt circuit are internally connected to these pins. Assemble a key matrix between these pins and the R0/C0 to R4/C4 (ML9092-01) or R0 to R5 (ML9092-02/03) or R0 to R4 (ML9092-04) pins. For the ML9092-01, C0 to C4 can be used as the output ports for the general-purpose port D depending on the input signal to the KPS pin.

#### KPS

Input pin that selects whether the R0/C0 to R4/C4 pins and C0/D0 to C4/D4 pins are used to detect the key switch status or whether they are used as the output pins for the general-purpose ports C and D. When this pin is pulled to a "H" level, the R0/C0 to R4/C4 pins and C0/D0 to C4/D4 pins function as pins that detect the key switch status. When this pin is pulled to a "L" level, it functions as the output pin for the general-purpose ports C and D. This pin must be fixed at either a "H" or "L" level.

This pin is provided only for the ML9092-01.

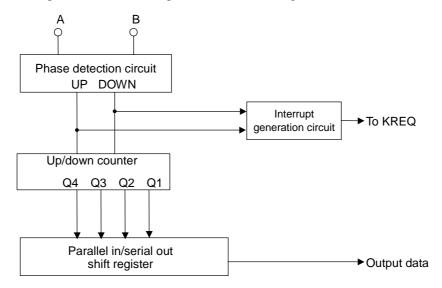

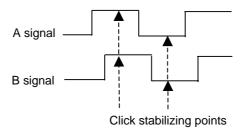

#### • A, B

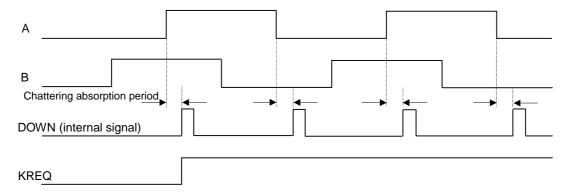

Input pins for encoder format rotary switches. A Schmitt circuit is internally connected to these pins. When turning the rotary switch clockwise, input to the A pin a signal more advancing in phase than the B pin. When turning the rotary switch counterclockwise, input to the B pin a signal more advancing in phase than the A pin.

#### • PA0

General-purpose port A output pin. This pin can output a current of -15 mA. If this pin is used to drive an LED, insert an external current limiting resistor in series with the LED. If this pin is not used, leave it unconnected (open).

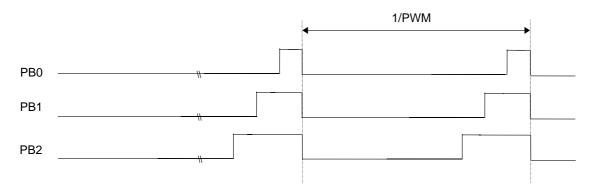

#### • PB0 to PB2

Port B pins, which are used for PWM outputs. These pins are provided for the ML9092-01/04. Any pins not to be used should be left unconnected (open).

#### • SEG1 to SEG60(56)

Segment signal output pins for LCD driving. Any pins not to be used should be left unconnected (open). For the ML9092-01, only SEG1 to SEG56 apply.

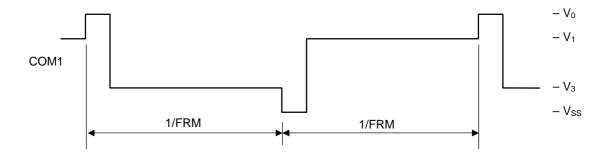

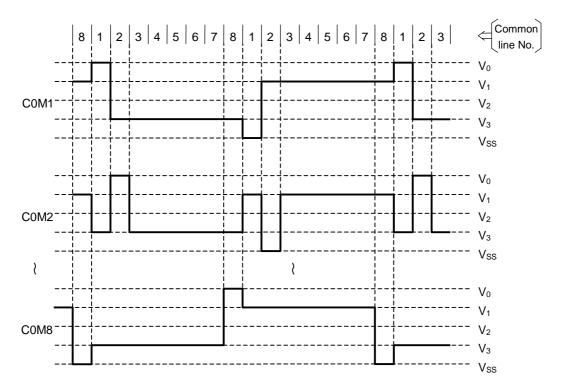

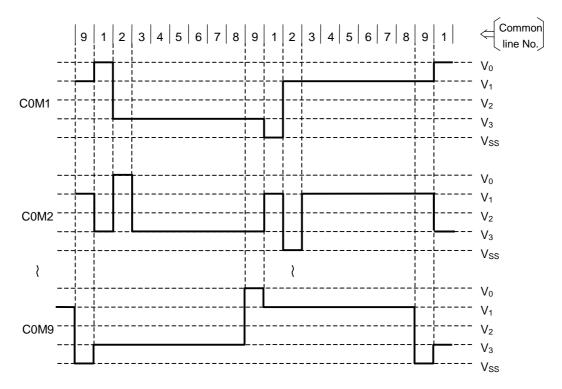

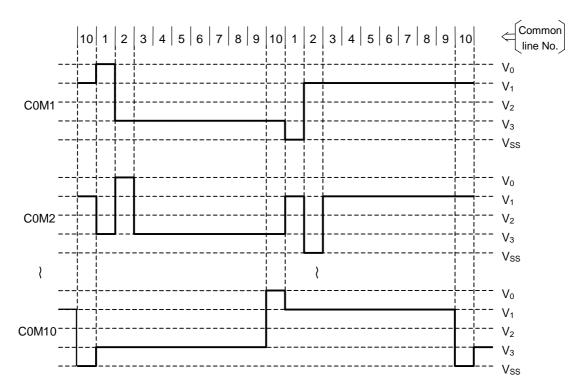

# • COM1 to COM10

Common signal output pins for LCD driving. Any pins not to be used should be left unconnected (open).

#### V<sub>DD</sub>

Logic power supply connection pin.

#### $\bullet$ $V_{SS}$

Power supply GND connection pin.

#### $\bullet$ $V_{IN}$

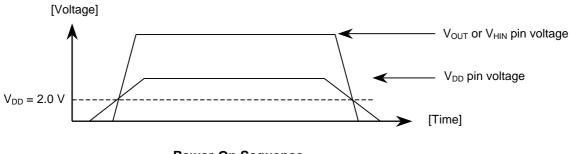

Voltage doubler reference voltage input pin. A voltage twice that which is input to this pin is output to the  $V_{OUT}$  pin. When the voltage doubler is not used, connect this pin to GND.

This pin is provided for the ML9092-01/02.

#### • V<sub>S1</sub>-

Negative connection pin for the capacitor for the voltage doubler. Connect a 4.7  $\mu$ F ( $\pm 30\%$ ) capacitor between this pin and the  $V_{Cl}$ + pin. When the voltage doubler is not used, leave this pin unconnected (open). This pin is provided for the ML9092-01/02.

#### • V<sub>C1</sub>+

Positive connection pin for the capacitor for the voltage doubler. Connect a 4.7  $\mu$ F ( $\pm 30\%$ ) capacitor between this pin and the  $V_{SI}$ – pin. When the voltage doubler is not used, leave this pin unconnected (open). This pin is provided for the ML9092-01/02.

#### $\bullet$ $V_{OUT}$

A voltage twice that which is input to the  $V_{IN}$  pin is output to this pin. Connect a 4.7  $\mu$ F capacitor between this pin and the  $V_{SS}$  pin. When the internal voltage doubler is not used, input the specified voltage to this pin from the outside. When built-in contrast adjustment (electronic volume) is used, leave the connection between this pin and the  $V_0$  pin open. The LCD drive voltage will be output from the  $V_0$  pin according to the contrast adjustment value. When built-in contrast adjustment is not used, connect this pin with the  $V_0$  pin. This pin is provided for the ML9092-01/02.

#### • V<sub>0</sub>, V<sub>2</sub>

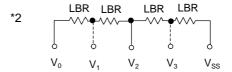

LCD bias pins. A bias dividing resistor is connected to these pins. These pins are provided for the ML9092-01/02/04.

#### $\bullet$ $V_{HIN}$

LCD drive high voltage power supply connection pin. When built-in contrast adjustment (electronic volume) is used, input the LCD drive power supply voltage to this pin. The LCD drive voltage will be output from the  $V_0$  pin according to the contrast adjustment value. When built-in contrast adjustment is not used, strap the  $V_{HIN}$  pin and  $V_0$  pin outside the IC, and input the LCD drive voltage into both pins. This pin is provided for the ML9092-03/04.

#### • $V_0, V_1, V_2, V_3$

LCD bias pins. A bias dividing resistor is connected to these pins. When using a large-screen LCD, however, input the LCD bias voltage from outside the IC to these pins. This is applicable to the ML9092-03.

# ABSOLUTE MAXIMUM RATINGS

| Parameter                            | Parameter Symbol         |           | Rating                                             | Unit     | Applicable Pins                                                                      |

|--------------------------------------|--------------------------|-----------|----------------------------------------------------|----------|--------------------------------------------------------------------------------------|

| Power Supply Voltage                 | $V_{DD}$                 | Ta = 25°C | -0.3 to +6.5                                       | V        | $V_{DD}$                                                                             |

| High Power Supply Voltage            | V <sub>H</sub>           | Ta = 25°C | -0.3 to +18.0                                      | V        | V <sub>OUT</sub> , V <sub>HIN</sub>                                                  |

| Bias Voltage                         | $V_{BI}$                 | Ta = 25°C | -0.3 to V <sub>OUT</sub> (V <sub>HIN</sub> ) + 0.3 | >        | V <sub>C1</sub> +, V <sub>0</sub> , V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub> |

| Voltage Doubler Reference<br>Voltage | V <sub>IN</sub>          | Ta = 25°C | $-0.3$ to $V_{DD} + 0.3$                           | <b>V</b> | V <sub>IN</sub>                                                                      |

| Input Voltage                        | Vı                       | Ta = 25°C | -0.3 to V <sub>DD</sub> + 0.3                      | ٧        | CS, CP, DI/O, OSC1,<br>C0 to C3,<br>C0 to C4, C0/D0 to<br>C4/D4, KPS, A, B,<br>RESET |

|                                      |                          | Ta = 25°C | -20 to +3                                          | mA       | PA0                                                                                  |

| Output Current                       | I <sub>O</sub> Ta = 25°C |           | −3 to +4                                           | mA       | PB0 to PB2, R0/C0 to<br>R4/C4, C0/D0 to<br>C4/D4, R0 to R4,<br>R0 to R5, DI/O, KREQ  |

| Power Dissipation                    | P <sub>D</sub>           | Ta = 85°C | 190                                                | mW       | _                                                                                    |

| Storage Temperature                  | T <sub>stg</sub>         | _         | -55 to +150                                        | °C       | _                                                                                    |

$V_{\text{SS}}$  is the reference voltage potential for all pins.

# RECOMMENDED OPERATING CONDITIONS

| Parameter                                                               | Parameter Symbol Condition      |                                                                                                                                    | Range                   | Unit | Applicable Pins   |

|-------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|-------------------|

| Power Supply Voltage                                                    | ipply Voltage V <sub>DD</sub> — |                                                                                                                                    | 4.5 to 5.5              | V    | $V_{DD}$          |

|                                                                         |                                 | Voltage doubler<br>not used<br>(Contrast<br>adjustment used)                                                                       | 4.5 to 16.5             | V    | V <sub>оит</sub>  |

| Externally Input Power<br>Supply Voltage 1<br>(Applies to ML9092-01/02) | Vоит                            | Voltage doubler<br>not used & V <sub>OUT</sub><br>pin connected<br>with V <sub>0</sub> pin<br>(Contrast<br>adjustment not<br>used) | 4.0 to 16.5             | V    | $V_{OUT}, V_{0}$  |

|                                                                         |                                 | Contrast adjustment used                                                                                                           | 4.5 to 16.5             | V    | V <sub>HIN</sub>  |

| Externally Input Power<br>Supply Voltage 2<br>(Applies to ML9092-03/04) | V <sub>HIN</sub>                | Contrast adjustment not used (V <sub>HIN</sub> pin connected with V <sub>0</sub> pin)                                              | 4.0 to 16.5             | V    | $V_{HIN}$ , $V_0$ |

| Bias Voltage                                                            | V <sub>0</sub>                  | _                                                                                                                                  | 4.0 to 16.5             | V    | V <sub>0</sub>    |

| Voltage Doubler Input<br>Voltage                                        | .   V <sub>IN</sub>   —         |                                                                                                                                    | $0.8V_{DD}$ to $V_{DD}$ | V    | V <sub>IN</sub>   |

| Operating Frequency of<br>External Clock                                | f <sub>OPE</sub>                | _                                                                                                                                  | 210 to 445              | kHz  | OSC1              |

| Oscillation Resistance                                                  | R                               | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}$                                                                                           | 56 <sup>*1</sup>        | kΩ   | OSC1, OSC2        |

| Operating Temperature T <sub>op</sub> —                                 |                                 | -40 to +85                                                                                                                         | °C                      | _    |                   |

$V_{\text{SS}}$  is the reference voltage potential for all pins.

\*1: Use a resistor with an accuracy of  $\pm 2 \%$

# **ELECTRICAL CHARACTERISTICS**

### **Oscillating Frequency Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter             | Symbol | Condition                           |     | Тур. | Max. | Unit | Applicable Pins |

|-----------------------|--------|-------------------------------------|-----|------|------|------|-----------------|

| Oscillating Frequency | 4      | 56 kΩ                               | 210 | 306  | 445  | kHz  | OSC1, OSC2      |

|                       | Tosc   | (resistor with accuracy within ±2%) | 210 | 300  | 443  | KIIZ | 0301, 0302      |

### **DC** Characteristics

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

|                     | $(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT}(V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40.000$ |                                                          |                     |       | 0.5  V,  1a = -40  10 + 65   C) |      |                                                                   |

|---------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------|-------|---------------------------------|------|-------------------------------------------------------------------|

| Parameter           | Symbol                                                                                                     | Condition                                                | Min.                | Тур.  | Max.                            | Unit | Applicable Pins                                                   |

| "H" Input Voltage 1 | V <sub>IH1</sub>                                                                                           | When input externally                                    | 0.85V <sub>DD</sub> | _     | _                               | V    | OSC1                                                              |

| "H" Input Voltage 2 | $V_{\text{IH2}}$                                                                                           | _                                                        | 0.85V <sub>DD</sub> | _     | _                               | V    | RESET                                                             |

| "H" Input Voltage 3 | V <sub>IH3</sub>                                                                                           | _                                                        | 0.85V <sub>DD</sub> | _     | _                               | V    | CP, A, B, C0–C3,<br>C0/D0–C4/D4,C0–C4<br>CS, DI/O                 |

| "H" Input Voltage 4 | $V_{IH4}$                                                                                                  | _                                                        | $0.8V_{DD}$         | _     | _                               | V    | KPS                                                               |

| "L" Input Voltage 1 | V <sub>IL1</sub>                                                                                           | When input externally                                    | _                   | _     | 0.15V <sub>DD</sub>             | V    | OSC1                                                              |

| "L" Input Voltage 2 | $V_{\text{IL}2}$                                                                                           | _                                                        | _                   | _     | 0.15V <sub>DD</sub>             | V    | RESET                                                             |

| "L" Input Voltage 3 | V <sub>IL3</sub>                                                                                           | _                                                        | _                   | _     | 0.15V <sub>DD</sub>             | V    | $\overline{\text{CP,}}$ A , B, $\overline{\text{CS,}}$ DI/O,      |

| "L" Input Voltage 4 | $V_{IL4}$                                                                                                  | _                                                        | _                   | _     | 0.2V <sub>DD</sub>              | V    | KPS                                                               |

| "L" Input Voltage 5 | V <sub>IL5</sub>                                                                                           | _                                                        | _                   | _     | 0.23V <sub>DD</sub>             | V    | C0/D0-C4/D4,C0-C3,<br>C0-C4                                       |

| "H" Input Current 1 | I <sub>IH1</sub>                                                                                           | $V_I = V_{DD}$                                           | _                   | _     | 10                              | μA   | RESET                                                             |

| "H" Input Current 2 | I <sub>IH2</sub>                                                                                           | $V_I = V_{DD}$                                           | _                   | _     | 10                              | μA   | C0/D0-C4/D4,<br>C0-C3, C0-C4                                      |

| "H" Input Current 3 | I <sub>IH3</sub>                                                                                           | DI/O = Input mode,<br>AII ports = HiZ,<br>$V_I = V_{DD}$ | _                   | _     | 10                              | μA   | DI/O, PA0, PB0–PB2,<br>R0/C0–R4/C4,<br>C0/D0–C4/D4                |

| "H" Input Current 4 | I <sub>IH4</sub>                                                                                           | $V_I = V_{DD}$                                           | _                   | _     | 1                               | μA   | OSC1, $\overline{\text{CS}}$ , $\overline{\text{CP}}$ , KPS, A, B |

| "L" Input Current 1 | I <sub>IL1</sub>                                                                                           | $V_{DD} = 5 \text{ V}, V_{I} = 0 \text{ V}$              | -0.1                | -0.05 | -0.02                           | mA   | RESET                                                             |

| "L" Input Current 2 | I <sub>IL2</sub>                                                                                           | $V_{DD} = 5 \text{ V}, V_{I} = 0 \text{ V}$              | -0.9                | -0.45 | -0.18                           | mA   | C0/D0-C4/D4,<br>C0-C3,C0-C4                                       |

| "L" Input Current 3 | I <sub>IL3</sub>                                                                                           | DI/O = Input mode,<br>AII ports = HiZ,<br>$V_1 = 0 V$    | -10                 | _     | _                               | μA   | DI/O, PA0, PB0–PB2,<br>R0/C0–R4/C4,<br>C0/D–C4/D4                 |

| "L" Input Current 4 | I <sub>IL4</sub>                                                                                           | V <sub>I</sub> = 0 V                                     | -1                  | _     | _                               | μA   | OSC1, $\overline{\text{CS}}$ , $\overline{\text{CP}}$ , KPS, A, B |

| Parameter            | Symbol           | Condition                                                                                           | Min.                  | Тур. | Max.        | Unit | Applicable Pins                                                          |

|----------------------|------------------|-----------------------------------------------------------------------------------------------------|-----------------------|------|-------------|------|--------------------------------------------------------------------------|

| "H" Output Voltage 1 | V <sub>OH1</sub> | $I_O = -0.4 \text{ mA}$                                                                             | V <sub>DD</sub> – 0.4 | —    | —           | V    | DI/O, KREQ                                                               |

| "H" Output Voltage 2 | V <sub>OH2</sub> | $I_{O} = -40  \mu A$                                                                                | 0.9V <sub>DD</sub>    | _    | _           | V    | OSC2                                                                     |

| "H" Output Voltage 3 | V <sub>OH3</sub> | $I_0 = -15 \text{ mA}$                                                                              | V <sub>DD</sub> – 1.7 | _    | _           | V    | PA0                                                                      |

| "H" Output Voltage 4 | V <sub>OH4</sub> | I <sub>O</sub> = -2 mA<br>(When R0/C0–<br>R4/C4 and<br>C0/D0–C4/D4 are<br>used as ports C<br>and D) | V <sub>DD</sub> – 1.2 | _    | _           | V    | Only applies to<br>ML9092-01.<br>PB0-PB2,<br>R0/C0-R4/C4,<br>C0/D0-C4/D4 |

| "H" Output Voltage 5 | V <sub>OH5</sub> | $I_O = -50 \mu A$<br>(When R0/C0–<br>R4/C4 are used<br>for key scanning)                            | V <sub>DD</sub> – 2.0 | _    | _           | V    | R0/C0-R4/C4(-01),<br>R0-R5 (-02, -03)<br>R0-R4 (-04)                     |

| "L" Output Voltage 1 | V <sub>OL1</sub> | $I_0 = 0.4 \text{ mA}$                                                                              | _                     | _    | 0.4         | V    | DI/O, KREQ                                                               |

| "L" Output Voltage 2 | V <sub>OL2</sub> | I <sub>O</sub> = 40 μA                                                                              | _                     | _    | $0.1V_{DD}$ | V    | OSC2                                                                     |

| "L" Output Voltage 3 | V <sub>OL3</sub> | I <sub>O</sub> = 1 mA<br>(When R0/C0–<br>R4/C4 and<br>C0/D0–C4/D4 are<br>used as ports C<br>and D)  | _                     | _    | 0.4         | V    | PA0, PB0-PB2,<br>C0/D0-C4/D4,<br>R0/C0-R4/C4                             |

| "L" Output Voltage 4 | V <sub>OL4</sub> | I <sub>O</sub> = 2.7 mA<br>(When R0/C0–<br>R4/C4 are used<br>for key scanning)                      |                       | _    | 0.3         | V    | R0/C-R4/C4 (-01),<br>R0-R5 (-02, -03)<br>R0-R4 (-04)                     |

ML9092-01/02/03/04

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}\text{C})$

| $(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ia = -40 \text{ to } +8$ |                    |                                                                    |                         |      |                         |      |                    |

|------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------|-------------------------|------|-------------------------|------|--------------------|

| Parameter                                                                                                              | Symbol             | Condition                                                          | Min.                    | Тур. | Max.                    | Unit | Applicable<br>Pins |

|                                                                                                                        | $V_{OS0}$          | $I_O = -10 \mu A$                                                  | $V_0 - 0.6$             |      | _                       | V    | SEG1-SEG56         |

| Segment Output                                                                                                         | V <sub>OS1</sub>   | I <sub>O</sub> = ±10 μA                                            | $2/4V_0 - 0.6$          | _    | 2/4V <sub>0</sub> + 0.6 | V    | (SEG60 for         |

| Voltage 2<br>(1/5 bias)                                                                                                | V <sub>OS2</sub>   | I <sub>O</sub> = ±10 μA                                            | 2/4V <sub>0</sub> - 0.6 | _    | 2/4V <sub>0</sub> + 0.6 | V    | ML9092-02/03       |

| ,                                                                                                                      | V <sub>OS3</sub>   | I <sub>O</sub> = +10 μA                                            | _                       | _    | V <sub>SS</sub> + 0.6   | V    | /04)               |

| -                                                                                                                      | V <sub>OC0</sub>   | I <sub>O</sub> = -10 μA                                            | V <sub>0</sub> -0.3     | _    | _                       | V    |                    |

| Common Output                                                                                                          | V <sub>OC1</sub>   | I <sub>O</sub> = ±10 μA                                            | $3/4V_0 - 0.3$          | _    | 3/4V <sub>0</sub> + 0.3 | V    | COM1-              |

| Voltage 1<br>(1/4 bias)                                                                                                | V <sub>OC2</sub>   | I <sub>O</sub> = ±10 μA                                            | 1/4V <sub>0</sub> – 0.3 | _    | 1/4V <sub>0</sub> + 0.3 | V    | COM10              |

| ,                                                                                                                      | V <sub>OC3</sub>   | I <sub>O</sub> = +10 μA                                            | _                       | _    | V <sub>SS</sub> + 0.3   | V    |                    |

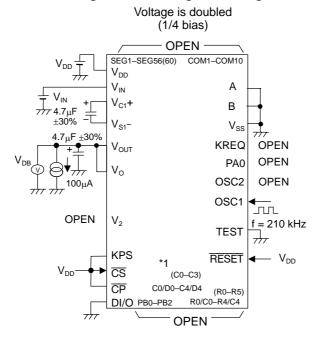

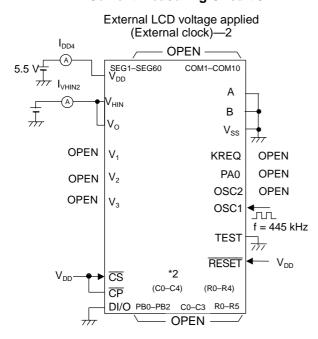

| Supply Current 1<br>(Applies to<br>ML9092-01/02)                                                                       | I <sub>DD1</sub>   | R = 56 kΩ Voltage doubler operating, No load *1                    | _                       | _    | 0.6                     | mA   | $V_{DD}$           |

| Supply Current 2<br>(Applies to<br>ML9092-01/02)                                                                       | I <sub>DD2</sub>   | External clock = 445 kHz Voltage doubler operating, No load *2     | _                       | _    | 0.6                     | mA   | $V_{DD}$           |

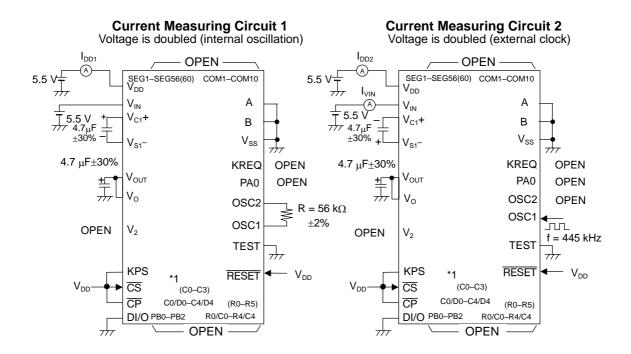

| Supply Current 3<br>(Applies to<br>ML9092-01/02)                                                                       | I <sub>VIN</sub>   | External clock = 445 kHz Voltage doubler operating, No load *2     | _                       | _    | 2                       | mA   | V <sub>IN</sub>    |

| Supply Current 4<br>(Applies to<br>ML9092-01/02)                                                                       | I <sub>VHIN1</sub> | External clock = 445 kHz Voltage doubler not operating, No load *3 | _                       | _    | 1                       | mA   | V <sub>OUT</sub>   |

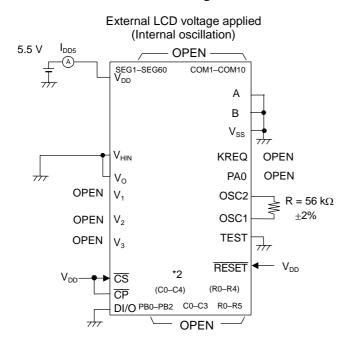

| Supply Current 5<br>(Applies to<br>ML9092-03/04)                                                                       | I <sub>DD3</sub>   | R = 56 k $\Omega$<br>No load *4                                    | _                       | _    | 0.6                     | mA   | $V_{DD}$           |

| Supply Current 6<br>(Applies to<br>ML9092-03/04)                                                                       | I <sub>DD4</sub>   | External clock = 445 kHz<br>No load *5                             | _                       | _    | 0.6                     | mA   | $V_{DD}$           |

| Supply Current 7<br>(Applies to<br>ML9092-03/04)                                                                       | I <sub>VHIN2</sub> | External clock = 445 kHz<br>No load *5                             | _                       |      | 1                       | mA   | V <sub>HIN</sub>   |

| Supply Current 8<br>(Applies to<br>ML9092-03/04)                                                                       | I <sub>DD5</sub>   | $R = 56 \text{ k}\Omega$ Voltage doubler not operating, No load *6 | _                       | _    | 100                     | μΑ   | $V_{DD}$           |

- \*1: Refer to the Current Measuring Circuit 1.

- \*2: Refer to the Current Measuring Circuit 2.

- \*3:

- \*4:

- \*5:

- Refer to the Current Measuring Circuit 2.

Refer to the Current Measuring Circuit 3.

Refer to the Current Measuring Circuit 4.

Refer to the Current Measuring Circuit 5.

Refer to the Current Measuring Circuit 6.

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter                             | Symbol              | Condition                                                                                                                                                 | Min.                        | Тур.      | Max.                     | Unit | Applicable<br>Pins               |

|---------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------|--------------------------|------|----------------------------------|

| Voltage doubler<br>Voltage            | $V_{DB}$            | External clock = 210 kHz<br>$V_{IN} = 0.8 V_{DD}$ to $V_{DD}$<br>(*1)                                                                                     | V <sub>IN</sub> × 1.9 – 0.5 | 9.8<br>*3 | $V_{\text{IN}} \times 2$ | V    | V <sub>OUT</sub>                 |

| LCD driving voltage when              | V <sub>LCDMAX</sub> | V <sub>DD</sub> = 5 V, V <sub>OUT</sub> = 10 V<br>(Voltage doubler not<br>operating, but voltage<br>applied externally)<br>Contrast data = FH,<br>No load | 9.5                         | 9.8       | 10                       | V    | V. V                             |

| internal variable<br>resistor is used | V <sub>LCDMIN</sub> | V <sub>DD</sub> = 5 V, V <sub>OUT</sub> = 10 V<br>(Voltage doubler not<br>operating, but voltage<br>applied externally)<br>Contrast data = 0H,<br>No load | 6.7                         | 7         | 7.3                      | V    | V <sub>0</sub> – V <sub>SS</sub> |

| LCD Driving<br>Bias Resistance        | LBR                 | (*2)                                                                                                                                                      | 5                           | 9         | 14                       | kΩ   | $V_0 - V_{ss}$                   |

Refer to the Voltage Doubler Voltage Measuring Circuit.  $V_{\text{IN}} = 5 \text{ V}, \, \text{Ta} = 25^{\circ}\text{C}$ \*1

<sup>\*3</sup>

#### **Measuring Circuits**

#### **Voltage Doubler Voltage Measuring Circuit**

\*1: For ML9092-01, these are SEG1–56, PB0–PB2, KPS, C0/D0–C4/D4, and R0/C0–R4/C4. For ML9092-02, these are SEG1–60, C0–C3, and R0–R5; PB0–PB2 and KPS are not provided.

#### **Current Measuring Circuit 3 Current Measuring Circuit 4** External LCD voltage applied External LCD voltage applied (External clock) (Internal oscillation) OPEN **OPEN** SEG1-SEG56(60) COM1-COM10 $V_{DD}$ SEG1-SEG60 COM1-COM10 $V_{DD}$ Α $V_{IN}$ **OPEN** $V_{C1}$ + $'_{\mathsf{HIN}}$ В В $V_{\text{SS}} \\$ $V_{SS}$ Vo **OPEN** $V_{S1}$ **OPEN** $I_{VHIN1}$ **KREQ OPEN** KREQ OPEN (A) $V_{OUT}$ OPEN PA0 **OPEN** PA0 **OPEN** Vo OSC<sub>2</sub> **OPEN** R = 56 kΩ OSC<sub>2</sub> **OPEN** OSC1 بمد ±2% OSC<sub>1</sub> $V_2$ **OPEN** f = 445 kHz **TEST TEST KPS** RESET RESET \*2 $V_{DD}$ CS $V_{DD}$ CS (C0-C3) (C0-C4) (R0-R4) СP C0/D0-C4/D4 СP (R0-R5) C0-C3 DI/O PB0-PB2 R0/C0-R4/C4 DI/O PB0-PB2

**OPEN**

#### **Current Measuring Circuit 5**

OPEN -

- \*1: For ML9092-01, these are SEG1–56, PB0–PB2, KPS, C0/D0–C4/D4, and R0/C0–R4/C4. For ML9092-02, these are SEG1–60, C0–C3, and R0–R5; PB0–PB2 and KPS are not provided.

- \*2: For ML9092-03, these are C0–C3 and R0–R5; PB0–PB2 are not provided. For ML9092-04, these are C0–C4 and R0–R4; PB0–PB2 are provided.

ML9092-01/02/03/04

# **Current Measuring Circuit 6**

\*2: For ML9092-03, these are C0–C3 and R0–R5; PB0–PB2 are not provided. For ML9092-04, these are C0–C4 and R0–R4; PB0–PB2 are provided.

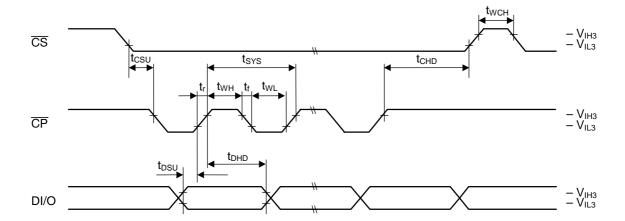

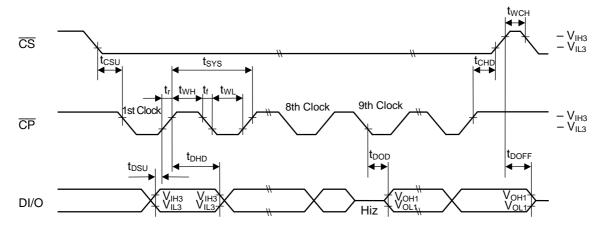

# **Switching Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

|                                | ( • 00                            |            | 1111/ |      | ,    |

|--------------------------------|-----------------------------------|------------|-------|------|------|

| Parameter                      | Symbol                            | Condition  | Min.  | Max. | Unit |

| CP Clock Cycle Time            | t <sub>SYS</sub>                  | _          | 500   | _    | ns   |

| CP "H" Pulse Width             | t <sub>WH</sub>                   | _          | 200   | _    | ns   |

| CP "L" Pulse Width             | t <sub>WL</sub>                   | _          | 200   | _    | ns   |

| CS "H" Pulse Width             | t <sub>WCH</sub>                  | _          | 100   | _    | ns   |

| CP Clock Rise/fall Time        | t <sub>r</sub> , t <sub>f</sub>   | _          | _     | 50   | ns   |

| CS Setup Time                  | t <sub>CSU</sub>                  | _          | 30    | _    | ns   |

| CS Hold Time                   | t <sub>CHD</sub>                  | _          | 150   | _    | ns   |

| DI/O Setup Time                | t <sub>DSU</sub>                  | _          | 50    | _    | ns   |

| DI/O Hold Time                 | t <sub>DHD</sub>                  | _          | 50    | _    | ns   |

| DI/O Output Delay Time         | t <sub>DOD</sub>                  | CL = 50 pF | _     | 100  | ns   |

| DI/O Output OFF Delay Time     | t <sub>DOFF</sub>                 | CL = 50 pF | _     | 100  | ns   |

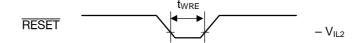

| RESET Pulse Width              | t <sub>WRE</sub>                  | _          | 2     | _    | μS   |

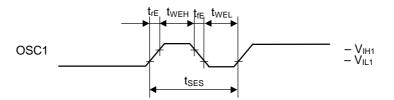

| External Clock Cycle Time      | t <sub>SES</sub>                  | _          | 1612  | 3389 | ns   |

| External Clock "H" Pulse Width | t <sub>WEH</sub>                  | _          | 645   | _    | ns   |

| External Clock "L" Pulse Width | t <sub>WEL</sub>                  | _          | 645   | _    | ns   |

| External Clock Rise/fall Time  | t <sub>rE</sub> , t <sub>fE</sub> | _          | _     | 50   | ns   |

# **Key Scan Characteristics**

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

| Parameter       | Symbol | Register setting | Dividing ratio | Osc     | Unit   |         |    |

|-----------------|--------|------------------|----------------|---------|--------|---------|----|

|                 |        | KT               |                | 210 kHz | 306kHz | 445 kHz |    |

| Kay Coop Daried | т      | 0                | 1/1536         | 7.3     | 5.0    | 3.5     |    |

| Key Scan Period | I scn  | 1                | 1/3072         | 14.6    | 10.0   | 6.9     | ms |

# Frame Frequency, PWM Frequency, and Voltage Doubler Frequency Characteristics

$(V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{OUT} (V_{HIN}) = 4.5 \text{ to } 16.5 \text{ V}, Ta = -40 \text{ to } +85^{\circ}C)$

|                        |                                 |        | (*00 –       | 10 0.0 1, 100  | 1 ( • 1 111 4) = • | .0 10 10.0 1,         | 14 - 10 10 |      |  |  |  |  |

|------------------------|---------------------------------|--------|--------------|----------------|--------------------|-----------------------|------------|------|--|--|--|--|

| Model                  | Parameter                       | Symbol | Display duty | Dividing ratio | Oso                | Oscillation frequency |            |      |  |  |  |  |

| Model                  | Model Parameter                 |        | Display duty | Dividing ratio | 210 kHz            | 306 kHz               | 445 kHz    | Unit |  |  |  |  |

| MI 0002                | _                               |        | 1/8          | 1/2560         | 82                 | 120                   | 174        |      |  |  |  |  |

| ML9092-<br>01/02/03/04 | Frame<br>Frequency              | FRM    | 1/9          | 1/2520         | 83                 | 121                   | 177        |      |  |  |  |  |

| 01/02/03/04            | 02/03/04 Frequency              |        | 1/10         | 1/2560         | 82                 | 120                   | 174        |      |  |  |  |  |

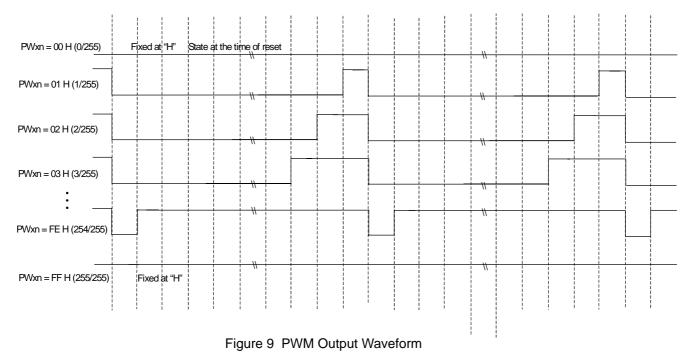

| ML9092-<br>01/04       | PWM<br>Frequency                | PWM    | _            | 1/1020         | 205                | 300                   | 436        | Hz   |  |  |  |  |

| ML9092-<br>01/02       | Voltage<br>Doubler<br>Frequency | _      | _            | 1/64           | 3281               | 4781                  | 6953       |      |  |  |  |  |

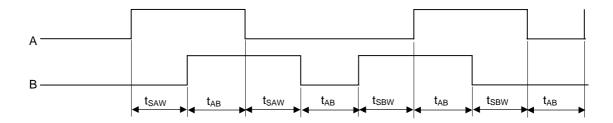

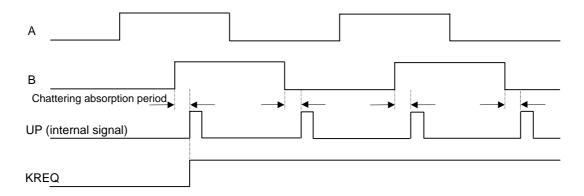

# **Switching Characteristics of Rotary Switch**

(V<sub>DD</sub> = 4.5 to 5.5 V, V<sub>OUT</sub> (V<sub>HIN</sub>) = 4.5 to 16.5 V, Ta = -40 to  $+85^{\circ}$ C)

| Parameter                       | Symbol           | Condition                         | Min. | Тур. | Max. | Unit |

|---------------------------------|------------------|-----------------------------------|------|------|------|------|

| Phase Recognition Time (A to B) | t <sub>SAW</sub> |                                   | 950  | _    | _    | μS   |

| Phase Recognition Time (B to A) | t <sub>SBW</sub> | $R = 56 \text{ k}\Omega \pm 2\%,$ | 950  | _    | _    | μS   |

| Phase Input Fixed Time          | t <sub>AB</sub>  |                                   | 950  | _    | _    | μS   |

# Clock synchronous serial interface timing diagrams

Clock synchronous serial interface input timing

Clock synchronous serial interface input-output timing

# Reset timing

#### External clock

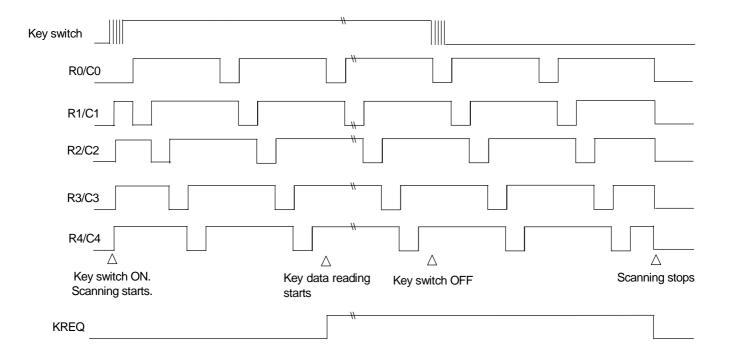

# **Key scan timing**

# Frame frequency

# PWM output frequency for port B (applies to ML9092-01/04)

# Rotary switch input timing

### **Instruction Code List (ML9092-01)**

|     |                        |       |    | Instr   | uction  | Cod     | е      |         |   |           |           |           | Data     |          |          |          |          |                                                                                                                                                                                                                             |

|-----|------------------------|-------|----|---------|---------|---------|--------|---------|---|-----------|-----------|-----------|----------|----------|----------|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. | Instruction            | Fixed |    | R/W     |         |         | ster N |         |   | -         |           |           |          | -        |          |          |          | Description                                                                                                                                                                                                                 |

| 0   | Key scan register read | 1     | D6 | D5<br>1 | D4<br>0 | D3<br>0 | 0      | D1<br>0 | 0 | D7<br>ST2 | D6<br>ST1 | D5<br>ST0 | D4<br>S4 | D3<br>S3 | D2<br>S2 | D1<br>S1 | D0<br>S0 | Reads scan read timing bits (ST0 to ST2) and key scan data (S0 to S4) of the key scan register.                                                                                                                             |

| 1   | Display data RAM write | 1     | 1  | 0       | 0       | 0       | 0      | 0       | 1 | D7        | D6        | D5        | D4       | D3       | D2       | D1       | D0       | Writes display data (D0 to D7) in the display data RAM after setting the X address of Y address.                                                                                                                            |

| 1   | Display data RAM read  | 1     | 1  | 1       | 0       | 0       | 0      | 0       | 1 | D7        | D6        | D5        | D4       | D3       | D2       | D1       | D0       | Reads display data (D0 to D7) from the display data RAM after setting the X address of Y address.                                                                                                                           |

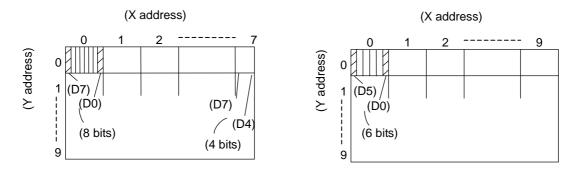

| 2   | X address register set | 1     | 1  | 0       | 0       | 0       | 0      | 1       | 0 | ı         | -         | -         | ı        | ХЗ       | X2       | X1       | X0       | Sets the X address (X0 to X3) of the display data RAM.                                                                                                                                                                      |

| 3   | Y address register set | 1     | 1  | 0       | 0       | 0       | 0      | 1       | 1 | ı         | -         | ı         | ı        | Y3       | Y2       | Y1       | Y0       | Sets the Y address (Y0 to Y3) of the display data RAM.                                                                                                                                                                      |

| 4   | Port register A set    | 1     | 1  | 0       | 0       | 0       | 1      | 0       | 0 | 1         | 1         | -         | 1        | 1        | -        | -        | PTA0     | Controls the output of the general-purpose port A (PTA0).                                                                                                                                                                   |

| 5   | Port register B set    | 1     | 1  | 0       | 0       | 0       | 1      | 0       | 1 | -         | -         | -         | -        | -        | PTB2     | PTB1     | PTB0     | Controls the output of the general-purpose port B (PTB0 to PTB2).                                                                                                                                                           |

| 6   | Port register C set    | 1     | 1  | 0       | 0       | 0       | 1      | 1       | 0 | -         | -         | -         | PTC4     | PTC3     | PTC2     | PTC1     | PTC0     | Controls the output of the general-purpose port C (PTC0 to PTC4)                                                                                                                                                            |

| 7   | Port register D set    | 1     | 1  | 0       | 0       | 0       | 1      | 1       | 1 | 1         | -         | -         | PTD4     | PTD3     | PTD2     | PTD1     | PTD0     | Controls the output of the general-purpose port D (PTD0 to PTD4).                                                                                                                                                           |

| 8   | Control register 1 set | 1     | 1  | 0       | 0       | 1       | 0      | 0       | 0 | INC       | WLS       | КТ        | SHL      | BE       | PE       | DTY1     | DTY0     | Sets the address increment X or Y direction (INC), display data word length (MLS), key scan time (KT), common driver shift direction (SHL), voltage doubler control (BE), port control (PE), and display duty (DTY0, DTY1). |

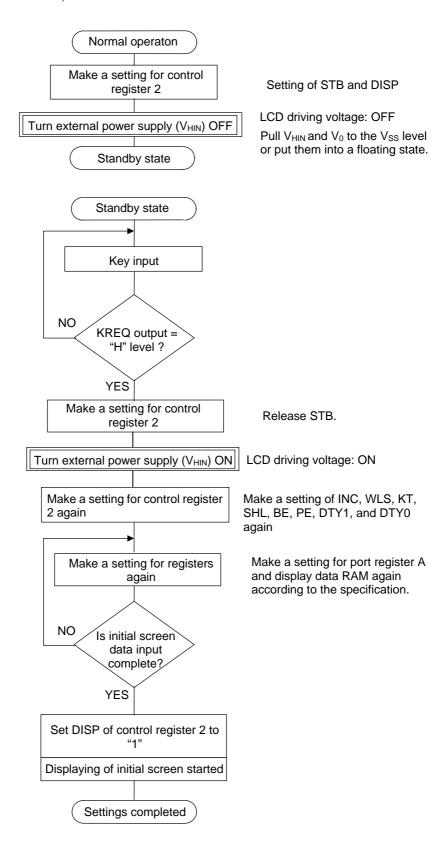

| 9   | Control register 2 set | 1     | 1  | 0       | 0       | 1       | 0      | 0       | 1 | 0         | 0         | 0         | 0        | 0        | 0        | 0        | DISP     | Sets display ON/OFF (DISP).                                                                                                                                                                                                 |

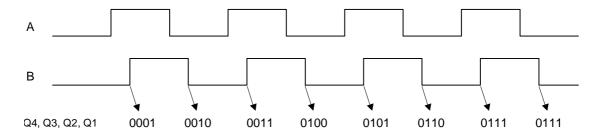

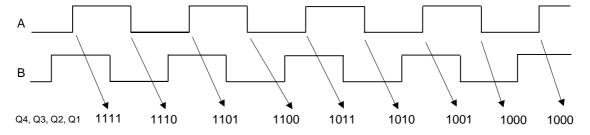

| Α   | Rotary encoder read    | 1     | 1  | 1       | 0       | 1       | 0      | 1       | 0 | Q4        | Q4        | Q4        | Q4       | Q4       | Q3       | Q2       | Q1       | Reads the counter bits (Q1 to Q4) of the rotary encoder.                                                                                                                                                                    |

| В   | Contrast ADJ set       | 1     | 1  | 0       | 0       | 1       | 0      | 1       | 1 | -         | -         | -         | -        | СТЗ      | CT2      | CT1      | СТО      | Sets contrast adjustment values with the contrast adjustment bits (CT0 to CT3).                                                                                                                                             |

| С   | PWM0 register set      | 1     | 1  | 0       | 0       | 1       | 1      | 0       | 0 | PW07      | PW06      | PW05      | PW04     | PW03     | PW02     | PW01     | PW00     | Sets the pulse width to be output from general-purpose port B (PTB0) with the bits (PW00 to PW07) of PWM0.                                                                                                                  |

| D   | PWM1 register set      | 1     | 1  | 0       | 0       | 1       | 1      | 0       | 1 | PW17      | PW16      | PW15      | PW14     | PW13     | PW12     | PW11     | PW10     | Sets the pulse width to be output from general-purpose port B (PTB1) with the bits (PW10 to PW17) of PWM1.                                                                                                                  |

| Е   | PWM2 register set      | 1     | 1  | 0       | 0       | 1       | 1      | 1       | 0 | PW27      | PW26      | PW25      | PW24     | PW23     | PW22     | PW21     | PW20     | Sets the pulse width to be output from general-purpose port B (PTB2) with the bits (PW20 to PW27) of PWM2.                                                                                                                  |

| F   | Test register set      | 1     | 1  | 0       | 0       | 1       | 1      | 1       | 1 | -         | -         | -         | T5       | T4       | Т3       | T2       | T1       | Test instruction exclusively used by manufacturer (T1 to T5). Customers must not use this instruction.                                                                                                                      |

PE

Notes:

R/W

ST0 to ST2

S0 to S4

D0 to D7

X0 to X3

Y0 to Y3

PTA0

PTB0 to PTB2

PTC0 to PTC4

PTD0 to PTD4

INC

WLS

KT

SHL : Read/write select bit

: Key scan read count display bits

: Key scan data

: Write or read data of the display data RAM

: X addresses of the display data RAM

: Y addresses of the display data RAM

: Port A data

: Port B output control

: Port C data

: Port D data

: Display data RAM address increment. 1: X direction, 0: Y direction

: Word length select bit

: Key scan period select bit

: Common driver shift direction select bit

: CCM10→COM1, 0: COM1→COM10

: Voltage doubler control bit

: Voltage doubler disable

BE

: Port enable/disable select bit 1: All ports enable 0: All ports go into high impedance for output 1: Display ON/OFF select bit 1: Display ON, 0: Display OFF select bit 1: Display ON, 0: Display OFF Rotary encoder switch count bits (2's complement) 1: Contrast adjustment bit 1: PWM/O setting bits 1: Bits for test instruction. Customers should not access these bits. DTY0, DTY1 DISP Q1 to Q4 CT0 to CT3 PW00 to PW07 PW10 to PW17 PW20 to PW2 T1 to T5

: Don't Care

### Instruction Code List (ML9092-02/03)

|     |                        | Instruction Code |       |    |    |    |        |    |    |     |     |     | Data |      |     |       |      |                                                                                                                                                                                                                                                         |

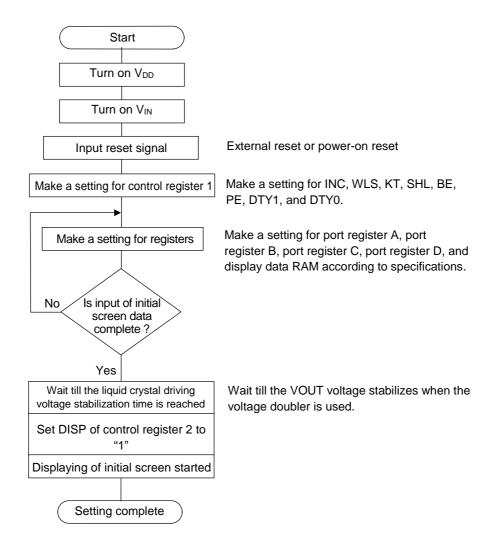

|-----|------------------------|------------------|-------|----|----|----|--------|----|----|-----|-----|-----|------|------|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|