# **MN8357**

# Half Tone Processor(HTP)

#### Outline

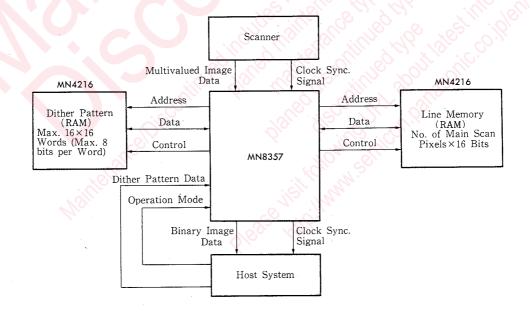

The half tone processor(HTP) MN8357 is an LSI which has a high-quality pseudo intermedicate toning (binary conversion)function, which output raster scan type multivalued image signals of facsimile and television signals to a binary output device such as Laser beam printer or static printer, and a moire eliminating function at the time of reading an image such as reticular point picture with periodicity

By combining with a scanner, the MN8357 can configure an advanced image input device which can handle various images such as character, pattern, reticular point picture, shaded picture, etc. as binary images.

#### ■ Features

- Various pseudo intermediate tone processing function CAPIX 1(Character, line drawing, picture)

CAPIX 2(Moire elimination only ... reticular point picture of printed matter, etc.)

Texture dither(Various patterns enabled by an external loading system)(For example, concentrated type, distribuled type, reticular point, etc.)

Simple binary conversion

- Input data width and processing speed Max. 8 bits/pixel, Max. 350 ns/pixel

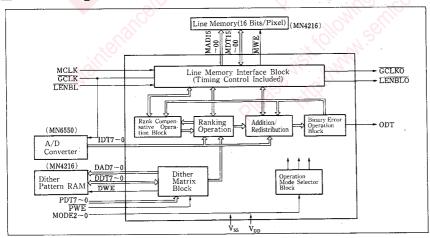

# ■ Block Diagram

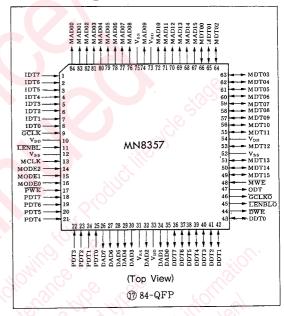

## Pin Configuration

- Wide image processing space

Horizontal scanning direction: Max. 65.536 pixels

Vertical scanning direction: Limitless

- ●84-pin flat package

# ■ Absolute Maximum Ratings( $T=25^{\circ}C$ , $V_{SS}=0$ V)

| Item                          | Symbol            | Rating                   | Unit |

|-------------------------------|-------------------|--------------------------|------|

| Supply voltage                | $V_{\mathrm{DD}}$ | -0.3~+7.0                | V    |

| Input voltage                 | V <sub>I</sub>    | $-0.3 \sim V_{DD} + 0.3$ | V    |

| Output voltage                | Vo                | $-0.3 - V_{pp} + 0.3$    | V    |

| Output current                | Io                | ±20                      | mA   |

| Power dissipation             | P <sub>D</sub>    | 500                      | mW   |

| Operating ambient temperature | $T_{opr}$         | 0~+70                    | °C   |

| Storage temperature           | $T_{\rm stg}$     | -55~+150                 | °C   |

# ■ Operating Conditions( $Ta=0\sim+70^{\circ}C$ , $V_{SS}=0V$ )

| Item                     | Symbol   | Condition | min. | typ. | max.  | Unit |

|--------------------------|----------|-----------|------|------|-------|------|

| Operating supply voltage | $V_{DD}$ |           | 4.75 | 5.0  | 5. 25 | V    |

# ■ I/O Capacitance

| Item       | Symbol           | Condition                                                              | min. | typ. | max. | Unit |

|------------|------------------|------------------------------------------------------------------------|------|------|------|------|

| Input pin  | C <sub>IN</sub>  | V -V-0V (-1 M)                                                         |      | 10   | 20   | pF   |

| Output pin | C <sub>OUT</sub> | $V_{DD} = V_I = 0V$ , $f = 1 \text{ MHz}$ , $T_a = 25^{\circ}\text{C}$ |      | 10   | 20   | pF   |

| I/O pin    | $C_{I/O}$        | 1a-25 C                                                                |      | 10   | 20   | pF   |

# ■ Electrical Characteristics

# • DC Characteristics ( $V_{DD}$ =4.75 $\sim$ 5.25 V, $V_{SS}$ =0 V, Ta=0 $\sim$ +70°C)

| Item                     | Symbol          | Condition                                          | min.              | typ. | max.     | Unit |

|--------------------------|-----------------|----------------------------------------------------|-------------------|------|----------|------|

| Static supply current    | $I_{DDS}$       | $V_I = V_{DD}$ or $V_{SS}$ , $XI = V_{DD}$         |                   | 1    | 200      | μA   |

| Input voltage "H" level  | $I_{DDO}$       | $V_I = V_{DD}$ or $V_{SS}$ , $V_{DD} = 5 V$ ,      | So vy             | 35   | 70       | mA   |

| Operating annula         | 7/11.           | Output open f=20MHz                                | 7/10              | نى:  |          |      |

| Operating supply current | V <sub>IH</sub> |                                                    | $V_{\mathrm{DD}}$ | 0/11 |          | V    |

|                          | 110 010         | e die glie die die die die die die die die die d   | ×0.7              | )    |          |      |

| Input voltage "L" level  | $V_{IL}$        | 180 CO1 PY                                         | 0                 |      | $V_{DD}$ | V    |

|                          |                 | 19, 4/2 70, 40                                     | , , ,             |      | ×0.2     |      |

| Input leakage current    | $I_{LI}$        | V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub> | -10               |      | -10      | μΑ   |

| Output voltage "H" level | $V_{OH}$        | $I_O = -4 \text{ mA}$                              | 2.8               |      |          | V    |

|                          |                 | $V_I = V_{DD}$ or $V_{SS}$                         |                   |      |          | ,    |

| Output voltage "L" level | V <sub>OL</sub> | $I_O = -4 \text{ mA},$                             |                   |      | 0.5      |      |

|                          |                 | $V_I = V_{DD}$ or $V_{SS}$                         |                   |      |          | ,    |

| Output leakage current   | $I_{LO}$        | $V_{O}=HI-Z$ , $V_{O}=V_{DD}$ or $V_{SS}$          | -10               |      | -10      | μΑ   |

|                          |                 | V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub> |                   |      |          | ,    |

## • AC Characteristics

| Item                      | Symbol         | min.                    | typ. | max. | Unit |

|---------------------------|----------------|-------------------------|------|------|------|

| MCLK ✓ to GCLK setup time | t <sub>o</sub> | 25                      |      |      | ns   |

| GCLK cycle time           | t <sub>1</sub> | t <sub>16*7</sub> (350) |      |      | ns   |

| GCLK "L" pulse width      | t <sub>2</sub> | t <sub>16</sub>         |      |      | ns   |

| GCLK "H" pulse width      | t <sub>3</sub> | t <sub>16</sub>         |      |      | ns   |

# • AC Characteristics(Continued)

| Item                          | Symbol          | min.                                  | typ.             | max.  | Unit |

|-------------------------------|-----------------|---------------------------------------|------------------|-------|------|

| GCLK to IDT steup time        | t <sub>4</sub>  | 0                                     |                  |       | ns   |

| GCLK to IDT hold time         | t <sub>5</sub>  | t <sub>16*2</sub>                     |                  |       | ns   |

| GCLK to GCLKO                 | t <sub>6</sub>  | 0                                     |                  | 50    | ns   |

| GCLK / to GCLKO/              | t <sub>7</sub>  | 0                                     |                  | 50    | ns   |

| GCLKO to ODT                  | t <sub>8</sub>  | 0                                     |                  | 50    | ns   |

| LENBL "H" pules width         | t <sub>9</sub>  | t <sub>16*22</sub>                    |                  |       | ns   |

| LENBL to LENBLO               | t <sub>10</sub> | 0                                     |                  | 50    | ns   |

| LENBL / to LENBLO /           | t <sub>11</sub> | 0                                     |                  | 50    | ns   |

| GCLK to LENBL setup           | t <sub>12</sub> | 50                                    |                  | 100   | ns   |

| time                          |                 |                                       |                  | 5     |      |

| GCLK to LENBL hold time       | t <sub>13</sub> | t <sub>16*7</sub>                     |                  | 1000  | ńs   |

| LENBL to MODE steup           | t <sub>14</sub> | t <sub>16*22</sub>                    |                  |       | ns   |

| time                          |                 |                                       | * ////           |       |      |

| LENBL ✓ to MODE hold time     | t <sub>15</sub> | t <sub>16*22</sub>                    | 7/10,            |       | ns   |

| MCLK cycle time               | t <sub>16</sub> | 50                                    | ,,O <sup>1</sup> | 2000  | ns   |

| MCLK "H" pulse width          | t <sub>17</sub> | 20                                    |                  |       | ns   |

| MCLK "L" pules width          | t <sub>18</sub> | 20                                    |                  |       | ns   |

| PWE to MODE stetup time       | t <sub>19</sub> | 100                                   | 56               |       | ns   |

| PWE / to MODE hold time       | t <sub>20</sub> | 50                                    |                  |       | ns   |

| PWE cycle time                | t <sub>21</sub> | 400                                   | 0,0              | ď     | ns   |

| PWE to PDT setup time         | t <sub>22</sub> | 000                                   | 4 416            |       | ns   |

| PWE palse width "L"           | t <sub>23</sub> | 70                                    | 9,000            |       | ns   |

| PWE / to PDT hold time        | t <sub>24</sub> | 50                                    | 70,1100          | 762 0 | ns   |

| PWE to DWE                    | t <sub>25</sub> |                                       | 900              | 50    | ns   |

| DWE palse width "L"           | t <sub>26</sub> | t <sub>23_30</sub>                    | 76 700           | 0/1/1 | ns   |

| PWE / to DWE /                | t <sub>27</sub> | 19, 411                               |                  | 50    | ns   |

| DWE to DDT VALID time         | t <sub>28</sub> |                                       | 65 VS            |       | ns   |

| DWE to DDT INVALID time       | t <sub>29</sub> | 913 9                                 | 7 10.14          | 20    | ns   |

| PWE ✓ to DAD VALID time       | t <sub>30</sub> | ille                                  |                  | 200   | ns   |

| DWE ∕to DAD INVALID time      | t <sub>31</sub> | 00                                    | <i></i>          |       | ns   |

| MCLK ∕ to Read DAD VALID time | t <sub>32</sub> | × 10, 11;                             |                  | 150   | ns   |

| DAD to Read DDT VALID time    | t <sub>33</sub> | $t_{16} \times 6 - (t_{34} + t_{32})$ |                  |       | ns   |

| MCLK to Read DDT setup        | t <sub>34</sub> | 20                                    |                  |       | ns   |

| time                          | (B)             | N/X                                   |                  |       |      |

| MCLK / to Read DDT hold time  | t <sub>35</sub> | 40                                    |                  |       | ns   |

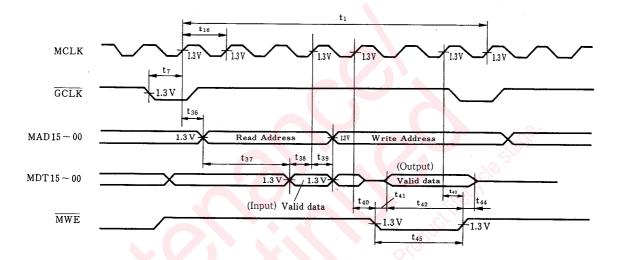

| MCLK to Read MAD VALID time   | t <sub>36</sub> |                                       |                  | 60    | ns   |

# • AC Characteristics(Continued)

| Item                         | Symbol          | min.                                                   | tyṗ. | max. | Unit |

|------------------------------|-----------------|--------------------------------------------------------|------|------|------|

| MAD to Read MDT VALID time   | t <sub>37</sub> | t <sub>16</sub> X3-(t <sub>38</sub> +t <sub>36</sub> ) |      |      | ns   |

| MCLK / to Read MDT setup     | t <sub>38</sub> | 20                                                     |      |      | ns   |

| time                         |                 |                                                        |      | ľ .  |      |

| MCLK to Write MAD VALID time | t <sub>39</sub> |                                                        |      | 60   | ns   |

| MCLK to MWE                  | t <sub>40</sub> |                                                        |      | 50   | ns   |

| MWE to MDT VALID time        | t <sub>41</sub> |                                                        |      | 20   | ns   |

| MWE   ✓ to Write MDT setup   | t <sub>42</sub> | 40                                                     |      |      | ns   |

| time                         |                 |                                                        |      |      |      |

| MCLK / to MWE /              | t <sub>43</sub> |                                                        |      | 50   | ns   |

| MWE / to Write MDT INVALID   | t <sub>44</sub> | 0                                                      |      | 500  | ns   |

| time                         |                 |                                                        |      |      |      |

| MWE pulse width "L"          | t <sub>45</sub> | 60                                                     |      | C)   | ns   |

# ■ Pin Descriptions

| Pin No.              | Name                              | I/O | Description                                                                                                                                                                                                                          |

|----------------------|-----------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1~8                  | IDT 7~IDT 0                       | I   | Pixel input data. Connects an 8-bit multivalued image input data line. Connects the MSB IDT7. Sets all the bits to the "H" level for the blackest image input data, and sets them to the "L" level for the whitest image input data. |

| 9                    | GCLK                              | Ι.  | Pixel clock. Supplies an "L" level signal when writing multivalued image data.                                                                                                                                                       |

| 10, . 54<br>33, 73   | $V_{DD}$                          |     | +5 V power connection pin                                                                                                                                                                                                            |

| 11                   | LENBL                             | I I | Line enable. Supplies the "L" level signal when indicating that one line is enabled. The line starts when it is changed from the "H" to "L" level, and it ends when changed from the "L" to the "H" level.                           |

| 12, 52<br>31, 75     | V <sub>ss</sub>                   | ) _ | GND                                                                                                                                                                                                                                  |

| 13                   | MCLK                              | I   | Master clock. Supplies a single-phase clock. A clock frequency is determined by the L-level pulse width and cycle of GCLK.                                                                                                           |

| 14~16                | MODE 2 ~ MODE 0                   | I   | Operation mode. Supplies a 3-bit operation control signal. The HTP initialize/pattern load, CAPIX 1, CAPIX 2, dither 1 or dither 2 mode can be set by a combination.                                                                 |

| 17                   | PWE                               | I   | Pattern write enable. Supplies the "L" level signal when writing pattern cycle or pattern input data. Normally, pattern cycle and pattern input data are continuously written.                                                       |

| 18~25                | PDT7~PDT0                         | I   | Pattern cycle data. Connects an 8-bit pattern cycle/pattern input data signal line. PDT7 is the MSB.                                                                                                                                 |

| 26~30<br>32<br>34~35 | DAD 7 ~DAD 3  DAD 2  DAD 1 ~DAD 0 | 0   | Address output. Signal line for address output of the dither memory. DAD7 is the MSB.                                                                                                                                                |

# ■ Pin Descriptions (Continued)

| Pin No.              | Name                                | I/O | Description                                                                                                                                                                                                   |

|----------------------|-------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36~43                | DDT7~DDT0                           | I/O | Data I/O. Bidirectional signal line for data I/O of the dither memory. DDT7 is the MSB. A data direction is an input when DWE is at the "H" level, and an output when at the "L" level.                       |

| 44                   | DVE                                 | 0   | Write enable. Signal line to control data read/write of the dither memory. Data is read from the dither memory when it is at the "H" level, and it is written to the dither memory when at the "L" level.     |

| 45                   | LENBLO                              | 0   | Write enable output. Output signal set to the "L" level when indicating that one line is enabled. Although synchronized with LENBL, it is used when an accurate pixel position is required.                   |

| 46                   | GCLKO                               | 0   | Pixel clock output. Output signal set to the "L" level when indicating that a binary image output signal is enabled. Although synchronized with GCLK, it is used when an accurate pixel position is required. |

| 47                   | ODT                                 | 0   | Pixel output data. Binary image output signal line with pseudo intermediate toning provided. "H" level for black pixel data, and "L" level for wnite pixel data                                               |

| 48                   | MWE                                 | I   | Write enable. Signal line to control data read/write of the line memory. Data is read from the line memory when it is at the "H" level, and written to the line memory when at the "L" level.                 |

| 49~51<br>53<br>55~66 | MDT15~MDT13<br>MDT12<br>MDT11~MDT00 | I/O | Data I/O. Bidirectional signal lines for data I/O of the line memory. MDT15 is the MSB. A data direction is an input when $\overline{\text{MWE}}$ is at the "H" level, and an output when at the "L" level.   |

| 67~72<br>74<br>76~84 | MAD15~MAD10<br>MAD09<br>MAD08~MAD00 | 0   | Address output. Signal line for address output of the line memory. MAD15 is the MSB.                                                                                                                          |

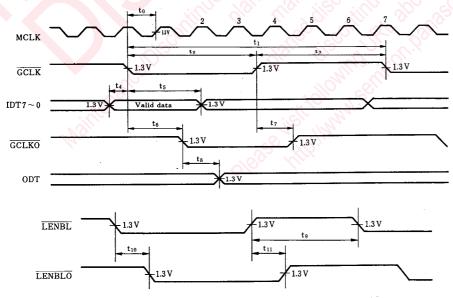

# ■ Timing Diagrams

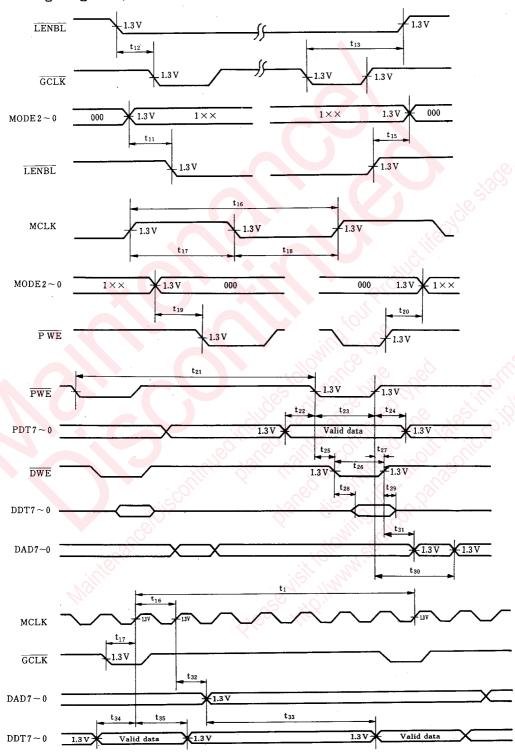

# ■ Timing Diagrams(Countinued)

# ■ Timing Diagrams(Countinued)

# ■ Descriptions of Signal Processing

| Item           | Signal            | Signal Dir | ection/Q'ty | Description          | Remarks                     |

|----------------|-------------------|------------|-------------|----------------------|-----------------------------|

| Image input    | IDT 7 ~ 0         | I          | 8           | Image input data     | IDT 7: MSB, X'FF': Black    |

|                | GCLK              | 1.         | 1           | Pixel clock          | Cycle: 350 ns or more       |

|                | LENBL             | I          | 1           | Write enable         | 17. 17.                     |

| Image output   | ODT               | 0          | 1           | Pixel output data    | "H": Black                  |

|                | GCLKO             | 0          | 1.          | Pixel clock output   | 16 14 60.)                  |

|                | LENBLO            | 0          | 1           | Write enable output  | , 'I', 'IC.                 |

| Line memory    | MAD15~00          | 0,         | 16          | Address output       | MAD15: MSB                  |

|                | MDT15~00          | I/O        | 16          | Data output          | MDD15: MSB                  |

|                | MWE               | 00         | 1           | Write enable         | 000                         |

| Pattern input  | PDT 7 ~ 0         | I          | 8           | Pattern cycle data   | PDT7:MSB                    |

|                | PWE               | I          | 1           | Pattern write enable |                             |

| Dither memory  | DAD 7 ~ 0         | 0          | 8           | Address output       |                             |

|                | DDT 7 ~ 0         | I/O        | 8           | Data I/O             |                             |

|                | DWE               | 0          | 1           | Write enable         |                             |

| Control signal | MCLK              | I          | 1           | Master clock         | Max. 20 MHz                 |

|                | MODE 2 ~ 0        | I          | 3           | Operation mode       | 000: HTP initialize/pattern |

|                |                   |            |             |                      | load                        |

|                |                   |            |             |                      | 100 : CAPIX 1               |

|                |                   |            |             |                      | 101 : CAPIX 2               |

|                |                   |            |             |                      | 110: Dither 1(max. 16×16)   |

|                |                   |            |             |                      | 111: Dither 2(max. 16×16)   |

| Power supply   | $V_{\mathrm{DD}}$ | I          | 4           | +5 V                 |                             |

| line           | V <sub>SS</sub>   | I          | . 4         | 0 V                  |                             |

## **■** Specifications

|                            | Item                                                                               | Description                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSI Factors                | Process Package Clock Supply voltage Power consumption Operating temperature range | CMOS 2.5µA1, 2 layers 84-pin flat package Max. 20 MHz 5V 130mW/typ. 0~70°C                                                                                                                                                                                                                                                                           |

| Image Processing Functions | Processing speed Input data width Image space Operation mode                       | Max. 350 ns/pixel  Max. 8 bits/pixel  Hor. scanning direction: Max. 65,536 pixels  Vert. scanning direction: Limitless  CAPIX 1(Character, line drawing, picture)  CAPIX 2(Moire elimination only Reticular point picture of printed matter, etc.)  Texture dither  Dither matrix load system  Optional cycle 1×1~16×16  Threshold value range 0~255 |

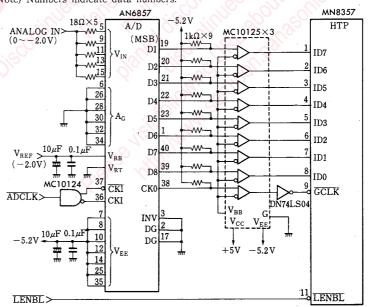

## ■ Applied Circuit

● When the MN8357 Is Applied as a Scanner Interface

### ■ Description of Functions

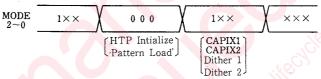

HTP operations are controlled by a combination of control signals MODE 2-MODE 0 and classified into

Pattern Load and 4 operation modes.

The following shows combinations of MODE 2-MODE 0 and their control sequences.

| N | MOD | E | Operation Mode              |    | MODE                 |   |                                           |

|---|-----|---|-----------------------------|----|----------------------|---|-------------------------------------------|

| 2 | 1   | 0 | Operation wode              | 2  | 2 1 0 Operation Mode |   | Operation Mode                            |

| 0 | 0   | 0 | HTP Initialize/Pattern Load | 1. | 0                    | 0 | CAPIX 1(Character, Line Drawing, Picture) |

| 0 | 0   | 1 | Combination Prohibited      | 1  | 0                    | 1 | CAPIX 2(Moire Elimination Only)           |

| 0 | 1   | 0 | Combination Prohibited      | 1  | 1                    | 0 | Dither 1                                  |

| 0 | 1   | 1 | Combination Prohibited      | 1  | 1                    | 1 | Dither 2                                  |

#### HTP Initialize/Pattern Load

HTP Initialize/Pattern Load is initiated by changing the control signals MODE 2-MODE 0 from "1××" to "000" and terminated by changing them the other way.

#### (1) HTP Initialize

All the scan window register, processed data storage register, line memory address register, data register and pattern cycle control addresses are cleared while MODE 2-MODE 0 are "000".

#### (2) Pattern Load

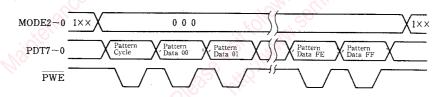

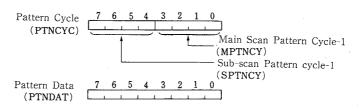

While MODE 2-MODE 0 are "000", Pattern Load is executed by supplying pattern cycle and pattern data to PDT7-0, and L-level pulse signal to PWE.

The following figure shows a signal supply timing and a pattern data supply sequence at Pattern Load time, and formats.

The pattern cycle and pattern data have a fixed supply sequence. If this sequence is a mistake, Pattern Load is not executed properly.

It is not necessary to always supply all the pattern data; you just supply from the pattern data. No.00 through pattern data which assumes the pattern cycle as its number. The number of pattern data supplied at that time is as follows.

No. of pattern data supplied =  $(SPTNCY-1) \times 16+(MPTNCY)$

Only the pattern cycle is required to be supplied when the ROM is used as dither memory.

## Pattern Load Timing

## ■ Description of Functions(Continued)

#### • Relations between Pattern Data Nos. and Positions

Main Scan Direction

| ~ l          |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     |    |

|--------------|----|----|----|----|----|----|----|----|----|--------------|----|----|----|-----|-----|----|

| . <u>[</u> ] | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09           | OA | OB | OC | OD  | OE  | OF |

| sct          | 10 | 11 | 12 | 13 |    |    |    |    |    |              |    |    |    |     |     | 1F |

| Direction    |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 2F |

| 1            |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 3F |

| scan         |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 4F |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 5F |

| ons.<br>↓    |    |    |    |    |    |    |    |    |    | $\mathbf{A}$ |    |    |    |     |     | 6F |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 7F |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 8F |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     |     | 9F |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     | ~   | AF |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     | (C) | BF |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    |     | 5   | CF |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    | 76  | ١   | DF |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    | 70. |     | EF |

|              |    |    |    |    |    |    |    |    |    |              |    |    |    | FD  | FE  | FF |

## ● CAPIX I (Character, Line Drawing, Picture)

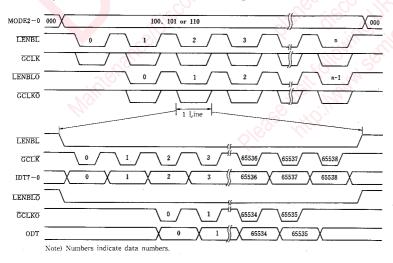

CAPIX 1 is initiated by changing the control signals MODE 2-MODE 0 from "000" to "100" and terminated by changing them the other way.

The following figure shows CAPIX 1 supply signal and output signal timings. Since the HTP performs processing by once reading into an internal scanning register, input pixel data and output DC data timings are shifted by 2 pixels in the main scan direction and by 1 pixel in the sub-scan direction, respectively.

Therefore, when an accurate positional relationship of processed pixel data is required, output pixel data are processed by using LENBLO and GCLKO.

The number of processed pixels in the main scan direction is up to 65,536. Even if GCLK is inputted, GCLKO is not outputted over 65,536 pulse. The number of processed pixels is also restricted by a line memory capacitance. When GCLK is inputted exceeding the capacitance, the contents of the line memory are destroyed and normal operation is not done, unless special protection is provided externally.

The table on the next page shows the patterns of Pattern Load which precedes CAPIX 1. The number of supplied patterns is 52.

#### ● CAPIX 1, CAPIX 2 and Dither 1 Timings

### ■ Description of Functions(Continued)

#### ● CAPIX | Patterns

| MODE          |

|---------------|

| 100           |

| Pattern Cycle |

| 33            |

| Pattern Data  |

| · ·           |

| Pattern Data |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

|--------------|----|----|----|----|---|----|---|---|---|---|---|---|---|---|---|---|

| Lower        | 0  | 1  | 2  | 3  | 4 | 5  | 6 | 7 | 8 | 9 | A | В | С | D | Е | F |

| 0            | 84 | 84 | 7C | 7C | X | X  | X | X | Х | X | X | Х | X | Х | X | X |

| 1            | 84 | 84 | 7C | 7C | Х | X. | X | X | X | X | X | X | X | X | Х | Х |

| 2            | 7C | 7C | 84 | 84 | X | Х  | Х | X | Χ | X | Х | Χ | X | X | Х | X |

| 3            | 7C | 7C | 84 | 84 | X | Х  | X | X | X | X | X | Χ | X | X | X | X |

| 4            |    |    |    |    |   |    |   |   |   |   |   |   | L |   |   |   |

| 5            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   | - |

| 6            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| 7            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| 8            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| 9            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   | N |

| A            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| В            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| С            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| D            |    |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| E            | J  |    |    |    |   |    |   |   |   |   |   |   |   |   |   |   |

| F            |    |    |    |    | L |    |   |   |   |   |   |   |   |   |   |   |

Note 1) "Upper" and "Lower" indicate a pattern data sending sequence (00-FF) after sending the pattern cycles.

Note 2) × denotes indefiniet data, and blanks denote data which are required to be sent.

# CAPIX 2(Moire Elimination Only Reticular Point Picture of Printed Matter, etc.)

CAPIX 2 is initiated by changing the control signals MODE 2-MODE 0 from "000" to "101" and terminated by changing them the other way.

CAPIX 2 supply signal and output signal timings are the same as those for CAPIX 1.

Pattern Load is not necessary for CAPIX 2.

#### Dither I

Dither is initiated by changing the control signals MODE 2-MODE 0 from "000" to "110" terminated by changing the other way.

Dither 1 supply signal and output signal timings are the same as those for CAPIX 1.

The following tables show the Pattern Load which procedes Dither 1. The number of pattern supplied depends on each pattern.

Relations between pattern data(PDT) and image input data(IDT), and image output data(ODT) are as follows:

When  $IDT-PDT \ge 0$ , ODT = 1When IDT-PDT < 0, ODT = 0PDT = FF(Hex.) - Dither pattern

#### Distributed Dither Patterns

| MODE          |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

|---------------|----|----|-------|------|------|-----|---|---|---|---|-----|----|------|---|-----------------|---|

| 11 n          |    | 11 | n = ( | ); D | the  | r 1 |   |   |   |   |     |    |      |   |                 |   |

| Pattern Cycle | •  | 1  | n = 1 | : D  | ithe | r 2 |   |   |   |   |     |    |      |   |                 |   |

| 33            |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| Pattern Data  | •  |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| Lower         | 0  | 1  | 2     | 3    | 4    | 5   | 6 | 7 | 8 | 9 | A   | В  | С    | D | Е               | F |

| 0             | F8 | 78 | D8    | 58   | X    | X   | Х | X | X | X | X   | X  | X    | X | X               | X |

| 1             | 38 | B8 | 18    | 98   | Х    | X   | Х | X | × | X | X   | X  | X    | X | ×               | X |

| 2             | C8 | 48 | E8    | 68   | X    | X   | X | X | × | X | X   | X  | X    | X | ×               | X |

| 3             | 08 | 88 | 28    | A8   | X    | X   | X | X | X | X | X   | X  | X    | X | ×               | X |

| 4             |    |    |       |      |      |     |   |   |   |   |     |    |      | _ |                 |   |

| 5             |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| 6             |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| 7             |    |    |       |      |      |     |   |   |   |   |     |    | Ţ    |   |                 |   |

| 8             |    |    |       |      | 7    |     |   |   |   |   |     |    |      |   |                 |   |

| 9             |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| Α             |    |    |       |      |      |     |   |   | 1 |   |     |    |      | ( | <b>&gt;</b> . 4 |   |

| В             |    |    |       |      |      |     |   |   |   |   |     |    |      |   |                 |   |

| С             |    | 7  |       |      |      |     |   |   |   |   |     |    | . 67 | 1 | 1               |   |

| D             |    |    |       |      |      | 4   |   |   |   |   |     | C  | 1    |   |                 |   |

| E             |    |    |       |      |      |     |   |   |   |   | . ( | >. | _    |   |                 |   |

| F '           |    |    |       |      |      |     |   |   |   |   | -// |    |      |   |                 |   |

#### ● Reticular Point (45°) Patterns

| MODE          |               |

|---------------|---------------|

| 11 n          | n=0: Dither 1 |

| Pattern Cycle | n=1: Dither 2 |

| FF            | n=1: Dither 2 |

| Pattern Data  | ~0,           |

| Pattern Data | 2 . |    |    |    |            | $\mathcal{O}$ |    |    |    |    |    |    |    |    |    |    |

|--------------|-----|----|----|----|------------|---------------|----|----|----|----|----|----|----|----|----|----|

| Lower        | 0   | 1  | 2  | 3  | 4          | 5             | 6  | 7  | 8  | 9  | A  | В  | С  | D  | Е  | F  |

| 0            | F8  | E8 | D4 | A8 | 54         | 30            | 14 | 03 | 06 | 67 | 2A | 56 | ΑA | D6 | EΑ | FC |

| 1            | E0  | CC | BC | A0 | 5C         | 40            | 29 | 1D | 1F | 32 | 42 | 5E | A2 | BE | CE | E2 |

| 2            | C4  | B4 | 98 | 90 | 6C         | 65            | 49 | 39 | 3B | 4B | 66 | 6E | 92 | 9A | B6 | C6 |

| 3            | 8C  | 88 | 84 | 7E | 7D         | 79            | 75 | 71 | 73 | 77 | 7B | 80 | 82 | 86 | 8A | 8E |

| 4            | 36  | 46 | 62 | 6B | 97         | 9F            | BB | CB | C9 | B9 | 9D | 95 | 98 | 60 | 44 | 34 |

| 5            | 1A  | 26 | 3F | 5B | A7         | C3            | D3 | E7 | E5 | D1 | C1 | A5 | 59 | 3C | 2C | 18 |

| 6            | 0A  | 13 | 2F | 53 | AF         | DB            | EF | F7 | F5 | ED | D9 | ΑD | 51 | 25 | 10 | 08 |

| 7            | 05  | 0F | 23 | 4F | <b>B</b> 3 | DF            | F3 | FF | FB | F1 | DD | B1 | 4D | 21 | 0D | 00 |

| 8            | 07  | 17 | 2B | 57 | AB         | D7            | EB | FD | F9 | E9 | D5 | A9 | 55 | 31 | 15 | 02 |

| 9            | 1E  | 33 | 43 | 5F | A3         | BF            | CF | E3 | E1 | CD | BD | A1 | 5D | 41 | 28 | 1C |

| A            | 3A  | 4A | 67 | 6F | 93         | 9B            | В7 | C7 | C5 | B5 | 99 | 91 | 6D | 64 | 48 | 38 |

| В            | 72  | 76 | 7A | 81 | 83         | 87            | 8B | 8F | 8D | 89 | 85 | 7F | 7C | 78 | 74 | 70 |

| _ C          | C8  | B8 | 9C | 94 | 69         | 61            | 45 | 35 | 37 | 47 | 63 | 6A | 96 | 9E | BA | CA |

| D            | E4  | D0 | C0 | A4 | 58         | 3D            | 2D | 19 | 1B | 27 | 3E | 5A | A6 | C2 | D2 | E6 |

| E            | F4  | EC | D8 | AC | 50         | 24            | 11 | 09 | 0B | 12 | 2E | 52 | ΑE | DA | EΕ | F6 |

| F            | FA  | F0 | DC | B0 | 4C         | 20            | 0C | 01 | 04 | 0E | 22 | 4E | B2 | DE | F2 | FE |

Note 1) "Upper" and "Lower" indicates a pattern data sending sequence(00-FF) after sending the pattern cycle.

Note 2) × denotes indefinite data. Blanks denote data which are not required to be sent.

#### Simple Binary Conversion Patterns

| Lower<br>Upper | 0  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9  | Α | В | С | D | Е | F |

|----------------|----|---|---|---|---|---|---|---|---|----|---|---|---|---|---|---|

| 0              | 80 |   | 1 |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 1              |    | 1 |   |   |   |   |   |   | L |    |   |   |   |   |   |   |

| 2              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 3              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 4              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 5              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 6              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 7              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 88             |    |   | L |   |   |   |   |   |   |    |   |   |   |   |   |   |

| 9              | Ī  |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| Α              |    |   |   |   |   |   |   |   |   | ٠. |   |   |   |   |   |   |

| В              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| C .            |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| D              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| E              | Ι. |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

| F              |    |   |   |   |   |   |   |   |   |    |   |   |   |   |   |   |

Note 1) "Upper" and "Lower" indicate a pattern data sending sequence(00-FF) after sending the pattern cycle.

Note 2) × denotes indifinite data, and blanks denote data which are not required to be sent.

## ■ Description of Function(Continued)

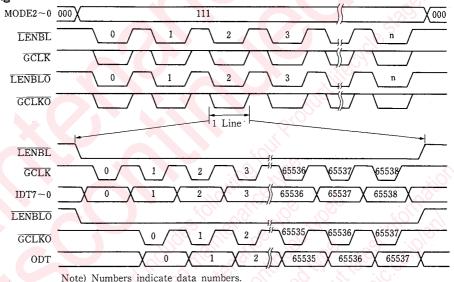

#### • Dither 2

Dither 2 is initiated by changing the control signals MODE 2-MODE 0 from "000" to "111" and terminated by changing the other way.

The following figure shows Dither 2 supply signal output signal timings. In order to adjust timings to CAPIX 1 or CAPIX 2, Dither 1 uses the line memory and performs processing by once reading data in the scanning register. Dither 2, however, performs

processing without using the line memory and scanning register. Input pixel data and output pixel data timings are shifted by only 1 pixel in the main scan direction.

The number of processed pixels in the main scan direction is limitless. The patterns of Pattern Load, which precedes Dither 2, are the same as those for dither 1.

### ● Dither 2 Timing

## Application Examples

## • Image Input Interface

The right figure shows an application example using an 8-bit A/D converter.

### ■ Application Examples(Continued)

| Signal    | Description         | Remarks                                          |

|-----------|---------------------|--------------------------------------------------|

| ANALOG IN | Analog input signal | Write: -2 V, Black: 0 V                          |

| ADCLK     | Sampling clock      | Enabled when changing from the "H" to "L" level. |

| LENBL     | Line enable signal  | 1-line data enable during the "L" level          |

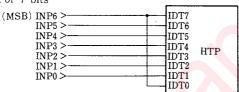

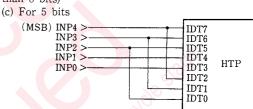

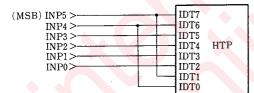

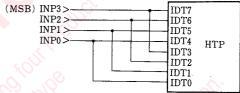

#### • Image Input Data Connections

(Connect as shown below when image input data is less than 8 bits)

### (b) For 6 bits

## ● Image Output Interface

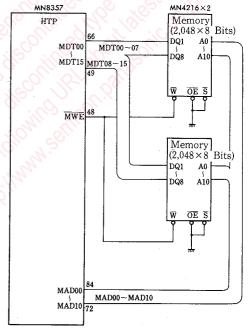

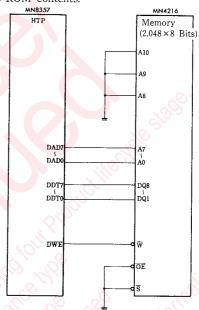

The following figure shows an example of writing 2,048-pixel output data into the memory:

## Line Memory Interface

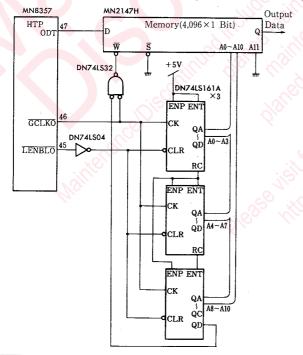

The following figure shows an example of processing 2,048 pixels:

# ■ Application Examples(Continued)

#### • Pattern Input Interface

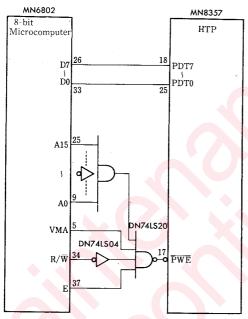

The following figure shows an application example using an 8-bit microcomputer:

## • Dither Memory Interface

(1) The following shows an example using the RAM:

## • Dither Memory Interface

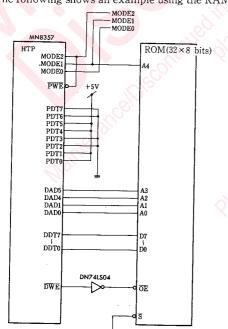

(2) The following figure shows an example using the ROM as the dither memory, and the following table shows ROM contents:

### ROM Contents

| Va 10                  |         |                        |

|------------------------|---------|------------------------|

| Corresponding OP. Mode | CAPIX   | 4×4 Distributed Dither |

| A 4<br>A 3~A 0         | no ollo | 1                      |

| 0000                   | 84      | F 8                    |

| 0001                   | 84      | 78                     |

| 0010                   | 7 C     | D 8                    |

| 0011                   | 7 C     | 58                     |

| 0100                   | 84      | 38                     |

| 0101                   | 84      | B 8                    |

| 0110                   | 7 C     | 18                     |

| 0111                   | 7 C     | 68                     |

| 1000                   | 7 C     | C 8                    |

| 1001                   | 7 C     | 48                     |

| 1010                   | 84      | E 8                    |

| 1011                   | 84      | 98                     |

| 1100                   | 7 C     | 08                     |

| 1101                   | 7 C     | 88                     |

| 1110                   | 84      | 28                     |

| 1111                   | 84      | A 8                    |

# Application Examples(Continued)

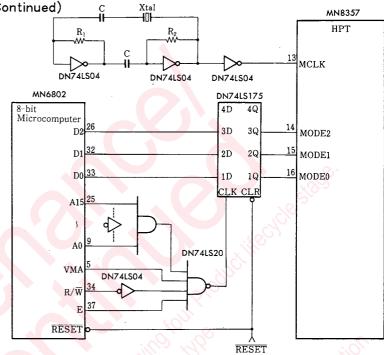

# Control Signal Interface

The following figure shows an application example using a crystal osillation pin and an 8-bit microcomputer:

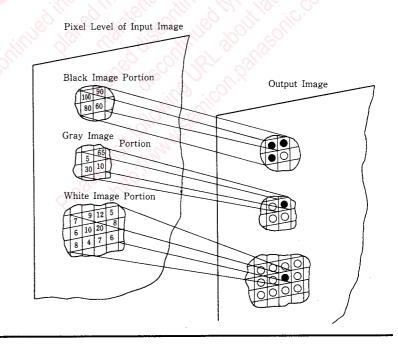

# ● CAPIX System-Correlative-density-Assignment of adjacent PIXels

Sequentially adds the pixel level of an input image, and outputs one black when a sum reaches a level which generates one black. Therefore, the area to be added is not limited.

The right figure shows a concept of the CAPIX system when the pixel level of the input image comes to 100(black) from 0(white).

#### (1) Black image portion

A sum of 4 pixels comes to 330, and 3 blacks are outputted into 4 pixels in an descending order of the pixel level(one black is equivalent to 100).

# (2) Gray image portion A sum of 4 pixels comes to

110, and 1 black is outputted into 4 pixels.

(3) White image portion

A sum of 12 pixels comes to

102, and 1 black is outputted into 12 pixels.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

- Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- · Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20080805