# 32-bit Microcontroller Traveo Family **Fact Sheet**

The Traveo™ family S6J3110, features 32-bit RISC microcontrollers with an ARM® Cortex®-R5 core and operate at 144MHz.4 MB of Flash memory can correspond also to the software capacity which will increase in the future. First Body application MCU with CAN-FD as a communication interface. CAN-FD is compatible with the conventional CAN and it can shorten the time of reprograming by high-speed communication. Moreover, this miocrocontroller has SHE(Secure Hardware Extension) as security function. It will prevent the extractraction and alteration of the data or keys. This microcontroller can control safely and quickly the circumference function of Body in which an increase will be expected from now on.

### **Features**

■ 32bit ARM® Cortex®-R5 CPU Core

■ Clock

□ Maximum clock frequency: 144MHz, 96MHz\*

■ DMA controller: 16 channels ■ External interrupt: 16 channels ■ Base timer: 30 channels

■ 32-bit free-run timer: 6 channels ■ 32-bit input capture: 12 channels ■ 32-bit output compare: 12 channels

12-bit A/D converter: 64, 56\* channels (2 units total)

■ Real Time Clock

■ Multi-function serial interface: 22, 4\* channels, Selectable from UART/CSIO/LIN/I2C

CAN-FD(192msb[reception]): 2, 1\* channels

Exclusion access memory

Watchdog timer: 1 channel(SW)+1 channel(HW)

CRC generation: 1 channel Secure Hardware Extension

General Purpose I/O port: 150, 116\*

Built-in CR oscillator Debug interface

□ JTAG Debug Port

Partial-wakeup function

■ Low Voltage Detector

■ Clock Supervisor

■ Power Supply: 1 power voltage(5V)

\* Spec for S6J311AHxB, S6J3119HxB, S6J3118HxB

## Package Example of Reference

Plastic • TEQFP176,176pin

## **Product Lineup**

| Part number<br>Parameter | S6J311ExxB | S6J311DxxB | S6J311CxxB | S6J311BxxB |

|--------------------------|------------|------------|------------|------------|

| Main Flash(Byte)         | 4096K+64K  | 3072K+64K  | 2048K+64K  | 1536K+64K  |

| Work Flash(Byte)         | 112K       | 112K       | 112K       | 112K       |

| RAM(Byte)                | 320K       | 256K       | 192K       | 128K       |

| Backup<br>RAM(Byte)      | 64K        | 64K        | 64K        | 64K        |

| Part number<br>Parameter | S6J311AHxB | S6J3119HxB | S6J3118HxB |

|--------------------------|------------|------------|------------|

| Main Flash(Byte)         | 1024K+64K  | 768K+64K   | 512K+64K   |

| Work Flash(Byte)         | 48K        | 48K        | 48K        |

| RAM(Byte)                | 80K        | 64K        | 48K        |

| Backup<br>RAM(Byte)      | 8K         | 8K         | 8K         |

## **Ordering Information**

| Part number       | Package                     |  |

|-------------------|-----------------------------|--|

| S6J311EJABSEx0000 | _                           |  |

| S6J311DJABSEx0000 | Plastic TEQFP(0.5mm pitch), |  |

| S6J311CJABSEx0000 | 176pin                      |  |

| S6J311BJABSEx0000 | ТТОРПТ                      |  |

| S6J311EHABSEx0000 | Plastic                     |  |

| S6J311DHABSEx0000 | TEQFP(0.5mm pitch),         |  |

| S6J311CHABSEx0000 | 144pin                      |  |

| S6J311BHABSEx0000 | Ι44ριιι                     |  |

| S6J311AHABSEx0000 | Plastic                     |  |

| S6J3119HABSEx0000 | TEQFP(0.5mm pitch),         |  |

| S6J3118HABSEx0000 | 144pin                      |  |

| S6J311EJBBSEx0000 | Plastic                     |  |

| S6J311DJBBSEx0000 | TEQFP(0.5mm pitch),         |  |

| S6J311CJBBSEx0000 | 176pin                      |  |

| S6J311BJBBSEx0000 | ТТОРПТ                      |  |

| S6J311EHBBSEx0000 | Plastic                     |  |

| S6J311DHBBSEx0000 | TEQFP(0.5mm pitch),         |  |

| S6J311CHBBSEx0000 | 144pin                      |  |

| S6J311BHBBSEx0000 | ιπριι                       |  |

| S6J311AHBBSEx0000 | Plastic                     |  |

| S6J3119HBBSEx0000 | TEQFP(0.5mm pitch),         |  |

| S6J3118HBBSEx0000 | 144pin                      |  |

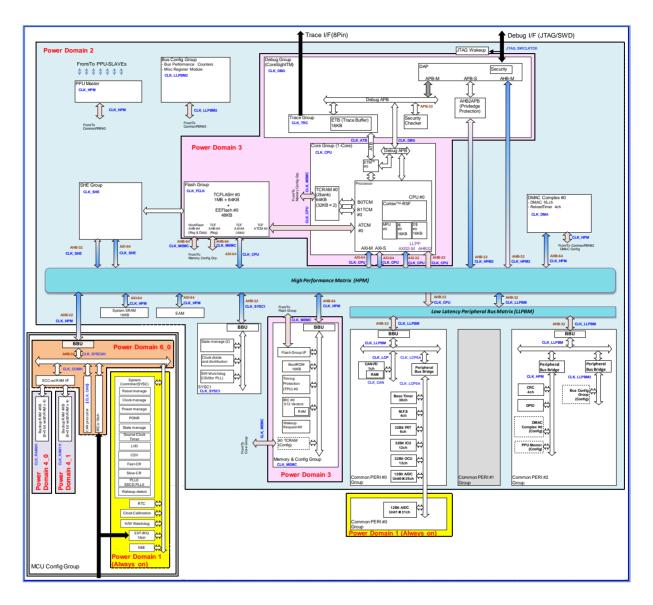

## **Block Diagram**

## Block Diagram of S6J311ExxB,S6J311DxxB,S6J311CxxB,S6J311BxxB

## **Document History**

Document Title: S6J3110 Series, 32-bit Microcontroller Traveo Family Fact Sheet

Document Number: 002-08974

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date                                                                                    | Description of Change                                                       |  |

|----------|---------|--------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| **       | 1       | NNAK               | Migrated to Cypress and assigned document number 002-08974. No change to document contents or format. |                                                                             |  |

| *A       | 5159031 | HIOT               | 03/04/2016                                                                                            | /2016 Updated to Cypress template Added SHE-OFF option and updated revision |  |

## Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

ARM® Cortex® Microcontrollers cypress.com/arm

Automotive cypress.com/automotive

Clocks & Buffers cypress.com/clocks

Interface cypress.com/interface

Lighting & Power Control cypress.com/powerpsoc

Memory cypress.com/memory

PSoC cypress.com/psoc

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

Wireless/RF cypress.com/wireless

### **PSoC® Solutions**

cypress.com/psoc

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

#### **Cypress Developer Community**

Community | Forums | Blogs | Video | Training

### **Technical Support**

cypress.com/support

#### ARM and Cortex are the trademarks of ARM Limited in the EU and other countries

© Cypress Semiconductor Corporation 2014-2016. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you under its copyright rights in the Software, a personal, non-exclusive, nontransferable license (without the right to sublicense) (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units. Cypress also grants you a personal, non-exclusive, nontransferable, license (without the right to sublicense) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely to the minimum extent that is necessary for you to exercise your rights under the copyright license granted in the previous sentence. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIEDWARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any liability arising out of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems, other medical devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or system could cause personal injury, death, or property damage ("Unintended Uses"). A critical component is any component of a device or system whose failure to perform can be reasonably expected to cause the failure of the device or system, or to affect its safety or effectiveness. Cypress is not liable, in whole or in part, and Company shall and hereby does release Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. Company shall indemnify and hold Cypress harmless from and against all claims, costs, damages, and other liabilities, including claims for personal injury or death, arising from or related to any Unintended Uses of Cypress products.

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.