19-2512; Rev 4; 3/08

EVALUATION KIT

# ±15kV ESD-Protected Touch-Screen Controllers Include DAC and Keypad Controller

## **General Description**

**Features**

The MAX1233/MAX1234 are complete PDA controllers in 5mm × 5mm, 28-pin QFN and TQFN packages. They feature a 12-bit analog-to-digital converter (ADC), low onresistance switches for driving resistive touch screens, an internal +1.0V/+2.5V or external reference, ±2°C accurate, on-chip temperature sensor, direct +6V battery monitor, keypad controller, 8-bit digital-to-analog converter (DAC), and a synchronous serial interface. Each of the keypad controllers' eight row and column inputs can be reconfigured as general-purpose parallel I/O pins (GPIO). All analog inputs are fully ESD protected, eliminating the need for external TransZorb<sup>™</sup> devices.

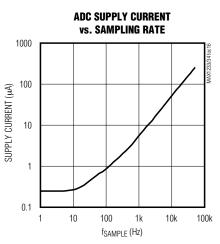

The MAX1233/MAX1234 offer programmable resolution and sampling rates. Interrupts from the devices alert the host processor when data is ready, when the screen is touched, or a key press is detected. Softwareconfigurable scan control and internal timers give the user flexibility without burdening the host processor. These devices consume only 260 $\mu$ A at the maximum sampling rate of 50ksps. Supply current falls to below 50 $\mu$ A for sampling rates of 10ksps. The MAX1233/MAX1234 are guaranteed over the -40°C to +85°C temperature range.

## **Applications**

Personal Digital Assistants Pagers

Touch-Screen Monitors

- Cellular Phones

- MP3 Players

- Portable Instruments

- Point-of-Sale Terminals

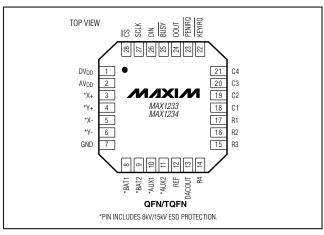

## **Pin Configuration**

## ///XI//

- ESD-Protected Analog Inputs ±15kV IEC 1000-4-2 Air-Gap Discharge ±8kV IEC 1000-4-2 Contact Discharge

- Single-Supply Operation +2.7V to +3.6V (MAX1233) +4.75V to +5.25V (MAX1234)

- ♦ 4-Wire Touch-Screen Interface

- Internal +1.0V/+2.5V Reference or External Reference (+1.0V to AV<sub>DD</sub>)

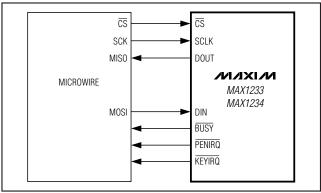

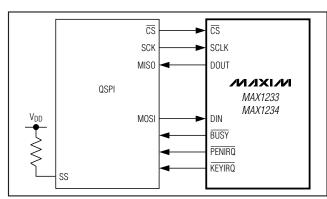

- ◆ SPI<sup>™</sup>/QSPI<sup>™</sup>/MICROWIRE<sup>™</sup>-Compatible 10MHz Serial Interface

- 12-Bit, 50ksps ADC Measures Resistive Touch-Screen Position and Pressure Two Auxiliary Analog Inputs Two Battery Voltages (0.5V to 6V) On-Chip Temperature

- ♦ 8-Bit DAC for LCD Bias Control

- ♦ 4 × 4 Keypad Programmable Controller Offers Up to Eight GPIO Pins

- Automatic Detection of Screen Touch, Key Press, and End of Conversion

- Programmable 8-, 10-, 12-Bit Resolution

- Programmable Conversion Rates

- ◆ AutoShutdown<sup>™</sup> Between Conversions

- Low Power

- 260µA at 50ksps 50µA at 10ksps 6µA at 1ksps 0.3µA Shutdown Current

- ♦ 28-Pin 5mm × 5mm QFN and TQFN Packages

## Ordering Information

| PART       | TEMP RANGE     | PIN-PACKAGE         |

|------------|----------------|---------------------|

| MAX1233EGI | -40°C to +85°C | 28 QFN (5mm x 5mm)  |

| MAX1233ETI | -40°C to +85°C | 28 TQFN (5mm x 5mm) |

| MAX1234EGI | -40°C to +85°C | 28 QFN (5mm x 5mm)  |

| MAX1234ETI | -40°C to +85°C | 28 TQFN (5mm x 5mm) |

TransZorb is a trademark of General Semiconductor Industries, Inc. SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp. AutoShutdown is a trademark of Maxim Integrated Products, Inc.

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

| AV <sub>DD</sub> to GND              | -0.3V to +6V                      |

|--------------------------------------|-----------------------------------|

| DV <sub>DD</sub> to AV <sub>DD</sub> | 0.3V to +0.3V                     |

| Digital Inputs/Outputs to GND        | 0.3V to (DV <sub>DD</sub> + 0.3V) |

| X+, Y+, X-, Y-, AUX1, AUX2,          |                                   |

| and REF to GND                       | 0.3V to (AV <sub>DD</sub> + 0.3V) |

| BAT1, BAT2 to GND                    | 0.3V to +6V                       |

| Maximum ESD per IEC 1000-4-2         | (per MIL STD-883 HBM)             |

| X+, X-, Y+, Y-, AUX1, AUX2, E        | BÄT1, BAT2±15kV                   |

| All Other Pins                                        | .±2.5kV |

|-------------------------------------------------------|---------|

| Maximum Current into Any Pin                          | 50mA    |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |         |

| 28-Pin QFN (derate 28.5mW/°C above +70°C)             | 2W      |

| 28-Pin TQFN (derate 28.5mW/°C above +70°C)            | 2W      |

| Operating Temperature Range40°C to                    | ) +85°C |

| Storage Temperature Range60°C to                      |         |

| Lead Temperature (soldering, 10s)                     | +300°C  |

MIXIM

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(DV_{DD} = AV_{DD} = +2.7V \ to \ +3.6V \ (MAX1233), \ DV_{DD} = AV_{DD} = +4.75V \ to \ +5.25V \ (MAX1234), \ external \ reference \ V_{REF} = 2.5V \ (MAX1233), \ V_{REF} = 4.096V \ (MAX1234); \ f_{SCLK} = 10MHz, \ f_{SAMPLE} = 50ksps, \ 12-bit \ mode, \ 0.1\mu F \ capacitor \ at \ REF, \ T_A = -40^\circ C \ to \ +85^\circ C, \ unless \ otherwise \ noted. \ Typical \ values \ are \ at \ T_A = +25^\circ C. )$

| PARAMETER                                                | SYMBOL     |                           | CONDITIONS                                                      | MIN     | ТҮР    | MAX       | UNITS             |  |  |

|----------------------------------------------------------|------------|---------------------------|-----------------------------------------------------------------|---------|--------|-----------|-------------------|--|--|

|                                                          |            | ANALOG-TO                 | D-DIGITAL CONVERTER                                             |         |        |           |                   |  |  |

| DC ACCURACY (Note 1)                                     |            |                           |                                                                 |         |        |           |                   |  |  |

| Resolution                                               |            | Software-p                | rogrammable 8/10/12 bit                                         |         |        | 12        | Bits              |  |  |

| No Missing Codes                                         |            |                           |                                                                 | 11      |        |           | Bits              |  |  |

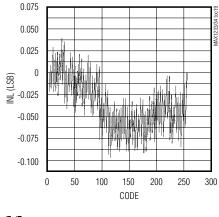

| Deletive Accuracy (Note 2)                               | INL        | 12-bit mod                | e                                                               |         | ±0.8   | ±2        |                   |  |  |

| Relative Accuracy (Note 2)                               |            | 10-bit and                | 8-bit modes                                                     |         | ±0.5   |           | LSB               |  |  |

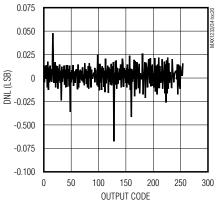

| Differential Nonlinearity                                | DNL        | 12-bit mod                | e                                                               |         | ±0.8   | ±2        | LSB               |  |  |

| Differential Norninearity                                | DINL       | 10-bit and                | 8-bit modes                                                     |         | ±0.5   |           | LOD               |  |  |

| Offset Error                                             |            | 12-bit mod                | e                                                               |         | ±0.5   | ±4        | LSB               |  |  |

| Oliset Endi                                              |            | 10-bit and                | 8-bit modes                                                     |         | ±0.5   |           | LOD               |  |  |

|                                                          |            | 12-bit mod                | e                                                               |         | ±0.5   | ±4        |                   |  |  |

| Gain Error (Note 3)                                      |            | 10-bit mod                | e                                                               |         | ±0.5   |           | LSB               |  |  |

|                                                          |            | 8-bit mode                | 1                                                               |         | ±0.5   |           |                   |  |  |

| Total Unadjusted Error                                   | TUE        | 12-bit mod                | e                                                               |         | ±2     |           | LSB               |  |  |

| Total Offacjusted Effor                                  | TUE        | 10-bit and                | 8-bit modes                                                     |         | ±1     |           | -                 |  |  |

| Offset Temperature Coefficient                           |            |                           |                                                                 |         | ±0.4   |           | ppm/°C            |  |  |

| Gain Temperature Coefficient                             |            |                           |                                                                 |         | ±0.4   |           | ppm/°C            |  |  |

| Channel-to-Channel Offset                                |            |                           |                                                                 |         | ±0.1   |           | LSB               |  |  |

| Channel-to-Channel Gain<br>Matching                      |            |                           |                                                                 |         | ±0.1   |           | LSB               |  |  |

| Noise                                                    |            | Including i               | nternal V <sub>REF</sub>                                        |         | 50     |           | μV <sub>RMS</sub> |  |  |

|                                                          |            | Full-scale                | MAX1233<br>AV <sub>DD</sub> = DV <sub>DD</sub> = +2.7V to +3.6V |         | ±0.4   |           |                   |  |  |

| Power-Supply Rejection                                   | PSR        | input                     | MAX1234<br>AV <sub>DD</sub> = DV <sub>DD</sub> = +5V ±5%        | ±0.3    |        |           | mV                |  |  |

| DYNAMIC SPECIFICATIONS (1)<br>f <sub>SCLK</sub> = 10MHz) | Hz SINE WA | /E, V <sub>IN</sub> = 2.5 | V <sub>P-P</sub> FOR MAX1233, V <sub>IN</sub> = 4.096V          | P-P FOR | MAX123 | 4, 50ksps | ;,                |  |  |

| Signal-to-Noise Plus Distortion                          | SINAD      |                           |                                                                 |         | 69     |           | dB                |  |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1233)}, DV_{DD} = AV_{DD} = +4.75V \text{ to } +5.25V \text{ (MAX1234)}, \text{ external reference } V_{REF} = 2.5V \text{ (MAX1233)}, V_{REF} = 4.096V \text{ (MAX1234)}; f_{SCLK} = 10MHz, f_{SAMPLE} = 50ksps, 12-bit mode, 0.1\muF capacitor at REF, T_A = -40°C \text{ to } +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                       | SYMBOL             | CONDITIONS                                                                                                         | MIN       | TYP    | MAX             | UNITS  |

|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------|-----------|--------|-----------------|--------|

| Total Harmonic Distortion       | THD                |                                                                                                                    |           | -84    |                 | dB     |

| Spurious-Free Dynamic Range     | SFDR               |                                                                                                                    |           | 84     |                 | dB     |

| Full-Power Bandwidth            |                    | -3dB point                                                                                                         |           | 0.5    |                 | MHz    |

| Full-Linear Bandwidth           |                    | SINAD > 67dB                                                                                                       |           | 50     |                 | kHz    |

| CONVERSION RATE                 |                    |                                                                                                                    |           |        |                 |        |

| Internal Oscillator Frequency   |                    |                                                                                                                    | 8         |        | 11.5            | MHz    |

| Aperture Delay                  |                    |                                                                                                                    |           | 30     |                 | ns     |

| Aperture Jitter                 |                    |                                                                                                                    |           | <50    |                 | ps     |

| Maximum Serial Clock Frequency  | fsclk              |                                                                                                                    | 10        |        |                 | MHz    |

| Duty Cycle                      |                    |                                                                                                                    | 30        |        | 70              | %      |

| AUXILIARY ANALOG INPUTS (A      | UX1, AUX2)         |                                                                                                                    |           |        |                 |        |

| Input Voltage Range             |                    |                                                                                                                    | 0         |        | VREF            | V      |

| Input Leakage Current           |                    | Channel not selected or conversion stopped                                                                         |           | ±0.1   | ±1              | μA     |

| Input Capacitance               |                    |                                                                                                                    |           | 34     |                 | pF     |

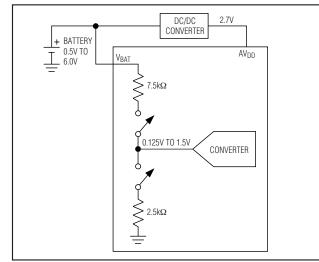

| BATTERY MONITOR INPUTS (BA      | AT1, BAT2)         | •                                                                                                                  |           |        |                 |        |

| Input Voltage Range             |                    |                                                                                                                    | 0.5       |        | 6.0             | V      |

|                                 |                    | Sampling battery                                                                                                   |           | 10     |                 | kΩ     |

| Input Impedance                 |                    | Battery monitor OFF                                                                                                |           | 1      |                 | GΩ     |

| Accuracy                        |                    | Internal reference                                                                                                 | -3        |        | +3              | %      |

| TEMPERATURE MEASUREMEN          | Г<br>Г             |                                                                                                                    |           |        |                 |        |

| Temperature Range               |                    |                                                                                                                    | -40       |        | +85             | °C     |

|                                 |                    | Differential method (Note 4)                                                                                       |           | 1.6    |                 |        |

| Resolution                      |                    | Single measurement method (Note 5)                                                                                 |           | 0.3    |                 | °C     |

| A                               |                    | Differential method (Note 4)                                                                                       |           | ±3     |                 |        |

| Accuracy                        |                    | Single measurement method (Note 5)                                                                                 |           | ±2     |                 | °C     |

| INTERNAL ADC REFERENCE          | •                  |                                                                                                                    |           |        |                 |        |

|                                 |                    | 2.5V mode, T <sub>A</sub> = +25°C                                                                                  | 2.470     | 2.500  | 2.530           | V      |

| Reference Output Voltage        | VREF               | 1.0V mode, T <sub>A</sub> = +25°C                                                                                  | 0.980     | 1.000  | 1.020           |        |

| Output Tempco                   | TCV <sub>REF</sub> |                                                                                                                    |           | 60     |                 | ppm/°C |

| Reference Output Impedance      |                    | Normal operation                                                                                                   |           | 250    |                 | Ω      |

| Reference Short-Circuit Current |                    |                                                                                                                    |           | 18     |                 | mA     |

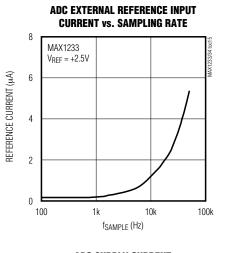

| EXTERNAL ADC REFERENCE (II      | NTERNAL RI         | EFERENCE DISABLED, REFERENCE APPL                                                                                  | IED TO RE | F)     |                 |        |

| Reference Input Voltage Range   |                    | (Note 6)                                                                                                           | 1.0       |        | V <sub>DD</sub> | V      |

| Input Impedance                 |                    | $\overline{\text{CS}}$ = GND or V <sub>DD</sub>                                                                    |           | 1      |                 | GΩ     |

|                                 | 1                  |                                                                                                                    | -         | -      | 1.0             |        |

|                                 |                    | V <sub>REF</sub> = +2.5V at 50ksps (MAX1233)                                                                       |           | 5      | 10              |        |

| Input Current                   |                    | $V_{REF} = +2.5V \text{ at } 50 \text{ksps} (MAX1233)$<br>$V_{REF} = +4.096V \text{ at } 50 \text{ksps} (MAX1234)$ |           | 5<br>8 | 10<br>15        | μA     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1233)}, DV_{DD} = AV_{DD} = +4.75V \text{ to } +5.25V \text{ (MAX1234)}, external reference V_{REF} = 2.5V \text{ (MAX1233)}, V_{REF} = 4.096V \text{ (MAX1234)}; f_{SCLK} = 10MHz, f_{SAMPLE} = 50ksps, 12-bit mode, 0.1\muF capacitor at REF, T_A = -40°C to +85°C, unless otherwise noted. Typical values are at T_A = +25°C.)$

| PARAMETER                                     | SYMBOL     | CONDITIONS                                  | MIN                        | ТҮР                       | МАХ                        | UNITS  |

|-----------------------------------------------|------------|---------------------------------------------|----------------------------|---------------------------|----------------------------|--------|

|                                               |            | DIGITAL-TO-ANALOG CONVERTER                 |                            |                           |                            |        |

| DC ACCURACY                                   |            |                                             |                            |                           |                            |        |

| Resolution                                    |            |                                             |                            |                           | 8                          | Bits   |

| Integral Linearity Error                      | INL        | (Note 7)                                    |                            |                           | ±1.0                       | LSB    |

| Differential Linearity Error                  | DNL        | No missing codes                            |                            |                           | ±1.0                       | LSB    |

| Offset Error                                  | Vos        | (Note 8)                                    |                            | ±1                        | ±25                        | mV     |

| Offset Error Temperature<br>Coefficient       |            |                                             |                            | 1                         |                            | ppm/°C |

| Full-Scale Error                              |            | Code = 255, no load                         |                            |                           | 5                          | %      |

| Full-Scale Error Temperature<br>Coefficient   |            | Code = 255, no load                         |                            | ±10                       |                            | ppm/°C |

| DYNAMIC PERFORMANCE                           |            |                                             |                            |                           |                            |        |

| Voltage Output Slew Rate                      |            | Positive and negative                       |                            | 0.4                       |                            | V/µs   |

| Output Settling Time                          |            | 0.5LSB; 50k $\Omega$ and 50pF load (Note 9) |                            | 20                        |                            | μs     |

| Glitch Impulse                                |            | Code 127 to 128                             |                            | 40                        |                            | nV/s   |

| Wake-Up Time                                  |            | From shutdown                               |                            | 50                        |                            | μs     |

| DAC OUTPUT                                    |            |                                             |                            |                           |                            |        |

| Internal DAC Reference                        | VREFDAC    | (Note 10)                                   | 0.85 ×<br>AV <sub>DD</sub> | 0.9 ×<br>AV <sub>DD</sub> | 0.95 ×<br>AV <sub>DD</sub> | V      |

|                                               |            | Code = 255; 0 to 100µA                      |                            | 0.5                       |                            |        |

| Output Load Regulation                        |            | Code = 0; 0 to 100µA                        |                            | 0.5                       |                            | LSB    |

| Output Resistance                             |            | Power-down mode                             |                            | 1.0                       |                            | MΩ     |

|                                               | •          | TOUCH-SCREEN CONTROLLER                     | •                          |                           |                            |        |

|                                               |            | Y+, X+                                      |                            | 7                         |                            |        |

| On-Resistance                                 |            | Y-, X-                                      |                            | 9                         |                            | Ω      |

| Touch-Detection Internal Pullup<br>Resistance |            | X+ to AV <sub>DD</sub>                      |                            | 1                         |                            | MΩ     |

|                                               |            | KEYPAD CONTROLLER                           |                            |                           |                            |        |

| Pullup Resistance                             |            | C4, C3, C2, C1 (Note 11)                    |                            | 0.5                       |                            | kΩ     |

| Pulldown Resistance                           |            | R4, R3, R2, R1 (Note 11)                    |                            | 16                        |                            | kΩ     |

|                                               | ·          | DIGITAL INTERFACE                           |                            |                           |                            |        |

| DIGITAL INPUTS (SCLK, CS, DI                  | I, R_, C_) |                                             |                            |                           |                            |        |

| Input Voltage Low                             | VIL        |                                             |                            |                           | 0.3 ×<br>DV <sub>DD</sub>  | V      |

| Input Voltage High                            | VIH        |                                             | 0.7 ×<br>DV <sub>DD</sub>  |                           |                            | V      |

| Input Leakage Current                         | ١L         |                                             |                            | ±0.1                      | ±1                         | μA     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1233)}, DV_{DD} = AV_{DD} = +4.75V \text{ to } +5.25V \text{ (MAX1234)}, \text{ external reference } V_{REF} = 2.5V \text{ (MAX1233)}, V_{REF} = 4.096V \text{ (MAX1234)}; f_{SCLK} = 10MHz, f_{SAMPLE} = 50 \text{ksps}, 12-bit mode, 0.1\muF capacitor at REF, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ , unless otherwise noted. Typical values are at T\_A = +25^{\circ}C.)

| PARAMETER                     | SYMBOL                       | CONDITIONS                                | MIN                       | ТҮР | MAX  | UNITS |

|-------------------------------|------------------------------|-------------------------------------------|---------------------------|-----|------|-------|

| Input Capacitance             | CIN                          |                                           |                           | 15  |      | pF    |

| DIGITAL OUTPUT (DOUT)         |                              |                                           |                           |     |      |       |

| Output Voltage Low            | Mai                          | I <sub>SINK</sub> = 2mA                   |                           |     | 0.4  | v     |

| Output voltage Low            | V <sub>OL</sub>              | I <sub>SINK</sub> = 4mA                   |                           |     | 0.8  | v     |

| Output Voltage High           | V <sub>OH</sub>              | I <sub>SOURCE</sub> = 1.5mA               | DV <sub>DD</sub> -<br>0.5 |     |      | V     |

| DIGITAL OUTPUT (BUSY, PENIF   | RQ, KEYIRQ, I                | R_, C_)                                   |                           |     |      |       |

| Output Voltage Low            | VOL                          | I <sub>SINK</sub> = 0.2mA                 |                           |     | 0.4  | V     |

| Output Voltage High           | Vон                          | ISOURCE = 0.2mA                           | DV <sub>DD</sub> -<br>0.5 |     |      | V     |

|                               | 1                            | POWER REQUIREMENTS                        | I                         |     |      | 1     |

|                               | AV <sub>DD</sub> /           | MAX1233                                   | 2.7                       | 3   | 3.6  | N/    |

| Supply Voltage (Note 12)      | $DV_DD$                      | MAX1234                                   | 4.75                      | 5   | 5.25 | V     |

|                               |                              | Idle; all blocks shut down                |                           | 0.5 | 5    |       |

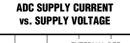

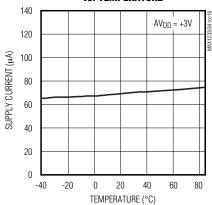

| Analog and Digital Supply     | IAVDD +<br>I <sub>DVDD</sub> | Only ADC on; f <sub>SAMPLE</sub> = 20ksps |                           | 150 | 500  |       |

| Current                       |                              | Only DAC on; no load                      |                           | 150 | 230  | μA    |

|                               |                              | Only internal reference on                |                           | 670 | 900  |       |

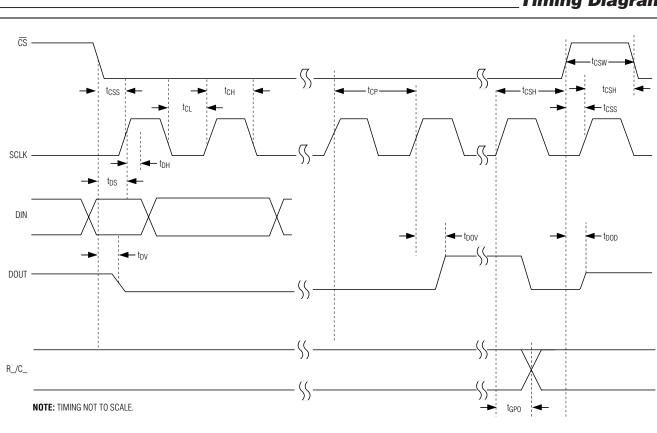

| TIMING CHARACTERISTICS        |                              |                                           |                           |     |      |       |

| SCLK Clock Period             | tCP                          |                                           | 100                       |     |      | ns    |

| SCLK Pulse Width High         | tсн                          |                                           | 40                        |     |      | ns    |

| SCLK Pulse Width Low          | t <sub>CL</sub>              |                                           | 40                        |     |      | ns    |

| DIN to SCLK Rise Setup        | tDS                          |                                           | 40                        |     |      | ns    |

| SCLK Rise to DIN Hold         | tDH                          |                                           | 0                         |     |      | ns    |

| SCLK Fall to DOUT Valid       | tdov                         | $C_{LOAD} = 50 pF$                        |                           |     | 40   | ns    |

| CS Fall to DOUT Enabled       | tDV                          | $C_{LOAD} = 50 pF$                        |                           |     | 45   | ns    |

| CS Rise to DOUT Disabled      | tDOD                         | $C_{LOAD} = 50 pF$                        |                           |     | 40   | ns    |

| CS Fall to SCLK Rise          | tcss                         |                                           | 40                        |     |      | ns    |

| CS Fall to SCLK Ignored       | tCSH                         |                                           | 0                         |     |      | ns    |

| SCLK Rise to R_/C_ Data Valid | tGPO                         | C <sub>LOAD</sub> = 50pF (Note 13)        |                           |     | 230  | ns    |

| CS Pulse Width High           | t <sub>CSW</sub>             |                                           | 40                        |     |      | ns    |

**Note 1:** Tested at  $DV_{DD} = AV_{DD} = +2.7V$  (MAX1233),  $DV_{DD} = AV_{DD} = +5V$  (MAX1234).

**Note 2:** Relative accuracy is the deviation of the analog value at any code from its theoretical value after the offset and gain errors have been removed.

Note 3: Offset nulled.

**Note 4:** Difference between TEMP1 and TEMP2; temperature in  $^{\circ}K = (V_{TEMP2} - V_{TEMP1}) \times 2680^{\circ}K/V$ . No calibration is necessary.

Note 5: Temperature coefficient is -2.1mV/°C. Determine absolute temperature by extrapolating from a calibrated value.

**Note 6:** ADC performance is limited by the conversion noise floor, typically 300µV<sub>P-P</sub>. An external reference below 2.5V can compromise the ADC performance.

Note 7: Guaranteed from code 5 to 255.

### **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V \text{ to } +3.6V \text{ (MAX1233)}, DV_{DD} = AV_{DD} = +4.75V \text{ to } +5.25V \text{ (MAX1234)}, \text{ external reference } V_{REF} = 2.5V \text{ (MAX1233)}, V_{REF} = 4.096V \text{ (MAX1234)}; f_{SCLK} = 10MHz, f_{SAMPLE} = 50 \text{ksps}, 12 \text{-bit mode}, 0.1\mu\text{F capacitor at REF}, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}\text{C}$ .)

Note 8: The offset value extrapolated from the range over which the INL is guaranteed.

- Note 9: Output settling time is measured by stepping from code 5 to 255, and from code 255 to 5.

- Note 10: Actual output voltage at full scale is 255/256 × VREFDAC.

- Note 11: Resistance is open when configured as GPIO or in shutdown.

- Note 12:  $AV_{DD}$  and  $DV_{DD}$  should not differ by more than 300mV.

**Note 13:** When configured as GPIO.

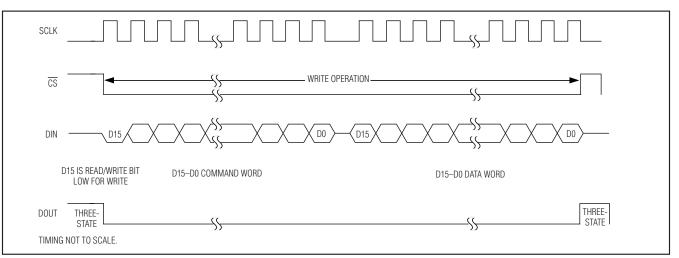

## **Timing Diagram**

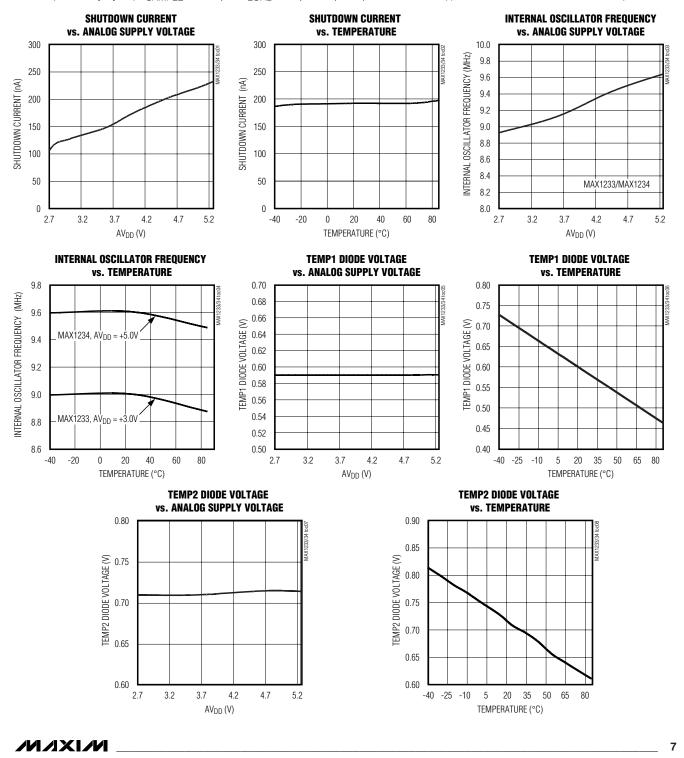

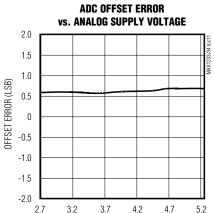

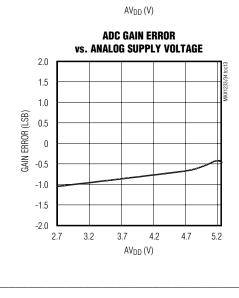

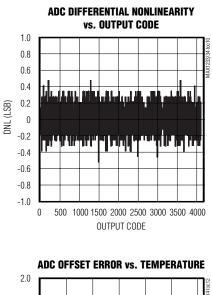

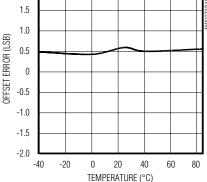

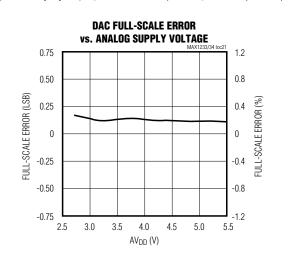

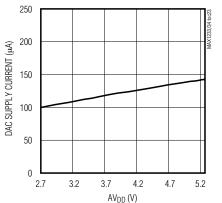

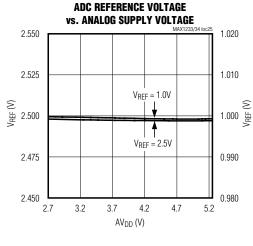

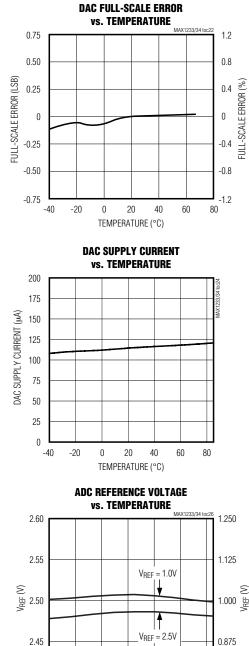

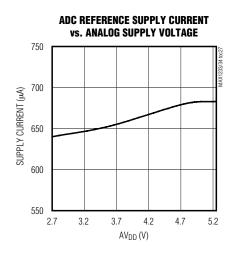

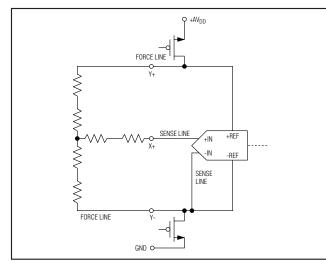

## **Typical Operating Characteristics**

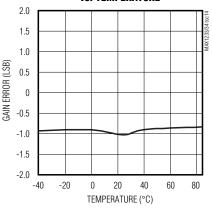

$(AV_{DD} = DV_{DD} = 3V (MAX1233) \text{ or } 5V (MAX1234), \text{ external } V_{REF} = +2.5V (MAX1233), \text{ external } V_{REF} = +4.096V (MAX1234), f_{SCLK} = 10MHz (50% duty cycle), f_{SAMPLF} = 20ksps, C_{LOAD} = 50pF, 0.1\muF \text{ capacitor at } REF, T_A = +25^{\circ}C, \text{ unless otherwise noted.}$

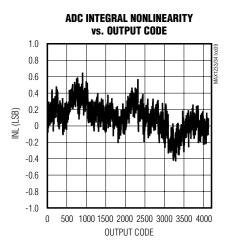

## **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = 3V (MAX1233) \text{ or } 5V (MAX1234), \text{ external } V_{REF} = +2.5V (MAX1233), \text{ external } V_{REF} = +4.096V (MAX1234), f_{SCLK} = 10MHz (50\% duty cycle), f_{SAMPLE} = 20ksps, C_{LOAD} = 50pF, 0.1\muF \text{ capacitor at REF, } T_A = +25^{\circ}C, \text{ unless otherwise noted.}$

ADC GAIN ERROR vs. TEMPERATURE

## **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = 3V (MAX1233) \text{ or } 5V (MAX1234), \text{ external } V_{REF} = +2.5V (MAX1233), \text{ external } V_{REF} = +4.096V (MAX1234), \text{ f}_{SCLK} = 10MHz (50\% duty cycle), \text{ f}_{SAMPLE} = 20ksps, C_{LOAD} = 50pF, 0.1\muF \text{ capacitor at } REF, T_A = +25^{\circ}C, \text{ unless otherwise noted.}$

250

M/IXI/M

ADC SUPPLY CURRENT vs. TEMPERATURE

#### DAC DIFFERENTIAL NONLINEARITY vs. Output code

### **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = 3V (MAX1233) \text{ or } 5V (MAX1234), \text{ external } V_{REF} = +2.5V (MAX1233), \text{ external } V_{REF} = +4.096V (MAX1234), \text{ f}_{SCLK} = 10MHz (50\% duty cycle), \text{ f}_{SAMPLE} = 20ksps, C_{LOAD} = 50pF, 0.1\muF \text{ capacitor at } REF, T_A = +25^{\circ}C, \text{ unless otherwise noted.}$

0.750

M/XX/M

60 80

40

TEMPERATURE (°C)

2.40

-40 -20

0 20

## **Typical Operating Characteristics (continued)**

$(AV_{DD} = DV_{DD} = 3V (MAX1233) \text{ or } 5V (MAX1234), \text{ external } V_{REF} = +2.5V (MAX1233), \text{ external } V_{REF} = +4.096V (MAX1234), \text{ } f_{SCLK} = 10MHz (50\% \text{ duty cycle}), \text{ } f_{SAMPLE} = 20 \text{ksps}, \text{ } C_{LOAD} = 50 \text{pF}, 0.1 \mu\text{F} \text{ capacitor at REF}, \text{ } T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$

## Pin Description

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                  |

|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

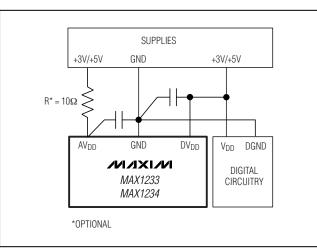

| 1   | DV <sub>DD</sub> | Positive Digital Supply Voltage, +2.7V to +3.6V for MAX1233, +4.75V to +5.25V for MAX1234. Bypass with a 0.1 $\mu$ F capacitor. Must be within 300mV of AV <sub>DD</sub> .                                                                                                                                                                                |

| 2   | AV <sub>DD</sub> | Positive Analog Supply Voltage, +2.7V to +3.6V for MAX1233, +4.75V to +5.25V for MAX1234. Bypass with a $0.1\mu$ F capacitor. Must be within 300mV of DV <sub>DD</sub> .                                                                                                                                                                                  |

| 3*  | X+               | X+ Position Input                                                                                                                                                                                                                                                                                                                                         |

| 4*  | Y+               | Y+ Position Input                                                                                                                                                                                                                                                                                                                                         |

| 5*  | Х-               | X- Position Input                                                                                                                                                                                                                                                                                                                                         |

| 6*  | Y-               | Y- Position Input                                                                                                                                                                                                                                                                                                                                         |

| 7   | GND              | Analog and Digital Ground                                                                                                                                                                                                                                                                                                                                 |

| 8*  | BAT1             | Battery Monitoring Input 1. Measures battery voltages up to 6V.                                                                                                                                                                                                                                                                                           |

| 9*  | BAT2             | Battery Monitoring Input 2. Measures battery voltages up to 6V.                                                                                                                                                                                                                                                                                           |

| 10* | AUX1             | Auxiliary Analog Input 1 to ADC. Measures analog voltages from zero to V <sub>REF</sub> .                                                                                                                                                                                                                                                                 |

| 11* | AUX2             | Auxiliary Analog Input 2 to ADC. Measures analog voltages from zero to VREF.                                                                                                                                                                                                                                                                              |

| 12  | REF              | Voltage Reference Output/Input. Reference voltage for analog-to-digital conversion. In internal reference mode, the reference buffer provides a 2.5V or 1.0V nominal output. In external reference mode, apply a reference voltage between 1.0V and AV <sub>DD</sub> . Bypass REF to GND with a $0.1\mu$ F capacitor in the external reference mode only. |

| 13  | DACOUT           | DAC Voltage Output; 0.9 × AV <sub>DD</sub> Full Scale                                                                                                                                                                                                                                                                                                     |

| 14  | R4               | Keypad Row 4. Can be reconfigured as GPIO3.                                                                                                                                                                                                                                                                                                               |

| 15  | R3               | Keypad Row 3. Can be reconfigured as GPIO2.                                                                                                                                                                                                                                                                                                               |

| 16  | R2               | Keypad Row 2. Can be reconfigured as GPIO1.                                                                                                                                                                                                                                                                                                               |

| 17  | R1               | Keypad Row 1. Can be reconfigured as GPIO0.                                                                                                                                                                                                                                                                                                               |

| 18  | C1               | Keypad Column 1. Can be reconfigured as GPIO4.                                                                                                                                                                                                                                                                                                            |

## Pin Description (continued)

| PIN | NAME   | FUNCTION                                                                                                                                                                          |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | C2     | Keypad Column 2. Can be reconfigured as GPIO5.                                                                                                                                    |

| 20  | C3     | Keypad Column 3. Can be reconfigured as GPIO6.                                                                                                                                    |

| 21  | C4     | Keypad Column 4. Can be reconfigured as GPIO7.                                                                                                                                    |

| 22  | KEYIRQ | Active-Low Keypad Interrupt. KEYIRQ is low when a key press is detected.                                                                                                          |

| 23  | PENIRQ | Active-Low Pen Touch Interrupt. PENIRQ is low when a screen touch is detected.                                                                                                    |

| 24  | DOUT   | Serial Data Output. Data is clocked out at SCLK falling edge. High impedance when $\overline{\text{CS}}$ is high.                                                                 |

| 25  | BUSY   | Active-Low Busy Output. BUSY goes low and stays low during each functional operation. The host controller should wait until BUSY is high again before using the serial interface. |

| 26  | DIN    | Serial Data Input. Data is clocked in on the rising edge of SCLK.                                                                                                                 |

| 27  | SCLK   | Serial Clock Input. Clocks data in and out of the serial interface and sets the conversion speed (duty cycle must be 30% to 70%).                                                 |

| 28  | CS     | Active-Low Chip Select. Data is not clocked into DIN unless $\overline{CS}$ is low. When $\overline{CS}$ is high, DOUT is high impedance.                                         |

| _   | EP     | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point.                        |

\*ESD protected: ±8kV Contact, ±15kV Air.

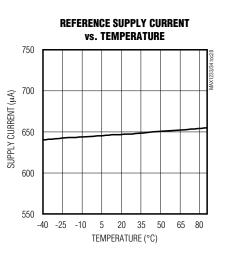

### Detailed Description

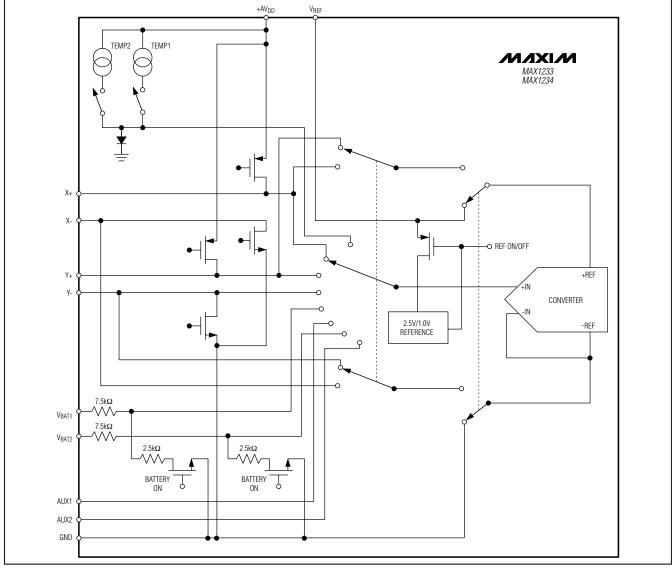

The MAX1233/MAX1234 are 4-wire touch-screen controllers. Figure 1 shows the functional diagram of the MAX1233/MAX1234. Each device includes a 12-bit sampling ADC, 8-bit voltage output DAC, keypad scanner that can also be configured as a GPIO, internal clock, reference, temperature sensor, two battery monitor inputs, two auxiliary analog inputs, SPI/QSPI/ MICROWIRE-compatible serial interface, and low onresistance switches for driving touch screens.

The 16-bit register inside the MAX1233/MAX1234 allows for easy control and stores results that can be read at any time. The BUSY output indicates that a functional operation is in progress. The PENIRQ and KEYIRQ outputs, respectively, indicate that a screen touch or a key press has occurred.

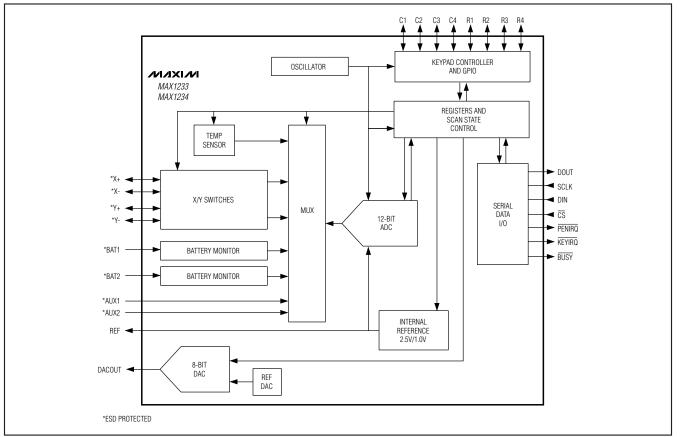

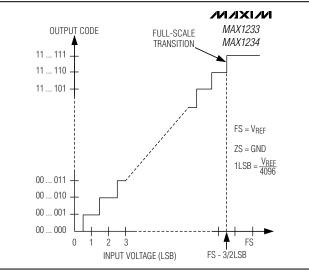

### **Touch-Screen Operation**

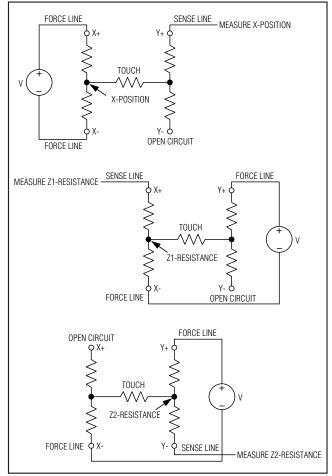

The 4-wire touch-screen controller works by creating a voltage gradient across the vertical or horizontal resistive touch screen connected to the analog inputs of the MAX1233/MAX1234, as shown in Figure 2. The voltage across the touch-screen panels is applied through internal MOSFET switches that connect each resistive layer to AV<sub>DD</sub> and ground. For example, to measure the Y position when a pointing device presses on the touch screen, the Y+ and Y- drivers are turned on, connecting one side of the vertical resistive layer to AV<sub>DD</sub> and the other side to ground. The horizontal resistive layer functions as a sense line. One side of this resistive layer gets connected to the X+ input, while the other side is left

open or floating. The point where the touch screen is pressed brings the two resistive layers in contact and creates a voltage-divider at that point. The data converter senses the voltage at the point of contact through the X+ input and digitizes it.

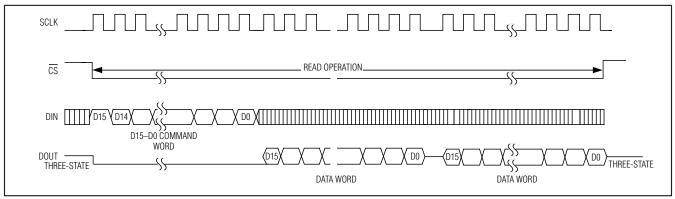

## 12-Bit ADC

#### Analog Inputs

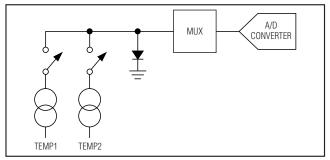

Figure 3 shows a block diagram of the ADC's analog input section including the input multiplexer, the differential input, and the differential reference. The input multiplexer switches between X+, X-, Y+, Y-, AUX1, AUX2, BAT1, BAT2, and the internal temperature sensor.

The time required for the T/H to acquire an input signal is a function of how quickly its input capacitance is charged. If the input signal's source impedance is high, the acquisition time lengthens, and more time must be allowed. The acquisition time ( $t_{ACQ}$ ) is the maximum time the device takes to acquire the input signal to 12-bit accuracy. Configure  $t_{ACQ}$  by writing to the ADC control register. See Table 1 for the maximum input signal source impedance (R<sub>SOURCE</sub>) for complete settling during acquisition.

Accommodate higher source impedances by placing a  $0.1\mu$ F capacitor between the analog input and GND.

#### Input Bandwidth

The ADC's input-tracking circuitry has a 0.5MHz smallsignal bandwidth. To avoid high-frequency signals being aliased into the frequency band of interest, antialias filtering is recommended.

12 \_

Figure 1. Block Diagram

Figure 2. Touch-Screen Measurement

# Table 1. Maximum Input SourceImpedance

| ACQUISITION<br>TIME (µs) | RESOLUTION<br>(BITS) | MAXIMUM R <sub>SOURCE</sub> FOR<br>COMPLETE SETTLING<br>DURING ACQUISITION (kΩ) |

|--------------------------|----------------------|---------------------------------------------------------------------------------|

| 1.5                      | 8                    | 2.6                                                                             |

| 1.5                      | 10                   | 2.0                                                                             |

| 1.5                      | 12                   | 1.5                                                                             |

| 5.0                      | 8                    | 23                                                                              |

| 5.0                      | 10                   | 19                                                                              |

| 5.0                      | 12                   | 15                                                                              |

| 95                       | 8                    | 560                                                                             |

| 95                       | 10                   | 470                                                                             |

| 95                       | 12                   | 400                                                                             |

Figure 3. Simplified Diagram of Analog Input Section

#### Analog Input Protection

Internal protection diodes that clamp the analog input to  $AV_{DD}$  and GND allow the analog input pins to swing from GND - 0.3V to  $AV_{DD} + 0.3V$  without damage. Analog inputs must not exceed  $AV_{DD}$  by more than 50mV or be lower than GND by more than 50mV for accurate conversions. If an off-channel analog input voltage exceeds the supplies, limit the input current to 50mA. **All analog inputs are also fully ESD protected**

to  $\pm$ 8kV, using the Contact-Discharge method and  $\pm$ 15kV using the Air-Gap method specified in IEC-1000-4-2.

### **Reference for ADC**

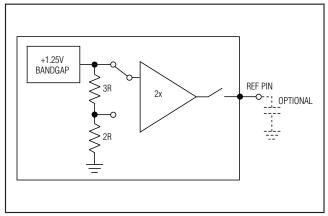

#### Internal Reference

The MAX1233/MAX1234 offer an internal voltage reference for the ADC that can be set to +1.0V or +2.5V. The MAX1233/MAX1234 typically use the internal reference for battery monitoring, temperature measurement, and for

Downloaded from: http://www.datasheetcatalog.com/

Figure 4. Block Diagram of the Internal Reference

measurement of the auxiliary inputs. Figure 4 shows the on-chip reference circuitry of the MAX1233/MAX1234.

Set the internal reference voltage by writing to the RFV bits in the ADC control register (see Tables 4, 5, and 12). The MAX1233/MAX1234 can accept an external reference connected to REF for ADC conversion.

#### External Reference

The MAX1233/MAX1234 can accept an external reference connected to the REF pin for ADC conversions. The internal reference should be disabled (RES1 = 1) when using an external reference. At a conversion rate of 50ksps, an external reference at REF must deliver up to 15µA of load current and have  $50\Omega$  or less output impedance. If the external reference has high output impedance or is noisy, bypass it close to the REF pin with a 0.1µF capacitor.

Selecting Internal or External Reference

Set the type of reference being used by programming the ADC control register. To select the internal reference, clock zeros into bits [A/D3:A/D0] and a zero to bit RES1, as shown in the *Control Registers* section. To change to external reference mode, clock zeros into bits [A/D3:A/D0] and a one to bit RES1. See Table 13 for more information about selecting an internal or external reference for the ADC.

#### **Reference Power Modes**

#### Auto Power-Down Mode (RES1 = RES0 = 0)

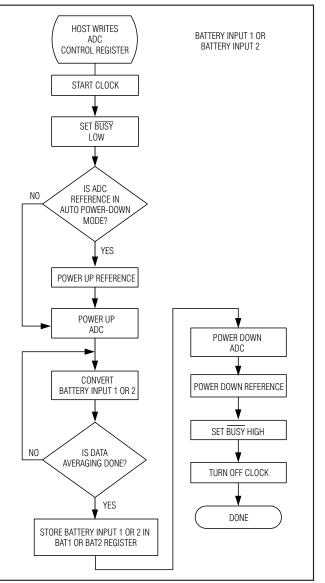

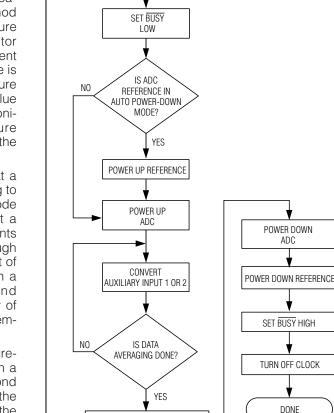

The MAX1233/MAX1234 are in auto power-down mode at initial power-up. Set the RES1 and RES0 bits to zero to use the MAX1233/MAX1234 in the auto power-down mode. In this mode, the internal reference is normally off. When a command to perform a battery measurement, temperature measurement, or auxiliary input measurement is written to the ADC control register, the device powers on the internal reference, waits for the internal reference to settle, completes the requested scan, and powers down the internal reference. The reference power delay depends upon the ADC resolution selected (see Table 8). Do not bypass REF with an external capacitor when performing scans in auto power-down mode.

#### Full-Power Mode (RES1 = 0, RES0 = 1)

In the full-power mode, the RES1 bit is set LOW and RES0 bit is set HIGH. In this mode, the device is powered up and the internal ADC reference is always ON. The MAX1233/MAX1234 internal reference remains fully powered after completing a scan.

#### **Internal Clock**

The MAX1233/MAX1234 operate from an internal oscillator, which is accurate to within 20% of the 10MHz specified clock rate. The internal oscillator controls the timing of the acquisition, conversion, touch-screen settling, reference power-up, and keypad debounce times.

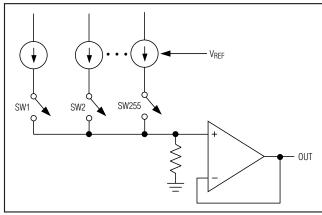

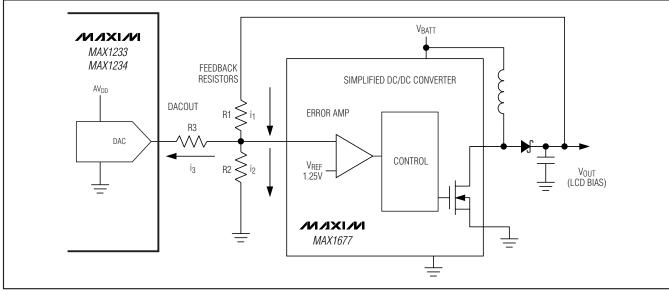

#### 8-Bit DAC

The MAX1233/MAX1234 have a voltage-output, true 8-bit monotonic DAC with less than 1LSB integral nonlinearity error and less than 1LSB differential nonlinearity error. It requires a supply current of only 150µA (typ) and provides a buffered voltage output. The DAC is at midscale code at power-up and remains there until a new code is written to the DAC register. During shutdown, the DAC's output is pulled to ground with a 1M $\Omega$  load.

The internal DAC can be used in various system applications such as LCD/TFT-bias control, automatic tuning (VCO), power amplifier bias control, programmable threshold levels, and automatic gain control (AGC).

The 8-bit DAC in the MAX1233/MAX1234 employs a current-steering topology as shown in Figure 5. At the core of this DAC is a reference voltage-to-current converter (V/I) that generates a reference current. This current is mirrored to 255 equally weighted current sources. DAC switches control the outputs of these current mirrors so that only the desired fraction of the total current-mirror currents is steered to the DAC output. The current is then converted to a voltage across a resistor, and the output amplifier buffers this voltage.

#### DAC Output Voltage

The 8-bit DAC code is binary unipolar with  $1LSB = (V_{REF}/256)$ . The DAC has a full-scale output voltage of  $(0.9 \times AV_{DD} - 1LSB)$ .

MAX1233/MAX1234

Figure 5. DAC Current-Steering Topology

#### **Output Buffer**

The DAC voltage output is an internally buffered unitygain follower that slews at up to  $\pm 0.4$ V/µs. The output can swing from zero to full scale. With a 1/4FS to 3/4FS output transition, the amplifier output typically settles to 1/2LSB in less than 5µs when loaded with 10k $\Omega$  in parallel with 50pF. The buffer amplifier is stable with any combination of resistive loads >10k $\Omega$  and capacitive loads <50pF.

#### Power-On Reset

All registers of the MAX1233/MAX1234 power up at a default zero state, except the DAC data register, which is set to 10000000, so the output is at midscale.

#### **Keypad Controller and GPIO**

The keypad controller is designed to interface a matrixtype 4 rows × 4 columns (16 keys or fewer) keypad to a host controller. The KEY control register controls keypad interrupt, keypad scan, and keypad debounce times. The KeyMask and ColumnMask registers enable masking of a particular key or an entire column of the keypad when they are not in use. The MAX1233/MAX1234 offer two keypad data registers. KPData1 is the pending register. KPData2 holds keypad scan results of only the unmasked keys. If 12 or fewer keys are being monitored, one or more of the row/column pins of the MAX1233/MAX1234 can be software programmed as GPIO pins.

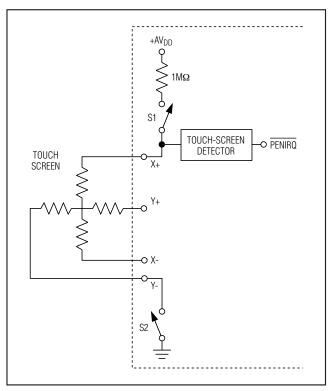

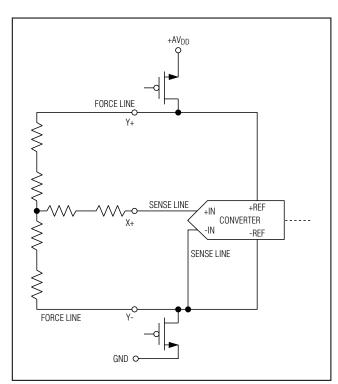

#### **Touch-Screen Detection**

Touch-screen detection can be enabled or disabled by writing to the ADC control register as shown in Table 4. Touch-screen detection is disabled at initial power-up. Once touch-screen detection is enabled, the Y- driver is on and the Y- pin is connected to GND. The X+ pin is internally pulled to  $AV_{DD}$  through a  $1M\Omega$  resistor as

Figure 6. Touch-Screen Detection Block Diagram

shown in Figure 6. When the screen is touched, the X+ pin is pulled to GND through the touch screen and a touch is detected.

When the 1M $\Omega$  pullup resistor is first connected, the X+ pin can be floating near ground. To prevent false touch detection in this case, the X+ pin is precharged high for 0.1 $\mu$ s using the 7 $\Omega$  PMOS driver before touch detection begins.

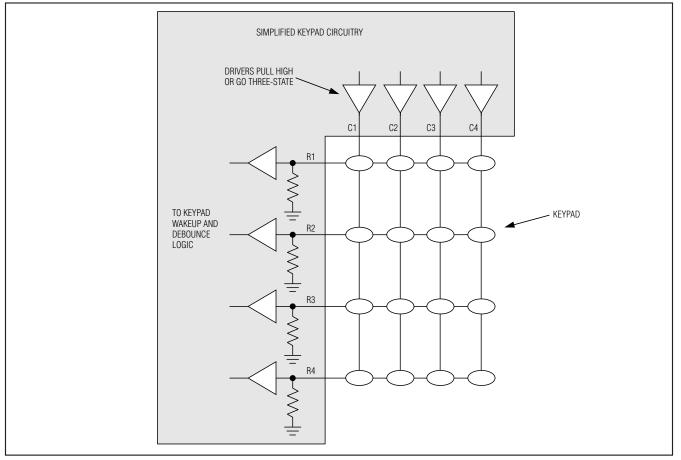

### **Key-Press Detection**

Key-press detection can be enabled or disabled by writing to the keypad control register as shown in Table 17. Key-press detection is disabled at initial power-up. Once key-press detection is enabled, the C\_ pins are internally connected to DV<sub>DD</sub> and the R\_ pins are internally pulled to GND through a 16k $\Omega$  resistor. When a key is pressed, the associated row pin is pulled to DV<sub>DD</sub> and the key press is detected. Figure 7 shows the key-press detection circuitry.

#### Interrupts

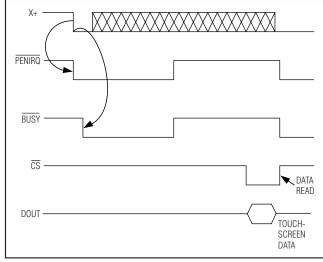

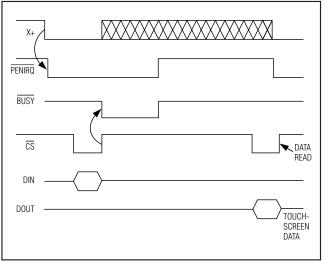

#### PEN Interrupt Request (PENIRQ)

The PENIRQ output can be used to alert the host controller of a screen touch. The PENIRQ output is normally high and goes low after a screen touch is detected.

Figure 7. Key-Press Detection Circuitry

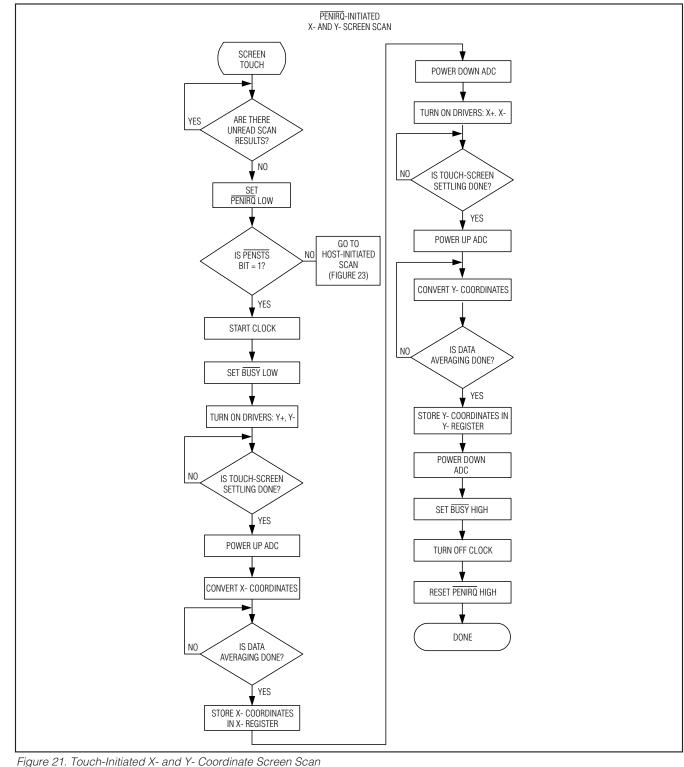

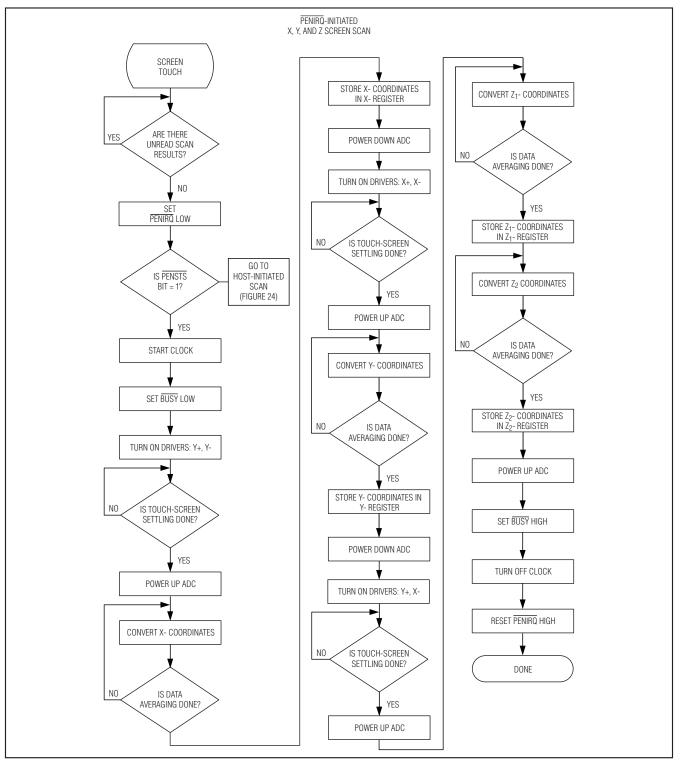

Figure 8a. Timing Diagram for Touch-Initiated Screen Scan

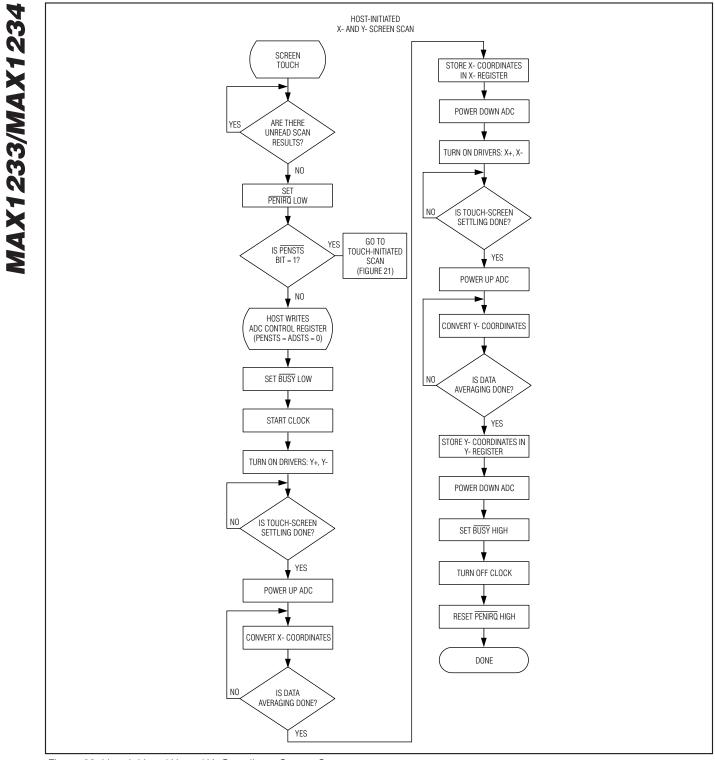

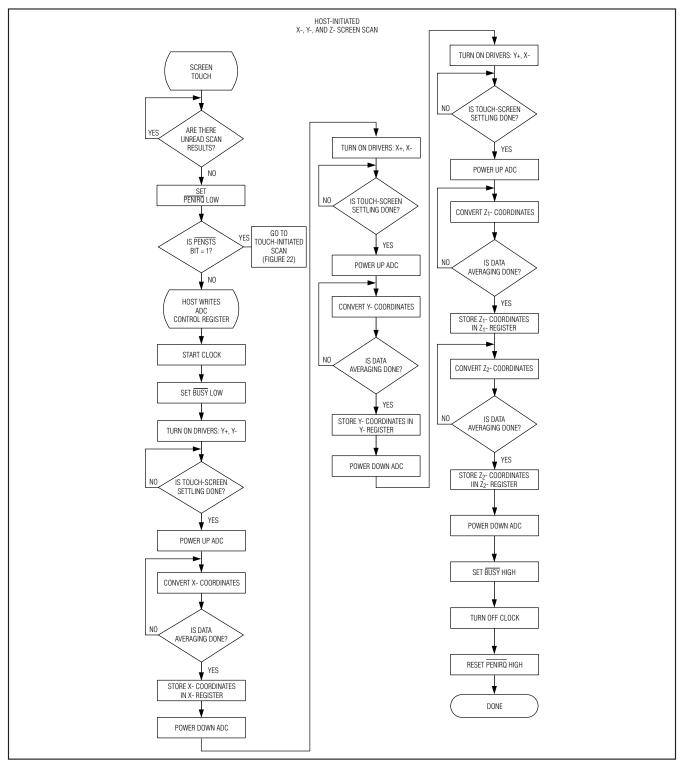

Figure 8b. Timing Diagram for Host-Initiated Screen Scan

PENIRQ returns high only after a touch-screen scan is completed. PENIRQ does not go low again until one of the touch-screen data registers is read. Figures 8a and 8b show the timing diagrams for the PENIRQ pin.

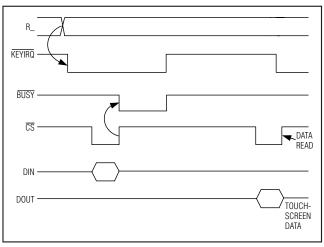

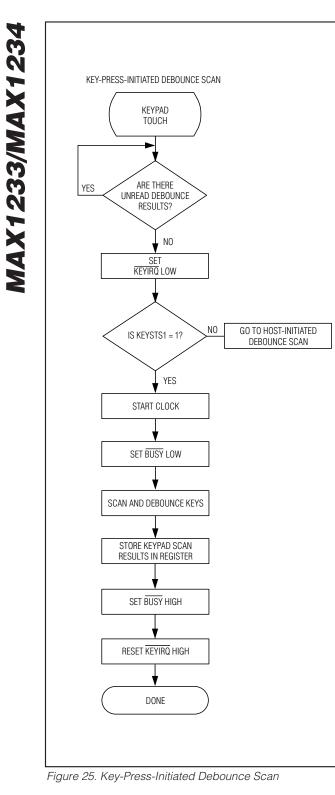

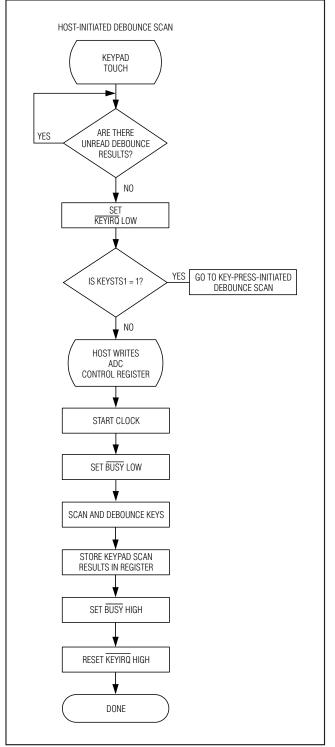

### Keypad Interrupt Request (KEYIRQ)

The KEYIRQ output can be used to alert the host controller of a key press. The KEYIRQ output is normally high and goes low after a key press is detected. KEYIRQ returns high only after a key-press scan is completed. KEYIRQ does not go low again until one of the key-press data registers is read. Figures 9a and 9b show the timing diagrams for the KEYIRQ pin.

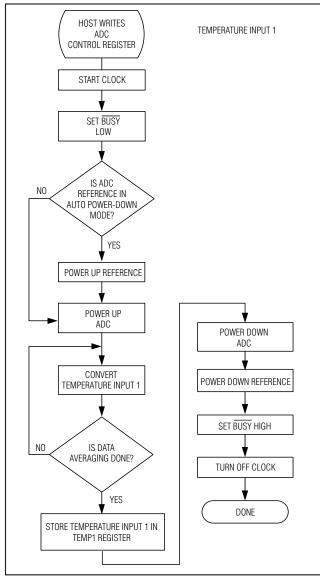

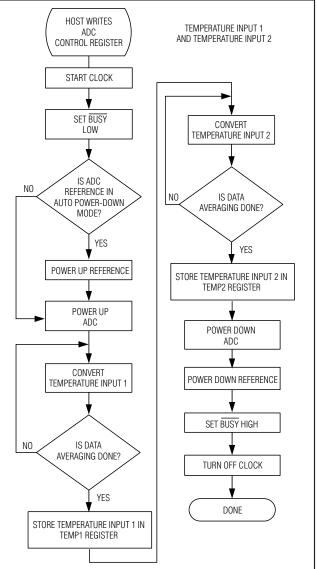

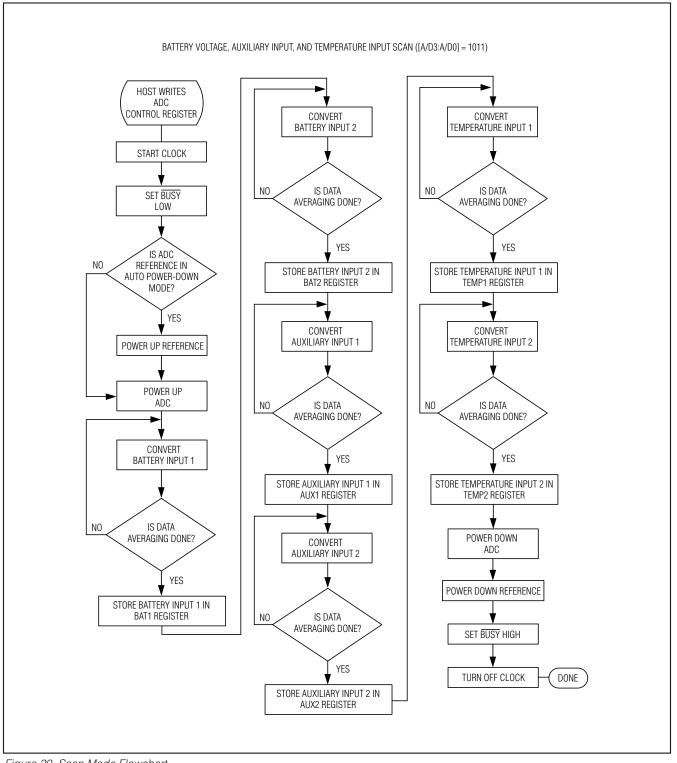

### **Busy Indicator (BUSY)**

BUSY informs the host processor that a scan is in progress. BUSY is normally high and goes low and stays low during each functional operation. The host controller should wait until BUSY is high again before using the serial interface.

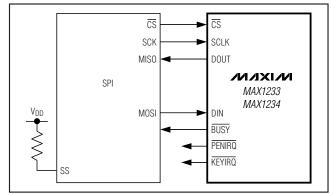

**Digital Interface** The MAX1233/MAX1234 interface to the host controller through a standard 3-wire serial interface at up to 10MHz. DIN and  $\overline{CS}$  are the digital inputs to the MAX1233/MAX1234. DOUT is the serial data output. Data is clocked out at the SCLK falling edge and is high impedance when  $\overline{CS}$  is high. When performing an ADC scan, CS must de-assert high before the end of the first conversion, otherwise the conversion results will not be stored. PENIRQ and KEYIRQ communicate interrupts from the touch-screen and keypad controllers to the host processor when a screen touch or a key press is detected. BUSY informs the host processor that a scan is in progress. In addition to these digital I/Os, the row and column pins of the keypad controller can be programmed as GPIO pins.

#### **Communications Protocol**

The MAX1233/MAX1234 are controlled by reading from and writing to registers through the 3-wire serial interface. These registers are addressed through a 16-bit command that is sent prior to the data. The command is shown in Table 2.

The first 16 bits after the falling edge of  $\overline{CS}$  contain the command word. The command word begins with an  $R/\overline{W}$  bit, which specifies the direction of data flow on the serial bus. Bits 14 through 7 are reserved for future use. Bit 6 specifies the page of memory in which the

**Table 2. Command Word Format**

R\_ KEYIRQ BUSY CS DOUT DOUT DOUT TOUCH-SCREEN DATA

Figure 9a. Timing Diagram for Key-Press-Initiated Debounce Scan

Figure 9b. Timing Diagram for Host-Initiated Keypad Debounce Scan

desired register is located. The last 6 bits specify the address of the desired register. The next 16 bits of data are read from or written to the address specified in the command word. After 32 clock cycles, the interface automatically increments its address pointer and continues reading or writing until the rising edge of  $\overline{CS}$ , or until it reaches the end of the page.

| BIT15<br>MSB | BIT14 | BIT13 | BIT12 | BIT11 | BIT10 | BIT9 | BIT8 | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0<br>LSB |

|--------------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|-------------|

| R/W          | RES   | RES   | RES   | RES   | RES   | RES  | RES  | RES  | PAGE | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0        |

18

| WRITE<br>COMMAND<br>(HEX) | READ<br>COMMAND<br>(HEX) | REGISTER<br>NAME | BIT15   | BIT14   | BIT13 | BIT12 | BIT11 | BIT10 | BIT9 | BIT8 | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | віто |

|---------------------------|--------------------------|------------------|---------|---------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| -                         | 0x8000                   | Х                | 0       | 0       | 0     | 0     | X11   | X10   | Х9   | X8   | X7   | X6   | X5   | X4   | X3   | X2   | X1   | X0   |

| _                         | 0x8001                   | Y                | 0       | 0       | 0     | 0     | Y11   | Y10   | Y9   | Y8   | Y7   | Y6   | Y5   | Y4   | Y3   | Y2   | Y1   | Y0   |

| _                         | 0x8002                   | Z1               | 0       | 0       | 0     | 0     | Z1_11 | Z1_10 | Z1_9 | Z1_8 | Z1_7 | Z1_6 | Z1_5 | Z1_4 | Z1_3 | Z1_2 | Z1_1 | Z1_0 |

| —                         | 0x8003                   | Z2               | 0       | 0       | 0     | 0     | Z2_11 | Z2_10 | Z2_9 | Z2_8 | Z2_7 | Z2_6 | Z2_5 | Z2_4 | Z2_3 | Z2_2 | Z2_1 | Z2_0 |

| _                         | 0x8004                   | KPD              | K15     | K14     | K13   | K12   | K11   | K10   | K9   | K8   | K7   | K6   | K5   | K4   | K3   | K2   | K1   | K0   |

| _                         | 0x8005                   | BAT1             | 0       | 0       | 0     | 0     | B1_11 | B1_10 | B1_9 | B1_8 | B1_7 | B1_6 | B1_5 | B1_4 | B1_3 | B1_2 | B1_1 | B1_0 |

| _                         | 0x8006                   | BAT2             | 0       | 0       | 0     | 0     | B2_11 | B2_10 | B2_9 | B2_8 | B2_7 | B2_6 | B2_5 | B2_4 | B2_3 | B2_2 | B2_1 | B2_0 |

| _                         | 0x8007                   | AUX1             | 0       | 0       | 0     | 0     | A1_11 | A1_10 | A1_9 | A1_8 | A1_7 | A1_6 | A1_5 | A1_4 | A1_3 | A1_2 | A1_1 | A1_0 |

| —                         | 0x8008                   | AUX2             | 0       | 0       | 0     | 0     | A2_11 | A2_10 | A2_9 | A2_8 | A2_7 | A2_6 | A2_5 | A2_4 | A2_3 | A2_2 | A2_1 | A2_0 |

| _                         | 0x8009                   | TEMP1            | 0       | 0       | 0     | 0     | T1_11 | T1_10 | T1_9 | T1_8 | T1_7 | T1_6 | T1_5 | T1_4 | T1_3 | T1_2 | T1_1 | T1_0 |

| —                         | 0x800A                   | TEMP2            | 0       | 0       | 0     | 0     | T2_11 | T2_10 | T2_9 | T2_8 | T2_7 | T2_6 | T2_5 | T2_4 | T2_3 | T2_2 | T2_1 | T2_0 |

| 0x000B                    | 0x800B                   | DAC data         | 0       | 0       | 0     | 0     | 0     | 0     | 0    | 0    | DA7  | DA6  | DA5  | DA4  | DA3  | DA2  | DA1  | DA0  |

| 0x000F                    | 0x800F                   | GPIO data        | GPD7    | GPD6    | GPD5  | GPD4  | GPD3  | GPD2  | GPD1 | GPD0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| _                         | 0x8010                   | KPData1          | K1_15   | K1_14   | K1_13 | K1_12 | K1_11 | K1_10 | K1_9 | K1_8 | K1_7 | K1_6 | K1_5 | K1_4 | K1_3 | K1_2 | K1_1 | K1_0 |

| —                         | 0x8011                   | KPData2          | K2_15   | K2_14   | K2_13 | K2_12 | K2_11 | K2_10 | K2_9 | K2_8 | K2_7 | K2_6 | K2_5 | K2_4 | K2_3 | K2_2 | K2_1 | K2_0 |

| 0x0040                    | 0x8040                   | ADC control      | PENSTS  | ADSTS   | A/D3  | A/D2  | A/D1  | A/D0  | RES1 | RES0 | AVG1 | AVG0 | CNR1 | CNR0 | ST2  | ST1  | ST0  | RFV  |

| 0x0041                    | 0x8041                   | KEY control      | KEYSTS1 | KEYSTS0 | DBN2  | DBN1  | DBN0  | HLD2  | HLD1 | HLD0 | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x0042                    | 0x8042                   | DAC control      | DAPD    | 0       | 0     | 0     | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x004E                    | 0x804E                   | GPIO pullup      | PU7     | PU6     | PU5   | PU4   | PU3   | PU2   | PU1  | PU0  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0x004F                    | 0x804F                   | GPIO control     | GP7     | GP6     | GP5   | GP4   | GP3   | GP2   | GP1  | GP0  | OE7  | OE6  | OE5  | OE4  | OE3  | OE2  | OE1  | OE0  |

| 0x0050                    | 0x8050                   | KPKeyMask        | KM15    | KM14    | KM13  | KM12  | KM11  | KM10  | KM9  | KM8  | KM7  | KM6  | KM5  | KM4  | KM3  | KM2  | KM1  | KM0  |

| 0x0051                    | 0x8051                   | KPColumnMask     | CM4     | CM3     | CM2   | CM1   | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

### Table 3. Register Summary

Note: All other registers are reserved and should always be 0. Power-on reset state is DAC data at midscale (0x0080), all other registers are 0.

#### Memory Map

In order to read the entire first page of memory, for example, the host processor must send the The MAX1233/MAX1234s' internal memory is divided MAX1233/MAX1234 the command 0x8000H. The into two pages-one for data and one for control, each of which contains thirty-two 16-bit registers. MAX1233/MAX1234 then begin clocking out 16-bit data starting with the X-data register. In order to write to the second page of memory, the host processor sends the Table 3 provides a summary of all registers and bit MAX1233/MAX1234 the command 0x0040H. The suclocations of the MAX1233/MAX1234. ceeding data is then written in 16-bit words beginning

### ADC Control Register

**Control Registers**

The ADC measures touch position, touch pressure, battery voltage, auxiliary analog inputs, and temperature. The ADC control register determines which input is selected and converted. Tables 4 and 5 show the format and bit descriptions for the ADC control register.

Figure 10a. Timing Diagram of Write Operation

with the ADC control register. Figures 10a and 10b show

a complete write and read operation, respectively,

between the processor and the MAX1233/MAX1234.

Figure 10b. Timing Diagram of Read Operation

### Table 4. ADC Control Register (Write 0x0040/Read 0x8040)

| BIT15  | BIT14 | BIT13 | BIT12 | BIT11 | BIT10 | BIT9 | BIT8 | BIT7 | BIT6 | BIT5 | BIT4 | BIT3 | BIT2 | BIT1 | BIT0 |

|--------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|

| PENSTS | ADSTS | A/D3  | A/D2  | A/D1  | A/D0  | RES1 | RES0 | AVG1 | AVG0 | CNR1 | CNR0 | ST2  | ST1  | ST0  | RFV  |

M/IXI/N

#### Bits 14-15: Pen Interrupt Status and ADC Status Bits

These bits are used to control or monitor ADC scans.

#### Bits 10-13: ADC Scan Select

These bits control which input to convert and which converter mode is used. The bits are identical regardless of a read or write. See Table 7 for details about using these bits.

#### **Bits 8-9: ADC Resolution Control**

These bits specify the ADC resolution and are identical regardless of read or write. Table 8 shows how to use these bits to set the resolution.

#### Bits 6-7: Converter Averaging Control

These bits specify the number of data averages the converter performs. Table 9 shows how to program for the desired number of averages. When averaging is used, ADSTS and BUSY indicate the converter is busy until all conversions needed for the averaging finish. These bits are identical, regardless of read or write.

#### Bits 4-5: ADC Conversion Rate Control

These bits specify the internal conversion rate, which the ADC uses to perform a single conversion, as shown in Table 10. Lowering the conversion rate also reduces power consumption. These bits are identical, regardless of read or write.

### Table 5. ADC Control Register Bit Descriptions (Write 0x0040/Read 0x8040)

| BIT      | NAME   | DESCRIPTION                                                                    |  |  |  |

|----------|--------|--------------------------------------------------------------------------------|--|--|--|

| 15 (MSB) | PENSTS | Read: pen interrupt status; Write: sets interrupt initiated touch-screen scans |  |  |  |

| 14       | ADSTS  | Read: ADC status; Write: stops ADC                                             |  |  |  |

| 13       | A/D3   | Selects ADC scan functions                                                     |  |  |  |

| 12       | A/D2   | Selects ADC scan functions                                                     |  |  |  |

| 11       | A/D1   | Selects ADC scan functions                                                     |  |  |  |

| 10       | A/D0   | Selects ADC scan functions                                                     |  |  |  |

| 9        | RES1   | Controls ADC resolution                                                        |  |  |  |

| 8        | RES0   | Controls ADC resolution                                                        |  |  |  |

| 7        | AVG1   | Controls ADC result averaging                                                  |  |  |  |

| 6        | AVG0   | Controls ADC result averaging                                                  |  |  |  |

| 5        | CNR1   | Controls ADC conversion rate                                                   |  |  |  |

| 4        | CNR0   | Controls ADC conversion rate                                                   |  |  |  |

| 3        | ST2    | Controls touch-screen settling wait time                                       |  |  |  |

| 2        | ST1    | Controls touch-screen settling wait time                                       |  |  |  |

| 1        | ST0    | Controls touch-screen settling wait time                                       |  |  |  |

| 0 (LSB)  | RFV    | Chooses 1.0V or 2.5V reference                                                 |  |  |  |

### **Table 6. ADSTS Bit Operation**

| PENSTS | ADSTS | READ FUNCTION                                               | WRITE FUNCTION                                                                                                                                      |

|--------|-------|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | 0     | No screen touch detected;<br>scan or conversion in progress | Performs one scan and waits to detect a screen touch. Upon detection, issues an interrupt and waits until told to scan by the host controller.      |

| 1      | 0     | Screen touch detected;<br>scan or conversion in progress    | Stops any ongoing scan and waits to detect a screen touch. Upon detection, issues an interrupt and performs a scan.                                 |

| 0      | 1     | No screen touch detected;<br>data available                 | Stops any ongoing scan and waits to detect a screen touch. Upon detection, issues an interrupt and waits until told to scan by the host controller. |

| 1      | 1     | Screen touch detected;<br>data available                    | Stops any ongoing scan and powers down the screen touch detection circuit. No screen touches are detected in this mode.                             |

### Table 7. ADC Scan Select (Touch Screen, Battery, Auxiliary Channels, and Temperature)

| A/D3 | A/D2 | A/D1 | A/D0 | FUNCTION                                                                                                                                                                |

|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 0    | 0    | 0    | Configures the ADC reference as selected by RES [1:0] bits as shown in Table 13. No measurement is performed.                                                           |

| 0    | 0    | 0    | 1    | Measures X/Y touch position and returns results to the X and Y data registers.                                                                                          |

| 0    | 0    | 1    | 0    | Measures X/Y touch position and Z1/Z2 touch pressure and returns results to the X, Y, Z1, and Z2 data registers.                                                        |

| 0    | 0    | 1    | 1    | Measures X touch position and returns results to the X data register.                                                                                                   |

| 0    | 1    | 0    | 0    | Measures Y touch position and returns results to the Y data register.                                                                                                   |

| 0    | 1    | 0    | 1    | Measures Z1/Z2 touch pressure and returns results to the Z1 and Z2 data register.                                                                                       |

| 0    | 1    | 1    | 0    | Measures Battery Input 1 through a 4:1 divider and returns results to the BAT1 data register.                                                                           |

| 0    | 1    | 1    | 1    | Measures Battery Input 2 through a 4:1 divider and returns results to the BAT2 data register.                                                                           |

| 1    | 0    | 0    | 0    | Measures Auxiliary Input 1 and returns results to the AUX1 data register.                                                                                               |

| 1    | 0    | 0    | 1    | Measures Auxiliary Input 2 and returns results to the AUX2 data register.                                                                                               |

| 1    | 0    | 1    | 0    | Measures temperature (single ended) and returns results to the TEMP1 data register.                                                                                     |

| 1    | 0    | 1    | 1    | Measures Battery Input 1, Battery Input 2, Auxiliary Input 1, Auxiliary Input 2, and temperature (differential), and returns results to the appropriate data registers. |

| 1    | 1    | 0    | 0    | Measures temperature (differential) and returns results to the TEMP1 and TEMP2 data registers.                                                                          |

| 1    | 1    | 0    | 1    | Turns on Y+, Y- drivers. No measurement is performed.                                                                                                                   |