# **USB 2.0 HSIC Hi-Speed 4-Port Hub Controller**

#### PRODUCT FEATURES

**Datasheet**

#### **Highlights**

- Hub Controller IC with 4 downstream ports

- High-Speed Inter-Chip (HSIC) support

- Upstream port selectable between HSIC or USB 2.0

2 downstream HSIC ports

- USB-IF Battery Charger revision 1.2 support on up & downstream ports (DCP, CDP, SDP)

- Battery charging support for Apple<sup>®</sup> devices

- FlexConnect: Downstream port 1 able to swap with upstream port, allowing master capable devices to control other devices on the hub

- USB to I<sup>2</sup>C<sup>TM</sup>/SPI bridge endpoint support

- USB Link Power Management (LPM) support

- SUSPEND pin for remote wakeup indication to host

- Start Of Frame (SOF) synchronized clock output pin

- Vendor Specific Messaging (VSM) support

- Enhanced OEM configuration options available through OTP or SMBus Slave Port

- Flexible power rail support

- VBUS or VBAT only operation

- 3.3V only operation

- VBAT + 1.8V operation

- 3.3V + 1.8V operation

- 48-pin (7x7mm) SQFN, RoHS compliant package

#### **Target Applications**

- LCD monitors and TVs

- Multi-function USB peripherals

- PC mother boards

- Set-top boxes, DVD players, DVR/PVR

- Printers and scanners

- PC media drive bay

- Portable hub boxes

- Mobile PC docking

- Embedded systems

#### **Additional Features**

- MultiTRAK<sup>TM</sup>

- Dedicated Transaction Translator per port

- PortMap

- Configurable port mapping and disable sequencing

- PortSwap

- Configurable differential intra-pair signal swapping

- PHYBoost<sup>TM</sup>

- Programmable USB transceiver drive strength for recovering signal integrity

- VariSense<sup>TM</sup>

- Programmable USB receiver sensitivity

- Low power operation

- Full Power Management with individual or ganged power control of each downstream port

- Built-in Self-Powered or Bus-Powered internal default settings provide flexibility in the quantity of USB expansion ports utilized without redesign

- Supports "Quad Page" configuration OTP flash

Four consecutive 200 byte configuration pages

- Fully integrated USB termination and Pull-up/Pulldown resistors

- On-chip Power On Reset (POR)

- Internal 3.3V and 1.2V voltage regulators

- On Board 24MHz Crystal Driver, Resonator, or External 24MHz clock input

- USB host/device speed indicator. Per-port 3-color LED drivers indicate the speed of USB host and device connection - hi-speed (480 Mbps), full-speed (12 Mbps), low-speed (1.5 Mbps)

- Environmental

- Commercial temperature range support (0°C to 70°C)

- Industrial temperature range support (-40°C to 85°C)

### Order Number(s):

| ORDER NUMBER                                 | TEMPERATURE<br>RANGE         | PACKAGE TYPE                 |  |  |

|----------------------------------------------|------------------------------|------------------------------|--|--|

| USB4624-1080HN (Hub Controller Enabled)      | 0°C to +70°C                 | 48-pin SQFN                  |  |  |

| USB4624-1070HN (Hub Controller Disabled)     | 0 0 10 470 0                 | 40-pili SQFN                 |  |  |

| USB4624-1080HN-TR (Hub Controller Enabled)   | 0°C to +70°C                 | 48-pin SQFN<br>(Tape & Reel) |  |  |

| USB4624-1070HN-TR (Hub Controller Disabled)  | 0 0 10 470 0                 |                              |  |  |

| USB4624i-1080HN (Hub Controller Enabled)     | -40°C to +85°C               | 48-pin SQFN                  |  |  |

| USB4624i-1070HN (Hub Controller Disabled)    | -40 C to +65 C               | 40-pili SQFN                 |  |  |

| USB4624i-1080HN-TR (Hub Controller Enabled)  | 40°C to .95°C                | 48-pin SQFN                  |  |  |

| USB4624i-1070HN-TR (Hub Controller Disabled) | -40 C to +85 C (Tane & Reel) |                              |  |  |

This product meets the halogen maximum concentration values per IEC61249-2-21

The table above represents valid part numbers at the time of printing and may not represent parts that are currently available. For the latest list of valid ordering numbers for this product, please contact the nearest sales office.

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS300000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# **Table of Contents**

| Chapter 1 General Description                                            |    |

|--------------------------------------------------------------------------|----|

| Chapter 2 Acronyms and Definitions                                       | 10 |

| 2.4 Acronyma                                                             | 10 |

| 2.1 Acronyms                                                             |    |

| 2.2 Reference Documents                                                  | 10 |

| Chapter 3 Pin Descriptions                                               | 11 |

| 3.1 Pin Descriptions                                                     |    |

|                                                                          |    |

| 3.2 Pin Assignments                                                      |    |

| 3.3 Buffer Type Descriptions                                             | 20 |

| Chapter 4 Power Connections                                              | 21 |

| 4.1 Integrated Power Regulators                                          |    |

| 4.1.1 3.3V Regulator                                                     |    |

| 4.1.2 1.2V Regulator                                                     |    |

| 4.2 Power Configurations                                                 |    |

| 4.2.1 Single Supply Configurations                                       |    |

| 4.2.2 Dual Supply Configurations                                         |    |

| 4.3 Power Connection Diagrams                                            |    |

| 4.3 Fower Connection Diagrams                                            | 23 |

| Chapter 5 Modes of Operation                                             | 24 |

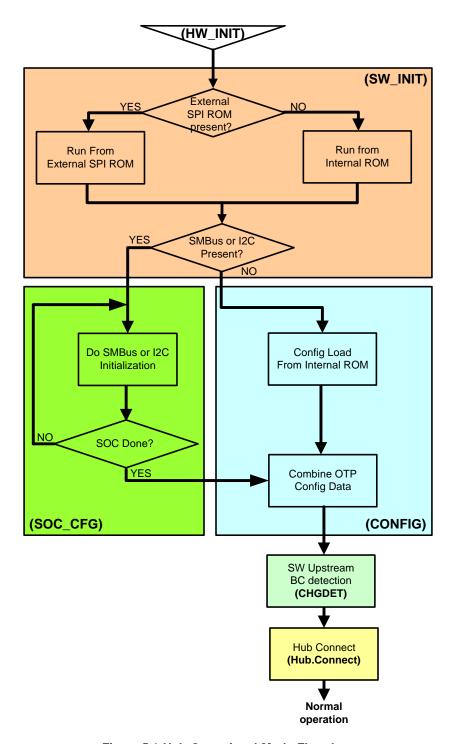

| 5.1 Boot Sequence                                                        | 26 |

| 5.1.1 Standby Mode                                                       |    |

| 5.1.2 Hardware Initialization Stage (HW_INIT)                            |    |

| 5.1.3 Software Initialization Stage (SW_INIT)                            |    |

| 5.1.4 SOC Configuration Stage (SOC_CFG)                                  |    |

| 5.1.5 Configuration Stage (CONFIG)                                       |    |

| 5.1.6 Battery Charger Detection Stage (CHGDET)                           |    |

| 5.1.7 Hub Connect Stage (Hub.Connect)                                    |    |

| 5.1.8 Normal Mode                                                        |    |

|                                                                          |    |

| Chapter 6 Device Configuration                                           |    |

| 6.1 Configuration Method Selection                                       |    |

| 6.2 Customer Accessible Functions                                        |    |

| 6.2.1 USB Accessible Functions                                           |    |

| 6.2.2 SMBus Accessible Functions                                         | 30 |

| 6.3 Device Configuration Straps                                          | 30 |

| 6.3.1 Port Disable (PRT_DIS_Mx/PRT_DIS_Px)                               | 31 |

| 6.3.2 SPI Speed Select (SPI_SPD_SEL)                                     |    |

| Chanton 7 Davies Intenferes                                              | 22 |

| Chapter 7 Device Interfaces                                              |    |

| 7.1 SPI Interface                                                        |    |

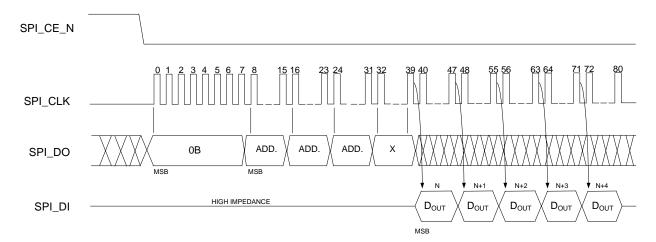

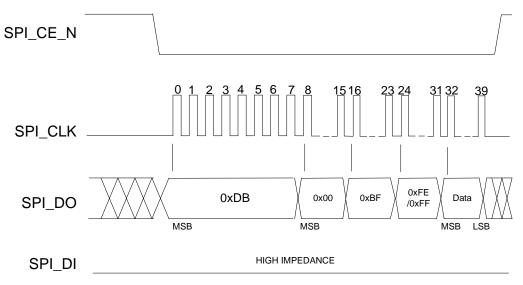

| 7.1.1 Operation of the Hi-Speed Read Sequence                            |    |

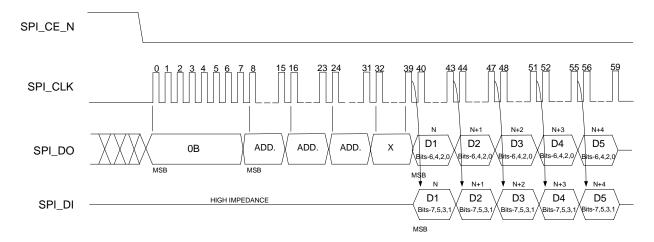

| 7.1.2 Operation of the Dual High Speed Read Sequence                     |    |

| 7.1.3 32 Byte Cache                                                      |    |

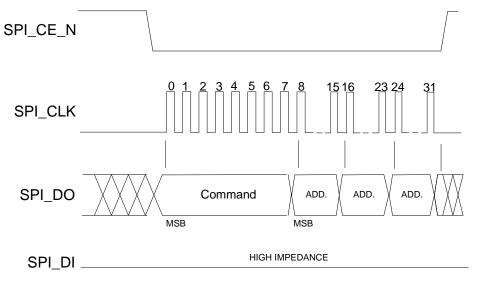

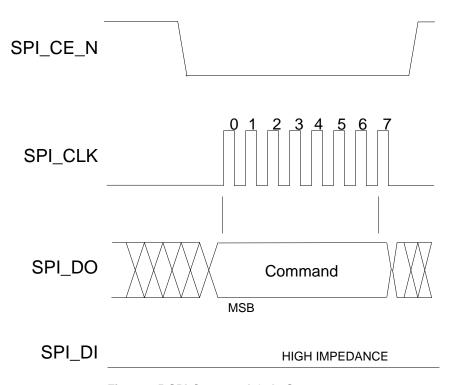

| 7.1.4 Interface Operation to the SPI Port When Not Performing Fast Reads |    |

| 7.1.5 Erase Example                                                      | 34 |

### Datasheet

| Chapter 11 Datasheet Revision History           | 56 |

|-------------------------------------------------|----|

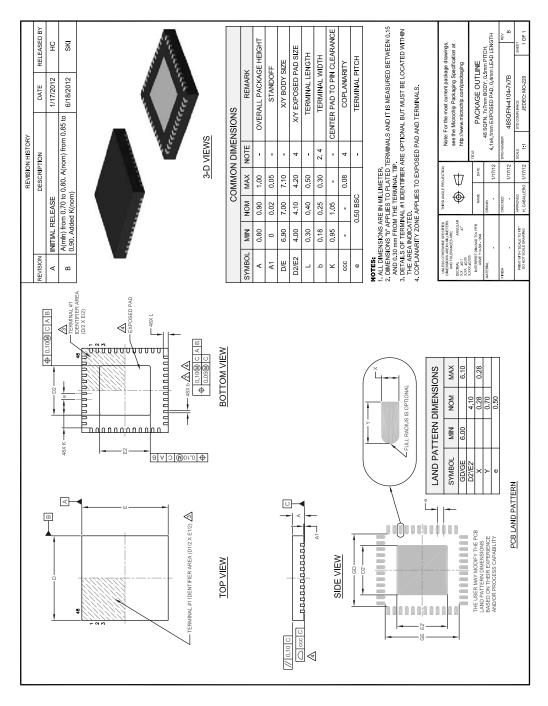

| Chapter 10 Package Outline                      | 55 |

| 9.6.2 External Reference Clock (REFCLK)         | 54 |

| 9.6.1 Oscillator/Crystal                        |    |

| 9.6 Clock Specifications                        |    |

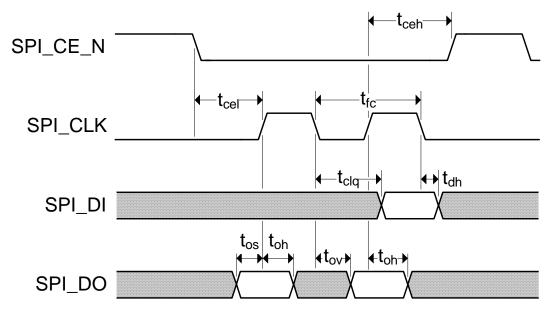

| 9.5.7 SPI Timing                                |    |

| 9.5.6 I2C Timing                                | 51 |

| 9.5.5 SMBus Timing                              |    |

| 9.5.4 HSIC Timing                               |    |

| 9.5.3 USB Timing                                |    |

| 9.5.2 Reset and Configuration Strap Timing      |    |

| 9.5.1 Power-On Configuration Strap Valid Timing |    |

| 9.5 AC Specifications                           |    |

| 9.4 DC Specifications                           |    |

| 9.3.2 Suspend / Standby                         |    |

| 9.3.1 Operational / Unconfigured                |    |

| 9.2 Operating Conditions**                      |    |

| 9.1 Absolute Maximum Ratings*                   |    |

| Chapter 9 Operational Characteristics           |    |

|                                                 |    |

| 8.6 Suspend (SUSPEND)                           |    |

| 8.5 Link Power Management (LPM)                 |    |

| 8.4.3 USB Bus Reset                             |    |

| 8.4.2 External Chip Reset (RESET_N)             |    |

| 8.4.1 Power-On Reset (POR)                      |    |

| 8.4 Resets                                      |    |

| 8.3.1 Port Control                              |    |

| 8.3 Flex Connect                                |    |

| 8.1.2 Downstream Battery Charging               |    |

| 8.1.1 Upstream Battery Charger Detection        |    |

| 8.1 Battery Charger Detection & Charging        |    |

| Chapter 8 Functional Descriptions               |    |

|                                                 | 20 |

| 7.2 SMBus Slave Interface                       | 37 |

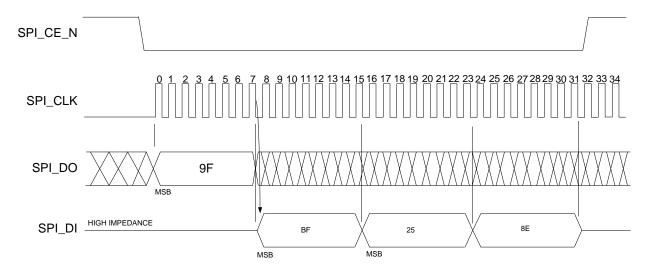

| 7.1.8 JEDEC-ID Read Example                     |    |

| 7.1.7 Command Only Program Example              | 36 |

| 7.1.6 Byte Program Example                      | 35 |

# **List of Figures**

| Figure 1.1  | System Block Diagram                      | . 9 |

|-------------|-------------------------------------------|-----|

| Figure 3.1  | 48-SQFN Pin Assignments                   | 11  |

| Figure 4.1  | Power Connections                         | 23  |

| Figure 5.1  | Hub Operational Mode Flowchart            | 25  |

| Figure 7.1  | SPI Hi-Speed Read Sequence                | 32  |

| Figure 7.2  | SPI Dual Hi-Speed Read Sequence           | 33  |

| Figure 7.3  | SPI Erase Sequence                        | 34  |

| Figure 7.4  | SPI Byte Program Sequence                 | 35  |

| Figure 7.5  | SPI Command Only Sequence                 | 36  |

| Figure 7.6  | SPI JEDEC-ID Read Sequence                | 37  |

| Figure 8.1  | Battery Charging External Power Supply    | 39  |

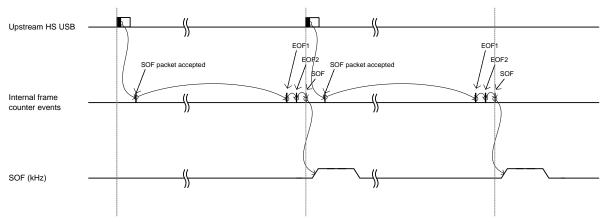

| Figure 8.2  | SOF Output Timing                         | 41  |

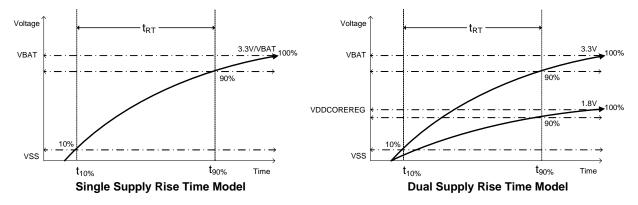

| Figure 9.1  | Single/Dual Supply Rise Time Models       | 45  |

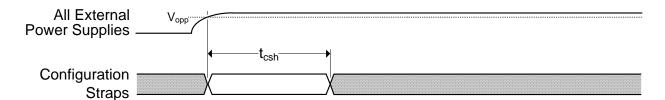

| Figure 9.1  | Power-On Configuration Strap Valid Timing | 50  |

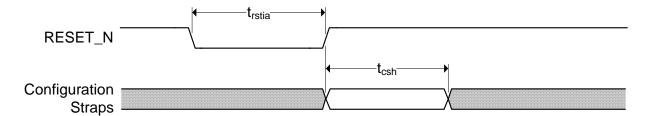

| Figure 9.2  | RESET_N Configuration Strap Timing        | 51  |

| Figure 9.3  | SPI Timing                                | 52  |

| Figure 10.1 | 48-SQFN Package Drawing                   | 55  |

# **List of Tables**

| Table 3.1  | Pin Descriptions                                                | 12 |

|------------|-----------------------------------------------------------------|----|

| Table 3.2  | 48-SQFN Package Pin Assignments                                 | 19 |

| Table 3.3  | Buffer Types                                                    | 20 |

| Table 6.1  | PRT_DIS_Mx/PRT_DIS_Px Configuration Definitions                 | 31 |

| Table 6.2  | SPI_SPD_SEL Configuration Definitions                           | 31 |

| Table 8.1  | Chargers Compatible with Upstream Detection                     | 38 |

| Table 8.2  | Downstream Port Types                                           | 40 |

|            | LPM State Definitions                                           |    |

| Table 9.1  | Operational/Unconfigured Power Consumption (HSIC Upstream)      | 46 |

| Table 9.2  | Operational/Unconfigured Power Consumption (USB Upstream)       | 46 |

| Table 9.3  | Single Supply Suspend/Standby Power Consumption (USB Upstream)  | 47 |

| Table 9.4  | Single Supply Suspend/Standby Power Consumption (HSIC Upstream) | 47 |

| Table 9.5  | Dual Supply Suspend/Standby Power Consumption (USB Upstream)    | 48 |

| Table 9.6  | Dual Supply Suspend/Standby Power Consumption (USB Upstream)    | 48 |

| Table 9.7  | DC Electrical Characteristics                                   | 49 |

| Table 9.8  | Power-On Configuration Strap Valid Timing                       | 50 |

|            | RESET_N Configuration Strap Timing                              |    |

| Table 9.10 | SPI Timing Values (30 MHz Operation)                            | 52 |

| Table 9.11 | SPI Timing Values (60 MHz Operation)                            | 53 |

|            | ? Crystal Specifications                                        |    |

| Table 11.1 | Revision History                                                | 56 |

# **Chapter 1 General Description**

The USB4624 is a low-power, OEM configurable, MTT (Multi-Transaction Translator) USB 2.0 hub controller with 4 downstream ports and advanced features for embedded USB applications. The USB4624 is fully compliant with the USB 2.0 Specification, USB 2.0 Link Power Management Addendum, High-Speed Inter-Chip (HSIC) USB Electrical Specification Revision 1.0, and will attach to an upstream port as a Full-Speed hub or as a Full-/Hi-Speed hub. The 4-port hub supports Low-Speed, Full-Speed, and Hi-Speed (if operating as a Hi-Speed hub) downstream devices on all of the enabled downstream (non-HSIC) ports. HSIC ports support only Hi-Speed operation.

The USB4624 has been specifically optimized for embedded systems where high performance, and minimal BOM costs are critical design requirements. Standby mode power has been minimized and reference clock inputs can be aligned to the customer's specific application. Flexible power rail options ease integration into energy efficient designs by allowing the USB4624 to be powered in a single-source (VBUS, VBAT, 3.3V) or a dual-source (VBAT + 1.8, 3.3V + 1.8) configuration. Additionally, all required resistors on the USB ports are integrated into the hub, including all series termination and pull-up/pull-down resistors on the D+ and D- pins.

The USB4624 supports both upstream battery charger detection and downstream battery charging. The USB4624 integrated battery charger detection circuitry supports the USB-IF Battery Charging (BC1.2) detection method and most Apple devices. These circuits are used to detect the attachment and type of a USB charger and provide an interrupt output to indicate charger information is available to be read from the device's status registers via the serial interface. The USB4624 provides the battery charging handshake and supports the following USB-IF BC1.2 charging profiles:

- DCP: Dedicated Charging Port (Power brick with no data)

- CDP: Charging Downstream Port (1.5A with data)

- SDP: Standard Downstream Port (0.5A with data)

- Custom profiles loaded via SMBus or OTP

The USB4624 provides an additional USB endpoint dedicated for use as a USB to I<sup>2</sup>C/SPI interface, allowing external circuits or devices to be monitored, controlled, or configured via the USB interface. Additionally, the USB4624 includes many powerful and unique features such as:

**FlexConnect**, which provides flexible connectivity options. The USB4624's downstream port 1 can be swapped with the upstream port, allowing master capable devices to control other devices on the hub.

**MultiTRAK**<sup>TM</sup> **Technology**, which utilizes a dedicated Transaction Translator (TT) per port to maintain consistent full-speed data throughput regardless of the number of active downstream connections. MultiTRAK<sup>TM</sup> outperforms conventional USB 2.0 hubs with a single TT in USB full-speed data transfers.

**PortMap**, which provides flexible port mapping and disable sequences. The downstream ports of a USB4624 hub can be reordered or disabled in any sequence to support multiple platform designs with minimum effort. For any port that is disabled, the USB4624 hub controllers automatically reorder the remaining ports to match the USB host controller's port numbering scheme.

**PortSwap**, which adds per-port programmability to USB differential-pair pin locations. PortSwap allows direct alignment of USB signals (D+/D-) to connectors to avoid uneven trace length or crossing of the USB differential signals on the PCB.

**PHYBoost**, which provides programmable levels of Hi-Speed USB signal drive strength in the downstream port transceivers. PHYBoost attempts to restore USB signal integrity in a compromised system environment. The graphic on the right shows an example of Hi-Speed USB eye diagrams before and after PHYBoost signal integrity restoration.

**VariSense**, which controls the USB receiver sensitivity enabling programmable levels of USB signal receive sensitivity. This capability allows operation in a sub-optimal system environment, such as when a captive USB cable is used.

#### Datasheet

The USB4624 is available in commercial (0°C to +70°C) and industrial (-40°C to +85°C) temperature range versions.

As shown in the ordering code matrix, two USB4624 firmware revisions are available: "-1080" and "-1070". The -1080 version enables the internal Hub Controller, while the -1070 version disables it. There are no additional differences between these two versions.

The Hub Controller adds advanced functionality to the USB4624 by enabling the host to send commands directly to it via the upstream USB connection. Commands to the Hub Controller must be sent to the virtual 5th port in the hub. The following functions can be controlled via commands through the Hub Controller:

- USB to SMBus Bridging: The host can send commands through USB to any device connected to the hub through the SMBus.

- USB to UART Bridging: The host can send commands through SUB to any device connected to the hub through the UART.

- GPIO Control: The GPIOs on the hub can be dynamically configured and controlled by the host.

- OTP Programming: Permanent customer configurations can be loaded to the One Time Programmable memory.

# 1.1 Block Diagram

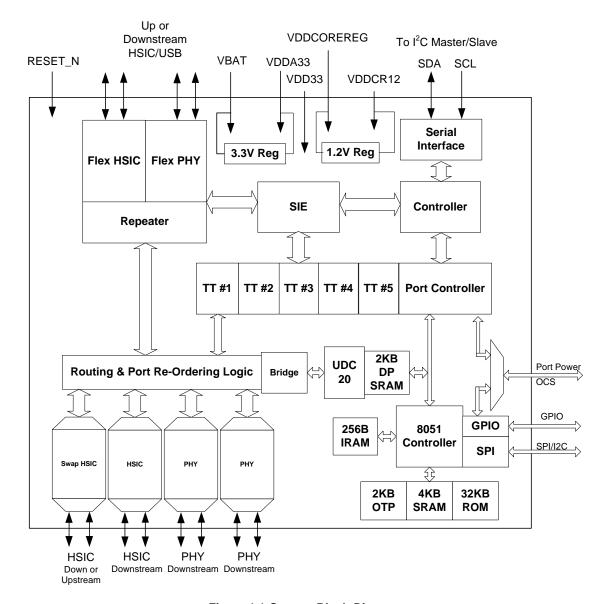

Figure 1.1 details the internal block diagram of the USB4624.

Figure 1.1 System Block Diagram

# **Chapter 2 Acronyms and Definitions**

## 2.1 Acronyms

EOP: End of Packet

**EP:** Endpoint

FS: Full-Speed

GPIO: General Purpose I/O (that is input/output to/from the device)

HS: Hi-Speed

**HSOS:** High Speed Over Sampling

HSIC: High-Speed Inter-Chip

I<sup>2</sup>C<sup>®</sup>: Inter-Integrated Circuit

LS: Low-Speed

**OTP:** One Time Programmable

PCB: Printed Circuit Board

PCS: Physical Coding Sublayer

PHY: Physical Layer

SMBus: System Management Bus

**UUID:** Universally Unique IDentification

### 2.2 Reference Documents

- 1. UNICODE UTF-16LE For String Descriptors USB Engineering Change Notice, December 29th, 2004, http://www.usb.org

- 2. Universal Serial Bus Specification, Revision 2.0, April 27th, 2000, http://www.usb.org

- 3. Battery Charging Specification, Revision 1.2, Dec. 07, 2010, http://www.usb.org

- 4. High-Speed Inter-Chip USB Electrical Specification, Version 1.0, Sept. 23, 2007, http://www.usb.org

- 5. *l*<sup>2</sup>*C-Bus Specification*, Version 1.1, http://www.nxp.com

- 6. System Management Bus Specification, Version 1.0, http://smbus.org/specs

# **Chapter 3 Pin Descriptions**

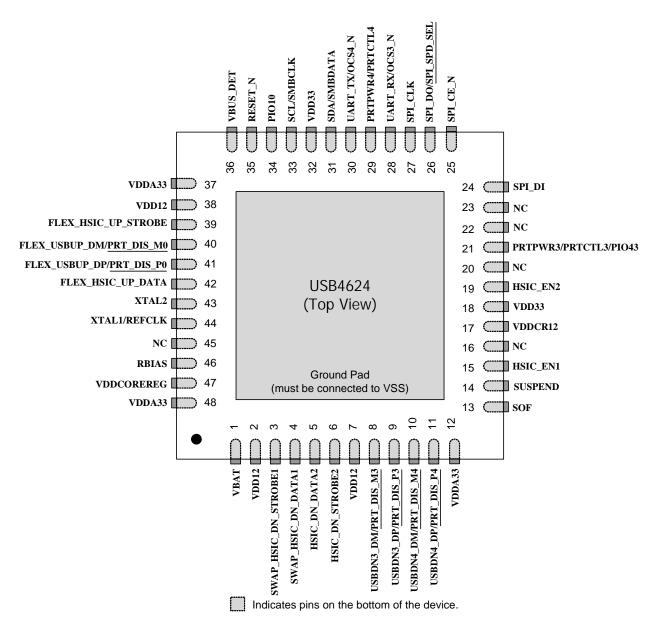

Figure 3.1 48-SQFN Pin Assignments

# 3.1 Pin Descriptions

This section provides a detailed description of each pin. The signals are arranged in functional groups according to their associated interface.

The "\_N" symbol in the signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. For example, RESET\_N indicates that the reset signal is active low. When "\_N" is not present after the signal name, the signal is asserted when at the high voltage level.

The terms assertion and negation are used exclusively. This is done to avoid confusion when working with a mixture of "active low" and "active high" signals. The term assert, or assertion, indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term negate, or negation, indicates that a signal is inactive.

**Note:** The buffer type for each signal is indicated in the BUFFER TYPE column of Table 3.1. A description of the buffer types is provided in Section 3.3.

**Table 3.1 Pin Descriptions**

| NUM PINS | NAME                                           | SYMBOL        | BUFFER<br>TYPE | DESCRIPTION                                                                                         |  |  |  |

|----------|------------------------------------------------|---------------|----------------|-----------------------------------------------------------------------------------------------------|--|--|--|

|          | USB/HSIC INTERFACES                            |               |                |                                                                                                     |  |  |  |

|          | Upstream                                       | FLEX USBUP DP | AIO            | Upstream USB Port 0 D+ data signal.                                                                 |  |  |  |

|          | USB D+                                         | . 11/200005.  | 7 110          | See Note 3.2.                                                                                       |  |  |  |

|          | (Flex Port 0)                                  |               |                | Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.     |  |  |  |

| 1        | Port 0 D+<br>Disable                           | PRT DIS PO    | IS             | This strap is used in conjunction with PRT DIS M0 to disable USB Port 0.                            |  |  |  |

|          | Configuration<br>Strap                         |               |                | 0 = Port 0 D+ Enabled<br>1 = Port 0 D+ Disabled                                                     |  |  |  |

|          |                                                |               |                | Note: Both PRT DIS P0 and PRT DIS M0 must be tied to VDD33 at reset to place Port 0 into HSIC mode. |  |  |  |

|          |                                                |               |                | See Note 3.3 for more information on configuration straps.                                          |  |  |  |

|          | Upstream<br>USB D-                             | FLEX_USBUP_DM | AIO            | Upstream USB Port 0 D- data signal.<br>See Note 3.2.                                                |  |  |  |

|          | (Flex Port 0)                                  |               |                | Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.     |  |  |  |

| 1        | Port 0 D-<br>Disable<br>Configuration<br>Strap | PRT DIS MO    | IS             | This strap is used in conjunction with PRT DIS P0 to disable USB Port 0.                            |  |  |  |

| ·        |                                                |               |                | 0 = Port 0 D- Enabled<br>1 = Port 0 D- Disabled                                                     |  |  |  |

|          |                                                |               |                | Note: Both PRT DIS P0 and PRT DIS M0 must be tied to VDD33 at reset to place Port 0 into HSIC mode. |  |  |  |

|          |                                                |               |                | See Note 3.3 for more information on configuration straps.                                          |  |  |  |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS | NAME                                           | SYMBOL                   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|----------|------------------------------------------------|--------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Upstream<br>HSIC Data<br>(Flex Port 0)         | FLEX_HSIC_UP_<br>DATA    | HSIC           | Upstream HSIC Port 0 DATA signal. See Note 3.2.  Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.                                                                                                                                        |

| 1        | Upstream<br>HSIC Strobe<br>(Flex Port 0)       | FLEX_HSIC_UP_<br>STROBE  | HSIC           | Upstream HSIC Port 0 STROBE signal. See Note 3.2.  Note: The upstream Port 0 signals can be optionally swapped with the downstream Port 1 signals.                                                                                                                                      |

| 1        | Downstream<br>HSIC Data<br>(Swap Port 1)       | SWAP_HSIC_DN_<br>DATA1   | HSIC           | Downstream HSIC Port 1 DATA signal.  Note: The downstream Port 1 signals can be optionally swapped with the upstream Port 0 signals.                                                                                                                                                    |

| 1        | Downstream<br>HSIC Strobe<br>(Swap Port 1)     | SWAP_HSIC_DN_<br>STROBE1 | HSIC           | Note: The downstream Port 1 signals can be optionally swapped with the upstream Port 0 signals.                                                                                                                                                                                         |

| 1        | Downstream<br>HSIC Data<br>(Port 2)            | HSIC_DN_DATA2            | HSIC           | Downstream HSIC Port 2 DATA signal.                                                                                                                                                                                                                                                     |

| 1        | Downstream<br>HSIC Strobe<br>(Port 2)          | HSIC_DN_STROBE2          | HSIC           | Downstream HSIC Port 2 STROBE signal.                                                                                                                                                                                                                                                   |

|          | Downstream<br>USB D+<br>(Port 3)               | USBDN3_DP                | AIO            | Downstream USB Port 3 D+ data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 3 D+<br>Disable<br>Configuration<br>Strap | PRT DIS P3               | IS             | This strap is used in conjunction with PRT DIS M3 to disable USB Port 3.  0 = Port 3 D+ Enabled 1 = Port 3 D+ Disabled  Note: Both PRT DIS P3 and PRT DIS M3 must be tied to VDD33 at reset to disable the associated port.  See Note 3.3 for more information on configuration straps. |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS | NAME                                           | SYMBOL              | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                             |

|----------|------------------------------------------------|---------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Downstream<br>USB D-<br>(Port 3)               | USBDN3_DM           | AIO            | Downstream USB Port 3 D- data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 3 D-<br>Disable<br>Configuration<br>Strap | PRT DIS M3          | IS             | This strap is used in conjunction with PRT DIS P3 to disable USB Port 3.  0 = Port 3 D- Enabled 1 = Port 3 D- Disabled  Note: Both PRT DIS P3 and PRT DIS M3                                                                                                                            |

|          |                                                |                     |                | must be tied to VDD33 at reset to disable the associated port.  See Note 3.3 for more information on configuration straps.                                                                                                                                                              |

|          | Downstream<br>USB D+<br>(Port 4)               | USBDN4_DP           | AIO            | Downstream USB Port 4 D+ data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 4 D+<br>Disable<br>Configuration<br>Strap | PRT DIS P4          | IS             | This strap is used in conjunction with PRT DIS M4 to disable USB Port 4.  0 = Port 4 D+ Enabled 1 = Port 4 D+ Disabled  Note: Both PRT DIS P4 and PRT DIS M4 must be tied to VDD33 at reset to disable the associated port.  See Note 3.3 for more information on configuration straps. |

|          | Downstream<br>USB D-<br>(Port 4)               | USBDN4_DM           | AIO            | Downstream USB Port 4 D- data signal.                                                                                                                                                                                                                                                   |

| 1        | Port 4 D-<br>Disable<br>Configuration<br>Strap | PRT DIS M4          | IS             | This strap is used in conjunction with PRT DIS P4 to disable USB Port 4.  0 = Port 4 D- Enabled 1 = Port 4 D- Disabled  Note: Both PRT DIS P4 and PRT DIS M4 must be tied to VDD33 at reset to disable the associated port.  See Note 3.3 for more information on configuration straps. |

|          |                                                | I <sup>2</sup> C/SI | MBUS INTER     | RFACE                                                                                                                                                                                                                                                                                   |

| 1        | I <sup>2</sup> C Serial<br>Clock Input         | SCL                 | I_SMB          | I <sup>2</sup> C serial clock input                                                                                                                                                                                                                                                     |

|          | SMBus Clock                                    | SMBCLK              | I_SMB          | SMBus serial clock input                                                                                                                                                                                                                                                                |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS | NAME                                   | SYMBOL      | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                |

|----------|----------------------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | I <sup>2</sup> C Serial                |             |                | I <sup>2</sup> C bidirectional serial data                                                                                                                                                 |

|          | Data                                   | SDA         | IS/OD8         | I-C bidirectional serial data                                                                                                                                                              |

| 1        | SMBus Serial<br>Data                   | SMBDATA     | IS/OD8         | SMBus bidirectional serial data                                                                                                                                                            |

|          | <u> </u>                               | SPI M       | ASTER INTE     | RFACE                                                                                                                                                                                      |

|          | SPI Chip                               | SPI_CE_N    | O12            | Active-low SPI chip enable output.                                                                                                                                                         |

| 1        | Enable<br>Output                       |             |                | Note: If the SPI is enabled, this pin will be driven high in powerdown states.                                                                                                             |

| 1        | SPI Clock<br>Output                    | SPI_CLK     | O12            | SPI clock output                                                                                                                                                                           |

|          | SPI Data<br>Output                     | SPI_DO      | O12            | SPI data output                                                                                                                                                                            |

|          | SPI Speed                              | SPI SPD SEL | IS<br>(BB)     | This strap is used to select the speed of the SPI.                                                                                                                                         |

|          | Select<br>Configuration<br>Strap       |             | (PD)           | 0 = 30MHz (default)<br>1 = 60MHz                                                                                                                                                           |

| 1        | Chap                                   |             |                | Note: If the latched value on reset is 1, this pin is tri-stated when the chip is in the suspend state. If the latched value on reset is 0, this pin is driven low during a suspend state. |

|          |                                        |             |                | See Note 3.3 for more information on configuration straps.                                                                                                                                 |

| 1        | SPI Data<br>Input                      | SPI_DI      | IS<br>(PD)     | SPI data input                                                                                                                                                                             |

|          | <u> </u>                               |             | MISC.          |                                                                                                                                                                                            |

|          | UART                                   | UART_RX     | IS             | Internal UART receive input                                                                                                                                                                |

| 1        | Receive Input                          |             |                | Note: This is a 3.3V signal. For RS232 operation, an external 12V translator is required.                                                                                                  |

|          | Port 3 Over-<br>Current<br>Sense Input | OCS3_N      | IS<br>(PU)     | This active-low signal is input from an external current monitor to indicate an over-current condition on USB Port 3.                                                                      |

|          | _UART_                                 | UART_TX     | O8             | Internal UART transmit output                                                                                                                                                              |

| 1        | Transmit<br>Output                     |             |                | Note: This is a 3.3V signal. For RS232 operation, an external 12V driver is required.                                                                                                      |

|          | Port 4 Over-<br>Current<br>Sense Input | OCS4_N      | IS<br>(PU)     | This active-low signal is input from an external current monitor to indicate an over-current condition on USB Port 4.                                                                      |

**Table 3.1 Pin Descriptions (continued)**

|          |                                              | 0.445-5- | BUFFER |                                                                                                                                                                                                                                                                       |

|----------|----------------------------------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                                         | SYMBOL   | TYPE   | DESCRIPTION                                                                                                                                                                                                                                                           |

|          | System Reset<br>Input                        | RESET_N  | I_RST  | This active-low signal allows external hardware to reset the device.                                                                                                                                                                                                  |

| 1        |                                              |          |        | Note: The active-low pulse must be at least 5us wide. Refer to Section 8.4.2, "External Chip Reset (RESET_N)," on page 42 for additional information.                                                                                                                 |

|          | Crystal Input                                | XTAL1    | ICLK   | External 24 MHz crystal input                                                                                                                                                                                                                                         |

| 1        | Reference<br>Clock Input                     | REFCLK   | ICLK   | Reference clock input. The device may be alternatively driven by a single-ended clock oscillator. When this method is used, XTAL2 should be left unconnected.                                                                                                         |

| 1        | Crystal<br>Output                            | XTAL2    | OCLK   | External 24 MHz crystal output                                                                                                                                                                                                                                        |

| 1        | External USB<br>Transceiver<br>Bias Resistor | RBIAS    | Al     | A 12.0k $\Omega$ (+/- 1%) resistor is attached from ground to this pin to set the transceiver's internal bias settings.                                                                                                                                               |

| 1        | Suspend<br>Output                            | SUSPEND  | PU     | This signal is used to indicate that the entire hub has entered the USB suspend state and that VBUS current consumption should be reduced in accordance with the USB specification. Refer to Section 8.6, "Suspend (SUSPEND)," on page 43 for additional information. |

|          |                                              |          |        | Note: SUSPEND must be enabled via the Protouch configuration tool.                                                                                                                                                                                                    |

|          | SOF<br>Synchronized                          | SOF      | O8     | This signal outputs an 8KHz clock synchronized with the USB Host SOF.                                                                                                                                                                                                 |

| 1        | 8KHz Clock<br>Output                         |          |        | Note: SOF output is controlled via the SOF_ENABLE bit in the UTIL_CONFIG1 register                                                                                                                                                                                    |

|          | Detect                                       | VBUS_DET | IS     | Detects state of upstream bus power.                                                                                                                                                                                                                                  |

|          | Upstream<br>VBUS Power                       |          |        | When designing a detachable hub, this pin must be connected to the VBUS power pin of the upstream USB port through a resistor divider (50k $\Omega$ by 100k $\Omega$ ) to provide 3.3V.                                                                               |

| 1        |                                              |          |        | For self-powered applications with a permanently attached host, this pin must be connected to either 3.3V or 5.0V through a resistor divider to provide 3.3V.                                                                                                         |

|          |                                              |          |        | In embedded applications, VBUS_DET may be controlled (toggled) when the host desires to renegotiate a connection without requiring a full reset of the device.                                                                                                        |

**Table 3.1 Pin Descriptions (continued)**

|          |                                  |          | 1              | <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|----------------------------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NUM PINS | NAME                             | SYMBOL   | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          | Port 1 HSIC<br>Enable            | HSIC_EN1 | O8/<br>OD8     | Used to indicate the connection state to the downstream HSIC device attached to Port 1.                                                                                                                                                                                                                                                                                                                                                            |

| 1        |                                  |          |                | 0 = Disconnect Port 1 HSIC<br>1 = Device ready to negotiate or sustain an HSIC<br>connection on Port 1.                                                                                                                                                                                                                                                                                                                                            |

|          | Port 2 HSIC<br>Enable            | HSIC_EN2 | O8/<br>OD8     | Used to indicate the connection state to the downstream HSIC device attached to Port 2.                                                                                                                                                                                                                                                                                                                                                            |

| 1        |                                  |          |                | 0 = Disconnect Port 2 HSIC<br>1 = Device ready to negotiate or sustain an HSIC<br>connection on Port 2.                                                                                                                                                                                                                                                                                                                                            |

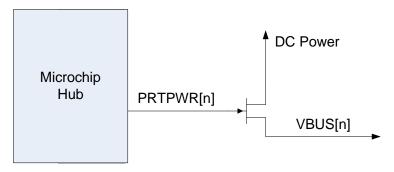

|          | Port 3 Power<br>Output           | PRTPWR3  | O8             | Enables power to a downstream USB device attached to Port 3.                                                                                                                                                                                                                                                                                                                                                                                       |

| 1        |                                  |          |                | 0 = Power disabled on downstream Port 3<br>1 = Power enabled on downstream Port 3                                                                                                                                                                                                                                                                                                                                                                  |

| ·        | Port 3 Control                   | PRTCTL3  | OD8/IS<br>(PU) | When configured as PRTCTL3, this pin functions as both the Port 3 power enable output (PRTPWR3) and the Port 3 over-current sense input (OCS3_N). Refer to the PRTPWR3 and OCS3_N descriptions for additional information.                                                                                                                                                                                                                         |

|          | Port 4 Power<br>Output           | PRTPWR4  | O8             | Enables power to a downstream USB device attached to Port 4.                                                                                                                                                                                                                                                                                                                                                                                       |

| 1        |                                  |          |                | 0 = Power disabled on downstream Port 4<br>1 = Power enabled on downstream Port 4                                                                                                                                                                                                                                                                                                                                                                  |

| 1        | Port 4 Control                   | PRTCTL4  | OD8/IS<br>(PU) | When configured as PRTCTL4, this pin functions as both the Port 4 power enable output (PRTPWR4) and the Port 4 over-current sense input (OCS4_N). Refer to the PRTPWR4 and OCS4_N descriptions for additional information.                                                                                                                                                                                                                         |

| 5        | No Connect                       | NC       | -              | This pin must be left floating for normal device operation.                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                                  |          | POWER          |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1        | Battery<br>Power Supply<br>Input | VBAT     | Р              | Battery power supply input. When VBAT is connected directly to a +3.3V supply from the system, the internal +3.3V regulator runs in dropout and regulator power consumption is eliminated. A 4.7 $\mu\text{F}$ (<1 $\Omega$ ESR) capacitor to ground is required for regulator stability. The capacitor should be placed as close as possible to the device. Refer to Chapter 4, "Power Connections," on page 21 for power connection information. |

| 3        | +3.3V Analog<br>Power Supply     | VDDA33   | Р              | +3.3V analog power supply. A 1.0 $\mu$ F (<1 $\Omega$ ESR) capacitor to ground is required for regulator stability. The capacitor should be placed as close as possible to the device. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                                                                       |

**Table 3.1 Pin Descriptions (continued)**

| NUM PINS                                               | NAME                                    | SYMBOL     | BUFFER<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------------------------|-----------------------------------------|------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                      | +3.3V Power<br>Supply                   | VDD33      | Р              | +3.3V power supply. These pins must be connected to VDDA33. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1                                                      | +1.8-3.3V<br>Core Power<br>Supply Input | VDDCOREREG | Р              | +1.8-3.3V core power supply input to internal +1.2V regulator. This pin may be connected to VDD33 for single supply applications when VBAT equals +3.3V. Running in a dual supply configuration with VDDCOREREG at a lower voltage, such as +1.8V, may reduce overall system power consumption. In dual supply configurations, a 4.7 $\mu F$ (<1 $\Omega$ ESR) capacitor to ground is required for regulator stability. The capacitor should be placed as close as possible to the device. Refer to Chapter 4, "Power Connections," on page 21 for power connection information. |

| 1                                                      | +1.2V Core<br>Power Supply              | VDDCR12    | Р              | +1.2V core power supply. In single supply applications or dual supply applications where 1.2V is not used, a 1.0 $\mu\text{F}$ (<1 $\Omega$ ESR) capacitor to ground is required for regulator stability. The capacitor should be placed as close as possible to the device. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                                                                                                               |

| 3                                                      | +1.2V HSIC<br>Power Supply<br>Input     | VDD12      | Р              | +1.2V HSIC power supply input. Refer to Chapter 4, "Power Connections," on page 21 for power connection information.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Exposed<br>Pad on<br>package<br>bottom<br>(Figure 3.1) | Ground                                  | VSS        | Р              | Common ground. This exposed pad must be connected to the ground plane with a via array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

- Note 3.2 When the device is configured to enable the HSIC upstream port, the USB Product ID (PID) will be 4624. When the device is configured to enable the USB upstream port, the USB PID will be 4524.

- Note 3.3 Configuration strap values are latched on Power-On Reset (POR) and the rising edge of RESET\_N (external chip reset). Configuration straps are identified by an underlined symbol name. Signals that function as configuration straps must be augmented with an external resistor when connected to a load. Refer to Section 6.3, "Device Configuration Straps," on page 30 for additional information.

# 3.2 Pin Assignments

Table 3.2 48-SQFN Package Pin Assignments

| PIN NUM | PIN NAME                           | PIN NUM              | PIN NAME                         |

|---------|------------------------------------|----------------------|----------------------------------|

| 1       | VBAT                               | 25                   | SPI_CE_N                         |

| 2       | VDD12                              | 26                   | SPI_DO/ <u>SPI_SPD_SEL</u>       |

| 3       | HSIC_DN_STROBE1                    | 27                   | SPI_CLK                          |

| 4       | HSIC_DN_DATA1                      | 28                   | UART_RX/OCS3_N                   |

| 5       | HSIC_DN_DATA2                      | 29                   | PRTPWR4/PRTCTL4                  |

| 6       | HSIC_DN_STROBE2                    | 30                   | UART_TX/OCS4_N                   |

| 7       | VDD12                              | VDD12 31 SDA/SMBDATA |                                  |

| 8       | USBDN3_DM/ <u>PRT_DIS_M3</u>       | 32                   | VDD33                            |

| 9       | USBDN3_DP/PRT_DIS_P3               | 33                   | SCL/SMBCLK                       |

| 10      | USBDN4_DM/ <u>PRT_DIS_M4</u>       | 34                   | NC                               |

| 11      | USBDN4_DP/ <u>PRT_DIS_P4</u>       | 35                   | RESET_N                          |

| 12      | VDDA33                             | 36                   | VBUS_DET                         |

| 13      | SOF                                | 37                   | VDDA33                           |

| 14      | SUSPEND                            | 38                   | VDD12                            |

| 15      | HSIC_EN1                           | 39                   | FLEX_HSIC_UP_STROBE              |

| 16      | NC                                 | 40                   | FLEX_USBUP_DM/PRT_DIS_M0         |

| 17      | VDDCR12 41 FLEX_USBUP_DP/PRT_DIS_P |                      | FLEX_USBUP_DP/ <u>PRT_DIS_P0</u> |

| 18      | VDD33 42                           |                      | FLEX_HSIC_UP_DATA                |

| 19      | HSIC_EN2 43 XTAL2                  |                      | XTAL2                            |

| 20      | NC                                 | NC 44 XTAL1/REFCLK   |                                  |

| 21      | PRTPWR3/PRTCTL3 45 NC              |                      | NC                               |

| 22      | NC 46 RBIAS                        |                      | RBIAS                            |

| 23      | NC                                 | 47                   | VDDCOREREG                       |

| 24      | SPI_DI                             | 48                   | VDDA33                           |

# 3.3 Buffer Type Descriptions

**Table 3.3 Buffer Types**

| BUFFER TYPE | DESCRIPTION                                                                                                                                                                                                                                         |  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| IS          | Schmitt-triggered input                                                                                                                                                                                                                             |  |

| I_RST       | Reset Input                                                                                                                                                                                                                                         |  |

| I_SMB       | I <sup>2</sup> C/SMBus Clock Input                                                                                                                                                                                                                  |  |

| O8          | Output with 8 mA sink and 8 mA source                                                                                                                                                                                                               |  |

| OD8         | Open-drain output with 8 mA sink                                                                                                                                                                                                                    |  |

| O12         | Output with 12 mA sink and 12 mA source                                                                                                                                                                                                             |  |

| OD12        | Open-drain output with 12 mA sink                                                                                                                                                                                                                   |  |

| HSIC        | High-Speed Inter-Chip (HSIC) USB Specification, Version 1.0 compliant input/output                                                                                                                                                                  |  |

| PU          | 50 μA (typical) internal pull-up. Unless otherwise noted in the pin description, internal pull-ups are always enabled.                                                                                                                              |  |

|             | <b>Note:</b> Internal pull-up resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled high, an external resistor must be added. |  |

| PD          | 50 μA (typical) internal pull-down. Unless otherwise noted in the pin description, internal pull-downs are always enabled.                                                                                                                          |  |

|             | Note: Internal pull-down resistors prevent unconnected inputs from floating. Do not rely on internal resistors to drive signals external to the device. When connected to a load that must be pulled low, an external resistor must be added.       |  |

| AIO         | Analog bi-directional                                                                                                                                                                                                                               |  |

| ICLK        | Crystal oscillator input pin                                                                                                                                                                                                                        |  |

| OCLK        | Crystal oscillator output pin                                                                                                                                                                                                                       |  |

| Р           | Power pin                                                                                                                                                                                                                                           |  |

# **Chapter 4 Power Connections**

# 4.1 Integrated Power Regulators

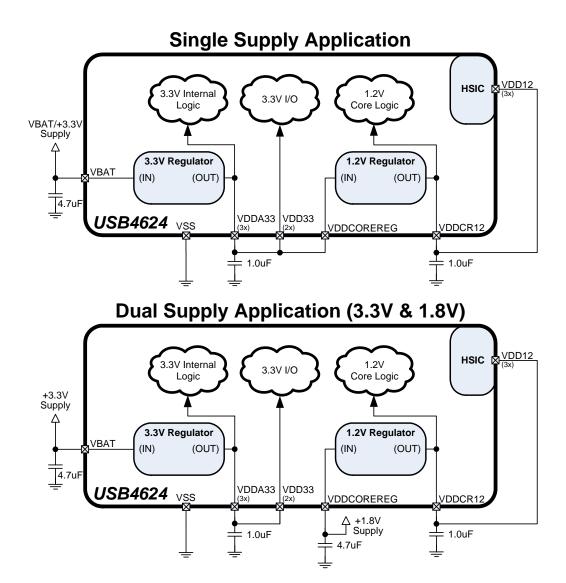

The integrated 3.3V and 1.2V power regulators provide flexibility to the system in providing power the device. Several different configurations are allowed in order to align the power structure to supplies available in the system.

The regulators are controlled by RESET\_N. When RESET\_N is brought high, the 3.3V regulator will turn on. When RESET\_N is brought low the 3.3V regulator will turn off.

# 4.1.1 3.3V Regulator

The device has an integrated regulator to convert from VBAT to 3.3V.

## **4.1.2 1.2V Regulator**

The device has an integrated regulator to convert from a variable voltage input on VDDCOREREG to 1.2V. The 1.2V regulator is tolerant to the presence of low voltage (~0V) on the VDDCOREREG pin in order to support system power solutions where a supply is not always present in low power states.

The 1.2V regulator supports an input voltage range consistent with a 1.8V input in order to reduce power consumption in systems which provide multiple power supply levels. In addition, the 1.2V regulator supports an input voltage up to 3.3V for systems which provide only a single power supply. The device will support operation where the 3.3V regulator output can drive the 1.2V regulator input such that VBAT is the only required supply.

# 4.2 Power Configurations

The device supports operation with no back current when power is connected in each of the following configurations. Power connection diagrams for these configurations are included in Section 4.3, "Power Connection Diagrams," on page 23.

# 4.2.1 Single Supply Configurations

### 4.2.1.1 **VBAT Only**

VBAT must be tied to the VBAT system supply. VDD33, VDDA33, and VDDCOREREG must be tied together on the board. In this configuration the 3.3V and 1.2V regulators will be active. For HSIC operation, VDD12 must be tied to VDDCR12.

### 4.2.1.2 3.3V Only

VBAT must be tied to the 3.3V system supply. VDD33, VDDA33, and VDDCOREREG must be tied together on the board. In this configuration the 3.3V regulator will operate in dropout mode and the 1.2V regulator will be active. For HSIC operation, VDD12 must be tied to VDDCR12.

# 4.2.2 **Dual Supply Configurations**

### 4.2.2.1 VBAT + 1.8V

VBAT must be tied to the VBAT system supply. VDDCOREREG must be tied to the 1.8V system supply. In this configuration, the 3.3V regulator and the 1.2V regulator will be active. For HSIC operation, VDD12 must be tied to VDDCR12.

### 4.2.2.2 3.3V + 1.8V

VBAT must be tied to the 3.3V system supply. VDDCOREREG must be tied to the 1.8V system supply. In this configuration the 3.3V regulator will operate in dropout mode and the 1.2V regulator will be active. For HSIC operation, VDD12 must be tied to VDDCR12.

# 4.3 Power Connection Diagrams

Figure 4.1 illustrates the power connections for the USB4624 with various power supply configurations.

**Figure 4.1 Power Connections**

Note: To achieve the lowest power possible, tie the VDD12 pins to VDD12CR.

# **Chapter 5 Modes of Operation**

The device provides two main modes of operation: Standby Mode and Hub Mode. The operating mode of the device is selected by setting values on primary inputs according to the table below.

**Table 5.1 Controlling Modes of Operation**

| RESET_N<br>INPUT | RESULTING<br>MODE | SUMMARY                                                                                                                                                                                                     |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                | Standby           | Lowest Power Mode: No functions are active other than monitoring the RESET_N input. All port interfaces are high impedance. All regulators are powered off.                                                 |

| 1                | Hub               | <b>Full Feature Mode</b> : Device operates as a configurable USB hub with battery charger detection. Power consumption is based on the number of active ports, their speed, and amount of data transferred. |

**Note:** Refer to Section 8.4.2, "External Chip Reset (RESET\_N)," on page 42 for additional information on RESET\_N.

The flowchart in Figure 5.1 shows the modes of operation. It also shows how the device traverses through the Hub mode stages (shown in bold.) The flow of control is dictated by control register bits shown in italics as well as other events such as availability of a reference clock. The remaining sections in this chapter provide more detail on each stage and mode of operation.

Figure 5.1 Hub Operational Mode Flowchart

# 5.1 Boot Sequence

## 5.1.1 Standby Mode

If the external hardware reset is asserted, the hub will be in Standby Mode. This mode provides a very low power state for maximum power efficiency when no signaling is required. This is the lowest power state. In Standby Mode all internal regulators are powered off, the PLL is not running, and core logic is powered down in order to minimize power consumption. Because core logic is powered off, no configuration settings are retained in this mode and must be re-initialized after RESET\_N is negated high.

## 5.1.2 Hardware Initialization Stage (HW\_INIT)

The first stage is the initialization stage and occurs on the negation of RESET\_N. In this stage the 1.2V regulator is enabled and stabilizes, internal logic is reset, and the PLL locks if a valid REFCLK is supplied. Configuration registers are initialized to their default state and strap input values are latched. The device will complete initialization and automatically enter the next stage. Because the digital logic within the device is not yet stable, no communication with the device using the SMBus is possible. Configuration registers are initialized to their default state.

If there is a REFCLK present, the next state is SW\_INIT.

## 5.1.3 Software Initialization Stage (SW INIT)

Once the hardware is initialized, the firmware can begin to execute. The internal firmware checks for an external SPI ROM. The firmware looks for an external SPI flash device that contains a valid signature of "2DFU" (device firmware upgrade) beginning at address 0xFFFA. If a valid signature is found, then the external ROM is enabled and the code execution begins at address 0x0000 in the external SPI device. If a valid signature is not found, then execution continues from internal ROM. SPI ROMs used with the device must be 1 Mbit and support either 30 MHz or 60 MHz. The frequency used is set using the SPI SPD SEL configuration strap. Both 1- and 2-bit SPI operation is supported. For optimum throughput, a 2-bit SPI ROM is recommended. Both mode 0 and mode 3 SPI ROMS are also supported. Refer to Section 6.3.2, "SPI Speed Select (SPI\_SPD\_SEL)," on page 31 for additional information on selection of the SPI speed.For all other configurations, the firmware checks for the presence of an external I<sup>2</sup>C/SMBus. It does this by asserting two pull down resistors on the data and clock lines of the bus. The pull downs are typically 50Kohm. If there are 10Kohm pull-ups present, the device becomes aware of the presence of an external SMBus/I<sup>2</sup>C bus. If a bus is detected, the firmware transitions to the SOC\_CFG state.

# 5.1.4 SOC Configuration Stage (SOC\_CFG)

In this stage, the SOC may modify any of the default configuration settings specified in the integrated ROM such as USB device descriptors, or port electrical settings, and control features such as upstream battery charging detection.

There is no time limit. In this stage the firmware will wait indefinitely for the SMBus/I<sup>2</sup>C configuration. When the SOC has completed configuring the device, it must write to register 0xFF to end the configuration.

## 5.1.5 Configuration Stage (CONFIG)

Once the SOC has indicated that it is done with configuration, then all the configuration data is combined. The default data, the SOC configuration data, the OTP data are all combined in the firmware and device is programmed.

After the device is fully configured, it will go idle and then into suspend if there is no VBUS or Hub.Connect present. Once VBUS is present, and upstream battery charging is enabled, the device will transition to the Battery Charger Detection Stage (CHGDET). If VBUS is present, and upstream battery charging is not enabled, the device will transitions to the Connect (Hub.Connect) stage.

## 5.1.6 Battery Charger Detection Stage (CHGDET)