# TMC8462 Datasheet

Document Revision V1.4 • 2018-May -09

The TMC8462 is a complete EtherCAT® Slave Controller optimized for real time. It comprises all blocks required for an EtherCAT slave including two 100-Mbit PHYs, a dual switch regulator power supply and 24V capable high voltage I/Os for industrial environments. Timer, watchdog, PWM and SPI/IIC master units allow for enhanced capabilities either in device emulation mode or in combination with an external CPU.

# **Applications**

- Factory Automation

- Process Automation

- Communication Modules

- Industrial IoT

- Industry 4.0

- Sensors & Encoders

#### **Features**

- Standard compliant EtherCAT<sup>®</sup> Slave

- Dual Integrated 100-Mbit Ethernet PHY

- SPI Process Data Interface (PDI)

- IO Block with 24 Multi-Function I/Os

- Internal 3.3V plus free 5V-24V switch regulator

- 8 High Voltage I/Os (up to 35V, 100mA)

- Multifunction block comprises Watchdog, 4 PWM outputs and Step/Dir generator

- Direct EtherCAT access to external ADCs, stepper motor controllers, etc.

- EtherCAT-P compatible voltage range

- Robotics

- Industrial Motion Control

- · Building Automation

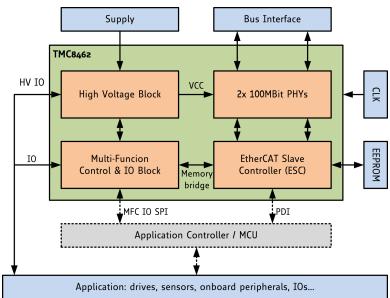

# Simplified Block Diagram

©2018 TRINAMIC Motion Control GmbH & Co. KG, Hamburg, Germany Terms of delivery and rights to technical change reserved. Download newest version at: www.trinamic.com

# **Contents**

| 1 | Product Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                        |  |  |  |  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| 2 | Order Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                      |  |  |  |  |

| 3 | Principles of Operation / Key Concepts 3.1 General Device Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8<br>8<br>9                                                                            |  |  |  |  |

| 4 | Device Pin Definitions 4.1 Pinout and Pin Coordinates of TMC8462-BA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                        |  |  |  |  |

| 5 | Device Usage and Handling 5.1 Process Data Interface 5.1.1 SPI protocol description 5.1.2 Timing example 5.2 MFC IO Control Interface 5.2.1 SPI Protocol description 5.2.2 Timing example 5.2.3 Sharing Bus Lines with the PDI SPI 5.3 Ethernet Physical Layer Connection 5.4 External Circuitry and Applications Examples 5.4.1 Device Reset 5.4.2 Supply Filtering for PLL Supply 5.4.3 PHY Power Regulator Filtering 5.4.4 External Circuit for Fixed Switching Regulator 0 5.4.5 External Circuit for Adjustable Switching Regulator 1 5.4.6 Minimum External Supply Circuit for Single 3.3V Supply 5.4.7 Minimum External Supply Circuit for Single 5V Supply 5.4.8 Minimum External Supply Circuit for Single SV Supply 5.4.9 Typical Power Supply Chain Using Both Buck Converters 5.4.10 Status LED Circuit 5.4.11 SII EEPROM Circuit 5.4.11 SII EEPROM Circuit 5.4.12 Considerations on PHY to PHY Connection | 24<br>26<br>27<br>28<br>31<br>31<br>31<br>32<br>33<br>33<br>34<br>35<br>36<br>37<br>38 |  |  |  |  |

| 6 | 6.1 General EtherCAT Information 6.2 Overview of Available Chip Features 6.3 EtherCAT Register Overview 6.4 EtherCAT Register Set 6.4.1 ESC Information 6.4.2 Station Address 6.4.3 Write Protection 6.4.4 Data Link Layer 6.4.5 Application Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                        |  |  |  |  |

|   | 6.4.10 SII EEPROM Interface                                | 7  |

|---|------------------------------------------------------------|----|

|   | 6.4.11 ESC Parameter RAM                                   | 31 |

|   | 6.4.12 MII Management Interface                            | 32 |

|   | 6.4.13 FMMUs                                               |    |

|   | 6.4.14 SyncManagers                                        |    |

|   | 6.4.15 Distributed Clocks Receive Times                    |    |

|   | 6.4.16 Distributed Clocks Time Loop Control Unit           |    |

|   | 6.4.17 Distributed Clocks Cyclic Unit Control              |    |

|   | 6.4.18 Distributed Clocks SYNC Out Unit                    |    |

|   |                                                            |    |

|   | 6.4.19 Distributed Clocks LATCH In Unit                    |    |

|   | 6.4.20 Distributed Clocks SyncManager Event Times          |    |

|   | 6.4.21 ESC Specific                                        |    |

|   | 6.4.22 Process Data RAM                                    | )9 |

|   |                                                            |    |

| 7 | MFC IO Block Description 11                                | _  |

|   | 7.1 General Information                                    |    |

|   | 7.2 MFC IO Register Overview                               |    |

|   | 7.3 MFC IO Register Set                                    | 15 |

|   | 7.3.1 Incremental Encoder Interface                        | 15 |

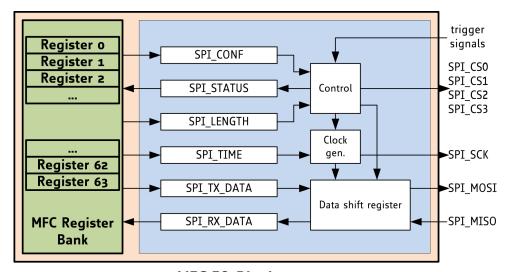

|   | 7.3.2 SPI Master Interface                                 |    |

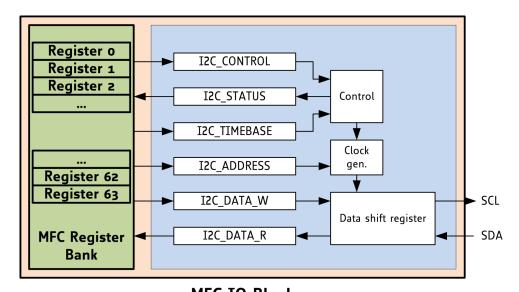

|   | 7.3.3 I2C Master Interface                                 |    |

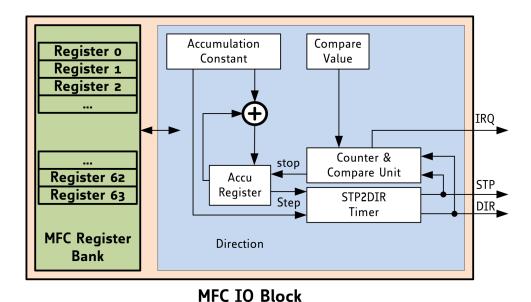

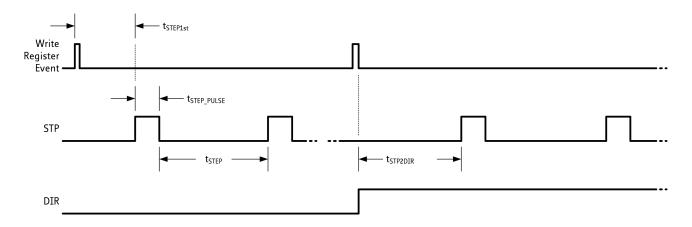

|   | 7.3.4 Step and Direction Signal Generator                  |    |

|   | 7.3.5 PWM Unit                                             |    |

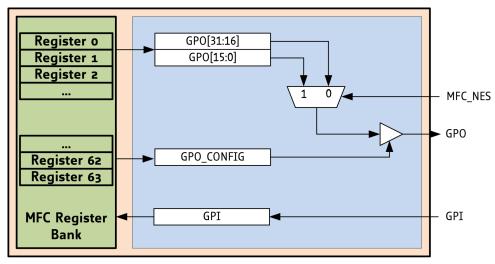

|   | 7.3.6 General Purpose I/Os                                 |    |

|   | · · · · · · · · · · · · · · · · · · ·                      |    |

|   |                                                            |    |

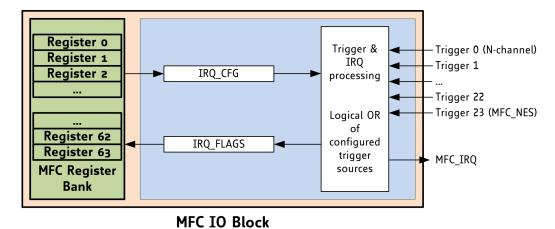

|   | 7.3.8 IRQ Control Block                                    |    |

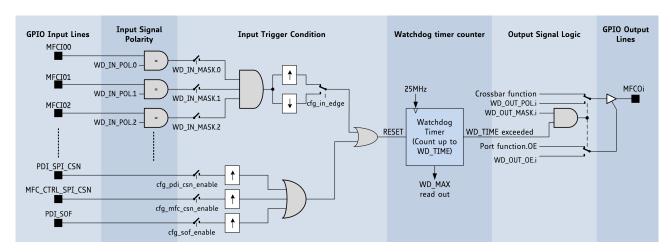

|   | 7.3.9 Watchdog                                             |    |

|   | 7.3.10 High Voltage Status and General Control             |    |

|   | 7.3.11 Application Layer Control                           |    |

|   | 7.4 SII EEPROM MFC IO Block Parameter Map                  |    |

|   | 7.5 SII EEPROM MFC IO Crossbar Mapping                     | 18 |

|   | 7.6 SII EEPROM MFC IO High Voltage IO (HVIO) Configuration | 52 |

|   | 7.7 SII EEPROM MFC IO Switching Regulator Configuration    |    |

|   | 7.8 SII EEPROM MFC IO Memory Block Mapping                 |    |

|   | 7.9 SII EEPROM MFC IO Register Configuration               |    |

|   | 7.10 MFC IO ESI/XML Configuration Block                    |    |

|   | 7.11 MFC IO Incremental Encoder Block                      |    |

|   | 7.12 MFC IO SPI Master Block                               |    |

|   | 7.12.1 SPI Examples                                        |    |

|   |                                                            |    |

|   | 7.13 MFC IO I2C Master Block                               |    |

|   | 7.13.1 I2C Example                                         |    |

|   | 7.14 MFC IO Step and Direction Block                       |    |

|   | 7.15 MFC IO PWM Block                                      |    |

|   | 7.16 MFC IO DAC Block                                      |    |

|   | 7.17 MFC IO General Purpose IO Block                       | 79 |

|   | 7.18 MFC IO IRQ Block                                      |    |

|   | 7.19 MFC IO Watchdog Block                                 | 31 |

|   | 7.20 MFC IO Emergency Switch Input                         |    |

|   | 7.21 MFC IO Analog and High Voltage Block                  |    |

|   | 7.21.1 Multi Voltage High Current I/O Lines                |    |

|   | 7.21.2 Switching Regulators                                |    |

|   | 7.21.3 Analog Block Status Register                        | 38 |

|   |                                                            | _  |

| 8  | Electrical Ratings                        | 190 |

|----|-------------------------------------------|-----|

|    | 8.1 Absolute Maximum Ratings              |     |

|    | <ul><li>8.2 Operational Ratings</li></ul> |     |

|    | 8.3.1 High Voltage I/O Block              |     |

|    | 8.3.2 Switching Regulators                | 192 |

|    | 8.3.3 Digital IOs                         |     |

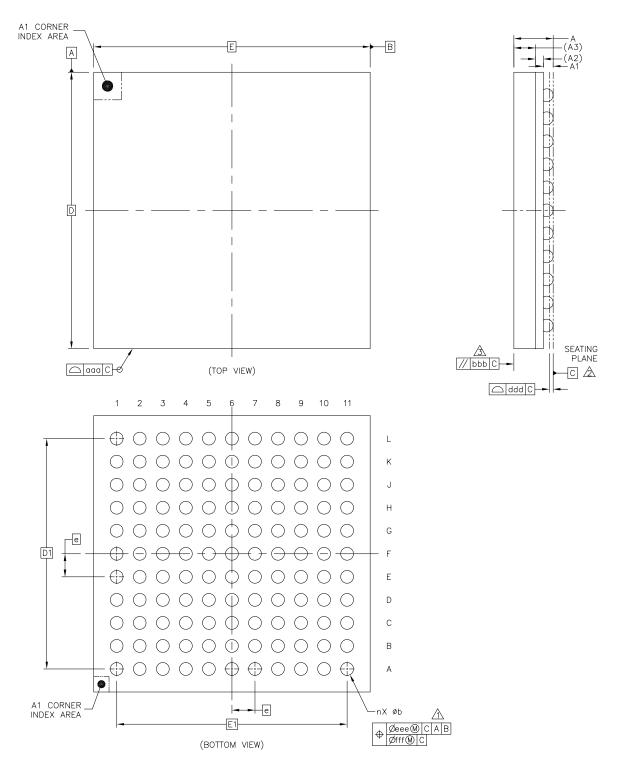

| 9  | Manufacturing Data                        | 194 |

|    | 9.1 Package Dimensions                    | 194 |

|    | 9.2 Marking                               | 196 |

|    | 9.3 Board and Layout Considerations       | 196 |

| 10 | ) Abbreviations                           | 197 |

| 11 | I TMC8462-BA Errata                       | 199 |

|    | 11.1 Case 1 – Lost Link Counters          | 199 |

| 12 | 2 Figures Index                           | 200 |

| 13 | 3 Tables Index                            | 201 |

| 14 | 1 Revision History                        | 204 |

|    | 14.1 IC Revision                          |     |

|    | 14.2 Document Revision                    | 204 |

## 1 Product Features

TMC8462 is an advanced EtherCAT Slave Controller device used for EtherCAT communication. It provides the interface for data exchange between EtherCAT master and the slave's local application controller. In addition, TMC8462 provides complex IO functions paired with high voltage features and integrated 100Bit Ethernet PHYs.

#### **Advantages:**

- Fully standard compliant and proven EtherCAT engine

- Highly integrated with highest feature count vs. package size

- · License-free & royalty-free

- High Voltage & robust

- · Saves board space & reduces BOM

- · Long-term availability

#### **Major Features:**

- EtherCAT Slave Controller with 2 ports for bus interfacing, 8 FMMU & 8 Sync Managers, Distributed clocks with 64 bit, 16KByte of Process Data Memory, external I2C EEPROM, SPI Process Data Interface (PDI), optional device emulation

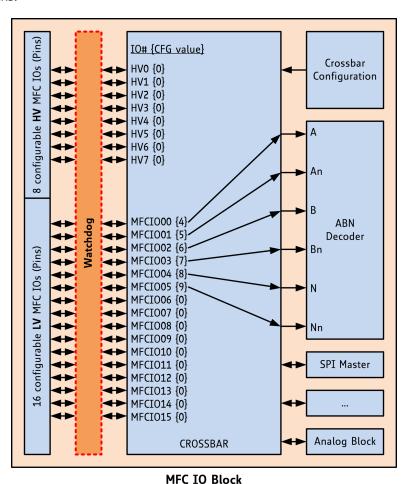

- TRINAMIC Multi-Function Control and IO block with 24 configurable IO ports for complex real-time IO functions (GPIOs, PWM, Step/Direction, I2C, SPI, DAC, incremental encoder) including 8 high voltage IOs

- TRINAMIC high voltage block with 8 short circuit protected push-/pull or open drain high voltage IOs for up to 24V and 100mA drive current

- Two integrated 500mA step down switching voltage regulators with one being fixed at 3.3V and one being programmable between 5V and 24V

- Internal 1.8V linear regulator for core voltage generation

- Two integrated 100-Mbit Ethernet PHYs to directly connect to twisted pair copper or back-to-back directly to another PHY

- Simple configuration of EtherCAT Slave Controller and Multi-Function Control and IO block via EEPROM

- 3.3V Digital IO Voltage

- Working with a single supply voltage depending on application: 3.3V only or 5V to 35V (5V, 12V, or 24V typical)

- Industrial Temperature Range -40°C to +85°C

- Integrated temperature measurement and over-temperature shutdown

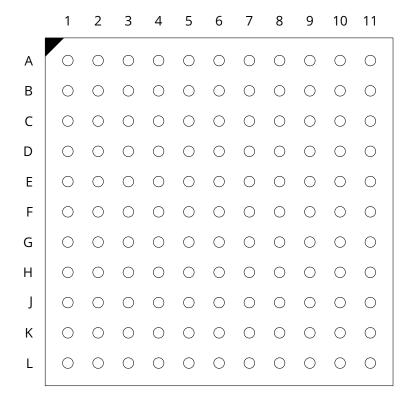

- Package: 9mm x 9mm BGA packge with 121 pins and 0.75mm pitch

# 2 Order Codes

| Order Code      | Description                                                                                                                                        | Size        |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| TMC8462-BA      | 2-BA TMC8462 Advanced EtherCAT® Slave Controller in 121 pin BGA package with 0.75mm pitch                                                          |             |  |  |

| TMC8462-EVAL    | i · · · · · · · · · · · · · · · · ·                                                                                                                |             |  |  |

| Landungsbruecke |                                                                                                                                                    |             |  |  |

| TMC8462-BOB-ETH | Breakout Board (BOB) for TMC8462-BA, with 0.1" header rows, reference clock source, SII-EEPROM, and RJ45 twisted pair copper transceiver interface | 2.0" x 1.5" |  |  |

Table 1: TMC8462 order codes

### **Trademark and Patents**

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany.

# 3 Principles of Operation / Key Concepts

TMC8462 is a highly integrated ASIC providing the interface between the Ethernet-based EtherCAT real-time field bus and the local application. Its extended digital and high voltage feature set provides additional functions to the EtherCAT slave.

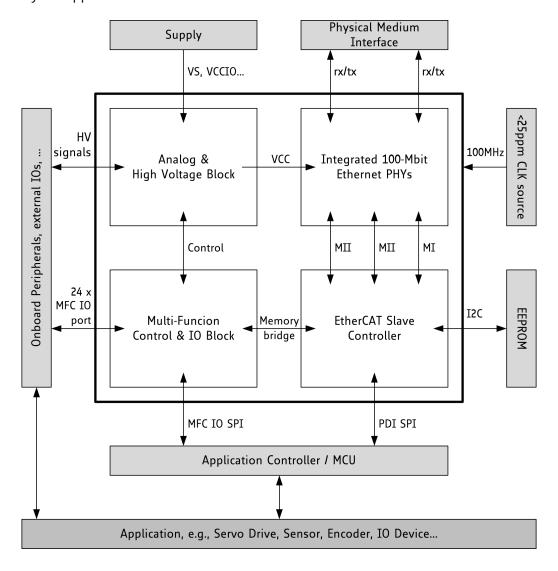

#### 3.1 General Device Architecture

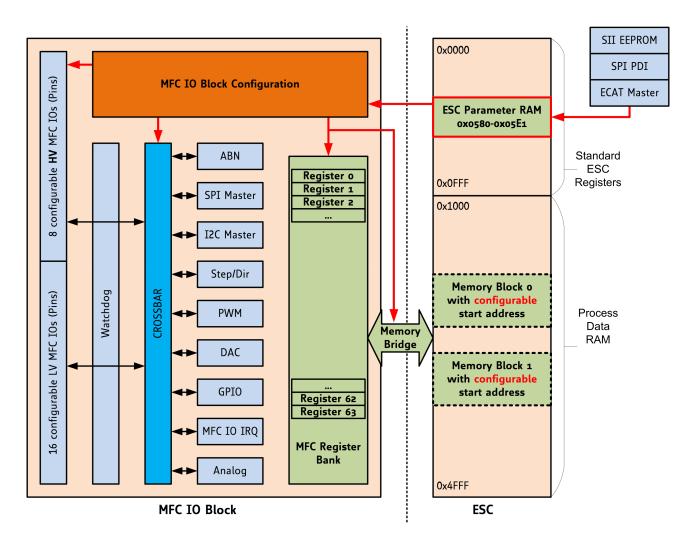

Figure 1 shows the general device architecture and major connections of TMC8462. The four function blocks EtherCAT Slave Controller, Multi-Function Control and IO, Analog and High Voltage, and Ethernet PHYs are introduced in the following sub-sections.

For operation, a stable 100MHz clock source, an IIC EEPROM, and power supply for IO and high voltage operation are required (if the high voltage features are used). An application controller, which also runs the EtherCAT slave stack, connects to the SPI interfaces. The application and onboard peripherals can be controlled by the application controller or the Multi-Function Control and IO block.

Figure 1: General device architecture

#### 3.2 EtherCAT Slave Controller

TMC8462 contains a standard-conform EtherCAT Slave Controller (ESC) providing real-time EtherCAT MAC layer functionality to EtherCAT slaves. It connects via MII interface to standard Ethernet PHYs and provides a digital control interface to a local application controller while also providing the option for standalone operation.

The ESC part of TMC8462 provides the following EtherCAT-related features. More information is available in Section 6.

- Two internal 100Mbit Ethernet PHYs

- Eight Fieldbus Memory Management Units (FMMU)

- Eight Sync Managers (SM)

- 16 KByte of Process Data RAM (PDRAM)

- 64B bit Distributed Clocks support

- I2C interface for external EEPROM for ESC configuration

- SPI Process Data Interface (PDI) with 30Mbit/s

- Proven EtherCAT State Machine (ESM)

- · Device Emulation Mode

### 3.3 Multi-Function and Control IO Block

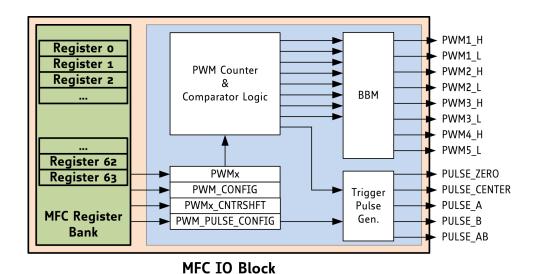

In addition to the EtherCAT functionality, the TMC8462 comes with a dedicated function block providing a configurable set of complex real-time IO functionality for smart (embedded) EtherCAT slave systems. This IO functionality is called Multi-Function Control and IO block (MFC IO). Its special focus is on motor and motion control while it is not limited to this application area.

The MFC IO block combines various functional sub blocks that are helpful in an embedded design to reduce complexity, to simplify bill of materials (BOM), and to provide hardware acceleration to compute intensive or time critical tasks. More information is available in Section 7.

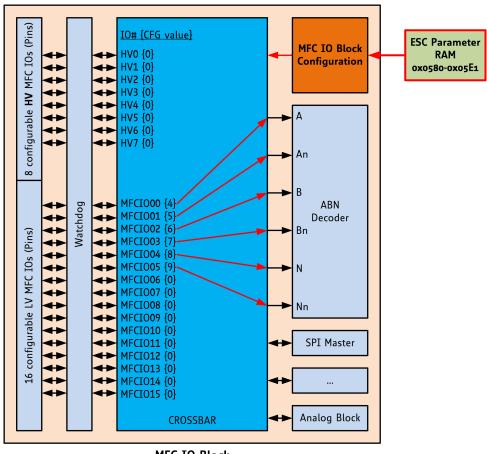

**Configurable IO Ports** The whole MFC IO block provides in total 24 IO ports that can be configured and assigned to any of the available functional units inside the MFC IO block. If not used, each IO port can be tristated.

**General Purpose IOs** Up to sixteen (16) general purpose IOs are available. Each IO can be configured either as input or as output. For the outputs, a safe state can be configured which is used in case of emergency event.

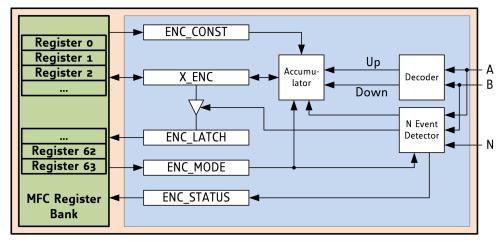

**Incremental Encoder Interface** Configurable incremental encoder interface with 32 bit position registers, single-ended or differential inputs, configurable counting constant for different resolutions, configurable polarity and N-signal behavior.

**Step/Direction Generator Block** The step and direction unit provides upt to 3 independent channels. Various configuration options and modes allow for example for continuous or one-shot mode, reading of the internal total step counters, pre-loading the next step frequency to be used at a certain counter value. The step and direction outputs signals can be single-ended or differential.

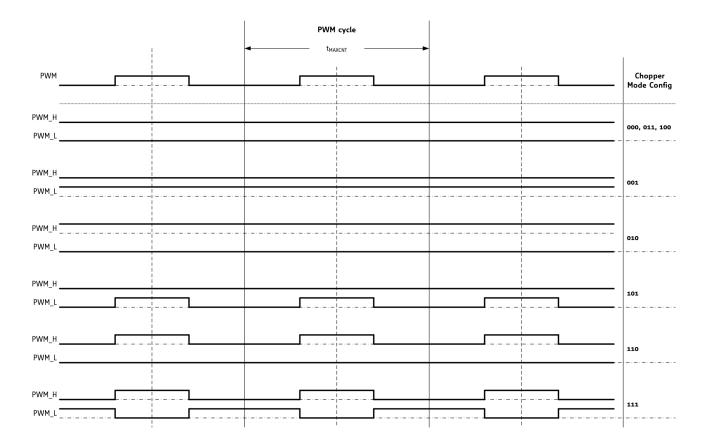

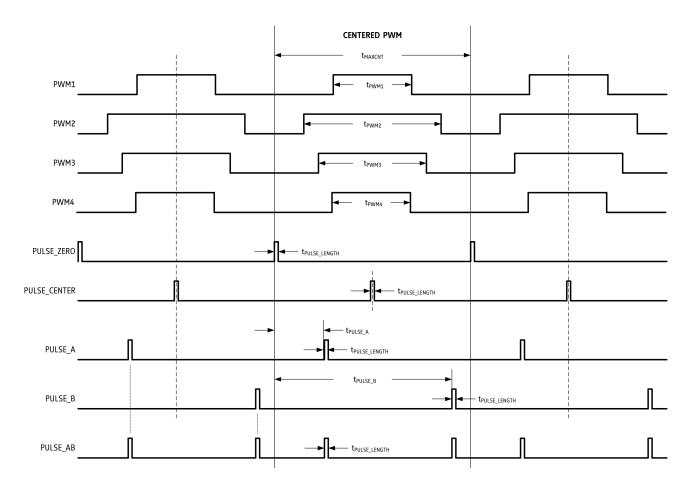

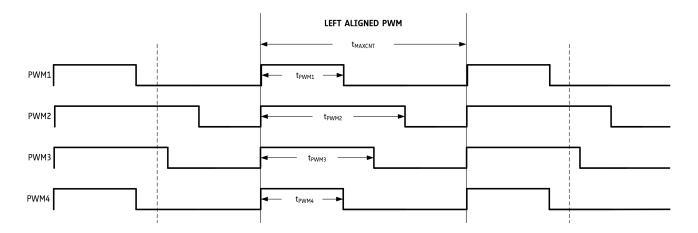

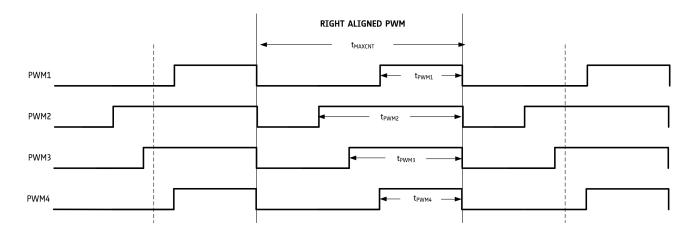

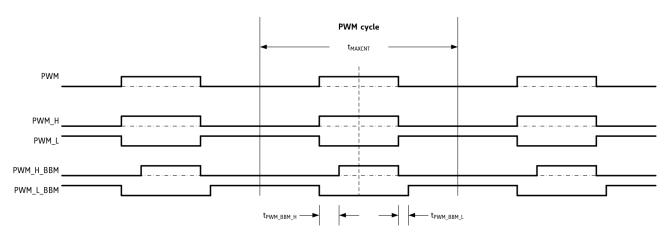

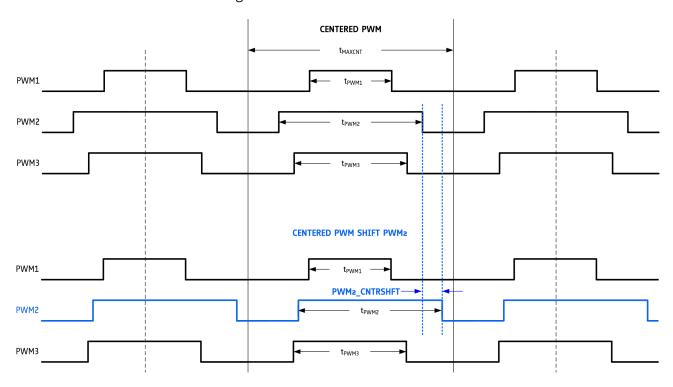

**PWM Block** The integrated PWM block provides up to 4 PWM channels. PWM frequency and duty cycle as well as polarities and dead times are configurable. The outputs can be configured for a safe state in case of emergency.

**Generic SPI Master Interface** The TMC8462 provides a generic SPI master interface to connect to onor off-board SPI slave peripherals like ADCs, sensors, or motor drivers. The SPI master interface is fully configurable and offers 4 slave select lines.

**Generic I2C Master Interface** A generic I2C master interface is also available in TMC8462 to connect to I2C slaves. The I2C bus speed is configurable.

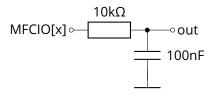

**Digital DAC** A simple digital 16 bit DAC channel is available which requires an external RC circuit for operation.

**Safety Functions** The following safety functions are available with the TMC8462

- Configurable watchdog functionality for the MFC IO block to monitor internal and external signals as well as EtherCAT activity. This block is fully configurable.

- A general emergency switch input can be activated. For critical outputs, a safe state can be configured which is used when the emergency switch triggers.

- A common IRQ signal is available at the MFC IO block which can be mapped to various events of the MFC IO block. The IRQ events can be processed by a local application controller.

## 3.4 Analog and High Voltage Block

TMC8462 has an integrated powerful high voltage sub block that provides analog functions and high voltage support to your EtherCAT slave. The integrated high voltage capabilities allow for BOM reduction and save board space. More information is available in Section 7.21.

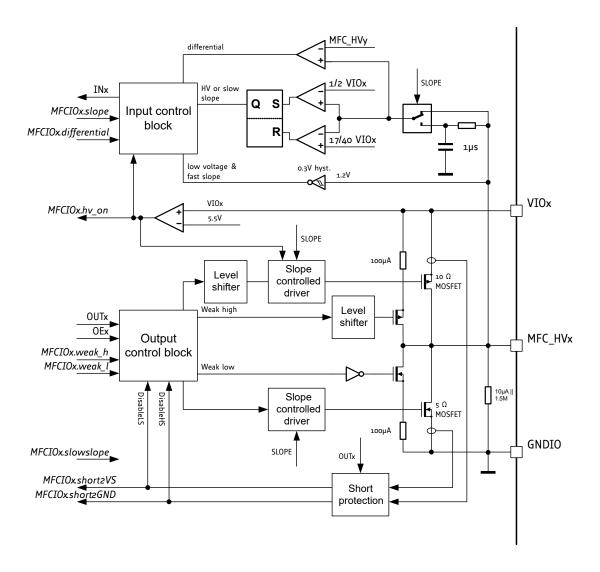

**High Voltage Ports** 8 of the 24 configurable IO ports of the MFC IO block are high voltage IO ports. For pure digital systems operating at 3.3V or 5V these ports can simply be used as standard IO ports. When using a higher supply voltage at the VIOx inputs the high voltage ports can be used at up to 35V (5V, 12V, 24V typical). The 8 high voltage ports are grouped into 3 groups with 2, 3, and 3 ports. Each group can be used a different supply voltage level using VIO1, VIO2, and VIO3 inputs.

Each high voltage port has a short circuit protected push-/pull or open drain output stage with 100mA drive current (ca. 200mA short time) and can be combined with any signal of the MFC IO block functions. The outputs' slope can be controlled. An optional input filter is selectable as well as pull downs or pull ups with  $100\mu A$ .

The high voltage ports have an over-temperature shutdown.

**WARNING**

When driving inductive loads a freewheeling diode must be provided to the high voltage I/O pins to prevent from latch-up.

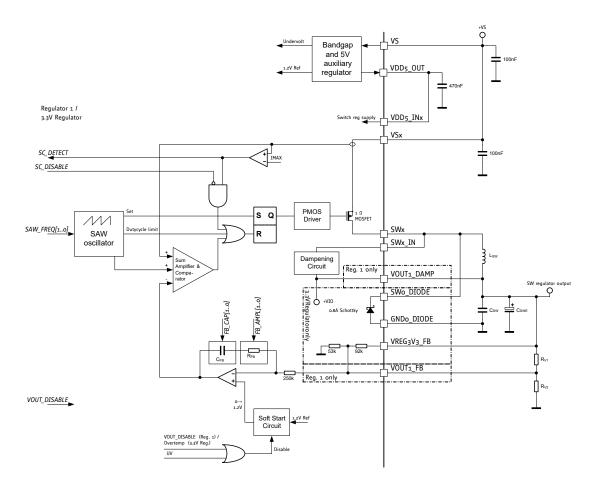

**Switching Regulators** Two switching regulators (buck regulators) are integrated into TMC8462 – SW0 and SW1. Both are capable of driving up to 500mA.

SW0 generates a fixed 3.3V rail for internal and external logic supply. SW1 is programmable between 3.3V and VS (up to 24V) and can be used for peripheral supply, e.g, to generate a 5V encoder supply. Each switching regulator comes with a separate over-temperature shutdown.

**Single Supply Operation** TMC8462 is designed to work with a single external power supply rail. All required supply voltages are generated internally. The required external supply rail depends on the application scenario (between 3.3V and 24V).

#### 3.5 Interfaces

**Field Bus Interface** TMC8462 contains 2 integrated 100-Mbit Ethernet PHYs and directly connects to the field bus using an external transformer circuit. In addition, the PHY interfaces of two TMC8462 devices can also be connected directly to allow back-to-back connection with only low part count and a small circuit. This is useful when extending the EtherCAT bus on the board or to a another slave close by.

**ESC Process Data Interface** The ESC part can be accessed via the so-called Process Data Interface (PDI). TMC8462 comes with an SPI PDI. Besides the standard SPI bus lines additional control signals belong to the SPI PDI, which are further described in Section 5.1..

**MFC IO Control Interface** The MFC IO block of TMC8462 can be accessed from EtherCAT master side or from the local application controller. For connection to the local application controller, a second SPI interface – the MFC IO SPI – is provided. The protocol used nearly identical to the SPI PDI interface. Additional information on the MFC IO SPI is given in Section 5.2.

**EEPROM Interface** The EEPROM interface is intended to be a point-to-point interface between TMC8462 and EEPROM with TMC8462 being the master. If other I2C masters are required to access the I2C bus, TMC8462 must be held in reset state, for example for in-circuit-programming of the EEPROM. During operation, the application controller must tristate its I2C interface. Depending on the EEPROM size the addressing mode must be properly set using the PROM\_SIZE configuration pin.

**Configuration Inputs** Hard-wired configuration pins are available at the TMC8462, which are used to configure various options related to the hardware configuration and application scenario and which will not change. These pins are PROM\_SIZE, PDI\_SHARED\_SPI\_BUS, and DEVICE\_EMULATION. More information on these configuration pins and signals is given in Section 4.2 and Section 5.

## 3.6 Software- and Tool-Support

TRINAMIC's EtherCAT Slave Controller family comes with extensive hardware and software tool support to get started quickly.

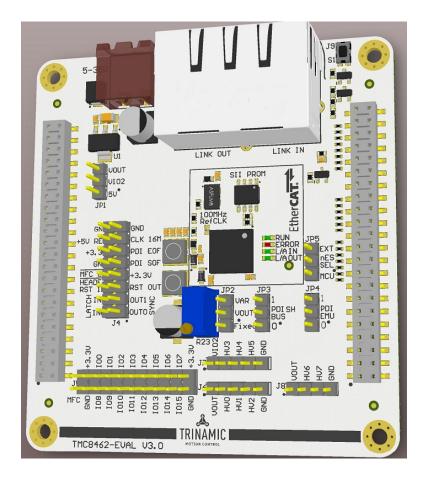

**Evaluation Board** An evaluation board is available for the TMC8462 with standard RJ45 connectors and transformers for interfacing twisted pair copper (TPC) media.

Figure 2: TMC8462 Evaluation Board

The complete board design files are available for download and can be used as reference. All information is available for download on the specific product page on TRINAMIC's website at <a href="http://www.trinamic.com/products/integrated-circuits/evalboards">http://www.trinamic.com/products/integrated-circuits/evalboards</a>.

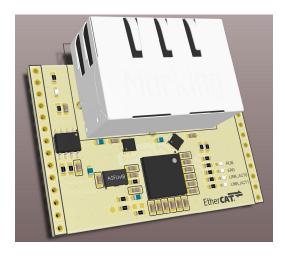

**Breakout Board (BOB)** Besides the Evaluation board another smaller breakout board is available. It allows for easy integration into own systems or connection to a prototyping platform. The breakout board provides the bus interface along with the ESC and requires an appropriate supply and controller connection. The BOB comes with standard RJ45 connectors to connect to TPC using the TMC8462 ESC with integrated Ethernet PHYs. TMC8462 is functionally equal to the TMC8461. The difference is in using external PHYs vs. integrated PHYs. The complete board design files are available for download and can be used as reference. All information is available for download from the evaluation board section on TRINAMIC's website at

https://www.trinamic.com/support/eval-kits/.

Figure 3: TMC8462 breakout board for RJ45 and TPC

**TRINAMIC Technology Access Package** In addition, a comprehensive source code and software package – TRINAMIC Technology Access Package (TTAP) – is available for download to get started quickly with own code.

The TTAP is available at https://www.trinamic.com/support/software/access-package/.

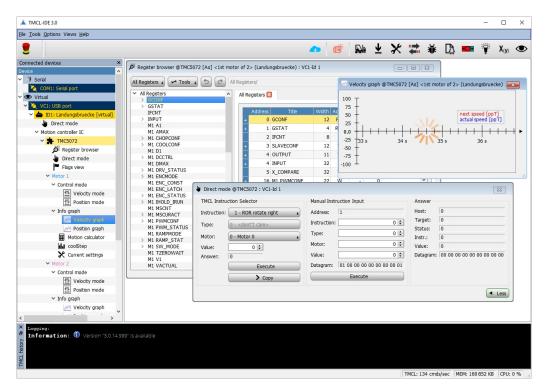

**TMCL-IDE** The TMCL-IDE is TRINAMIC's primary tool (for Windows PCs) to control TRINAMIC modules and evaluation boards. Besides, it provides feature like remote firmware updates, module monitoring options, and specific Wizard support. The TMCL-IDE can be used along with TRINAMICs modular evaluation board system.

Figure 4: TMCL-IDE

The latest version and additional information is available for download from TRINAMIC's website at <a href="http://www.trinamic.com/software-tools/tmcl-ide">http://www.trinamic.com/software-tools/tmcl-ide</a>.

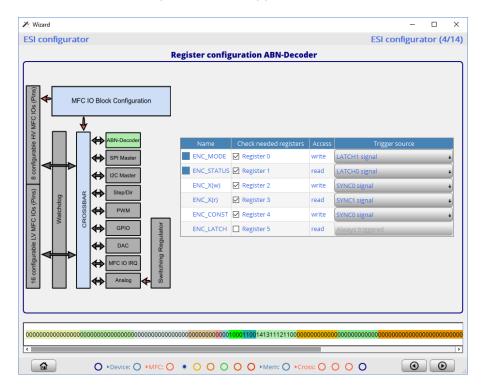

**EtherCAT Slave Configuration** Configuration of the EtherCAT Slave Controller is done during boot time with configuration information read from the SII EEPROM after reset or power cycling. This information must be (pre)programmed into the SII EEPROM. This can be done via the EtherCAT master using a so-called EtherCAT Slave Information (ESI) file in standardized XML format. The SII EEPROM can also be (re)written using the local application controller.

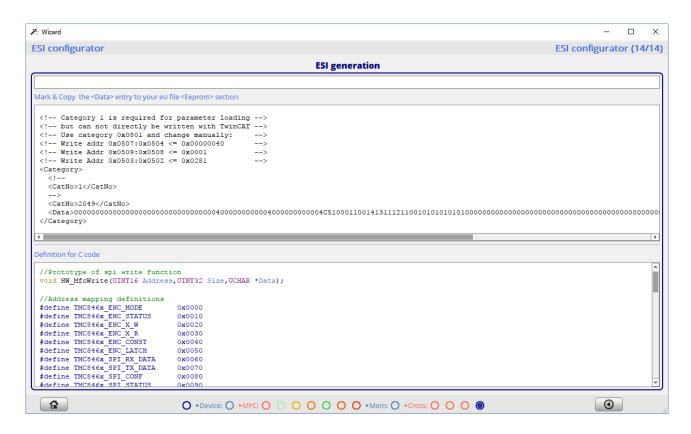

**ESI Configuration Wizard** The TMCL-IDE contains a wizard to assist users with the configuration of the TMC8462 various MFC IO functions. The wizard shows available and allowed options and provides XML code snippets for the ESI file for the SII EEPROM as well as generic C-Code blocks. These can be used as starting point for own firmware development for the application controller.

Figure 5: Configuration wizard example - MFC IO block configuration

Figure 6: Configuration wizard example – SII EEPROM content and C-code output

# **4 Device Pin Definitions**

# 4.1 Pinout and Pin Coordinates of TMC8462-BA

Figure 7: TMC8462-BA Pinout top view

# **4.2 Signal Descriptions**

| Name                   | Pin | Type (I,O,PU,PD) | Function                                                                                                                                                                                                                 |

|------------------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>General Signals</b> |     |                  |                                                                                                                                                                                                                          |

| NRESET                 | К4  | I/O              | Low active system reset. NRESET is an I/O pin. Connected to VCCIO via a 10K resistor and to GND via a 10nF capacitor if no other reset source for proper power-on reset is used. For more information see Section 5.4.1. |

| REF_CLK100_IN          | L3  | I                | 100MHz Reference clock input, connect to a clock source <25ppm.                                                                                                                                                          |

| CLK16_OUT              | H7  | 0                | 16.6MHz auxiliary clock output. Not available during reset.                                                                                                                                                              |

| EN_CLK16_OUT           | E9  | 1                | Enable signal for CLK16_OUT: 0 = off, 1 = on                                                                                                                                                                             |

| Name      | Pin | Type (I,O,PU,PD) | Function                                                                                                                                                                                                                                 |

|-----------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_OUT | J4  | 0                | This high-active reset output is activated via EtherCAT register $0 \times 0040$ ), therefore RESET_OUT has to trigger the NRESET input, which clears RESET_OUT. This connection incl. changing the polarity has to be made externally . |

| Name       | Pin | Type (I,O,PU,PD) | Function                                                                                                                                                                                                                          |

|------------|-----|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EEPROM IOs |     |                  |                                                                                                                                                                                                                                   |

| PROM_INIT  | J5  | 0                | Signal indicating that EEPROM has been loaded,<br>0 = not ready, 1 = EEPROM loaded                                                                                                                                                |

| PROM_CLK   | H4  | 0                | External I2C EEPROM clock signal, use 1K pull up resistor to 3.3V                                                                                                                                                                 |

| PROM_DATA  | H5  | 1/0              | External I2C EEPROM data signal, use 1k pull up resistor to 3V3                                                                                                                                                                   |

| PROM_SIZE  | G9  | I                | Selects between two different EEPROM sizes since the communication protocol for EEPROM access changes if a size > 16kBit is used (an additional address byte is required then). 0 = up to 16kBit EEPROM, 1 = 32 kBit-4Mbit EEPROM |

| DC Synchronization IOs |    |   |                                                                       |  |

|------------------------|----|---|-----------------------------------------------------------------------|--|

| SYNC_OUT0              | D7 | 0 | Distributed Clocks synchronization output 0, typically connect to MCU |  |

| SYNC_OUT1              | D6 | 0 | Distributed Clocks synchronization output 1, typically connect to MCU |  |

| LATCH_IN0              | C7 | I | Latch input 0 for Distributed Clocks, connect to GND if not used.     |  |

| LATCH_IN1              | C6 | I | Latch input 1 for Distributed Clocks, connect to GND if not used.     |  |

| LEDs      |    |   |                                                                                           |

|-----------|----|---|-------------------------------------------------------------------------------------------|

| LED_RUN   | B3 | 0 | Run Status LED, connect to green LED (Anode) 0 = LED off, 1 = LED on                      |

| LED_ERR   | C3 | 0 | Error Status LED, connect to red LED (Anode) 0 = LED off, 1 = LED on                      |

| LINK_ACT0 | D3 | 0 | Link In Port Status and Activity, connect to green<br>LED (Anode) 0 = LED off, 1 = LED on |

| LINK_ACT1 | E3 | 0 | Link Out Port Status and Activity, connect to green LED (Anode) 0 = LED off, 1 = LED on   |

| Name                 | Pin                                    | Type (I,O,PU,PD) | Function                                                                                                                                                                                                                                   |  |  |  |

|----------------------|----------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Process Data Interfa | Process Data Interface IOs to/from MCU |                  |                                                                                                                                                                                                                                            |  |  |  |

| PDI_SOF              | H3                                     | 0                | Ethernet Start-of-Frame if 1                                                                                                                                                                                                               |  |  |  |

| PDI_EOF              | G3                                     | 0                | Ethernet End-of-Frame if 1                                                                                                                                                                                                                 |  |  |  |

| PDI_SPI_CSN          | L4                                     | I                | Chip select signal of the process data interface                                                                                                                                                                                           |  |  |  |

| PDI_SPI_SCK          | K3                                     | I                | Serial clock signal of the process data interface                                                                                                                                                                                          |  |  |  |

| PDI_SPI_MOSI         | L5                                     | I                | Serial data out signal of the process data interface                                                                                                                                                                                       |  |  |  |

| PDI_SPI_MISO         | K5                                     | 0                | Serial data in signal of the process data interface                                                                                                                                                                                        |  |  |  |

| PDI_SPI_IRQ          | J3                                     | 0                | Interrupt signal for primary process data interface, connect to MCU                                                                                                                                                                        |  |  |  |

| PDI_WDSTATE          | G4                                     | 0                | EtherCAT Watchdog state, 0: Expired, 1: Not expired                                                                                                                                                                                        |  |  |  |

| PDI_WDTRIGGER        | F4                                     | 0                | EtherCAT Watchdog trigger if 1                                                                                                                                                                                                             |  |  |  |

| PDI_EMULATION        | J7                                     | I                | Selects between PDI interface (SPI) or standalone operation with state machine emulation inside ESC. Has weak internal pull down. 0 = default, PDI interface active, 1 = standalone operation, state machine emulation in Slave Controller |  |  |  |

| MFC IO Control Inter | MFC IO Control Interface IOs |   |                                                                                                                                                                                                                        |  |  |  |

|----------------------|------------------------------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MFC_CTRL_SPI_CSN     | D4                           | I | Chip select signal of the MFC IO control interface                                                                                                                                                                     |  |  |  |

| MFC_CTRL_SPI_SCK     | E4                           | I | Serial clock signal of the MFC IO control interface                                                                                                                                                                    |  |  |  |

| MFC_CTRL_SPI_MOSI    | C4                           | I | Serial data out signal of the MFC IO control interface                                                                                                                                                                 |  |  |  |

| MFC_CTRL_SPI_MISO    | E7                           | 0 | Serial data in signal of the MFC IO control interface                                                                                                                                                                  |  |  |  |

| MFC_IRQ              | E6                           | 0 | MFCIO block IRQ for configurable events, connect to MCU, high active                                                                                                                                                   |  |  |  |

| MFC_NES              | C5                           | I | low active (not) Emergency Stop/Switch/Halt (to<br>bring PWM or other outputs into a safe state),<br>the event must be cleared actively, has weak in-<br>ternal pull down, must be driven high for normal<br>operation |  |  |  |

| PDI_SHARED_BUS       | F9                           | I | Selects between separate SPI buses (MISO, MOSI, SCK) or one SPI bus with two CS lines for the PDI and MFC CTRL SPI interface: 0 = two separate SPI buses, 1 = one shared SPI bus using the PDI_SPI_x bus lines         |  |  |  |

| Name    | Pin | Type (I,O,PU,PD) | Function                    |

|---------|-----|------------------|-----------------------------|

| MFC IOs |     |                  |                             |

| MFCIO00 | J8  | I/O              | MFCIO block low voltage I/O |

| MFCIO01 | J9  | I/O              | MFCIO block low voltage I/O |

| MFCIO02 | J10 | I/O              | MFCIO block low voltage I/O |

| MFCIO03 | J11 | I/O              | MFCIO block low voltage I/O |

| MFCIO04 | H8  | I/O              | MFCIO block low voltage I/O |

| MFCIO05 | H9  | I/O              | MFCIO block low voltage I/O |

| MFCIO06 | H10 | I/O              | MFCIO block low voltage I/O |

| MFCIO07 | H11 | I/O              | MFCIO block low voltage I/O |

| MFCIO08 | D8  | I/O              | MFCIO block low voltage I/O |

| MFCIO09 | D9  | I/O              | MFCIO block low voltage I/O |

| MFCIO10 | D10 | I/O              | MFCIO block low voltage I/O |

| MFCIO11 | D11 | I/O              | MFCIO block low voltage I/O |

| MFCIO12 | C8  | I/O              | MFCIO block low voltage I/O |

| MFCIO13 | C9  | I/O              | MFCIO block low voltage I/O |

| MFCIO14 | C10 | I/O              | MFCIO block low voltage I/O |

| MFCIO15 | C11 | 1/0              | MFCIO block low voltage I/O |

| MFC High Voltage IOs     |     |     |                              |

|--------------------------|-----|-----|------------------------------|

| MFC_HV0 (MFCIO16) A4     |     | 1/0 | MFCIO block high voltage I/O |

| MFC_HV1 (MFCIO17) A5 I/O |     | 1/0 | MFCIO block high voltage I/O |

| MFC_HV2 (MFCIO18)        | A6  | 1/0 | MFCIO block high voltage I/O |

| MFC_HV3 (MFCIO19)        | A7  | 1/0 | MFCIO block high voltage I/O |

| MFC_HV4 (MFCIO20)        | A8  | 1/0 | MFCIO block high voltage I/O |

| MFC_HV5 (MFCIO21)        | A9  | 1/0 | MFCIO block high voltage I/O |

| MFC_HV6 (MFCIO22)        | A10 | 1/0 | MFCIO block high voltage I/O |

| MFC_HV7 (MFCIO23)        | A11 | I/O | MFCIO block high voltage I/O |

| Name                         | Pin | Type (I,O,PU,PD) | Function                               |

|------------------------------|-----|------------------|----------------------------------------|

| MFC High Voltage IO Supplies |     |                  |                                        |

| VIO1                         | B5  | I                | MFCHVIO block 1 supply voltage         |

| VIO2                         | B7  | I                | MFCHVIO block 2 supply voltage         |

| VIO3                         | В9  | I                | MFCHVIO block 3 supply voltage         |

| GNDIO1                       | B6  | I                | MFCHVIO block 1 ground, connect to GND |

| GNDIO2                       | B8  | I                | MFCHVIO block 2 ground, connect to GND |

| GNDIO3                       | B10 | I                | MFCHVIO block 3 ground, connect to GND |

| Device Supply and G | Device Supply and Ground |   |                                                                                  |  |

|---------------------|--------------------------|---|----------------------------------------------------------------------------------|--|

| VS                  | B11                      | I | Supply voltage, use a 100nF filter capacitor                                     |  |

| VCCIO               | E10, F10,                | I | I/O supply voltage, use a 100nF filter capacitor per pin                         |  |

|                     | G10, F11                 |   |                                                                                  |  |

| VCC_CORE            | F6, G6,                  | I | Core supply voltage, connect to VDD1V8_OUT, use a 100nF filter capacitor per pin |  |

|                     | F7, G7                   |   |                                                                                  |  |

| PLLCLK_VCCIO        | K6                       | I | PLL supply voltage, connect to VCCIO through a filter (R/L/C)                    |  |

| TSTCLK_SELECT       | Н6                       | I | Test input, always connect to VCCIO for normal operation                         |  |

| GND                 | C1, F1,                  | I | Supply Ground                                                                    |  |

|                     | J1, A3,                  |   |                                                                                  |  |

|                     | B4, F5,                  |   |                                                                                  |  |

|                     | G5, E8,                  |   |                                                                                  |  |

|                     | F8, G8                   |   |                                                                                  |  |

| PLLCLK_GND          | J6                       | I | PLL supply ground, connect to GND                                                |  |

| Voltage Regulator IOs |     |   |                                                                        |

|-----------------------|-----|---|------------------------------------------------------------------------|

| VDD1V8_OUT            | G11 | 0 | Output of internal 1.8V regulator, <b>use a 100nF filter capacitor</b> |

| VDD5_OUT              | E11 | 0 | Output of internal 5V regulator, use a 100nF filter capacitor if VS≥5V |

| Name                      | Pin | Type (I,O,PU,PD) | Function                                                                                  |

|---------------------------|-----|------------------|-------------------------------------------------------------------------------------------|

| Switching Regulator 0 IOs |     |                  |                                                                                           |

| VS0                       | L7  | I                | Switching regulator 0 supply voltage, Switching regulator 0 provides a fixed 3.3V output. |

| GND0                      | L9  | I                | Switching regulator 0 ground, <b>connect to GND</b>                                       |

| SW0                       | L8  | 0                | Switching regulator 0 output, fixed 3.3V                                                  |

| SW_DIODE                  | K7  | I                | Switching regulator 0 internal diode, connect to SW0 only if VS0 is at or below 5V        |

| GND_DIODE                 | K8  | I                | Switching regulator 0 internal diode ground, <b>connect to GND</b>                        |

| Switching Regulator 1 IOs |     |   |                                                                                                    |

|---------------------------|-----|---|----------------------------------------------------------------------------------------------------|

| VS1                       | L11 | I | Switching regulator 1 supply voltage, Switching regulator 1 provides an adjustable output voltage. |

| GND1                      | K9  | I | Switching regulator 1 ground, connect to GND                                                       |

| SW1                       | L10 | 0 | Switching regulator 1 output, adjustable                                                           |

| VOUT                      | K10 | I | Switching regulator 1 inductor ringing suppression feedback                                        |

| VOUT_FB                   | K11 | I | Switching regulator 1 feedback voltage, 1.2V typically                                             |

| Bus Interface 0 IOs (EtherCAT IN Port) |    |         |                                                                        |

|----------------------------------------|----|---------|------------------------------------------------------------------------|

| TN0                                    | D1 | 0       | Negative pin of differential transmit output pair                      |

| TP0                                    | E1 | 0       | Positive pin of differential transmit output pair                      |

| RN0                                    | A1 | I       | Negative pin of differential receive output pair                       |

| RP0                                    | B1 | I       | Positive pin of differential receive output pair                       |

| REGOUT0                                | A2 | 0       | Regulator power output, use a 10uF and 0.1uF for filtering power noise |

| MCLK                                   | F2 | 0       | PHY management clock, leave open if not needed                         |

| MDIO                                   | F3 | I/O, PU | PHY management data, use 4K7 pull up resistor to VCCIO (3.3V)          |

| Name                                    | Pin | Type (I,O,PU,PD) | Function                                                               |

|-----------------------------------------|-----|------------------|------------------------------------------------------------------------|

| Bus Interface 1 IOs (EtherCAT OUT Port) |     |                  |                                                                        |

| TN1                                     | K1  | IO               | Negative pin of differential transmit output pair                      |

| TP1                                     | L1  | Ю                | Positive pin of differential transmit output pair                      |

| RN1                                     | G1  | Ю                | Negative pin of differential receive output pair                       |

| RP1                                     | H1  | Ю                | Positive pin of differential receive output pair                       |

| REGOUT1                                 | L2  | 0                | Regulator power output, use a 10uF and 0.1uF for filtering power noise |

| Test Pins only |    |       |                                           |

|----------------|----|-------|-------------------------------------------|

| TST_MODE       | E5 | 1     | Test mode enable, <b>connect to GND</b>   |

| TST_ANA        | D5 | 0     | Analog test output, <b>leave open</b>     |

| RXCLK0         | D2 | Ю     | Clock test pin, <b>leave open</b>         |

| RXCLK1         | G2 | Ю     | Clock test pin, <b>leave open</b>         |

| TXCLK0         | E2 | Ю     | Clock test pin, <b>leave open</b>         |

| TXCLK1         | H2 | Ю     | Clock test pin, <b>leave open</b>         |

| RXDV0          | B2 | I, PD | Test pin, leave open for normal operation |

| RXDV1          | K2 | I, PD | Test pin, leave open for normal operation |

| TXER0          | C2 | I, PD | Test pin, leave open for normal operation |

| TXER1          | J2 | I, PD | Test pin, leave open for normal operation |

| CLKO_100       | L6 | 0     | 100MHz clock output                       |

Table 2: Pin and Signal description for TMC8462-BA

# 5 Device Usage and Handling

### **5.1 Process Data Interface**

The Process Data Interface (PDI) is an SPI interface with a clock frequency of up to 30 MHz. The ESC registers and the process data RAM can be accessed from an external microcontroller using this interface. The interface can be configured via the EEPROM, however it is recommended to use the default configuration (SPI mode 3 with low active chip select). For further details, see the ESC SPI slave configuration registers in Section 6.

Additionally, some signals are available that can be evaluated by the application controller.

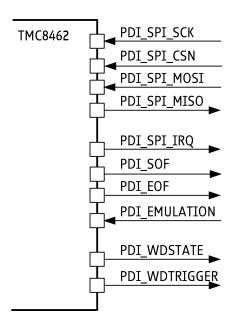

Figure 8: PDI control signals

| TMC8462 pin   | Description                                                                                                                                                                                                 | Typical pin on a MCU                                          |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| PDI_SPI_CSN   | SPI chip select for the TMC8462 PDI                                                                                                                                                                         | SSx                                                           |

| PDI_SPI_SCK   | SPI master clock                                                                                                                                                                                            | SCK                                                           |

| PDI_SPI_MOSI  | Master out slave in data                                                                                                                                                                                    | MOSI                                                          |

| PDI_SPI_MISO  | Master in slave out data                                                                                                                                                                                    | MISO                                                          |

| PDI_SPI_IRQ   | Configurable IRQ from PDI                                                                                                                                                                                   | General purpose Input                                         |

| PDI_EMULATION | 0: default mode for complex slaves, state machine changes processed in microcontroller firmware (SSC); 1: device emulation mode for, e.g., simple slaves, state machine changes directly handled in the ESC | General purpose Output or connected to either ground or 3.3V. |

| PDI_SOF       | Indicates start of an Ethernet/EtherCAT frame (MII_RXDV = '1')                                                                                                                                              | General purpose Input                                         |

| TMC8462 pin   | Description                                  | Typical pin on a MCU  |

|---------------|----------------------------------------------|-----------------------|

| PDI_EOF       | Indicates end of an Ethernet/EtherCAT frame  | General purpose Input |

| PDI_WDSTATE   | 0: Watchdog expired; 1: Watchdog not expired | General purpose Input |

| PDI_WDTRIGGER | Watchdog triggered if '1'                    | General purpose Input |

Table 3: PDI signal description

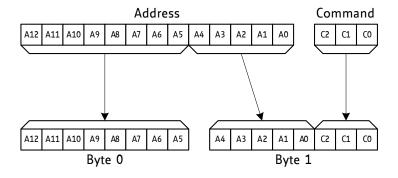

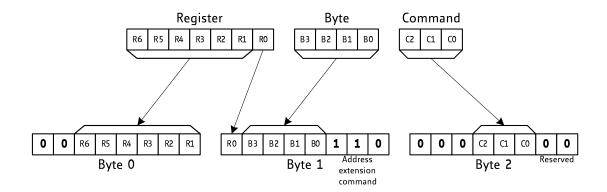

## 5.1.1 SPI protocol description

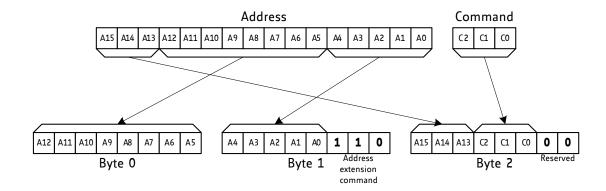

Each SPI datagram contains a 2- or 3-byte address/command part and a data part. For addresses below 0x2000, the 2-byte addressing mode can be used, the 3 byte addressing mode can be used for all addresses.

| C2 | C1 | C0 | Command                                     |

|----|----|----|---------------------------------------------|

| 0  | 0  | 0  | NOP (no operation, no following data bytes) |

| 0  | 0  | 1  | Reserved                                    |

| 0  | 1  | 0  | Read                                        |

| 0  | 1  | 1  | Read with wait state byte                   |

| 1  | 0  | 0  | Write                                       |

| 1  | 0  | 1  | Reserved                                    |

| 1  | 1  | 0  | Address extension, signaling 3 byte mode    |

| 1  | 1  | 1  | Reserved                                    |

Table 4: PDI SPI commands

Figure 9: PDI SPI 2 byte addressing

Figure 10: PDI SPI 3 byte addressing

Unless highest performance is required, using only the 3-byte addressing mode and the read with wait state command is recommended since it reduces the need for special cases in the software. During the address/command bytes, the ESC replies with the contents of the event request registers (0x0220, 0x0221 and in 3 byte addressing mode 0x0222).

#### **Command 0 - NOP**

This command can be used for checking the event request registers and resetting the PDI watchdog without a read or write access.

Example datagram: 0x00 0x00 Example reply (AL Control event bit is set): 0x01 0x00

#### Command 2 - READ

With the read command, an arbitrary amount of data can be read from the device. The first byte read is the data from the address given by the address/command bytes. With every read byte, the address is incremented. During the data transfer, the SPI master sends 0x00 except for the last byte where a 0xFF is sent

When using this command, a pause of 240ns or more must be included between the address/command bytes and the data bytes for the ESC to fetch the requested data.

Example datagram (Read from address 0x0120 and 0x0121): 0x09 0x02 0x00 0xFF Example reply (Operational State requested): 0x01 0x00 0x08 0x00

### **Command 3 - READ WITH WAIT STATE BYTE**

This command is similar to the Read command with an added dummy byte between the address/command part and the data part of the datagram. This allows enough time to fetch the data in any case.

Example datagram (Read starting at address 0x3400): 0xA0 0x06 0x2C 0xFF 0x00 0x00 0x00 0xFF Example reply (0xXX is undefined data): 0x00 0x00 0x00 0x00 0xXX 0x44 0x41 0x54 0x41

#### **Command 4 - WRITE**

The write command allows writing of an arbitrary number of bytes to writable ESC registers or the process data RAM. It requires no wait state byte or delay after the address/command bytes. After every transmitted byte, the address is incremented.

Example datagram (Write starting at address 0x4200): 0x10 0x06 0x50 0x4C 0x48 Example reply (0xXX is undefined data): 0x00 0x00 0x00 0xXX 0xXX Address 0x4200 now contains 0x4C, Address 0x4201 contains 0x48

#### **Command 6 - ADDRESS EXTENSION**

The address extension command is mainly used for the 3-byte addressing mode as shown in Figure 10. For SPI masters that can only process datagrams with an even number of bytes, it might be necessary to pad the datagram to an even number of bytes. This can be achieved by duplicating the third byte of the 3-byte address/command part and using the address extension command in all but the last duplicate. For example, a SPI master that is only capable of transmitting a multiple of 4 bytes cannot use the example datagram for a write access above since it contains 5 bytes. With three added padding bytes, the master has to transmit two 4-byte groups.

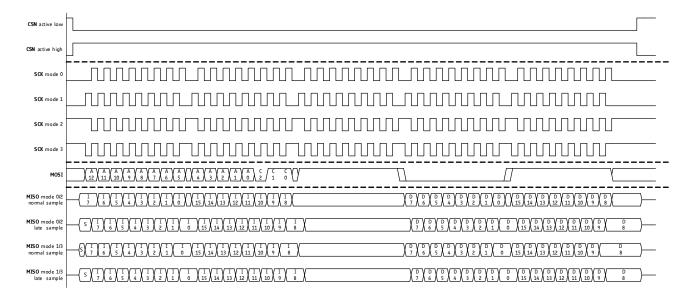

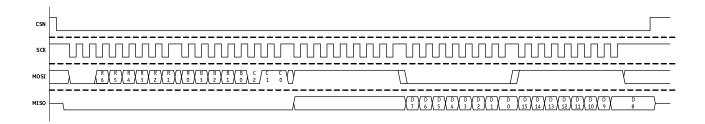

#### 5.1.2 Timing example

This example shows a generic read access with wait state and 2 byte addressing. All configurable options are shown. The delays between the transferred bytes are just to show the byte boundaries and are not required.

Figure 11: SPI timing example

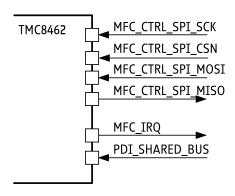

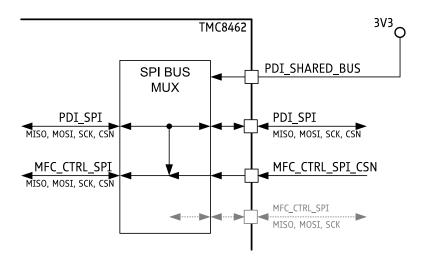

### 5.2 MFC IO Control Interface

The MFC IO block of the TMC8462 comes with a dedicated SPI slave interface to allow direct access from a local application controller. It is called MFC CTRL SPI interface. This interface to the MFC IO block's functions is always available, even if the EtherCAT state machine is currently not in operational state (OP). Protocol structure and timing are identical to the PDI SPI.

The MFC Control SPI is a SPI mode 3 slave with low active chip select. The SPI clock frequency can be up to 30MHz. The following diagram shows all signals related to the MFC CTRL SPI interface.

Figure 12: MFC control signals

| TMC8462 pin       | Description                                                                                                                                                                                                                                  | Typical pin on a MCU                                          |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| MFC_CTRL_SPI_CSN  | SPI chip select for the TMC8462 PDI                                                                                                                                                                                                          | SSx                                                           |

| MFC_CTRL_SPI_SCK  | SPI master clock                                                                                                                                                                                                                             | SCK                                                           |

| MFC_CTRL_SPI_MOSI | Master out slave in data                                                                                                                                                                                                                     | MOSI                                                          |

| MFC_CTRL_SPI_MISO | Master in slave out data                                                                                                                                                                                                                     | MISO                                                          |

| MFC_IRQ           | Configurable IRQ from MFC IO block                                                                                                                                                                                                           | General purpose Input                                         |

| PDI_SHARED_BUS    | 0: separate SPI buses for PDI and MFC CTRL; 1: shared/common SPI bus for PDI and MFC CTRL with 2 CSN signals using the PDI SPI bus. The SPI bus signals MFC_CTRL_SPI_SCK, MFC_CTRL_SPI_MISO, MFC_CTRL_SPI_MOSI can be left open in this case | General purpose Output or connected to either ground or 3.3V. |

Table 5: MFC CTRL SPI signal description

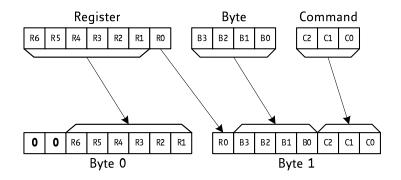

#### 5.2.1 SPI Protocol description

The protocol of the MFC CTRL SPI is the same as the PDI SPI interface (see section 5.1.1) The addresses for register access are calculated using the register number and the byte number in each register. To calculate the address, the register number is shifted left by 4 bits and the byte number is added as the 4 lowest bits. Access using the 3 byte addressing mode is possible, and can be used when 2 byte mode is not implemented for the PDI SPI but since the highest bits of the address are always 0, accessing the MFC Control SPI via 2 byte mode is sufficient.

Figure 13: MFC CTRL SPI 2 byte addressing

Figure 14: MFC CTRL SPI 3 byte addressing

#### 5.2.2 Timing example

This example shows a generic MFC register read access with wait state. The delays between the transferred bytes are just to show the byte boundaries and are not required.

Figure 15: MFC SPI timing example

#### 5.2.3 Sharing Bus Lines with the PDI SPI

To reduce the number of signals on the PCB or if the local application controller has only one SPI interface, the MFC CTRL SPI bus can share the SPI bus signals of the PDI SPI, requiring only separate chip select signals. In this case, both interfaces are internally switched to the PDI SPI interface pins. The original MFC CTRL SPI signals (MOSI, MISO, and SCK) remain unconnected in this case. Only the MFC\_CTRL\_SPI\_CSN pin/signal must be used if the MFCIO block is accessed.

To share the SPI bus lines, configuration pin PDI\_SHARED\_BUS must be pulled high as shown in the figure below.

Figure 16: SPI bus sharing

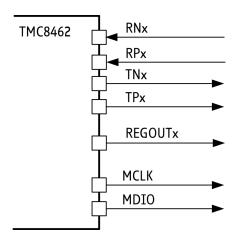

# **5.3 Ethernet Physical Layer Connection**

TMC8462 comes with two integrated 100-Mbit Ethernet PHYs eliminating the need for external PHY components. The physical media interface can connect to (shielded) twisted pair copper buses ((S)TPC). Port signals with index 0 represent the EtherCAT IN port. Port signals with index 1 represent the EtherCAT OUT port.

Figure 17: Physical bus interface pins

| TMC8462 pin | Description                                                                                                   |  |

|-------------|---------------------------------------------------------------------------------------------------------------|--|

| TNx         | Negative pin of differential transmit output pair                                                             |  |

| TPx         | Positive pin of differential transmit output pair                                                             |  |

| RNx         | Negative pin of differential receive output pair                                                              |  |

| RPx         | Positive pin of differential receive output pair                                                              |  |

| REGOUTX     | This is a regulator power output. A 10uF and 0.1uF should be connected to this pin for filtering power noise. |  |

| MCLK        | PHY configuration clock output                                                                                |  |

| MDIO        | PHY configuration data in-/output                                                                             |  |

Table 6: Physical bus interface pin description

# 5.4 External Circuitry and Applications Examples

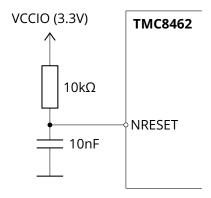

#### 5.4.1 Device Reset

The NRESET signal should at least be connected to VCCIO via a 10K resistor and to GND via a 10nF capacitor if no other controlled reset source for proper power-on behavior and reset is used.

Figure 18: Minimum external circuit for power-on reset

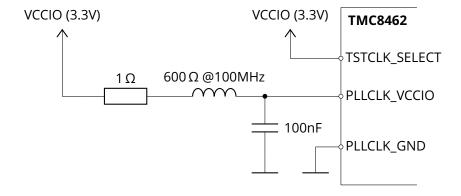

### 5.4.2 Supply Filtering for PLL Supply

The internal PLL is supplied with the same 3.3V as used for VCCIO. An R/L/C filter structure as shown in the circuit diagram is used. PLLCLK\_GND is connected to common ground.

Figure 19: PLL supply filter

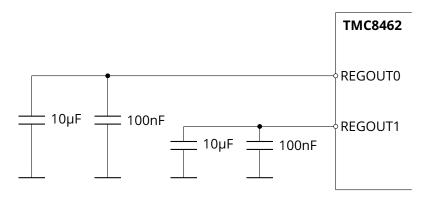

# 5.4.3 PHY Power Regulator Filtering

The internal PHY circuits require external filter capacitors.

Figure 20: PHY power regulator filtering

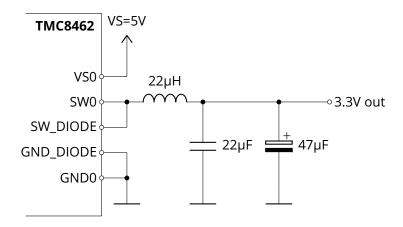

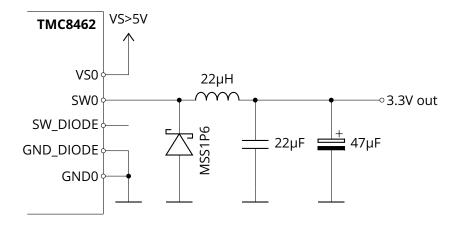

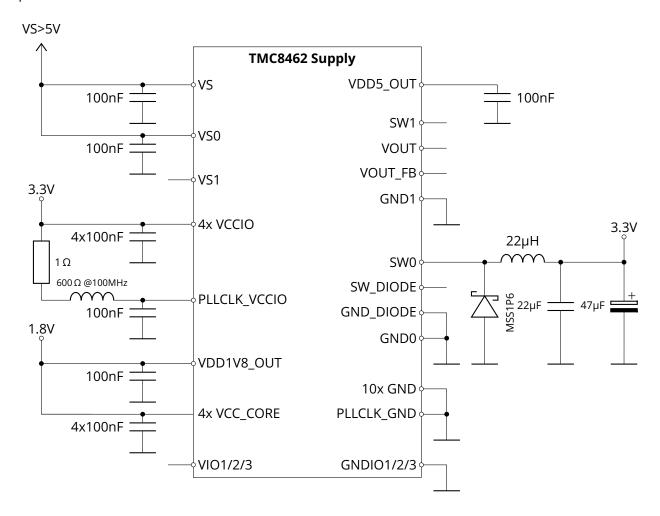

### 5.4.4 External Circuit for Fixed Switching Regulator 0

Switching regulator 0 is an internal buck switching regulator and generates <u>a fixed</u> 3.3V supply with approximately 500mA. This 3.3V supply shall be used to power VCCIO and PLLCLK\_VCCIO. This regulator comes with an integrated Schottky diode which minimizes part count, when an external 5V supply is available. This 3.3V can also be used to power other on-board devices, e.g., EEPROM or LEDs. The 3.3V rail is available at switching regulator 0 output SWO.

More information on the switching regulators is given in Section 7.21.

Figure 21: External circuit for switching regulator 0 with VS0 = 5V

Figure 22: External circuit for switching regulator 0 with VSO > 5V

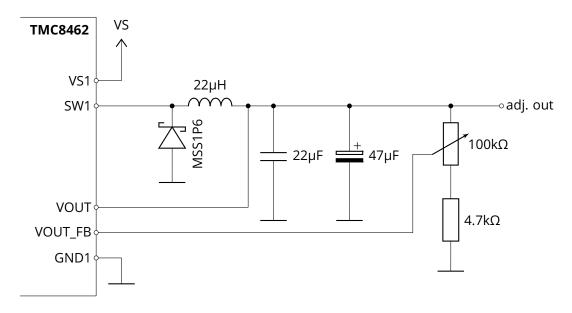

### 5.4.5 External Circuit for Adjustable Switching Regulator 1

Switching regulator 1 is an internal buck switching regulator and generates an <u>adjustable</u> supply rail with approximately 500mA. The voltage at SW1 can be adjusted using a resistor network in the switching regulator's feedback path at VOUT\_FB. VOUT\_FB should be at 1.2V using a resistor divider. SW1 can be used to power the high voltage IOs using VIO1, VIO2, VIO3 as well as switching regulator 0 input VS0 (which generates a fixed 3.3V rail). SW1 can also be used to power other peripheral devices, e.g., Hall signals of a BLDC motor or external encoders.

More information on the switching regulators is given in Section 7.21.

Figure 23: External circuit for adjustable buck regulator

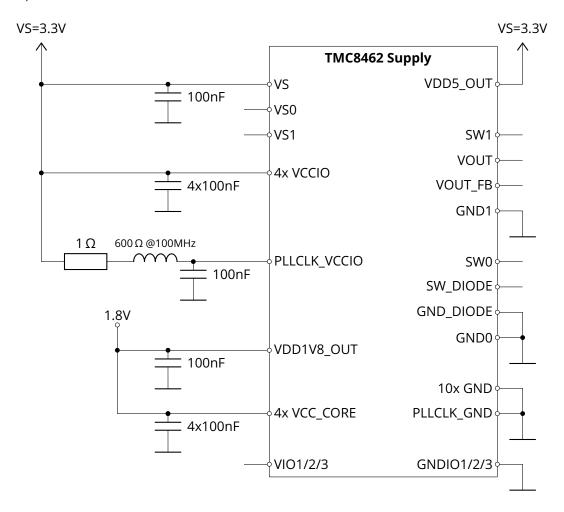

### 5.4.6 Minimum External Supply Circuit for Single 3.3V Supply

The diagram shows the minimum external circuit when using a single 3.3V supply only. Both internal switching regulators are not used in this example. Therefore, both supply ports VSO and VS1 are not connected.

The high voltage IOs are also not used in this example. Therefore, the three high voltage IO supply ports VIO1, VIO2, and VIO3 are not connected.

Figure 24: Minimum external supply circuit for single 3.3V supply

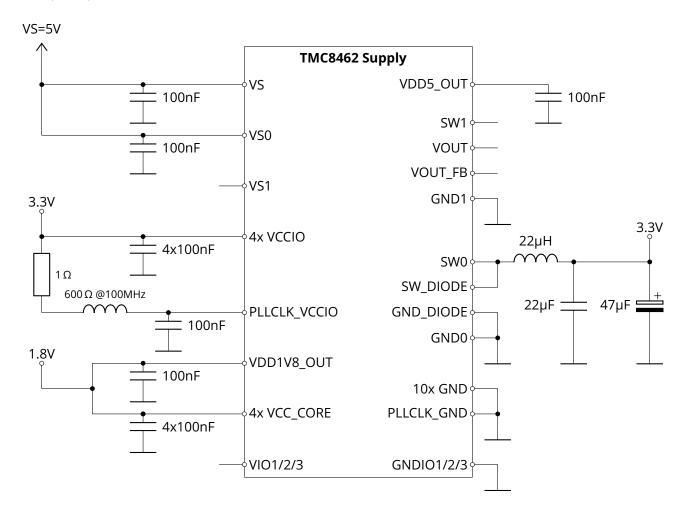

## 5.4.7 Minimum External Supply Circuit for Single 5V Supply

The diagram shows the minimum external circuit when using a single 5V supply only. Switching regulator 0 is used to generate the 3.3V for VCCIO and PLLCLK\_VCCIO. Switching regulator 1 is not used in this example. Therefore, supply port VS1 is not connected. The high voltage IOs are also not used in this example. Therefore, the three high voltage IO supply ports VIO1, VIO2, and VIO3 are not connected.

Figure 25: Minimum external supply circuit for single 5V supply

#### 5.4.8 Minimum External Supply Circuit for Single Supply >5V

To connect TMC8462 to a single supply greater than 5V the circuit is very similar to Figure 25. The main difference is that an additional external diode (MSS1P6) is required at output SW0. The pin SW\_DIODE is open.

Figure 26: Minimum external supply circuit for single supply >5V

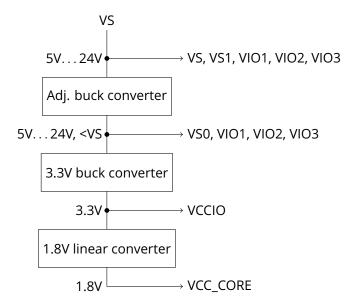

### 5.4.9 Typical Power Supply Chain Using Both Buck Converters

Figure 27: Typical power supply chain using both buck converters

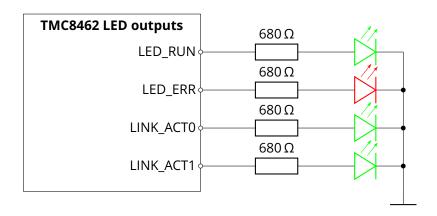

#### 5.4.10 Status LED Circuit

The TMC8462has 4 status LED outputs. All outputs are supplied from VCCIO (3.3V), and drive a LED with current limiting resistor to GND. The use of low current LED is recommended to keep supply current low and to stay within the current limit of 10mA per pin. The appropriate resistor value must be chosen for the selected LED's forward voltage.

For a 2V forward voltage at 2mA, a value of 680 Ohm is a reasonable value.

The LED colors are defined by **ETG.1300** (available on www.ethercat.org).

Figure 28: Status LED circuit

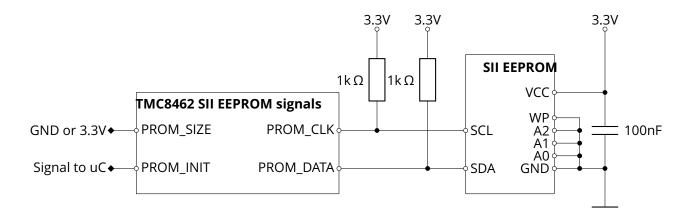

#### 5.4.11 SII EEPROM Circuit

An  $I^2C$  EEPROM is required for operation with the SII interface. Its size can be up to 4MBit. While the access protocol of the  $I^2C$  EEPROMs is standardized, the addressing procedure changes from one address

byte up to 16kBit to two address bytes from 32kBit. Up to 16kBit the PROM\_SIZE pin must be tied to GND, above that, it must be tied to VCCIO (3.3V).

Figure 29: SII EEPROM circuit (shown for EEPROMs >32kBit)

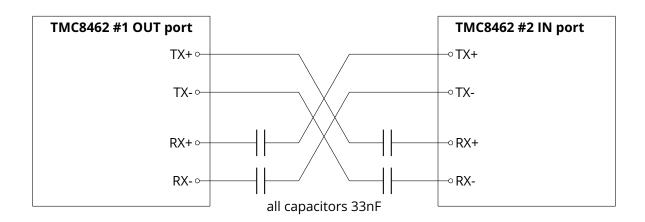

#### 5.4.12 Considerations on PHY to PHY Connection

In applications with multiple EtherCAT slave controllers in one enclosed device or even on the same PCB, it is not always necessary to connect the slave controllers via magnetics, RJ-45 connectors (or similar) and a patch cable. Instead a direct backbone connection or traces on the PCB can be used to directly link the PHYs, however coupling capacitors must be used in the connection.

This option reduces the cost as well as the required space in the setup.

Note

This connection method should be used only over short distances with no or few connectors in between. It is not recommended for longer distances, especially using a wired connection.

Figure 30: Direct PHY to PHY connection

# **6 EtherCAT Slave Controller Description**

#### 6.1 General EtherCAT Information

TMC8462 contains a standard-conform EtherCAT Slave Controller (ESC) providing real-time EtherCAT MAC layer functionality to EtherCAT slave devices. The ESC part of TMC8462 provides the following EtherCAT-related features:

- 16 KByte of Process Data RAM (PDRAM): The PDRAM is a dual ported RAM, which allows exchange of data between the EtherCAT master and the local application.

- Eight Sync Managers (SM): Sync Managers are used to control and secure the data exchange via the PDRAM in terms of data consistency, data security, and synchronized read/write operations on the data objects. Two modes –buffered mode and mailbox mode are available.

- Eight Fieldbus Memory Management Units (FMMU): FMMUs are used for mapping of logical addresses to physical addresses. The EtherCAT master uses logical addressing for data than spans multiple slaves. An FMMU can map such a logical address range to a continuous local physical address range.

- 64 bit Distributed Clock support (DC): DC is the base of the real-time capability of EtherCAT. Their underlying algorithms compute delay times between the master and the slaves and between slaves and update a common time stamp in all slaves. This way, synchronized time stamps (LATCH0/1) and synchronized trigger signals (SYNCO/1) are available in every slave and to the master.

- IIC interface for external SII EEPROM for ESC configuration: After reset and at power up, the ESC requires reading basic (and advanced) configuration data from an external SII EEPROM to properly configure interfaces, operation modes, and and feature availability. The SII EEPROM may be read and written by the master or the local application controller as well.

- SPI Process Data Interface (PDI): The PDI is the interface between the local application controller and the ESC. Application-specific process data and EtherCAT control and status information for the EtherCAT State Machine (ESM) is exchanged via this interface.

- Device Emulation Mode: This mode is a special mode of operation where no ESM in the application controller is required. The slave's operation states are simply directly set by the master without control of an ESM. This is beneficial for small and simple slaves, for example simple IO devices.

To manufacture own slaves devices, a registration with the EtherCAT Technology Group (ETG) is required. More information and resources on the EtherCAT technology and the EtherCAT standard are available here:

- EtherCAT Technology Group (ETG) (http://www.ethercat.org/)

- EtherCAT is standardized by the IEC (http://www.iec.ch/) and filed as IEC-Standard 61158.

# **6.2** Overview of Available Chip Features

The following table shows EtherCAT chip features available in TRINAMIC's EtherCAT slave controller solutions.

| Chip Feature / Description                                                         | Domain         | TMC8460 | TMC8461 | TMC8462 | TMC8670 |

|------------------------------------------------------------------------------------|----------------|---------|---------|---------|---------|

| Extended DL control register 0x0102:0x0103 enabled                                 | Register       | 1       | 1       | 1       | 1       |

| AL Status code register 0x0134:0x0135 enabled                                      | Register       | 1       | 1       | 1       | 1       |

| ECAT interrupt mask 0x0200:0x0201 enabled                                          | Register       | 1       | 1       | 1       | 1       |

| Configured station alias 0x0012:0x0013 enabled                                     | Register       | 1       | 1       | 1       | 1       |

| General purpose inputs 0x0F18:0x0F1F enabled                                       | Register       | 0       | 0       | 0       | 0       |

| General purpose outputs 0x0F10:0x0F17 enabled                                      | Register       | 0       | 0       | 0       | 0       |

| AL event mask 0x0204:0x0207 enabled                                                | Register       | 1       | 1       | 1       | 1       |

| Physical RD/WR offset 0x0108:0x0109 enabled                                        | Register       | 0       | 1       | 1       | 0       |